一种集成控制芯片的智能功率模块的制作方法

[0001]

本申请涉及电路领域,具体涉及一种集成控制芯片的智能功率模块。

背景技术:

[0002]

智能功率模块,即ipm(intelligent power module),是一种将电力电子和集成电路技术结合的功率驱动类产品。智能功率模块把功率开关器件和高压驱动电路集成在一起,并内藏有过电压、过电流和过热等故障检测电路。智能功率模块一方面接收控制芯片的控制信号,驱动后续电路工作,另一方面将系统的状态检测信号送回控制芯片。与传统分立方案相比,智能功率模块以其高集成度、高可靠性等优势赢得越来越大的市场,尤其适合于驱动电机的变频器及各种逆变电源,是变频调速,冶金机械,电力牵引,伺服驱动,变频家电的一种理想电力电子器件。

[0003]

针对小功率的电机,目前的ipm的电路拓扑没有单相全桥逆变结构,更没有集成单相全桥逆变结构+控制芯片的ipm,当需要通过控制芯片控制智能功率模块以驱动电机等负载时,只能通过将分立的控制芯片、驱动芯片以及多个三极晶体管在外围控制电路的连接下得以实现,上述的实现方式存在电路设计复杂,且占电路基板面积较大的问题。

[0004]

因此,现有技术存在缺陷,急需改进。

技术实现要素:

[0005]

本申请实施例的目的在于提供一种集成控制芯片的智能功率模块,能极大地简化模块的外围电路设计。

[0006]

本申请实施例提供了一种集成控制芯片的智能功率模块,包括:

[0007]

一控制芯片,其包括通用i/o接口以及第一vss端口;

[0008]

一hvic芯片,其包括第二vss端口、高侧输入端口、低侧输入端口、高侧输出端口以及低侧输出端口;所述高侧输入端口仅有hin1端口以及hin2端口,所述低侧输入端口仅有lin1端口以及lin2端口,所述高侧输出端口仅有ho1端口以及ho2端口,所述低侧输出端口仅有lo1端口以及lo2端口,所述第二vss端口连接于所述第一vss端口,所述hin1端口、hin2端口、lin1端口以及lin2端口均与所述通用i/o接口连接;

[0009]

一逆变器单元,所述逆变器单元仅有第一三极晶体管、第二三极晶体管、第三三极晶体管以及第四三极晶体管;

[0010]

所述第一三极晶体管,其栅极与所述ho1端口连接,其漏极连接于p点,其源极连接于a点;

[0011]

所述第二三极晶体管,其栅极与所述lo1端口连接,其漏极与所述第一三极晶体管的源极连接,其源极与所述第二vss端口连接;

[0012]

所述第三三极晶体管,其栅极与所述ho2端口连接,其漏极与所述第一三极晶体管的漏极连接,其源极连接于b点;

[0013]

所述第四三极晶体管,其栅极与所述lo2端口连接,其漏极与所述第三三极晶体管

的源极连接,其源极与所述第二三极晶体管的源极连接。

[0014]

优选地,本申请实施例的集成控制芯片的智能功率模块中,所述控制芯片内部设有至少两个高速运算放大器、至少两个比较器、至少一个a/d转换器、至少一个d/a转换器、多路复用器、通讯接口模块、核心处理器、电源模块以及时钟模块,所述高速运算放大器、比较器、a/d转换器、d/a转换器运算放大器均通过所述多路复用器与所述核心处理器连接,所述电源模块与所述高速运算放大器、比较器、a/d转换器、d/a转换器、多路复用器、通讯接口模块、核心处理器以及时钟模块连接,用于给所述控制芯片供电。

[0015]

优选地,本申请实施例的集成控制芯片的智能功率模块中,所述hvic芯片还包括vreg端口,所述控制芯片还包括vdd端口,所述vdd端口连接于所述vreg端口。

[0016]

优选地,本申请实施例的集成控制芯片的智能功率模块中,还包括第一自举电容和第二自举电容;

[0017]

所述hvic芯片还包括vb1端口以及vs1端口,所述vb1端口通过所述第一自举电容与所述vs1端口连接;所述hvic芯片还包括vb2端口以及vs2端口,所述vb2端口通过第二自举电容与所述vs2端口连接。

[0018]

优选地,本申请实施例的集成控制芯片的智能功率模块中,还包括一采样电阻;

[0019]

所述采样电阻的第一端连接所述第二三极晶体管的源极,所述采样电阻的第二端与所述第二vss端口连接;

[0020]

所述hvic芯片内设置有过流保护电路,用于当所述采样电阻采集的电流超过设定阈值时,停止工作。

[0021]

优选地,本申请实施例的集成控制芯片的智能功率模块中,还包括串联连接的第一分压电阻和第二分压电阻;

[0022]

所述hvic 芯片还包括itrip端口,所述第一分压电阻连接所述第二三极晶体管的源极,所述第一分压电阻和第二分压电阻的中间连接点与所述itrip端口连接,所述第二分压电阻分别与所述第一vss端口和第二vss端口连接;

[0023]

所述itrip端口在所述hvic芯片的内部通过一滤波电容下拉到所述第二vss端口。

[0024]

优选地,本申请实施例的集成控制芯片的智能功率模块中,所述第一三极晶体管、第二三极晶体管、第三三极晶体管以及第四三极晶体管为igbt晶体管、逆导型igbt晶体管或mosfet晶体管中的一种。

[0025]

优选地,本申请实施例的集成控制芯片的智能功率模块中,所述第一三极晶体管、第二三极晶体管、第三三极晶体管以及第四三极晶体管均为igbt晶体管;

[0026]

每个igbt晶体管连接有快恢复二极管,所述快恢复二极管的正极与所述igbt晶体管的源极连接,所述快恢复二极管的负极与所述igbt晶体管的漏极连接。

[0027]

优选地,本申请实施例的集成控制芯片的智能功率模块中,每个三极晶体管的栅极连接一栅极驱动电阻,所述栅极驱动电阻设于所述hvic芯片内部。

[0028]

优选地,本申请实施例的集成控制芯片的智能功率模块中,所述hvic芯片内还设置有过压保护开关、过温保护开关、报错电路以及使能电路。

[0029]

本申请实施例采用单颗hvic芯片来控制两组三极晶体管形成的单相全桥电路,并集成有控制芯片,只需外接母线储能电容、电源电路等,对控制芯片进行程序烧录后就能自动输出负载电机驱动所需要的pwm波形,通过hvic芯片和三极晶体管进行功率放大,实现电

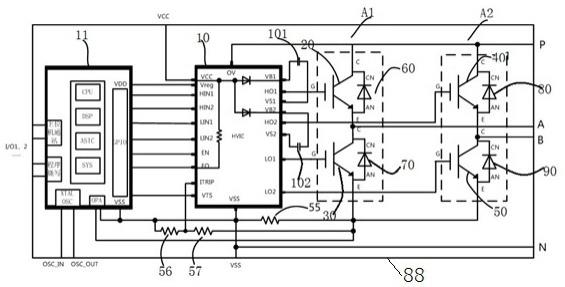

modulation,为脉宽调制,简称pwm),以控制hvic芯片10;一逆变器单元,该逆变器单元有且仅有第一三极晶体管20、第二三极晶体管30、第三三极晶体管40以及第四三极晶体管50;第一三极晶体管20,其栅极与ho1端口连接,其漏极连接于p点,其源极连接于a点;第二三极晶体管30,其栅极与lo1端口连接,其漏极与第一三极晶体管20的源极连接,其源极与第二vss端口连接;第三三极晶体管40,其栅极与ho2端口连接,其漏极与第一三极晶体管20的漏极连接,其源极连接于b点;第四三极晶体管50,其栅极与lo2端口连接,其漏极与第三三极晶体管40的源极连接,其源极与第二三极晶体管30的源极连接。

[0040]

需要说明的是,如图1所示,p点为本申请实施例集成控制芯片的智能功率模块的高压输入端,a点为本申请实施例集成控制芯片的智能功率模块的第一输出端a,b点为本申请实施例集成控制芯片的智能功率模块的第二输出端b,n点为本申请实施例集成控制芯片的智能功率模块的低电压参考端。在实际应用中,第一输出端a和第二输出端b为电机负载的接口,而p点用于接入电机负载的供电电源,n点与第二三极晶体管30和第四三极晶体管50的源极连接。

[0041]

在一些实施例中,如图3所示,本申请实施例的集成控制芯片的智能功率模块,控制芯片11为mcu芯片,mcu芯片内部设有至少两个高速运算放大器(opa)、至少两个比较器(cmp)、至少一个a/d转换器(adc)、至少一个d/a转换器(dac)、多路复用器(mux)、通讯接口模块、核心处理器、电源模块以及时钟模块。上述的高速运算放大器、比较器、a/d转换器、d/a转换器运算放大器均通过多路复用器与核心处理器连接,而电源模块与高速运算放大器、比较器、a/d转换器、d/a转换器、多路复用器、通讯接口模块、核心处理器以及时钟模块连接,用于给mcu芯片供电。

[0042]

需要说明的是,上述的高速运算放大器用于对mcu芯片接收或发送的信号进行数学运算的放大;比较器用于将mcu芯片接收到的检测信号与相应的基准信号相比较,根据该比较结果,mcu芯片给出相应的控制信号;a/d转换器和d/a转换器均为12位,用于数模或模数信号的转换;通讯接口模块包括uart\i2c\spi等通讯模块;核心处理器包括cpu、dsp、asic、sys等单元,sys包含至少32kb flash和至少8kb sram,以及看门狗、中断、寄存器等等;电源电路包括ldo(low dropout regulator,译为低压差线性稳压器)以及检测保护电路等,给内部电路供电;时钟模块包括内置rc振荡时钟电路、外部晶振时钟电路、pll (phase locked loop,为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取资料等)。

[0043]

其中,mcu 芯片还包括多个用作上位机通讯和程序仿真烧写的i/o引脚(一般为4~8个),以及时钟模块引出的晶振引脚,即如图1中的osc_in引脚和osc_out引脚。此外,hvic芯片10还包括vreg端口,mcu芯片还包括vdd端口, vdd端口连接于vreg端口。其中,vreg端口为hvic芯片10的基准电压端口,为mcu芯片提供5v电压。由此,在本申请实施例的集成控制芯片的智能功率模块中,mcu芯片仅仅需要引出4~8个上位机通讯和程序仿真烧写的i/o引脚以及两个晶振引脚,而外围接入的控制芯片至少有8-44个引脚,本申请实施例的集成控制芯片的智能功率模块可大大减少封装模块引脚的数量,简化电路设计,方便使用。

[0044]

在一些实施例中,如图2所示,图2是本申请一些实施例中的一种智能功率模块的hvic芯片10的原理图。hvic芯片10还包括vcc端口,该vcc端口引出作为整个智能功率模块的vcc引脚。且第二vss端口也引出作为整个智能功率模块的vss引脚。其中,vcc端口是hvic

芯片10的供电电源正端,通过vcc引脚连接外部电源;第二vss端口为hvic芯片10的供电电源负端,vss引脚为智能功率模块的公共接地端。在实际应用中,vcc端口与第二vss端口之间的电压一般设置为15v,当然,可根据实际需要设置该处的电压,在此,并不做限制。

[0045]

需要说明的是,智能功率模块的vcc引脚通过hvic芯片10的vcc端口连接hvic芯片10内部的电源电路,给hvic芯片10提供工作电源。hvic芯片10的hin1端口连接hvic芯片10内部的第一高侧驱动电路,并通过hvic芯片10的ho1端口输出控制信号,以决定第一三极晶体管20的通断;hvic芯片10的hin2端口连接hvic芯片10内部的第二高侧驱动电路,并通过hvic芯片10的ho2端口输出控制信号,以决定第三三极晶体管40的通断;hvic芯片10的lin1端口连接hvic芯片10内部的第一低侧驱动电路,并通过hvic芯片10的lo1端口输出控制信号,以决定第二三极晶体管30的通断;hvic芯片10的lin2端口连接hvic芯片10内部的第二低侧驱动电路,并通过hvic芯片10的lo2端口输出控制信号,以决定第四三极晶体管50的通断。其中,本申请实施例的智能功率模块的hvic芯片10的hin1端口、hin2端口、lin1端口以及lin2端口接收mcu芯片0v或5v的控制信号。当然,根据实际需要可以接收其他电压幅值的输入信号,具体根据电路所连接的实际器件进行选择。

[0046]

需要进一步地进行说明的是,hvic芯片10内部还设有电源欠压保护电路,其与电源电路连接,以保护智能功率模块和器件。且两路高侧驱动电路也连接有高侧欠压保护电路,对智能功率模块和器件进行保护。

[0047]

其中,该第二三极晶体管30以及该第一三极晶体管20组成一个全桥电路a1。该第三三极晶体管40以及该第四三极晶体管50组成一个全桥电路a2。全桥电路a1中的第一三极晶体管20和第二三极晶体管30只能择一导通;全桥电路a2中的第三三极晶体管40和第四三极晶体管50也只能择一导通。因此,第一三极晶体管20和第四三极晶体管50构成一组通路,由同一组信号驱动,同时导通/关断;第三三极晶体管40和第二三极晶体管30构成另一组通路,由同一组信号驱动,同时导通/关断。

[0048]

在实际应用中,mcu芯片通过hin1端口、hin2端口、lin1端口、lin2端口发送的pwm波,通过hvic芯片10的ho1端口、h02端口、lo1端口、lo2端口输出的电平信号以控制四个三极晶体管通断。在第一三极晶体管20和第四三极晶体管50构成一组通路、第三三极晶体管40和第二三极晶体管30构成另一组通路中择一通路导通,以实现电机的变频驱动。

[0049]

需要说明的是,相应地,hvic芯片10内部的第一高侧驱动电路与第一低侧驱动电路之间、第二高侧驱动电路与第二低侧驱动电路之间分别设有设有互锁与死区电路,以实现全桥电路中的两个三极晶体管只能择一导通,防止短路。

[0050]

进一步地,在一些实施例中,该智能功率模块还包括第一自举电容101以及第二自举电容102。其中,该hvic芯片10还包括vb1端口以及vs1端口,vb2端口以及vs2端口。vb1端口通过第一自举电容101与vs1端口连接。vb2端口通过第二自举电容102与vs2端口连接。其中,vb1端口为第一自举电容101的供电电源正端,vs1端口为第一自举电容101的供电电源负端;vb2端口为第二自举电容102的供电电源正端,vs2端口为第二自举电容102的供电电源负端。第一自举电容101以及第二自举电容102用于储能供电(或者说升压),为hvic芯片10的供电电源提供升压。该智能功率模块还包括两个自举二极管,hvic芯片10的vcc端口通过电源电路与两个自举二极管的阳极连接,两个自举二极管的阴极分别通过vb1端口和vb2端口与第一自举电容101、第二自举电容102对应连接,该自举二极管用于整流,防止电流倒

灌,以保护电源电路。在现有的智能功率模块中,其设置多为一颗三路三相全桥驱动ic+6个三极晶体管,使得模块的封装面积过大,难以将自举电容这一大功率器件设置在模块内部,只能在外接相应的自举电容,但外接自举电容会导致模块的易用性差,可靠性也变差。

[0051]

在一些实施例中,该智能功率模块还包括一采样电阻55,第二vss端口通过采样电阻55与第二三极晶体管的源极30、第四三极晶体管50的源极以及智能功率模块的低电压参考端n点依次连接。进一步地,hvic芯片10设有itrip端口,该itrip端口为hvic芯片10的过流保护端口。hvic芯片10内设置有过流保护电路,该过流保护电路连接itrip端口,且itrip端口在hvic芯片10的内部通过一滤波电容下拉到所第二vss端口。

[0052]

进一步地,本申请实施例的集成控制芯片的智能功率模块中,还包括串联连接的第一分压电阻57和第二分压电阻56。第一分压电阻57连接所述第二三极晶体管的源极,第一分压电阻57和第二分压电阻56的中间连接点与itrip端口连接,第二分压电阻56分别与第一vss端口和第二vss端口连接。且第二分压电阻56还与mcu芯片内部的高速运算放大器连接,高速运算放大器同时也与第二三极晶体管的源极30、第四三极晶体管50的源极。当采样电阻55检测到智能功率模块的低电压参考端n点处的电压,将该电压通过智能功率模块反馈给mcu芯片,并通过高速运算放大器将该信号放大,mcu根据将该电压转换成对应的电流,并与设定的电流阈值相比,若该电流超过设定阈值时,再通过itrip端输入相应的控制信号,通过控制过流保护电路停止hvic芯片10的工作,继而停止智能功率模块的工作,对器件进行保护。

[0053]

当然,可以理解地,在一些实施例中,hvic芯片10内还设置有过温保护开关、过压保护开关、使能保护开关、报错电路等。针对过温保护开关、过压保护开关、使能保护开关、报错电路,hvic芯片10对应设置有vts端口、ov端口、en端口、fo端口,上述vts端口、en端口、fo端口也通过通用i/o接口与mcu芯片连接,对应接收或反馈相应的信号到mcu芯片,而ov端口与高压输入端p点连接,检测高压输入端p点的电压是否超过设定阈值,对器件进行包括。其中,过温保护开关为正温度系数温度保护开关。此外,hvic芯片10的fo端口内部通过电阻上拉到vcc端口。

[0054]

在一些实施例中,本申请实施例的集成控制芯片的智能功率模块的第一三极晶体管20、第二三极晶体管30、第三三极晶体管40以及第四三极晶体管50为igbt晶体管、逆导型igbt晶体管或mosfet晶体管中的一种。

[0055]

如图4a所示,图4a为本申请实施例1中的一种集成控制芯片的智能功率模块的侧面结构示意图。在图4a所示的实施例中,第一三极晶体管20、第二三极晶体管30、第三三极晶体管40以及第四三极晶体管50均为逆导型igbt晶体管或mosfet晶体管,无需并联快恢复二极管。在图4a的实施例中,hvic芯片10采用银胶或焊锡粘接到绝缘基板15上,逆导型igbt晶体管或mosfet晶体管13采用焊锡粘接到绝缘基板15上,控制芯片11采用银胶或焊锡粘接到绝缘基板15上;hvic芯片10再采用金、铜、铝等键合线14连接到绝缘基板电路,igbt晶体管或mosfet晶体管13采用铝键合线连接到绝缘基板电路或hvic芯片10;引线框架16采用焊锡粘接到绝缘基板15上;最后采用环氧塑封材料17把基板和所有芯片、键合线都包封起来,仅露出引脚。

[0056]

如图4b所示,图4b为本申请实施例2中的一种集成控制芯片的智能功率模块的侧面结构示意图。在图4b所示的实施例中,第一三极晶体管20、第二三极晶体管30、第三三极

晶体管40以及第四三极晶体管50均为igbt晶体管。每个igbt晶体管13连接有快恢复二极管18,快恢复二极管18的正极与igbt晶体管13的源极连接,快恢复二极管18的负极与igbt晶体管13的漏极连接。

[0057]

进一步地,在图4a和图4b所示的实施例中,每个三极晶体管的栅极连接一栅极驱动电阻,该栅极驱动电阻设于hvic芯片10的内部,用于防止驱动电流瞬时过大,产生振荡。

[0058]

本申请实施例的智能功率磨料采用绝缘基板把mcu、hvic、igbt、frd等芯片和引线框架组装起来,通过键合线连接形成完整的sipm电路,通过环氧塑封材料封装在一起,形成物理保护,构成具有完整系统功能单相全桥sipm模块,单个sipm只需外接母线储能电容、电源电路等, mcu芯片程序烧写后,能自动输出电机驱动需要的pwm波形,通过hvic芯片和igbt芯片进行功率放大,就能实现电机驱动、逆变等功能,简化电路设计,使用方便。

[0059]

以上所述仅为本申请的实施例而已,并不用于限制本申请的保护范围,对于本领域的技术人员来说,本申请可以有各种更改和变化。凡在本申请的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本申请的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1