供电电路及电源供应器的制作方法

1.本发明涉及供电装置,特别是一种供电电路及电源供应器。

背景技术:

2.电源供应器是一种将交流电转成低压稳定的直流电,以供电器使用的装置。当交流电为市电时,电源供应器的输入电压一般为100v至250v之间,输入交流电频率为50hz或60hz,输出电压可为21v、12v、5v或3.3v等稳定的直流电压。相关技术中使用变压器将输入电压的高压交流电降压为低压交流电,再将低压交流电转换为直流电压。由于变压器体积较大,因此无法降低电源供应器的大小。此外,当输出电压的范围变大,变压器所需的耐压也会增加,然而耐压组件体积较大,更增加电源供应器的大小,因此相关技术中的电源供应器在便携设备或其他小型电器上使用不便。

技术实现要素:

3.本发明实施例提供一种供电电路,包括整流电路、充电电路、时窗调整电路、驱动电压调整电路、取样反馈电路及储存电路。整流电路用以接收输入电压以产生整流电能。充电电路耦接于整流电路,具有调变输入端与电源电能端,调变输入端用以接收控制电压,并依据控制电压来选择性地于电源电能端输出充电电能,充电电能大小与控制电压大小为正相关。时窗调整电路耦接于调变输入端,用以接收输出电压信号,并输出控制电压至调变输入端,时窗调整电路依据输出电压信号所对应的取样输出电压来调整控制电压,控制电压的大小与取样输出电压大小为负相关。驱动电压调整电路耦接于调变输入端,用以接收输出电压信号,并依据输出电压信号将控制电压控制于钳位电压之内。取样反馈电路耦接于电源电能端,用以依据电源电能端的电压产生输出电压信号。储存电路耦接于电源电能端,用以储存充电电能以拉高电源电能端的电压。当电源电能端的电压较低时,所对应的输出电压信号会使钳位电压具有较高上限;当电源电能端的电压较高时,所对应的输出电压信号会使钳位电压具有较低上限,较高上限大于较低上限。

4.本发明实施例提供一种电源供应器,包括供电电路、功率开关及脉冲宽度调制信号产生器。功率开关用以选择性地导通或截止以进行电源转换,以调控电源供应器的输出电压。脉冲宽度调制信号产生器用以提供脉冲宽度调制信号来控制功率开关,脉冲宽度调制信号产生器耦接于供电电路的电源电能端,用以自电源电能端接收电能来维持脉冲宽度调制信号产生器运作。

附图说明

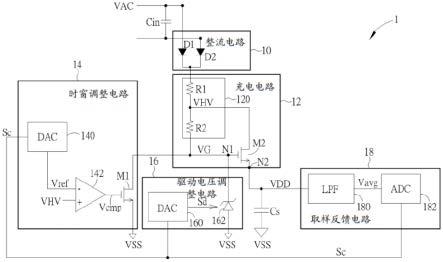

5.图1为本发明实施例中一种供电电路的电路示意图。

6.图2为图1中的低通滤波器的电路示意图。

7.图3为图1中的供电电路的信号波形图。

8.图4为本发明实施例中另一种供电电路的电路示意图。

9.图5为本发明实施例中一种电源供应器的框图。

10.附图标记:

11.1,4,50:供电电路

12.10:整流电路

13.12:充电电路

14.120:分压电路

15.14:时窗调整电路

16.140:数字模拟转换电路

17.142:比较电路

18.16:驱动电压调整电路

19.160:数字模拟转换电路

20.162:二极管组

21.18,48:取样反馈电路

22.180:低通滤波器

23.182:模拟数字转换电路

24.480:取样电路

25.5:电源供应器

26.52:脉冲宽度调制信号产生器

27.54:功率开关

28.c1:第一电容

29.c2:第二电容

30.cin:输入电容

31.cs:储存电路

32.d1,d2:二极管

33.m1:第一放大电路

34.m2:第二放大电路

35.n1:调变输入端

36.n2:电源电能端

37.r1,r2:电阻

38.s1:第一开关

39.s2:第二开关

40.sc:输出电压信号

41.sd:充电能力控制信号

42.spwm:脉冲宽度调制信号

43.t0至t14:时间

44.vac:输入电压

45.vavg:平均电压

46.vcmp:比较电压

47.vdd:电压

48.vdd_bottom:下限电压

49.vdd_top:上限电压

50.vg:控制电压

51.vhv:分压

52.vout:输出电压

53.vref:取电临界电压

54.vss:接地电压

55.vs,vs(1)至vs(11):取样电压

具体实施方式

56.图1为本发明实施例中一种供电电路1的电路示意图。供电电路1可接收输入电压vac,及依据输入电压vac提供合适的电压vdd。具体而言,供电电路1可于输入电压vac较低时,自输入电压vac接收电能进行充电以提高电压vdd;于输入电压vac较高时停止充电,同时储存电路cs持续释放电能供应电压vdd,将电压vdd维持在运作范围内。如此仅于输入电压vac较低时才导通接收电能对储存电路cs进行充电,而于输入电压vac较高时断路暂停接收电能、暂停对储存电路cs充电,如此可提高运作效率,同时降低供电电路1的面积。输入电压vac可由市电或其他交流电压源供电,其均方根值可介于100v至240v之间,其峰值可介于155至373v之间。当此供电电路1应用于一反激电源供应器(flyback transformer)中,输入电压vac可为该反激电源供应器的辅助绕组线圈电压vaux,并且该辅助绕组线圈电压vaux与该反激电源供应器的二次侧输出电压vout具有一变压器绕线组圈数比关系,该二次侧输出电压vout可介于3.3v至27v之间变化。该电压vdd可为直流电压,且可用来作为该反激电源供应器一次侧的脉冲宽度调变器(pwm modulator)的电源电能,该电压vdd可设定为高于8v。

57.供电电路1可包括输入电容cin、整流电路10、充电电路12、时窗调整电路14、驱动电压调整电路16、取样反馈电路18及储存电路cs。输入电容cin可耦接于整流电路10,整流电路10可耦接于充电电路12,充电电路12可耦接于时窗调整电路14、驱动电压调整电路16及储存电路cs,储存电路cs可耦接于取样反馈电路18,取样反馈电路18可耦接于时窗调整电路14。

58.输入电容cin可接收输入电压vac及滤除输入电压vac中的高频噪声,整流电路10可对滤除噪声后的输入电压vac进行整流以产生整流电能。整流电能的电压可称为整流电压。输入电容cin包括第一端及第二端。整流电路10可包括二极管d1及二极管d2。二极管d1包括第一端,耦接于输入电容cin的第一端;及第二端。二极管d2包括第一端,耦接于输入电容cin的第二端;及第二端,耦接于二极管d1的第二端。

59.充电电路12可具有调变输入端n1与电源电能端n2,时窗调整电路14及驱动电压调整电路16耦接于调变输入端n1,取样反馈电路18耦接于电源电能端n2。充电电路12可接收控制电压vg,并依据控制电压vg来选择性地于电源电能端n2输出充电电能。充电电路12可包括分压电路120及第二放大电路m2。分压电路120可耦接于整流电路10,及可接收整流电压以输出整流电能的分压vhv。分压电路120可包括电阻r1及电阻r2。电阻r1包括第一端,耦接于二极管d1的第二端及二极管d2的第二端;及第二端。电阻r2包括第一端,耦接于电阻r1

的第二端;及第二端。电阻r2的第一端可输出分压vhv。第二放大电路m2可耦接于分压电路120、时窗调整电路14及驱动电压调整电路16,及可依据控制电压vg来选择性地产生充电电能。当控制电压vg大于第二放大电路m2的阀值电压时,第二放大电路m2会产生充电电能,充电电能大小与控制电压vg大小为正相关。当控制电压vg小于第二放大电路m2的阀值电压时,第二放大电路m2会停止产生充电电能。充电电能的电流可称为充电电流。第二放大电路m2可由晶体管实现,例如nmos晶体管。第二放大电路m2可以以电压随动器(voltage follower)的方式设置。若第二放大电路m2由nmos晶体管实现时,nmos晶体管的漏极端可接收分压vhv,nmos晶体管的栅极端可为调变输入端n1,nmos晶体管的源极端可为电源电能端n2。

60.储存电路cs可储存充电电能以拉高电源电能端n2的电压vdd。储存电路cs可包括储存电容,储存电容包括第一端,耦接于电源电能端n2;及第二端,耦接于接地端。接地端可提供接地电压vss,例如0v。具体而言,当储存充电电能时充电电流可对储存电路cs充电以建立电压vdd。电压vdd可被输出至外部电路用以供电。

61.取样反馈电路18可依据电源电能端n2的电压vdd产生输出电压信号sc。取样反馈电路18可包括低通滤波器(low pass filter,lpf)180及模拟数字转换电路(analog-to-digital convertor,adc)182。低通滤波器180包括第一端,耦接于储存电路cs,用以接收电源电能端n2的电压vdd以产生电压vdd的平均电压vavg;及第二端,用以输出平均电压vavg。低通滤波器180可由开关电容滤波器(switched capacitor filter)实现,如图2所示。图2为低通滤波器180的电路示意图。低通滤波器180可包括第一开关s1、第一电容c1、第二开关s2及第二电容c2。第一开关s1包括第一端,耦接于储存电路cs,用以接收电源电能端n2的电压vdd;及第二端。第一电容c1包括第一端,耦接于第一开关s1的第二端;及第二端,耦接于接地端。第二开关s2包括第一端,耦接于第一开关s1的第二端;及第二端。第二电容c2包括第一端,耦接于第二开关s2的第二端,用以输出平均电压vavg;及第二端,耦接于接地端。第一开关s1及第二开关s2可依据预定切换频率f交替切换。当第一开关s1导通且第二开关s2截止时,第一电容c1可被充电且可储存电荷qin=c1*vdd,当第一开关s1截止且第二开关s2导通时,第一电容c1可被放电且可释放电荷qout=c1*vavg,每个切换周期传送至第二开关s2的第二端的电荷为qtrans=c1*(vdd-vavg),每个切换周期中的平均电流为iavg=f*c1*(vdd-vavg),等效电阻r为(vdd-vavg)/iavg=1/(f*c1)。第一开关s1、第一电容c1及第二开关s2的等效电阻r可由切换频率f及第一电容c1决定。第一开关s1、第二开关s2、第一电容c1及第二电容c2可由晶体管实现,及可形成低通滤波器180,用以输出平均电压vavg。

62.参考图1,模拟数字转换电路182包括第一端,耦接于低通滤波器180,用以依据预定信号范围将平均电压vavg进行量化而转换为输出电压信号sc;及第二端,用以将输出电压信号sc输出。量化可为均匀量化或非均匀量化。输出电压信号sc可为数字信号,例如3位数字信号。模拟数字转换电路182可包含缓存器(register),例如3位缓存器,用以储存3位数字信号。例如,预定信号范围可为10v至12v,模拟数字转换电路182可将预定信号范围分为8份。当平均电压vavg大于12v时,模拟数字转换电路182可产生输出电压信号sc的最小值3b000;当平均电压vavg小于10v时,模拟数字转换电路182可产生输出电压信号sc的最大值3b111。模拟数字转换电路182可将靠近预定信号范围的上限电压(例如:12v)的平均电压vavg进行量化而产生电压信号sc的较小值;及将靠近预定信号范围的下限电压(例如:10v)

的平均电压vavg进行量化而产生电压信号sc的较大值。例如,当平均电压vavg为11.6v时,模拟数字转换电路182可产生3b001的输出电压信号sc;当平均电压vavg为10.4v时,模拟数字转换电路182可产生3b110的输出电压信号sc。

63.时窗调整电路14可接收输出电压信号sc,依据输出电压信号sc所对应的取电临界电压vref来调整控制电压vg,并输出控制电压vg至调变输入端n1。时窗调整电路14可包括数字模拟转换电路(digital-to-analog converter,dac)140、比较电路142及第一放大电路m1。数字模拟转换电路140可耦接于取样反馈电路18,比较电路142可耦接于数字模拟转换电路140及分压电路120,第一放大电路m1可耦接于比较电路142及第二放大电路m2。数字模拟转换电路140可将输出电压信号sc进行数字模拟转换以产生取电临界电压vref。输出电压信号sc的位值可对应取电临界电压vref的模拟值。例如,输出电压信号sc的最大值3b111可对应取电临界电压vref的最大值100v,输出电压信号sc的最小值3b000可对应取电临界电压vref的最小值50v。比较电路142可接收取电临界电压vref及分压vhv以依据取电临界电压vref及分压vhv产生比较电压vcmp。分压vhv可具有全波整流波形。比较电路142可为运算放大器,包括正向输入端,可接收分压vhv;负向输入端,可接收取电临界电压vref;及输出端,可输出比较电压vcmp。第一放大电路m1可依据比较电压vcmp产生控制电压vg。控制电压vg的大小与取电临界电压vref大小为负相关。整流电能的分压vhv减去取电临界电压vref来决定一电压差值,该电压差值与比较电压vcmp为正相关,控制电压vg大小与比较电压vcmp大小为负相关。当取电临界电压vref越高,对于相同的分压vhv来说比较电压vcmp会越低,且控制电压vg会越高;当取电临界电压vref越低,对于相同的分压vhv来说比较电压vcmp会越高,且控制电压vg会越低。当分压vhv大于取电临界电压vref时,比较电压vcmp可为正值,第一放大电路m1会导通以产生小于第二放大电路m2的阀值电压的控制电压vg,进而截止第二放大电路m2来停止输出充电电能及不对储存电路cs充电,即取电时窗关闭且充电电路12停止从分压vhv取电、停止产生充电电流;当分压vhv小于取电临界电压vref时,比较电压vcmp可为负值,第一放大电路m1会截止以产生大于第二放大电路m2的阀值电压的控制电压vg,进而导通第二放大电路m2来对储存电路cs输出充电电能以进行充电,即取电时窗开启且充电电路12开始从分压vhv取电,充电电能大小与控制电压vg大小为正相关。

64.驱动电压调整电路16可接收输出电压信号sc,并依据输出电压信号sc将控制电压vg控制于钳位电压之内。钳位电压可为控制电压vg的上限电压。当电源电能端n2的电压vdd较低时所对应的输出电压信号sc会使钳位电压较高,因此增加供电电路1的充电能力;当电源电能端n2的电压vdd较高时所对应的输出电压信号sc会使钳位电压较低,因此降低供电电路1的充电能力。驱动电压调整电路16可包括数字模拟转换电路160及二极管组162。数字模拟转换电路160可耦接于取样反馈电路18,取样反馈电路18可耦接于数字模拟转换电路160及充电电路12。数字模拟转换电路160可将输出电压信号sc进行数字模拟转换以产生充电能力控制信号sd。二极管组162可依据充电能力控制信号sd提供钳位电压。当平均电压vavg越高,则二极管组162可依据充电能力控制信号sd提供越低的钳位电压;当平均电压vavg越低,则二极管组162可依据充电能力控制信号sd提供越高的钳位电压。

65.输出电压信号sc可用以控制取电时窗及控制电压vg的钳位电压。当平均电压vavg增加时,输出电压信号sc会减小,减短取电时窗及降低控制电压vg的钳位电压;当平均电压vavg减少时,输出电压信号sc会增加,增长取电时窗及增加控制电压vg的钳位电压。供电电

路1直接由输入电压vac取电以产生电压vdd,依据电压vdd的平均电压vavg调整取电时窗及控制电压vg的钳位电压,将电压vdd维持在运作范围内,提高运作效率,同时降低电路面积。

66.图3为供电电路1的信号波形图,包括3取电时窗,第一取电时窗介于时间t1至t4之间,第二取电时窗介于时间t7至t8之间,第三取电时窗介于时间t11至t12之间。在3个取电时窗之中,充电电路12对储存电路cs充电,电压vdd增加;在3个取电时窗之外,储存电路cs被放电,电压vdd降低。电压vdd维持于上限电压vdd-top及下限电压vdd-bottom之间。例如上限电压vdd-top可为12v,下限电压vdd-bottom可为10v。在时间t0至t1之间,分压vhv超出取电临界电压vref,控制电压vg小于第二放大电路m2的阀值电压,第二放大电路m2截止,充电电路12停止从分压vhv取电来产生充电电流,故电压vdd降低。

67.在时间t1及t4之间,分压vhv小于取电临界电压vref,控制电压vg大于第二放大电路m2的阀值电压,第二放大电路m2导通,第一取电时窗开启。在第一取电时窗中,在时间t2及t3之间,分压vhv已低于电压vdd,储存电路cs放电,使得电压vdd降低;在时间t1至t2之间、及时间t3至t4之间,分压vhv大于电压vdd,储存电路cs从分压vhv取电,电压vdd增加。在时间点t4,第一取电时窗关闭,电压vdd到达峰值。在时间t4至t7之间,分压vhv超出取电临界电压vref,控制电压vg小于第二放大电路m2的阀值电压,第二放大电路m2截止,电压vdd降低。在时间点t5,取样反馈电路18会依据电压vdd产生平均电压vavg。相较于前一个取电时窗,由于平均电压vavg上升,使得平均电压vavg及上限电压vdd-top之间的差值减小,输出电压信号sc的信号值会减小。在时间点t6,时窗调整电路14会依据输出电压信号sc更新取电临界电压vref至较低值。

68.在时间t7至t8之间,分压vhv小于取电临界电压vref,控制电压vg大于第二放大电路m2的阀值电压,第二放大电路m2导通,第二取电时窗开启。在第二取电时窗中,当分压vhv低于电压vdd时,储存电路cs放电,使得电压vdd降低;当分压vhv大于电压vdd时,储存电路cs从分压vhv取电,电压vdd增加。在时间点t8,第二取电时窗关闭,电压vdd到达峰值。由于判定第二取电时窗使用的取电临界电压vref小于判定第一取电时窗使用的取电临界电压vref,因此第二取电时窗较第一取电时窗短。在时间t8至t11之间,分压vhv超出取电临界电压vref,控制电压vg小于第二放大电路m2的阀值电压,第二放大电路m2截止,电压vdd降低。在时间点t9,取样反馈电路18会依据电压vdd产生平均电压vavg。相较于前一个取电时窗,由于平均电压vavg上升,使得平均电压vavg及上限电压vdd-top间的差值减小,输出电压信号sc的信号值会减小。在时间点t10,时窗调整电路14会依据输出电压信号sc更新取电临界电压vref至更低值。

69.在时间t11至t12之间,分压vhv小于取电临界电压vref,控制电压vg大于第二放大电路m2的阀值电压,第二放大电路m2导通,第三取电时窗开启。在第三取电时窗中,当分压vhv低于电压vdd时,储存电路cs放电,使得电压vdd降低;当分压vhv大于电压vdd时,储存电路cs从分压vhv取电,电压vdd增加。在时间点t12,第三取电时窗关闭,电压vdd到达峰值。由于判定第三取电时窗使用的取电临界电压vref小于判定第二取电时窗使用的取电临界电压vref,因此第三取电时窗较第二取电时窗短。在时间点t12至下个取电时窗开启前,分压vhv超出取电临界电压vref,控制电压vg小于第二放大电路m2的阀值电压,第二放大电路m2截止,电压vdd降低。在时间点t13,取样反馈电路18会依据电压vdd产生平均电压vavg。相较于前一个取电时窗,由于平均电压vavg下降,使得平均电压vavg及上限电压vdd-top之间的

差值增加,输出电压信号sc的信号值会增加。在时间点t14,时窗调整电路14会依据输出电压信号sc更新取电临界电压vref至较高值。

70.图3包括在第一取电时窗、第二取电时窗及第三取电时窗中的电压vdd的局部放大图30、32及34。由于驱动电压调整电路16会依据输出电压信号sc产生钳位电压,及将控制电压vg控制于钳位电压之内以调整供电电路1的充电能力,因此第一取电时窗、第二取电时窗及第三取电时窗中的电压vdd会具有不同的上升斜率(充电速度)。越高的钳位电压会对应越大的上升斜率;越低的钳位电压会对应越小之上升斜率。

71.其中第一取电时窗的平均电压vavg高于前一个取电时窗的平均电压vavg,故于第一取电时窗后的时间点t6,时窗调整电路14将取电临界电压vref向下修正,且驱动电压调整电路16调降钳位电压。类似地,第二取电时窗的平均电压vavg仍高于第一取电时窗的平均电压vavg,故于第二取电时窗后的时间点t10,时窗调整电路14将取电临界电压vref再次向下修正,驱动电压调整电路16也再次调降钳位电压。相对地,第三取电时窗的平均电压vavg低于第二取电时窗的平均电压vavg,故于第三取电时窗后的时间点t14,时窗调整电路14将取电临界电压vref改为向上修正,驱动电压调整电路16也改为调升钳位电压。因为第一取电时窗的钳位电压大于第二取电时窗的钳位电压,且第二取电时窗的钳位电压大于第三取电时窗的钳位电压,故局部放大图30、32及34显示第一取电时窗的充电速度大于第二取电时窗的充电速度,第二取电时窗的充电速度大于第三取电时窗的充电速度。

72.图4为本发明实施例中另一种供电电路4的电路示意图。供电电路4及供电电路1之间的差异在于取样反馈电路48。以下针对取样反馈电路48详细解释。取样反馈电路48包括取样电路480及模拟数字转换电路(analog-to-digitalconverter,adc)182。取样电路480耦接于储存电路cs,可依据比较电压vcmp对电源电能端n2的电压vdd取样而产生取样电压vs。模拟数字转换电路182耦接于取样电路480,可将取样电压vs转换为输出电压信号sc。图1及图4中的模拟数字转换电路182以相似方式运作,在此不再赘述。

73.在一些实施例中,取样电路480可于比较电压vcmp小于比较临界值一段第一延迟时间之后取样电源电能端n2的电压vdd以产生取样电压vs。比较临界值可为0v。当比较电压vcmp小于比较临界值时,第二放大电路m2导通,取样电路480可于第二放大电路m2导通且经过第一延迟时间之后,对电压vdd取样以产生取样电压vs。第一延迟时间可大于或等于0。例如,可选择非零的第二延迟时间以获得电压vdd的谷值作为取样电压vs。在另一些实施例中,取样电路480可于比较电压vcmp大于比较临界值一段第二延迟时间之后取样电源电能端n2的电压vdd以产生取样电压vs。当比较电压vcmp大于比较临界值时,第二放大电路m2截止,取样电路480可于第二放大电路m2截止且经过第二延迟时间之后,对电压vdd进行取样以产生取样电压vs。第二延迟时间可大于或等于0。当第一延迟时间为0时,取样电压vs可为电压vdd的峰值。

74.参考图3,在时间t4之后,分压vhv超出取电临界电压vref,比较电压vcmp大于比较临界值(0v),在比较电压vcmp大于比较临界值且经过第一延迟时间后(时间t5),取样反馈电路48会对电压vdd取样以产生取样电压vs(1),由于取样电压vs(1)及电压vdd的上限电压vdd-top之间的差值较小,输出电压信号sc的信号值会减小。在时间t6,时窗调整电路14会依据输出电压信号sc更新取电临界电压vref至较低值。在时间t8之后,分压vhv超出取电临界电压vref,比较电压vcmp大于比较临界值(0v),在比较电压vcmp大于比较临界值且经过

第一延迟时间后(时间t9),取样反馈电路48会依据电压vdd产生取样电压vs(2)。由于取样电压vs(1)及上限电压vdd-top的间之差值减小,输出电压信号sc的信号值会减小。在时间t10,时窗调整电路14会依据输出电压信号sc更新取电临界电压vref至更低值。在时间t12之后,分压vhv超出取电临界电压vref,比较电压vcmp大于比较临界值(0v),在比较电压vcmp大于比较临界值且经过第一延迟时间后(时间t13),取样反馈电路48会依据电压vdd产生取样电压vs(3)。由于电压vdd的取样电压vs(2)及上限电压vdd-top之间的差值增加,输出电压信号sc的信号值会增加。在时间t14,时窗调整电路14会依据输出电压信号sc更新取电临界电压vref至较高值。

75.由于取样反馈电路48在相对于时窗的预定时间点取得取样电压,无需等待一段时间后才产生平均电压vavg,反应速度较快,加速调整调整取电时窗及控制电压vg的钳位电压,使供电电路4将电压vdd维持在运作范围内,提高运作效率,同时降低电路面积。

76.图5为本发明实施例中一种电源供应器5的框图。电源供应器5包括供电电路50、脉冲宽度调制信号产生器52及功率开关54。供电电路50可由供电电路1或供电电路4实现,提供电压vdd至脉冲宽度调制信号产生器52。脉冲宽度调制信号产生器52可提供脉冲宽度调制信号spwm来控制功率开关54,脉冲宽度调制信号产生器52耦接于供电电路的电源电能端n2,可自电源电能端n2接收电能来维持脉冲宽度调制信号产生器52运作。响应所接收到的脉冲宽度调制信号spwm,功率开关54可选择性地导通或截止以进行电源转换,如此依据脉冲宽度调制信号spwm改变功率开关54导通的频率与工作周期(dutycycle),进而调控电源供应器5的输出电压vout。

77.电源供应器5采用供电电路1或供电电路4产生电压vdd,提高运作效率,同时降低电路面积。

78.本发明实施例还揭露一种充电控制方法,用以控制供电电路1。充电控制方法包括下列步骤:

79.步骤s1:时窗调整电路14依据该输出电压信号sc来调整该取电临界电压vref;

80.步骤s2:比较分压vhv以及取电临界电压vref,当分压vhv小于取电临界电压vref时,提供取电时窗;

81.步骤s3:在取电时窗中,开启充电电路12以输出充电电能来对储存电路充电cs,充电电能大小与控制电压vg大小为正相关;

82.步骤s4:依据电源电能端n2的电压vdd,自适应地调整控制电压vg;

83.步骤s5:依据电源电能端n2的电压vdd提供脉冲宽度调制信号spwm至功率开关54,使功率开关54选择性地导通或截止以进行电源转换,以调控输出电压vout;

84.步骤s6:输出输出电压vout以对负载供电。

85.在步骤s4中,当该电源电能端n2的电压vdd上升时,下降控制电压vg;而当电源电能端n2的电压vdd下降时,增大控制电压vg。充电控制方法调整取电时窗,将电压vdd维持在运作范围内,提高运作效率,同时降低电路面积。

86.以上所述仅为本发明的较佳实施例,凡依本发明权利要求范围所做的等同变化与修饰,皆应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1