用于总线接口装置的负电压保护的制作方法

用于总线接口装置的负电压保护

1.相关申请的交叉引用

2.本技术要求于2020年5月12日提交的美国临时申请第63/023,387号的权益,该美国临时申请的全部内容通过引用并入本文。

技术领域

3.本发明涉及用于诸如局域互联网络(lin)总线接口、时钟扩展外围设备接口(cxpi)总线接口等基于mosfet的总线接口的负电压保护,具体地,涉及用于总线的接口、包括所述接口的收发器和电池管理半导体管芯以及与总线接口的方法。

背景技术:

4.lin(局域互联网络)是用于车辆中的部件之间的通信的串行网络协议。lin总线是用于车载网络的单线双向总线。收发器或类似的装置提供微控制器与物理lin总线之间的接口。微控制器的逻辑值经由lin接口的

‘

txd’输入被驱动到lin总线上,其中在txd输入上传送的传输数据被转换为lin总线信号。lin接口还具有

‘

rxd’输出,该

‘

rxd’输出将信息从lin总线读回到微控制器。

5.根据lin规范1.2、1.3、2.0、2.1、2.2和2.2a,在lin总线上允许两种逻辑状态:显性和隐性。在显性状态中,lin总线上的电压被设置为接地电平或接近接地电平。在隐性状态中,lin总线上的电压被设置为电源电压。通过将lin接口的txd输入设置为逻辑低电平,该接口在其lin总线接口引脚上生成显性电平。lin接口的rxd输出读回lin总线上的信号并且使用逻辑低信号向微控制器指示显性lin总线信号。响应于微控制器将接口装置的txd引脚设置为逻辑高电平,该接口将其lin总线接口引脚设置为隐性电平。同时,由接口的rxd输出上的逻辑高电平指示lin总线上的隐性电平。

6.双极型晶体管广泛用于lin接口用于驱动lin总线。由于较高的成本,双极型晶体管已经随着时间的推移被较不昂贵的mosfet(金属氧化物场效应晶体管)器件——通常为高压pmos器件——取代。高压pmos器件需要保护以免受到出现在lin总线上的负电压的影响。lin总线上的电压可在

‑

40v至+45v的范围内。已经使用高压二极管来保护基于高压pmos的驱动器免受lin总线上的负电压的危害。然而,高压pmos器件遭受寄生pnp器件的导通的影响。lin规范对lin总线上的电压具有斜坡时间(slope time)要求,因此需要转换速率控制。存在于基于高压pmos的lin驱动器中的寄生pnp器件的导通阻碍了转换速率的控制并且增加了lin驱动器芯片(管芯)中的衬底噪声。

7.因此,需要用于基于mosfet的lin总线接口的改进的负电压保护。

技术实现要素:

8.根据用于总线的接口的实施方式,在该总线上,第一逻辑状态由较高电压电平传达并且第二逻辑状态由较低电压电平传达,该接口包括:输出级,该输出级包括:功率晶体管,该功率晶体管被配置成将较低电压电平驱动至总线上以传达第二逻辑状态;以及在功

率晶体管与总线之间的保护装置,该保护装置被配置成:在保护装置导通时将功率晶体管耦接至总线以及在保护装置关断时限制功率晶体管处的负电压偏移;以及控制电路,该控制电路被配置成:在总线电压高于较低电压电平时导通保护装置以及在总线电压处于较低电压电平或者低于较低电压电平时关断保护装置。

9.根据电池管理半导体管芯的实施方式,该电池管理半导体管芯包括:逻辑,该逻辑被配置成测量与对电池进行充电和/或放电相关联的一个或更多个参数;以及接口,该接口被配置成经由总线传送针对电池的测量结果,在该总线上,第一逻辑状态由较高电压电平传达并且第二逻辑状态由较低电压电平传达,其中该接口包括:输出级,该输出级包括:功率晶体管,该功率晶体管被配置成将较低电压电平驱动至总线上以传达第二逻辑状态;以及在功率晶体管与总线之间的保护装置,该保护装置被配置成:在保护装置导通时将功率晶体管耦接至总线以及在保护装置关断时限制功率晶体管处的负电压偏移;以及控制电路,该控制电路被配置成:在总线电压高于较低电压电平时导通保护装置以及在总线电压处于较低电压电平或者低于较低电压电平时关断保护装置。

10.根据与总线接口的方法的实施方式,在该总线上,第一逻辑状态由较高电压电平传达并且第二逻辑状态由较低电压电平传达,该方法包括:经由具有功率晶体管和保护装置的输出级将较低电压电平驱动至总线上以传达第二逻辑状态,其中,保护装置被配置成:在保护装置导通时将功率晶体管耦接至总线以及在保护装置关断时限制功率晶体管处的负电压偏移;以及控制保护装置的栅极端子处的电压,使得在总线电压高于较低电压电平时导通保护装置以及在总线电压处于较低电压电平或者低于较低电压电平时关断保护装置。

11.本领域技术人员在阅读以下详细描述以及在查看附图后将认识到其他特征和优点。

附图说明

12.附图中的元件不一定相对于彼此成比例。相似的附图标记指代对应类似的部件。各种示出的实施方式的特征可以进行结合,除非它们互相排斥。在附图中描绘了实施方式,并且在以下的描述中详细说明了实施方式。

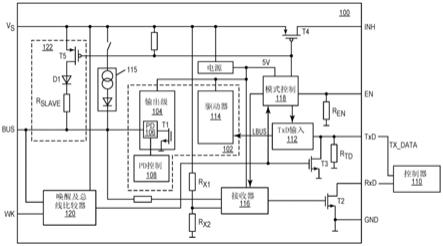

13.图1示出了局域互联网络(lin)收发器的实施方式的框图。

14.图2更详细地示出了lin收发器的接口的示意图。

15.图3示出了与图2中所示的lin接口的操作相关联的各种波形。

16.图4、图6、图8和图10示出了包括在lin接口中的控制电路的不同实施方式的示意图。

17.图5、图7、图9和图11分别示出了与图4、图6、图8和图10中所示的控制电路的操作相关联的波形。

18.图12示出了包括在控制电路中的电荷泵的实施方式的电路示意图。

19.图13示出了与图12中所示的电荷泵的操作相关联的各种波形。

20.图14至图17示出了控制电路的附加实施方式的示意图。

21.图18示出了包括在lin接口中的保护装置的实施方式的示意图。

22.图19示出了半导体衬底的部分截面,在半导体衬底中保护装置的p沟道晶体管器

件共享公共的本体区。

23.图20示出了包括lin接口的电池管理半导体管芯(芯片)的实施方式的框图。

具体实施方式

24.本文描述的实施方式提供了用于诸如局域互联网络(lin)总线接口、时钟扩展外围设备接口(cxpi)总线接口等基于mosfet的总线接口的负电压保护。基于mosfet的总线接口的输出(驱动器)级可以包括例如用于根据将要在总线上传达的逻辑状态来驱动总线的电压电平的pmos功率晶体管器件。例如,在lin规范1.2、1.3、2.0、2.1、2.2和2.2a的情况下,驱动到总线上的电压电平指示显性状态或隐性状态。保护装置在该保护装置导通时将输出级的功率晶体管耦接至总线并且在保护装置关断时限制功率晶体管处的负电压偏移。本文描述的负电压保护方案包括用于以在限制功率晶体管处的负电压偏移同时也避免了在保护装置内寄生器件导通的方式控制保护装置的导通/关断状态的控制电路。

25.接下来参照附图描述改进的负电压保护方案的示例性实施方式。在lin总线的背景下描述实施方式。然而,本文所描述的改进的负电压保护方案也可以应用于使得例如汽车车体控制应用(包括转向开关、ac和仪表板系统)中的电子控制单元(ecu)之间能够多路复用的其他汽车通信协议。例如,在以下实施方式中描述的接口、总线和收发器元件可以与cxpi协议兼容而不是与lin协议兼容。

26.图1示出了lin收发器100的实施方式。lin收发器100包括用于lin总线的接口102,在lin总线上,第一逻辑状态由较高电压电平传达,并且第二逻辑状态由较低电压电平传达。在一个实施方式中,接口102与lin规范1.2、1.3、2.0、2.1、2.2和2.2a兼容,第一逻辑状态对应于lin规范1.2、1.3、2.0、2.1、2.2和2.2a中定义的隐性状态,以及第二逻辑状态对应于lin规范1.2、1.3、2.0、2.1、2.2和2.2a中定义的显性状态。

27.无论lin总线的具体类型如何,lin接口102包括输出级104,该输出级104具有用于驱动lin总线的功率晶体管t1和在功率晶体管t1与lin总线之间的保护装置

‘

pd’106。功率晶体管t1将较高电压电平驱动至lin总线上以传达第一逻辑状态,并且将较低电压电平驱动至lin总线上以传达第二逻辑状态。

28.保护装置106在该保护装置106导通时将功率晶体管t1耦接至lin总线以及在保护装置106关断时限制功率晶体管t1处的负电压偏移。lin接口102还包括控制电路108,该控制电路108用于:在lin总线电压高于较低电压电平时导通保护装置106以及在lin总线电压处于较低电压电平或者低于较低电压电平时关断保护装置106。

29.图1中所示的lin收发器100还包括lin总线引脚

‘

bus’,该lin总线引脚

‘

bus’耦接至lin接口102的输出级104。lin总线引脚bus用于将lin收发器100耦接至lin总线。lin收发器100的传输数据输入引脚

‘

txd’用于接收来自诸如微控制器的控制器110的传输数据流

‘

tx_data’。lin收发器100的传输数据输入电路112将接收到的传输数据流转换为lin总线信号

‘

lbus’,该lin总线信号

‘

lbus’被提供至lin接口102的驱动器电路114。在lin规范1.2、1.3、2.0、2.1、2.2和2.2a的情况下,集成下拉器件r

td

确保接收到的传输数据流在显性状态下为逻辑低。lin收发器100还具有接地引脚

‘

gnd’和用于提供电源电压vsup(例如,电池电压)的电源输入引脚

‘

vs’。内部终端和上拉电流源110可以将电源输入引脚vs耦接至lin总线引脚bus。

30.lin收发器的接收电路116从lin总线读回lin总线信号,并且基于lin总线信号的电压电平指示lin总线的逻辑状态。接收电路116通过上拉电路r

x1

、r

x2

耦接至电源输入引脚vs。lin收发器100的接收数据输出引脚

‘

rxd’将如由接收电路116指示的lin总线的逻辑状态经由驱动器器件t2传送至控制器110,该驱动器器件t2将接收到的数据流

‘

rx_data’传输至控制器110。

31.lin收发器100还可以具有用于接收使能信号的使能输入引脚

‘

en’。耦接至使能输入引脚en的可以是集成下拉器件r

en

和电路118,该电路118用于当在使能输入引脚en处接收到的信号有效(例如,逻辑高)时将lin收发器100设置为正常操作模式。在正常操作模式中,来自控制器112的数据经由txd引脚被传输至lin总线,并且接收器116检测lin总线上的数据流并将检测到的数据转发至rxd输出引脚。

32.lin收发器100还可以具有与lin总线的状态有关的唤醒输入引脚

‘

wk’,该唤醒输入引脚可以用于将lin收发器100置于待机模式,在待机模式下,不允许lin总线上的通信。lin收发器100可以包括:比较器电路120,其用于监测唤醒输入引脚wk的状态和lin总线以确定何时将lin收发器100置于待机模式;以及上拉器件t3,其用于将传输数据输入引脚txd牵拉到电源输入引脚vs以指示第一逻辑状态(例如,如lin规范1.2、1.3、2.0、2.1、2.2和2.2a中所定义的隐性状态)。

33.lin收发器100还可以具有作为与电源有关的输出的禁止输出引脚

‘

inh’。禁止输出引脚inh可以用于当lin收发器100在主模式中使用时控制外部电压调节器或者控制外部总线终端电阻器。禁止输出引脚inh通过功率器件t4耦接至电源输入vs。lin收发器100还可以包括用于将lin收发器100置于从属模式的电路122。可以通过例如经由开关器件t5连接lin总线引脚bus与电源输入引脚vs或禁止输出引脚inh之间的电阻r

slave

和反向二极管d1来将lin收发器100置于主模式。然而,在lin收发器100中还可以包括其他附加的电路。

34.图2更详细地示出了lin接口102。根据本实施方式,lin收发器100的电源输入引脚vs通过例如一对串联连接的反向二极管da、db和电阻器ra、rb连接至lin总线引脚bus。lin接口102的控制电路108在lin总线电压

‘

vlin’低于针对较低电压电平的最大允许值且高于0v时关断保护装置106并且在高于该电压条件时导通保护装置106。在一个实施方式中,例如,如lin规范1.2、1.3、2.0、2.1、2.2和2.2a中所规定的,针对较低电压电平的最大允许值为如图3所示的1.2v。

35.在图2中,保护装置106被示出为p沟道晶体管器件pm1,该p沟道晶体管器件pm1具有耦接至lin总线引脚bus的漏极端子

‘

d’和耦接至驱动lin总线的功率晶体管t1的源极端子

‘

s’。对于p沟道器件,源极区和漏极区是p掺杂的,并且本体区是n掺杂的。本体区

‘

bg’处于衬底电位

‘

vsub’,该衬底电位

‘

vsub’可以处于与接地参考端子

‘

vssl’相同的电位。当p沟道晶体管保护器件pm1由控制电路108导通时,驱动器电流

‘

idrv’从pm1的漏极d流向源极s,并且在功率晶体管t1的漏极端子d处出现电压vdi。

36.当由lin收发器100的传输数据输入电路114提供的lin总线信号lbus从逻辑高电平转变为逻辑低电平时,lin总线电压vlin从第一逻辑状态转变为第二逻辑状态但是以受控的转换速率转变。当lin总线信号lbus从逻辑低电平转变为逻辑高电平时,lin总线电压vlin从第二逻辑状态转变为第一逻辑状态同样以受控的转换速率转变。图2通过右上方的vlin波形中的虚斜线指示了高到低转换速率以及低到高转换速率。lin接口102的控制电路

108通过避免p沟道晶体管器件pm1内的寄生导通来确保保护装置106不会不利地影响转换速率控制。

37.为此,并且对于图2中所示的p沟道晶体管保护器件pm1的实施方式,控制电路108驱动p沟道晶体管器件pm1的栅极端子

‘

g’趋向0v,以使lin总线从第一逻辑状态转变为第二逻辑状态,其中对于图2中所示的实施方式,p沟道晶体管器件pm1的栅极端子g处的电压

‘

vg1’确定针对lin总线的较低电压电平。对于lin规范1.2、1.3、2.0、2.1、2.2和2.2a,这意味着控制电路108针对lin总线电压处于0v或接近0v而关断p沟道晶体管保护器件pm1。例如,如图3所示,控制电路108可以在0v与允许lin总线处于显性状态的最大电压

‘

vmax’之间关断p沟道晶体管保护器件pm1。通过以这样的方式控制保护装置106,避免了在p沟道晶体管保护器件pm1内寄生导通,同时也限制了功率晶体管t1处的负电压偏移。

38.图4更详细地示出了lin接口102的控制电路108。根据本实施方式,控制电路108包括串联连接的第一p沟道晶体管器件pm2和第二p沟道晶体管器件pm3,第一p沟道晶体管器件pm2和第二p沟道晶体管器件pm3与功率晶体管t1并联耦接。p沟道晶体管器件pm2的源极端子s和本体区bg耦接至保护装置106。p沟道晶体管器件pm2的漏极端子d和栅极端子g耦接至p沟道晶体管器件pm3的源极端子s。p沟道晶体管器件pm3的本体区bg耦接至保护装置106。p沟道晶体管器件pm3的栅极端子g耦接至p沟道晶体管器件pm3的漏极端子d并且耦接至保护装置106的栅极端子g。控制电路108还包括串联连接在p沟道晶体管器件pm3的漏极端子d与接地参考端子vssl之间的电阻器r1。在lin规范1.2、1.3、2.0、2.1、2.2和2.2a的情况下,电阻器r1可以在兆欧姆的范围内。

39.根据图4的实施方式,第二逻辑状态的电压电平由p沟道晶体管保护器件pm1的阈值电压

‘

vthp1’确定。在lin规范1.2、1.3、2.0、2.1、2.2和2.2a的情况下,这意味着:取决于vthp1的变化的量,可能无法满足由lin规范对于显性状态所需的1.2v最大电平vmax。这在图5中被示出,图5示出了lin总线电压vlin与p沟道晶体管保护器件pm1的栅极电压vg1之间的差。该差对应于p沟道晶体管保护器件pm1的栅源电压

‘

vgs1’,该栅源电压

‘

vgs1’由下式给出:

40.vgs1=vthp2+vthp3>vthp1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

41.其中,vthp2是p沟道晶体管器件pm2的阈值电压,以及vthp3是p沟道晶体管器件pm3的阈值电压。

42.图6示出了lin接口102的控制电路108的另一个实施方式。图6中所示的实施方式与图4中所示的实施方式类似。然而,不同的是,控制电路108还包括串联耦接在p沟道晶体管器件pm3与接地参考端子vssl之间的第一n沟道晶体管器件nm1。对于n沟道器件,源极和漏极是n掺杂的并且本体是p掺杂的。在图6中,n沟道晶体管器件nm1的源极端子s和本体区bg耦接至接地参考端子vssl。n沟道晶体管器件nm1的漏极端子d例如通过电阻器r1耦接至p沟道晶体管器件pm3的漏极端子d。n沟道晶体管器件nm1的栅极端子g耦接至n沟道晶体管器件nm1的漏极端子d。当lin总线电压vlin下降到低于n沟道晶体管器件nm1的阈值电压

‘

vthn1’时,n沟道晶体管器件nm1关断。在lin总线电压vlin下降到低于p沟道晶体管保护器件pm1的阈值电压vthp1减去n沟道晶体管器件nm1的本体二极管bd1的正向电压

‘

vfn1’时,控制电路108关断保护装置106。

43.如图7所示,当lin总线电压vlin下降到低于n沟道晶体管器件nm1的阈值电压

vthn1时,n沟道晶体管器件nm1关断。当这个条件出现时,p沟道晶体管器件pm2和p沟道晶体管器件pm3两者也都关断。相应地,可以通过p沟道晶体管保护器件pm1的栅极电容将p沟道晶体管保护器件pm1的栅极电压vg1减小到

‑

vfn1。在lin规范1.2、1.3、2.0、2.1、2.2和2.2a的情况下,这意味着用于显性状态的电压电平维持在1.2v的最大值以下,其中具有足够的余量。

44.图8示出了lin接口102的控制电路108的另一个实施方式。图8中所示的实施方式与图6中所示的实施方式类似。然而,不同的是,控制电路108还包括与n沟道晶体管器件nm1并联耦接的电荷泵200。电荷泵200是提供电流

‘

icp’的电流源,当lin总线处于第二逻辑状态时,该电流

‘

icp’维持保护装置106的栅极端子g处的负电压,如图9所示。在lin规范1.2、1.3、2.0、2.1、2.2和2.2a的情况下,电荷泵200在显性状态下激活以根据lin规范的dc规范保持p沟道晶体管保护器件pm1的栅极端子g处的负电压

‑

vg1。

45.图10示出了lin接口102的控制电路108的另一个实施方式。图8中所示的实施方式与图6中所示的实施方式类似。然而,不同的是,控制电路108还包括串联耦接在n沟道晶体管器件nm1与接地参考端子vssl之间的第二n沟道晶体管器件nm2。n沟道晶体管器件nm1的源极端子s耦接至n沟道晶体管器件nm2的漏极端子d。n沟道晶体管器件nm1的漏极端子d和栅极端子g耦接至p沟道晶体管器件pm3的漏极端子d。第二n沟道晶体管器件nm2的源极端子s和本体区bg两者以及n沟道晶体管器件nm1的本体区bg都耦接至接地参考端子vssl。当lin总线处于第一逻辑状态时,n沟道晶体管器件nm2被配置成关断。在一个实施方式中,n沟道晶体管器件nm2的栅极端子g由lin总线的逻辑状态控制,使得当lin总线处于第一逻辑状态时,n沟道晶体管器件nm2关断。

46.例如,由lin收发器100的传输数据输入电路114提供的lin总线信号lbus可以被反转300。反转后的信号驱动n沟道晶体管器件nm2的栅极端子g。相应地,当lin总线处于第一逻辑状态时,n沟道晶体管器件nm2关断。在lin规范1.2、1.3、2.0、2.1、2.2和2.2a的情况下,这意味着n沟道晶体管器件nm2在隐性状态下关断。lin规范1.2、1.3、2.0、2.1、2.2和2.2a要求当输出级104和驱动器114关断时为20μa的最大电流消耗。当lin总线处于隐性状态时关断n沟道晶体管器件nm2减小了lin总线引脚bus处的电流消耗i

bus_pas_rec

并且因此有助于满足lin规范1.2、1.3、2.0、2.1、2.2和2.2a。

47.反转后的lbus信号还形成了用于与串联连接的n沟道晶体管器件nm1、nm2并联耦接的电荷泵200的电荷泵使能信号en_cp。如之前结合图8所说明的,当lin总线处于第二逻辑状态时,电荷泵200维持在保护装置106的栅极端子g处的负电压。在图9中,当lin总线信号lbus为用于指示第一逻辑状态(例如,lin规范1.2、1.3、2.0、2.1、2.2和2.2a中的隐性状态)的逻辑高时,电荷泵使能信号en_cp为逻辑低,并且从而禁用电荷泵200。当lin总线信号lbus为用于指示第二逻辑状态(例如,lin规范1.2、1.3、2.0、2.1、2.2和2.2a中的显性状态)的逻辑低时,电荷泵使能信号en_cp为逻辑高,并且从而启用电荷泵200。

48.图12示出了电荷泵200的实施方式。根据本实施方式,电荷泵200具有耦接至电源电压vddd的p沟道晶体管器件pmcp1和通过电阻器rcp1耦接至p沟道晶体管器件pmcp1的n沟道晶体管器件nmcp1。两个附加的n沟道晶体管器件nmcp2、nmcp3通过电容器ccp1耦接至节点

‘

vcp’。电荷泵使能信号en_cp和节点vcp处的缓冲信号被输入至逻辑与(and)门400。逻辑与门400的反转后的输出通过电阻器rcp2耦接至第四n沟道晶体管器件nmcp4的漏极。n沟道

晶体管器件nmcp4的栅极耦接至逻辑与门400的非反转的输出。逻辑与门400的反转后的输出被再次反转,以形成触发信号

‘

vtrig’,该触发信号

‘

vtrig’耦接至p沟道晶体管器件pmcp1的栅极和n沟道晶体管器件nmcp1的栅极。触发信号vtrig的反转后的版本驱动n沟道晶体管器件nmcp2的栅极并且再次被反转以驱动n沟道晶体管器件nmcp3的栅极。n沟道晶体管器件nmcp3的源极形成充电节点

‘

cp’,该充电节点

‘

cp’如图8和图10所示耦接至n沟道晶体管器件nm1的漏极端子。

49.图13示出了在电荷泵200的不同节点处的各种电流(i)和电压(v)波形。如图13上部的第二个波形所示,触发信号vtrig基于晶体管器件pmcp1、nmcp1、nmcp2和nmcp3的导通/关断状态控制电荷泵200的充电/放电状态。

50.图14示出了lin接口102的控制电路108的另一个实施方式。图14中所示的实施方式与图4中所示的实施方式类似。然而,不同的是,控制电路108包括串联连接在p沟道晶体管器件pm3的漏极端子d与接地参考端子vssl之间的电流源500而不是电阻器r1。

51.图15示出了lin接口102的控制电路108的另一个实施方式。图15中所示的实施方式与图6中所示的实施方式类似。然而,不同的是,控制电路108包括附加的n沟道晶体管器件nm3和耦接至n沟道晶体管器件nm3的漏极端子d的电流源600。n沟道晶体管器件nm3的源极端子s和本体区bg两者都耦接至接地参考端子vssl。n沟道晶体管器件nm3的栅极端子g均耦接至n沟道晶体管器件nm3的漏极端子d并且耦接至n沟道晶体管器件nm1的栅极端子g。

52.图16示出了lin接口102的控制电路108的另一个实施方式。图16中所示的实施方式与图15中所示的实施方式类似。然而,不同的是,控制电路108还包括与n沟道晶体管器件nm1并联耦接的电荷泵200。如结合图8和图10所说明的,当lin总线处于第二逻辑状态时,电荷泵200维持保护装置106的栅极端子g处的负电压。

53.图17示出了lin接口102的控制电路108的另一个实施方式。图17中所示的实施方式与图16中所示的实施方式类似。然而,不同的是,控制电路108还包括串联耦接在n沟道晶体管器件nm1与p沟道晶体管器件pm3之间的附加的n沟道晶体管器件nm2。当lin总线处于第一逻辑状态时,n沟道晶体管器件nm2关断。

54.图18示出了lin接口102的保护装置106的另一个实施方式。根据本实施方式,保护装置106包括与另一p沟道晶体管器件pm4单片集成的p沟道晶体管器件pm1,使得p沟道晶体管器件pm1、pm4共享公共的本体区。p沟道晶体管器件pm1的源极端子s耦接至功率晶体管t1。p沟道晶体管器件pm1的漏极端子d和p沟道晶体管器件pm4的漏极端子耦接至lin总线引脚bus。p沟道晶体管器件pm4的源极端子s耦接至公共的本体区。p沟道晶体管器件pm1的栅极端子g和p沟道晶体管器件pm4的栅极端子耦接至控制电路108,并且p沟道晶体管器件pm1的栅极端子g和p沟道晶体管器件pm4的栅极端子两者具有相同的栅极电压vg1。

55.图19示出了半导体衬底700的部分截面,在半导体衬底700中,保护装置106的p沟道晶体管器件pm1、pm4共享公共的本体区702。半导体衬底700为p型掺杂,公共的本体区702为n型掺杂,并且p沟道晶体管器件pm1、pm4的源极区和漏极区704为p型掺杂。根据本实施方式,即使p沟道晶体管器件pm4的本体区bg/702浮动,图19中所示的寄生pnp器件也不会被激活。在这种情况下,通过控制p沟道晶体管器件pm1的栅极端子g和p沟道晶体管器件pm4的栅极端子g来提高用于第二逻辑状态(例如,lin规范1.2、1.3、2.0、2.1、2.2和2.2a中的显性状态)的电压电平。

56.图20示出了包括本文描述的lin接口102的电池管理半导体管芯800(芯片)的实施方式。电池管理半导体管芯800还包括逻辑802例如模拟和/或数字电路,该逻辑802用于测量与对电池804进行充电和/或放电相关联的一个或更多个参数,电池804向一个或更多个电力负载806供电。例如,测量逻辑802可以包括一个或更多个电流传感器、电压传感器、温度传感器等。lin接口102经由lin总线810将电池804的测量结果传送至电子控制单元(ecu)808(例如,微控制器),在lin总线810上,第一逻辑状态由较高电压电平传达并且第二逻辑状态由较低电压电平传达。如本文之前所说明的,lin接口102包括输出级104,该输出级104具有用于将较低电压电平驱动至lin总线810上以传达第二逻辑状态的功率晶体管t1(图20中未示出)以及在功率晶体管t1与lin总线810之间的保护装置106(图20中未示出)。保护装置106在保护装置106导通时将功率晶体管t1耦接至lin总线810以及在保护装置106关断时限制功率晶体管t2处的负电压偏移。lin接口102还包括控制电路108(图20中未示出),控制电路108在lin总线电压高于较低电压电平时导通保护装置106,以及在lin总线电压处于较低电压电平或者低于较低电压电平时关断保护装置106。

57.如本文之前所说明的,改进的负电压保护方案可以应用于除了lin以外的汽车通信协议。例如,在先前的实施方式中所描述的接口、总线和收发器元件可以与cxpi协议兼容而不是与lin协议兼容。

58.尽管本公开内容没有如此限制,但是以下编号的示例表明了本公开内容的一个或更多个方面。

59.示例1.一种用于总线的接口,在总线上,第一逻辑状态由较高电压电平传达并且第二逻辑状态由较低电压电平传达,所述接口包括:输出级,所述输出级包括:功率晶体管,所述功率晶体管被配置成将所述较低电压电平驱动至所述总线上以传达所述第二逻辑状态;以及在所述功率晶体管与所述总线之间的保护装置,所述保护装置被配置成:在所述保护装置导通时将所述功率晶体管耦接至所述总线以及在所述保护装置关断时限制所述功率晶体管处的负电压偏移;以及控制电路,所述控制电路被配置成:在所述总线电压高于所述较低电压电平时导通所述保护装置以及在所述总线电压处于所述较低电压电平或者低于所述较低电压电平时关断所述保护装置。

60.示例2.根据示例1所述的接口,其中,所述控制电路被配置成:在所述总线电压低于针对所述较低电压电平的最大允许值且高于0v时关断所述保护装置。

61.示例3.根据示例1或2所述的接口,其中,所述控制电路被配置成:驱动所述保护装置的栅极端子趋向0v,以使所述总线从所述第一逻辑状态转变为所述第二逻辑状态,并且其中,所述保护装置的栅极端子处的电压确定用于所述总线的所述较低电压电平。

62.示例4.根据示例1至3中任一项所述的接口,其中,所述控制电路包括串联连接的第一p沟道晶体管器件和第二p沟道晶体管器件,所述第一p沟道晶体管器件和所述第二p沟道晶体管器件与所述功率晶体管并联耦接。

63.示例5.根据示例4所述的接口,其中:所述第一p沟道晶体管器件的源极端子和本体区耦接至所述保护装置;所述第一p沟道晶体管器件的漏极端子和栅极端子耦接至所述第二p沟道晶体管器件的源极端子;所述第二p沟道晶体管器件的本体区耦接至所述保护装置;以及所述第二p沟道晶体管器件的栅极端子耦接至所述第二p沟道晶体管器件的漏极端子并且耦接至所述保护装置的栅极端子。

64.示例6.根据示例4或5所述的接口,其中:所述控制电路还包括串联耦接在所述第二p沟道晶体管器件与接地之间的第一n沟道晶体管器件;所述第一n沟道晶体管器件被配置成:在所述总线电压下降到低于所述第一n沟道晶体管器件的阈值电压时关断;以及所述控制电路被配置成:在所述总线电压下降到低于所述保护装置的阈值电压减去所述第一n沟道晶体管器件的本体二极管的正向电压时关断所述保护装置。

65.示例7.根据示例6所述的接口,其中:所述第一n沟道晶体管器件的源极端子和本体区耦接至接地;所述第一n沟道晶体管器件的漏极端子耦接至所述第二p沟道晶体管器件的漏极端子;以及所述第一n沟道晶体管器件的栅极端子耦接至所述第一n沟道晶体管器件的漏极端子。

66.示例8.根据示例6或7所述的接口,其中:所述控制电路还包括与所述第一n沟道晶体管器件并联耦接的电荷泵;并且所述电荷泵被配置成:当所述总线处于所述第二逻辑状态时,维持所述保护装置的栅极端子处的负电压。

67.示例9.根据示例6至8中任一项所述的接口,其中:所述控制电路还包括串联耦接在所述第一n沟道晶体管器件与接地之间的第二n沟道晶体管器件;所述第二n沟道晶体管器件被配置成:在所述总线处于所述第一逻辑状态时关断。

68.示例10.根据示例9所述的接口,其中:所述第一n沟道晶体管器件的源极端子耦接至所述第二n沟道晶体管器件的漏极端子;所述第一n沟道晶体管器件的漏极端子和栅极端子耦接至所述第二p沟道晶体管器件的漏极端子;所述第二n沟道晶体管器件的源极端子和本体区两者以及所述第一n沟道晶体管器件的本体区耦接至接地;以及所述第二n沟道晶体管器件的栅极端子受所述总线的逻辑状态控制,使得在所述总线处于所述第一逻辑状态时所述第二n沟道晶体管器件关断。

69.示例11.根据示例9或10所述的接口,其中:所述控制电路还包括与所述串联连接的第一n沟道晶体管器件和第二n沟道晶体管器件并联耦接的电荷泵;并且所述电荷泵被配置成:在所述总线处于所述第二逻辑状态时,维持所述保护装置的栅极端子处的负电压。

70.示例12.根据示例6至11中任一项所述的接口,其中,所述控制电路还包括串联连接在所述第二p沟道晶体管器件的漏极端子与所述第一n沟道晶体管器件的漏极端子之间的电阻器。

71.示例13.根据示例6至12中任一项所述的接口,其中,所述控制电路还包括第二n沟道晶体管器件和耦接至所述第二n沟道晶体管器件的漏极端子的电流源。

72.示例14.根据示例13所述的接口,其中:所述第二n沟道晶体管器件的源极端子和本体区两者都耦接至接地;以及所述第二n沟道晶体管器件的栅极端子耦接至所述第二n沟道晶体管器件的漏极端子和所述第一n沟道晶体管器件的栅极端子两者。

73.示例15.根据示例13或14所述的接口,其中:所述控制电路还包括与所述第一n沟道晶体管器件并联耦接的电荷泵;并且所述电荷泵被配置为:在所述总线处于所述第二逻辑状态时,维持所述保护装置的栅极端子处的负电压。

74.示例16.根据示例15所述的接口,其中:所述控制电路还包括串联耦接在所述第一n沟道晶体管器件与所述第二p沟道晶体管器件之间的第三n沟道晶体管器件;并且所述第三n沟道晶体管器件被配置成:在所述总线处于所述第一逻辑状态时关断。

75.示例17.根据示例4至16中任一项所述的接口,其中,所述控制电路还包括串联连

接在所述第二p沟道晶体管器件的漏极端子与接地之间的电流源。

76.示例18.根据示例1至17中任一项所述的接口,其中:所述保护装置包括p沟道晶体管器件,所述p沟道晶体管器件具有耦接至所述总线的漏极端子和耦接至所述功率晶体管的源极端子;所述控制电路被配置成:驱动所述p沟道晶体管器件的栅极端子趋向0v,以使所述总线从所述第一逻辑状态转变为所述第二逻辑状态;以及其中,所述p沟道晶体管器件的栅极端子处的电压确定用于所述总线的所述较低电压电平。

77.示例19.根据示例1至18中任一项所述的接口,其中:所述保护装置包括与第二p沟道晶体管器件单片集成的第一p沟道晶体管器件,使得所述第一p沟道晶体管器件和所述第二p沟道晶体管器件共享公共的本体区;所述第一p沟道晶体管器件的源极端子耦接至所述功率晶体管;所述第一p沟道晶体管器件的漏极端子和所述第二p沟道晶体管器件的漏极端子耦接至所述总线;所述第二p沟道晶体管器件的源极端子耦接至所述公共的本体区;以及所述第一p沟道晶体管器件的栅极端子和所述第二p沟道晶体管器件的栅极端子耦接至所述控制电路。

78.示例20.根据示例1至19中任一项所述的接口,其中,所述总线是局域互联网络(lin)总线。

79.示例21.根据示例1至19中任一项所述的接口,其中,所述总线是时钟扩展外围设备接口(cxpi)总线。

80.示例22.一种收发器,所述收发器包括根据示例1至21中任一项所述的接口,所述收发器还包括:第一引脚,所述第一引脚耦接至输出级并且被配置成耦接至总线;第二引脚,所述第二引脚被配置成从控制器接收传输数据流;传输电路,所述传输电路被配置成将接收到的传输数据流转换为提供至所述接口的总线信号;接收电路,所述接收电路被配置成从所述总线读回总线信号,并且基于所述总线信号的电压电平指示所述总线的逻辑状态;以及第三引脚,所述第三引脚被配置成将由所述接收电路指示的所述总线的逻辑状态传送至所述控制器。

81.示例23.一种电池管理半导体管芯,包括:逻辑,所述逻辑被配置成测量与对电池进行充电和/或放电相关联的一个或更多个参数;以及接口,所述接口被配置成经由总线传送针对所述电池的测量结果,在所述总线上,第一逻辑状态由较高电压电平传达并且第二逻辑状态由较低电压电平传达,其中所述接口包括:输出级,所述输出级包括:功率晶体管,所述功率晶体管被配置成将所述较低电压电平驱动到所述总线上以传达所述第二逻辑状态;以及在所述功率晶体管与所述总线之间的保护装置,所述保护装置被配置成:在所述保护装置导通时将所述功率晶体管耦接至所述总线以及在所述保护装置关断时限制所述功率晶体管处的负电压偏移;以及控制电路,所述控制电路被配置成:在所述总线电压高于所述较低电压电平时导通所述保护装置以及在所述总线电压处于所述较低电压电平或者低于所述较低电压电平时关断所述保护装置。

82.示例24.一种与总线接口的方法,在所述总线上,第一逻辑状态由较高电压电平传达并且第二逻辑状态由较低电压电平传达,所述方法包括:经由具有功率晶体管和保护装置的输出级将所述较低电压电平驱动至所述总线上以传达所述第二逻辑状态,其中,所述保护装置被配置成:在所述保护装置导通时将所述功率晶体管耦接至所述总线以及在所述保护装置关断时限制所述功率晶体管处的负电压偏移;以及控制所述保护装置的栅极端子

处的电压,使得在所述总线电压高于所述较低电压电平时所述保护装置导通以及在所述总线电压处于所述较低电压电平或者低于所述较低电压电平时所述保护装置关断。

83.使用诸如“第一”、“第二”等的术语来描述各种元件、区域、部分等,并且术语也不旨在是限制性的。在整个说明书中,相似的术语指代相似的元件。

84.如本文所使用的,术语“具有”、“含有”、“包含(including)”、“包括(comprising)”等为开放性术语,所述术语指示所陈述元件或特征的存在,但是不排除附加的元件或特征。除非上下文另外明确指出,否则冠词“一个”、“一种”和“该”旨在包括复数和单数。

85.应当理解,除非另外特别指出,否则本文描述的各种实施方式的特征可以彼此进行组合。

86.尽管本文已经图示和描述了特定实施方式,但是本领域普通技术人员将理解,在不脱离本发明的范围的情况下,可以用各种替选和/或等同的实现方式代替所示和所描述的特定实施方式。本技术旨在覆盖本文所讨论的特定实施方式的任何修改或变型。因此,本发明旨在仅受权利要求及其等同方案限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1