一种COT并联电路以及电源设备的制作方法

一种cot并联电路以及电源设备

技术领域

1.本技术实施例涉及电路领域,尤其涉及一种恒定导通时间控制(constant on time control,cot)并联电路以及电源设备。

背景技术:

2.随着电子产品集成度的提升,嵌入式高性能电路系统要求电源设备在输出高电流的同时,供电电源的输出电压能够快速响应负载的跳变。cot能够快速响应负载跳变,保持输出电压稳定,满足负载跳变需求。通过多路cot并联能够提高电源设备的电流输出能力。

3.目前,cot多相并联电路输出信号的过程中,首先需要构造一个连续的ramp信号。cot多相并联电路中包括的控制器可以根据每个ramp信号的周期产生一个脉冲信号。接收到脉冲信号的开关组件依次输出功率信号。随着开关组件输出功率信号的频率提高,构造连续ramp信号的频率也需要随之提高。例如,若单个开关组件的工作频率为8mhz,对于一个4相cot并联电路来说,连续ramp信号的频率为32mhz;对于一个6相cot并联电路来说,连续ramp的频率为48mhz。开关组件工作的频率提升时,连续ramp的频率也需要随之提升。

4.连续ramp通常由信号发生器产生,然而,采用bcd工艺生产的信号发生器存在固有延迟,构造高频ramp信号的难度较大,难以产生更高频率的连续ramp,进而,限制了cot多相并联电路输出功率信号的频率,即限制了电源设备输出功率信号的频率。

技术实现要素:

5.本技术提供了一种cot并联电路以及电源设备,降低了高频cot多相并联的实现难度。

6.本技术第一方面提供了一种恒定导通时间控制cot并联电路,包括:第一相变器、第二相变器、多项控制器和滤波模块;所述第一相变器的输出端与所述多项控制器的输入端和所述滤波模块的第一输入端电连接;所述第二相变器的输入端与所述多项控制器的输出端电连接,所述第二相变器的输出端与所述滤波模块的第二输入端电连接;所述多项控制器用于:在所述cot并联电路接收到的ramp信号的一个周期内,根据所述第一相变器输出的第一功率信号控制所述第二相变器输出第二功率信号。

7.本技术中,电源设备中包括的cot多项并联电路接收第一相变器输出的第一功率信号后,可以向第二相变器输出第一脉冲信号,第一脉冲信号用于指示第二相变器输出第二功率信号。进而,cot多项并联电路可以在ramp信号的一个周期内输出多个功率信号,无需提升ramp信号的频率便可输出高频功率信号,降低了高频cot多相并联的实现难度。

8.在上述第一方面的一种可能的实现方式中,所述多项控制器包括分频器、第一反相器、第一周期控制模块、第二周期控制模块以及第一或门;所述分频器的输入端与所述第一相变器的输出端电连接,所述分频器的输出端通过第一连接点与所述第一周期控制模块的输入端和所述第一反相器的输入端电连接;所述第一反相器的输出端与所述第二周期控制模块的输入端电连接;所述第一或门的输入端与所述第一周期控制模块的输出端和所述

第二周期控制模块的输出端电连接;所述第一周期控制模块和所述第二周期控制模块用于:通过多个电容和多个恒流源构成的时间采集电路采集第一相变换器输出第一功率信号的输出周期,根据所述输出周期输出目标信号;所述第一或门用于:根据所述第一周期控制模块或所第二周期控制模块输出的所述目标信号输出第一脉冲信号,所述第一脉冲信号用于指示所述第二相变器输出所述第二功率信号。

9.该种可能的实现方式中,多项控制器通过第一周期模块和第二周期模块采集第一功率信号的输出周期,根据第一功率信号的输出周期规划目标信号的输出时间,进而输出目标信号。第一或门根据第一周期控制模块或者第二周期控制模块输出的目标信号来输出第一脉冲信号。该种可能的实现方式提供了一种多项控制器根据第一功率信号控制第二相变器输出第二功率信号的具体实现方式,提升了方案的可实现性。

10.在上述第一方面的一种可能的实现方式中,所述第一周期控制模块包括第二反相器、恒流源模块、第一开关模块、第二开关模块、电容模块和第一比较器,所述电容模块包括第一电容和第二电容;所述第二反相器的第一端与所述分频器的输出端电连接,所述第二反相器的第二端与所述第二开关模块的第一端电连接;所述第一开关模块的第一端与所述分频器的输出端电连接,所述第一开关模块的第二端与所述恒流源模块的第一端电连接,所述第一开关模块的第三端与所述电容模块的第一端电连接;所述第二开关模块的第二端与所述恒流源模块的第二端电连接,所述第二开关模块的第三端接地;所述电容模块的第三端接地;所述第一比较器的负极输入端通过第二连接点与所述第一开关模块和所述第一电容电连接,所述第一比较器的正极输入端通过第三连接点与所述第一开关模块和所述第二电容电连接;所述第一开关模块用于:根据所述分频器输出的不同信号来控制所述恒流源模块向所述电容模块中的第一电容和第二电容充电的时间,所述恒流源模块向所述电容模块中的第一电容和第二电容充电的时间与所述第一功率信号的输出周期相同;所述第二开关模块用于:根据所述第二反相器输出的信号控制所述第一电容放电;所述第一比较器用于:当所述第一电容放电时,确认所述第一电容的电压值小于所述第二电容的电压值时输出所述目标信号。

11.该种可能的实现方式中,第一开关模块可以根据分频器输出的不同信号来控制恒流源模块向电容模块中的第一电容和第二电容充电的时间,分频器输出高电平信号时,第一开关模块接收到高电平信号,控制开关闭合,以便恒流源模块可以通过闭合的开关向第一电容和第二电容充电,充电的时间与第一相变器输出第一功率信号的周期相同。这样,第一开关模块便完成了对于第一功率信号周期的采集。分频器输出低电平信号时,第一开关模块接收到低电平信号,控制开关断开,恒流源模块停止向第一开关模块充电。第二反相器接收到分频器输出的低电平信号,将低电平信号转化为高电平信号后向第二开关模块输出,第二开关模块接收到高电平信号后控制位于恒流源模块和地线之间的开关闭合,以便第一电容可以通过恒流源模块缓慢放电。第一比较器的负极输入端采集第一电容的电压,第一比较器的正极输入端采集第二电容的电压,当第一电容缓慢放电至电压小于第二电容的电压时,则第一比较器发生反转,向第一或门输出目标信号,该目标信号可以使第一或门输出第一脉冲信号。该种可能的实现方式提供了一种多项控制器的具体实现方式,提升了方案的可实现性。

12.在上述第一方面的一种可能的实现方式中,所述第一周期控制模块还包括第一触

发器;所述第一触发器的第一输入端与所述第一比较器电连接,所述第一触发器的第二输入端与所述分频器电连接,所述第一触发器的输出端与所述第二开关模块电连接;所述第一触发器用于:根据所述第一比较器和所述分频器输出的电信号控制所述第二开关模块中部分开关闭合;所述第二开关模块还用于:根据所述第一触发器输出的信号通过部分开关闭合来控制所述第一电容和所述第二电容清空电荷。

13.该种可能的实现方式中,第一触发器接收到分频器输出的信号后,向第二开关模块输出低电平信号,第二开关模块中位于第一电容和地线之间的开关以及位于第二电容和地线之间的开关断开。若第一触发器接收到第一比较器输出的目标信号后,第一触发器控制第二开关模块中位于第一电容和地线之间的开关以及位于第二电容和地线之间的开关闭合,进而,第二开关模块根据第一触发器输出的信号控制第一电容和第二电容与地线连接,从而清空电荷,以便第一电容和第二电容在下一个工作周期可以继续充放电从而正常工作。

14.在上述第一方面的一种可能的实现方式中,其特征在于,所述恒流源模块包括第一恒流源、第二恒流源和第三恒流源,所述第一开关模块包括第一开关和第二开关,所述第二开关模块包括第三开关、第四开关和第五开关;所述第一开关和所述第二开关的第一端与所述分频器的输出端电连接,所述第一开关的第二端与所述第一恒流源的第一端电连接,所述第一开关的第三端与所述第一电容的第一端电连接,所述第二开关的第二端与所述第二恒流源的第一端电连接,所述第二开关的第三端与所述第二电容的第一端电连接;所述第三开关的第一端与所述第二反相器电连接,所述第三开关的第二端与所述第三恒流源电连接,所述第三开关的第三端接地,所述第四开关的第一端通过第四连接点与所述第一电容的第一端和所述第一开关的第三端电连接,所述第四开关的第二端与所述第一触发器的输出端电连接,所述第四开关的第三端接地,所述第五开关的第一端通过第五连接点与所述第二电容的第一端和所述第二开关的第三端电连接,所述第五开关的第二端与所述第一触发器的输出端电连接,所述第五开关的第三端接地;所述第一恒流源和所述第二恒利源的第二端与外部电源电连接。

15.该种可能的实现方式中,提供了一种多项控制器中包括的恒流源模块、第一开关模块、第二开关模块和电容模块的具体实现方式以及具体连接关系,提升了方案的可实现性。

16.在上述第一方面的一种可能的实现方式中,所述的cot并联电路还包括信号处理模块;

17.所述信号处理模块的输入端与所述滤波模块的输出端电连接,所述信号处理模块的输出端与所述第一相变器的输入端电连接;所述信号处理模块用于:根据接收到的ramp信号和所述滤波模块输出的信号输出第二脉冲信号,所述第二脉冲信号用于指示所述第一相变器输出所述第一功率信号。

18.该种可能的实现方式中,cot并联电路还包括信号处理模块,其中,信号处理模块可以接收ramp信号和滤波模块输出的信号,当ramp信号的值小于滤波模块输出的信号的值时输出第二脉冲信号,第二脉冲信号可以指示第一相变器输出第一功率信号。该种可能的实现方式提供了一种控制第一相变器输出第一功率信号的具体控制方法,提升了方案的可实现性。

19.在上述第一方面的一种可能的实现方式中,所述信号处理模块包括第一运算放大器以及第二比较器;所述第一运算放大器的第一输入端输入第一参考信号,所述第一运算放大器的第二输入端与所述滤波模块的输出端电连接,所述第一运算放大器的输出端与所述第二比较器的第一输入端电连接;所述第二比较器的第二输入端输入斜坡补偿ramp信号,所述第二比较器的输出端与所述第一相变器的输入端电连接;所述第一运算放大器用于:根据所述第一参考信号和所述滤波模块输出的信号调整向所述第二比较器输出的信号的值;所述第二比较器用于:确认所述ramp信号的值小于所述第一运算放大器输出信号的值时输出所述第一脉冲信号。

20.该种可能的实现方式中,第一运算放大器601用于反馈调节第二比较器602输出的脉冲信号的频率。第一参考信号用于调节信号eao的大小。若第一参考信号的值大于滤波模块104所输出的功率信号,则第一运算放大器601增大输出信号eao的值,则第二比较器602输出脉冲信号的频率加快。同理,若第一参考信号的值小于滤波模块104所输出的功率信号,则第一运算放大器601减小输出信号eao的值,则第二比较器602输出脉冲信号的频率减慢。进而,可以通过调节参考电压来调整第二比较器602输出脉冲信号的频率,进一步控制整个cot并联电路输出电流的强度。

21.该种可能的实现方式中,所述第一相变器包括第一导通计时器、第一驱动电路、第六开关和第七开关;所述第一导通计时器的第一输入端与所述信号处理模块的输出端电连接,所述第一导通计时器的第二输入端与所述第二相变器的第二输入端电连接,所述第一导通计时器的输出端与所述第一驱动电路的输入端电连接;所述第一驱动电路的第一输出端与所述第六开关的第一端电连接,所述第一驱动电路的第二输出端与所述第七开关的第一端电连接;所述第六开关的第二端与外部电源电连接,所述第六开关的第三端与所述第一导通计时器的第二输入端、所述第七开关的第二端和所述滤波模块的第一输入端电连接;所述第七开关的第二端与所述滤波模块的第一输入端电连接,所述第七开关的第三端接地;所述第一导通计时器用于:根据所述信号处理模块输出的第二脉冲信号和所述第六开关输出的信号输出第一信号和第二信号,所述第一信号用于指示所述第一驱动电路闭合所述第六开关且断开所述第七开关,所述第一相变器中的外部电源通过处于闭合状态的第六开关输出所述第一功率信号,所述第二信号用于指示所述第一驱动电路闭合所述第七开关且断开所述第六开关,所述第一相变器停止输出所述第一功率信号。

22.该种可能的实现方式中,信号处理模块根据滤波模块输出的功率信号和接收到的ramp信号向第一导通计时器输出脉冲信号,第一导通计时器根据该脉冲信号和vcc通过第六开关输出的电流输出控制信号,该控制信号中的高电平信号可以控制第一驱动模块闭合第六开关,从而第六开关连接的外部电源vcc向滤波模块输入电流,即第一相变器输出第一功率信号,该控制信号中的低电平信号可以控制第一驱动模块断开第六开关,闭合第七开关。该种可能的实现方式提供了一种第一相变器的具体结构,提升了方案的可实现性。

23.在上述第一方面的一种可能的实现方式中,所述第二相变器包括第二导通计时器、第二驱动电路、第八开关和第九开关;所述第二导通计时器的第一输入端与所述多项控制器的输出端电连接,所述第二导通计时器的第二输入端与所述第一相变器的第二输入端电连接,所述第二导通计时器的输出端与所述第二驱动电路的输入端电连接;所述第二驱动电路的第一输出端与所述第八开关的第一端电连接,所述第二驱动电路的第二输出端与

所述第九开关的第一端电连接;所述第八开关的第二端与外部电源电连接,所述第八开关的第三端与所述第二导通计时器的第二输入端、所述第九开关的第二端以及所述滤波模块的第二输入端电连接;所述第九开关的第二端与所述滤波模块的第二输入端电连接,所述第九开关的第三端接地;所述第二通电延时定时电路用于:根据所述多项控制器输出的第一脉冲信号和所述第八开关输出的信号输出第三信号和第四信号,所述第三信号用于指示所述第二驱动电路闭合所述第八开关且断开所述第九开关,所述第二相变器中的外部电源通过处于闭合状态的第八开关输出所述第二功率信号,所述第四信号用于指示所述第二驱动电路闭合所述第九开关且断开所述第八开关,所述第二相变器停止输出所述第二功率信号。

24.该种可能的实现方式中,多项控制器接收到第一功率信号,向第二导通计时器输出第一脉冲信号,第二导通计时器根据该脉冲信号和vcc通过第八开关输出的电流输出控制信号,该控制信号中的高电平信号可以控制第二驱动模块闭合第八开关,从而第八开关连接的外部电源vcc向滤波模块输入电流,即第二相变器输出第二功率信号,该控制信号中的低电平信号可以控制第二驱动模块断开第八开关,闭合第九开关。该种可能的实现方式提供了一种第二相变器的具体结构,提升了方案的可实现性。

25.在上述第一方面的一种可能的实现方式中,所述第一导通计时器包括第三开关模块、第四电容、第三比较器和第三触发器;所述第三开关模块的第一端与所述第一驱动电路电连接,所述第三开关模块的第二端与外部电源电连接,所述第三开关模块的第三端与所述第四电容的第一端电连接,第三开关模块的第四端接地;所述第四电容的第二端与所述第三比较器的正极输入端电连接,所述第四电容的第三端接地;所述第三比较器的输出端与所述第三触发器的第一输入端电连接;所述第三触发器的第二输入端与所述信号处理模块电连接,所述第三触发器的输出端与所述第一驱动电路电连接;所述第三开关模块用于:根据所述第一驱动电路输出的信号控制所述外部电源向所述第四电容充电;所述第三比较器用于:确认所述第三比较器的第二输入端接收的参考信号的值小于所述第四电容的电压值时,输出第五信号;所述第三触发器用于:根据所述信号处理模块输出的脉冲信号后输出所述第一信号,根据所述第五信号输出所述第二信号。

26.在上述第一方面的一种可能的实现方式中,所述第一导通计时器还包括均流电路和第三运算放大器,所述均流电路包括多个rc滤波器,其中部分rc滤波器之间存在共同节点;所述均流电路的第一端与所述第六开关和所述第二相变器电连接,所述均流电路的输出端与所述第三运算放大器电连接;所述均流电路用于:对所述第一相变器和所述第二相变器输出的所述第一功率信号和所述第二功率信号滤波后做平均后得到均值信号,向所述第三运算放大器的正极输入端输入滤波后的第一功率信号,向所述第三运算放大器的负极输入端输入所述均值信号;所述第三运算放大器用于:确认所述滤波后的第一功率信号小于所述均值信号后,减小所述第三比较器的第二端输入的参考信号的值,确认所述第一功率信号大于所述均值信号后,增加所述第三比较器的第二端输入的参考信号的值。

27.本技术中,均流电路可以对第一相变器和第二相变器输出的第一功率信号和第二功率信号做平均后得到均值信号。第三运算放大器可以确认第一功率信号小于均值信号后,减小第三比较器的第二端输入的参考信号的值,第三比较器发生反转的时间更短,则第一功率信号的值减小。确认第一功率信号大于均值信号后,增加第三比较器的第二端输入

的参考信号的值,第三比较器发生反转的时间更长,则第一功率信号的值增大。均流电路和第三比较器可以调节第一输出功率的大小,使第一输出功率稳定在一个合理的范围。

28.在上述第一方面的一种可能的实现方式中,所述滤波模块包括第一电感、第二电感和第三电容;所述第一电感的第一端与所述第六开关的第三端和所述第七开关的第二端电连接,所述第一电感的第二端与所述第二电感的第一端以及所述第三电容的第一端电连接;所述第二电感的第一端有所述第八开关的第三端和所述第九开关的第二端电连接,所述第二电感的第二端与所述第三电容的第一端电连接;所述第三电容的第二端接地;所述第一电感、所述第二电感和所述第三电容共同用于:过滤所述第一功率信号和所述第二功率信号的输出波纹。

29.该种可能的实现方式中,提供了一种滤波模块的具体实现形式,提升了方案的可实现性。

30.本技术实施例第二方面提供一种电源设备,该电源设备包括控制器与cot并联电路,该cot并联电路在控制器的控制下输出功率信号,该cot并联电路为上述第一方面或第一方面任意一种可能实现方式中所描述的cot并联电路。

31.从以上技术方案可以看出,本技术实施例具有以下优点:

32.本技术中,电源设备中包括的cot多项并联电路接收第一相变器输出的第一功率信号后,可以向第二相变器输出第一脉冲信号,第一脉冲信号用于指示第二相变器输出第二功率信号。进而,cot多项并联电路可以在ramp信号的一个周期内输出多个功率信号,无需提升ramp信号的频率便可输出高频功率信号,降低了高频cot多相并联的实现难度。

附图说明

33.图1为本技术提供的一电源设备的应用示意图;

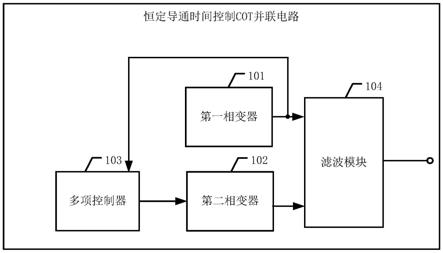

34.图2是本技术提供的一种cot多相并联电路的一结构示意图;

35.图3是本技术提供的一种cot多相并联电路的另一结构示意图;

36.图4是本技术提供的一种cot多相并联电路的一应用示意图;

37.图5a为本技术提供的一种多项控制器的一结构示意图;

38.图5b是本技术提供的一种第一周期控制模块的一结构示意图;

39.图5c是本技术提供的一种第一周期控制模块的另一结构示意图;

40.图5d是本技术提供的一种多项控制器的另一结构示意图;

41.图5e为本技术提供的一种多项控制器的另一结构示意图;

42.图6是本技术提供的一种多项控制器的另一应用示意图;

43.图7是本技术提供的一种多项控制器的另一结构示意图;

44.图8是本技术提供的一种cot多相并联电路的另一结构示意图;

45.图9是本技术提供的一种cot多相并联电路的另一结构示意图;

46.图10是本技术提供的第一导通计时器的一结构示意图;

47.图11是本技术提供的第一导通计时器的另一结构示意图;

48.图12是本技术提供的第一导通计时器和第二导通计时器的一结构示意图;

49.图13是本技术提供的一种均流电路的一结构示意图;

50.图14是本技术提供的一种cot多项并联电路的另一结构示意图。

具体实施方式

51.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员所获得的所有其他实施例,都属于本发明保护的范围。

52.本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”、“第三”、“第四”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的实施例能够以除了在这里图示或描述的内容以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

53.随着电子产品集成度的提升,嵌入式高性能电路系统要求电源设备在输出高电流的同时,供电电源的输出电压能够快速响应负载的跳变。cot能够快速响应负载跳变,保持输出电压稳定,满足负载跳变需求。通过多路cot并联能够提高电源设备的电流输出能力。

54.目前,cot多相并联电路输出信号的过程中,首先需要构造一个连续的ramp信号。cot多相并联电路中包括的控制器可以根据每个ramp信号的周期产生一个脉冲信号。接收到脉冲信号的开关组件依次输出功率信号。随着开关组件输出功率信号的频率提高,构造连续ramp信号的频率也需要随之提高。例如,若单个开关组件的工作频率为8mhz,对于一个4相cot并联电路来说,连续ramp信号的频率为32mhz;对于一个6相cot并联电路来说,连续ramp的频率为48mhz。开关组件工作的频率提升时,连续ramp的频率也需要随之提升。

55.连续ramp通常由信号发生器产生,然而,采用bcd工艺生产的信号发生器存在固有延迟,构造高频ramp信号的难度较大,难以产生更高频率的连续ramp,进而,限制了cot多相并联电路输出功率信号的频率,即限制了电源设备输出功率信号的频率。

56.针对现有的cot多相并联电路在工作时存在的上述问题,本技术提供了一种cot多相并联电路以及电源设备,电源设备中包括的cot多项并联电路接收第一相变器输出的第一功率信号后,可以向第二相变器输出第一脉冲信号,第一脉冲信号用于指示第二相变器输出第二功率信号。进而,cot多项并联电路可以在ramp信号的一个周期内输出多个功率信号,无需提升ramp信号的频率便可输出高频功率信号,降低了高频cot多相并联的实现难度。

57.图1为本技术提供的一电源设备的应用示意图。

58.请参阅图1,本技术中,包括cot多相并联电路的电源设备为负载设备充电的场景可以参阅如图1所示的手机充电场景进行理解。如图1所示,电源设备的一端通过插座接入电网,该电源设备的另一端接入手机,就可以接通从电网到手机的充电回路,从而实现手机充电的过程。

59.图1所示的电源设备只是一种可能的形态,实际上电源设备的种类可以有多种,不同类型的终端设备的电源设备可以不相同,相同类型的终端设备的电源设备也可以不相同,此处本技术中不做限定。

60.图2是本技术提供的一种cot多相并联电路的一结构示意图。

61.请参阅图2,图2展示了本技术提供的cot多相并联电路的拓扑结构,第一相变器

101、第二相变器102、多项控制器103和滤波模块104;第一相变器101的输出端与多项控制器103的输入端和滤波模块104的第一输入端电连接;第二相变器102的输入端与多项控制器103的输出端电连接,第二相变器102的输出端与滤波模块104的第二输入端电连接。

62.该种可能的实现方式中,多项控制器103接收到第一相变器101输出的第一功率信号后,在cot并联电路接收到的ramp信号的一个周期内,根据第一相变器输出的第一功率信号控制第二相变器输出第二功率信号。滤波模块104可以对第一功率信号和第二功率信号进行滤波,降低第一功率信号和第二功率信号的输出波纹,以便cot多相并联电路可以平稳输出功率信号。

63.本技术中,为了提高cot多相并联电路的电流输出能力,cot多相并联电路还可以包括更多的相变器,该种可能的实现方式将在下面的示例中进行说明。

64.图3是本技术提供的一种cot多相并联电路的另一结构示意图。

65.请参阅图3,本技术中,可选的,cot多相并联电路还可以包括第三相变器105。第三相变器105的输入端与多项控制器103的输出端电连接,第三相变器105的输出端与滤波模块104电连接。

66.本技术中,第一相变器向多项控制器103和滤波模块104输出第一功率信号。多项控制器103接收到第一相变器101输出的第一功率信号后,多项控制器103向第二相变器102输出第一脉冲信号,第一脉冲信号可以触发第二相变器102输出第二功率信号。多项控制器103向第三相变器105输出第三脉冲信号,第三脉冲信号可以触发第三相变器105输出第三功率信号。滤波模块104可以对第一功率信号、第二功率信号和第三功率信号进行滤波,降低第一功率信号、第二功率信号和第三功率信号的输出波纹,以便cot多相并联电路可以平稳输出功率信号。

67.本技术中,图3所示的实施例提供的cot多相并联电路包括了第三相变器105,提高了cot多相并联电路的电流输出能力,可选的,同理可知,为了提高cot多相并联电路的电流输出能力,本技术提供的cot多相并联电路还可以包括第四相变器、第五相变器第六相变器等更多的相变器,具体此处不做限定。

68.图4是本技术提供的一种cot多相并联电路的一应用示意图。

69.请参阅图4,以cot多相并联电路包括三个相变器为例进行说明cot多相并联电路中功率信号和脉冲信号的发送时机。信号处理模块根据ramp信号以及功率信号a输出脉冲信号0,第一相变器则根据脉冲信号0输出功率信号a,多项控制器根据功率信号a向第二相变器输出脉冲信号1,第二相变器根据脉冲信号1输出功率信号b。多项控制器向第三相变器输出脉冲信号2,第三相变器输出功率信号c。多项控制器向第四相变器输出脉冲信号3,第三相变器输出功率信号d。当ramp信号的下一个周期到来时,则继续重复上述的信号输出过程。

70.本技术中,cot多相并联电路可以包括更多或更少的相变器,cot多相并联电路包括更多或更少的相变器时功率信号和脉冲信号的发送时机与上述图4所示的实施例相类似,具体此处不做赘述。

71.本技术中,图2至图4所示的实施例中所说明的多项控制器103具有具体的实现方式,下面将详细说明多项控制器103中包括的具体结构。

72.图5a为本技术提供的一种多项控制器的一结构示意图。

73.请参阅图5a,图5a展示了本技术提供的多项控制器的具体结构。多项控制器包括分频器201、第一反相器202、第一周期控制模块203、第二周期控制模块204以及第一或门205。

74.分频器201的输入端与第一相变器202的输出端电连接,分频器201的输出端通过第一连接点与第一周期控制模块204的输入端和第一反相器202的输入端电连接;第一反相器202的输出端与第二周期控制模块204的输入端电连接;第一或门205的输入端与第一周期控制模块204的输出端和第二周期控制模块204的输出端电连接;

75.本技术中,第一周期模块203和第二周期模块204接收到分频器201输出的不同信号后,第一周期模块203和第二周期模块204可以通过多个电容和多个恒流源构成的时间采集电路采集第一相变换器输出第一功率信号的输出周期,根据输出周期输出目标信号。第一或门205可以根据第一周期控制模块203或所第二周期控制模块204输出的目标信号输出第一脉冲信号,第一脉冲信号用于指示第二相变器102输出第二功率信号。

76.图5b是本技术提供的一种第一周期控制模块的一结构示意图。

77.请参阅图5b,图5b展示了本技术提供的第一周期控制模块203,第一周期控制模块203包括第二反相器301、恒流源模块302、第一开关模块303、第二开关模块304、电容模块305和第一比较器306,电容模块305包括第一电容和第二电容;

78.第二反相器301的第一端与分频器201的输出端电连接,第二反相器301的第二端与第二开关模块304的第一端电连接;第一开关模块303的第一端与分频器201的输出端电连接,第一开关模块303的第二端与恒流源模块302的第一端电连接,第一开关模块303的第三端与电容模块305的第一端电连接;第二开关模块304的第二端与恒流源模块302的第二端电连接,第二开关模块304的第三端接地,电容模块305的第三端接地;第一比较器306的负极输入端通过第二连接点与第一开关模块303和第一电容电连接,第一比较器的正极输入端通过第三连接点与第一开关模块303和第二电容电连接;

79.本技术中,第一开关模块303可以根据分频器输出的不同信号来控制恒流源模块302向电容模块305中的第一电容和第二电容充电的时间,分频器201输出高电平信号时,第一开关模块303接收到高电平信号,控制开关闭合,以便恒流源模块302可以通过闭合的开关向第一电容和第二电容充电,充电的时间与第一相变器101输出第一功率信号的周期相同。这样,第一开关模块303便完成了对于第一功率信号周期的采集。分频器201输出低电平信号时,第一开关模块303接收到低电平信号,控制开关断开,恒流源模块302停止向第一开关模块303充电。第二反相器301接收到分频器201输出的低电平信号,将低电平信号转化为高电平信号后向第二开关模块304输出,第二开关模块304接收到高电平信号后控制位于恒流源模块302和地线之间的开关闭合,以便第一电容可以通过恒流源模块302缓慢放电。第一比较器306的负极输入端采集第一电容的电压,第一比较器306的正极输入端采集第二电容的电压,当第一电容缓慢放电至电压小于第二电容的电压时,则第一比较器306发生反转,向第一或门205输出目标信号,该目标信号可以使第一或门205输出第一脉冲信号。

80.图5c是本技术提供的一种第一周期控制模块的另一结构示意图。

81.请参阅图5c,可选的,第一周期控制模块还包括第一触发器307;第一触发器307的第一输入端与第一比较器306电连接,第一触发器307的第二输入端与分频器201电连接,第一触发器307的输出端与第二开关模块304电连接。

82.本技术中,第一触发器307接收到分频器输出的信号后,向第二开关模块输出低电平信号,第二开关模块中位于第一电容和地线之间的开关以及位于第二电容和地线之间的开关断开。若第一触发器307接收到第一比较器306输出的目标信号后,第一触发器控制第二开关模块中位于第一电容和地线之间的开关以及位于第二电容和地线之间的开关闭合,进而,第二开关模块304根据第一触发器307输出的信号控制第一电容和第二电容与地线连接,从而清空电荷。

83.图5d是本技术提供的一种多项控制器的另一结构示意图。

84.请参阅图5d,可选的,恒流源模块包括第一恒流源401、第二恒流源402和第三恒流源403,第一开关模块包括第一开关404和第二开关405,第二开关模块包括第三开关406、第四开关407和第五开关408;

85.第一开关404和第二开关405的第一端与分频器201的输出端电连接,第一开关404的第二端与第一恒流源401的第一端电连接,第一开关404的第三端与第一电容409的第一端电连接,第二开关405的第二端与第二恒流源402的第一端电连接,第二开关的第三端与第二电容的第一端电连接;

86.第三开关406的第一端与第二反相器202电连接,第三开关406的第二端与第三恒流源405电连接,第三开关406的第三端接地,第四开关407的第一端通过第四连接点与第一电容409的第一端和第一开关404的第三端电连接,第四开关407的第二端与第一触发器307的输出端电连接,第四开关407的第三端接地,第五开关408的第一端通过第五连接点与第二电容410的第一端和第二开关405的第三端电连接,第五开关408的第二端与第一触发器307的输出端电连接,第五开关408的第三端接地;

87.第一恒流源401和第二恒利源402的第二端与外部电源vcc电连接。

88.本技术中,分频器201输出高电平信号时,第一开关404和第二开关405闭合,第一恒流源401和第二恒流源402通过处于闭合状态的第一开关404和处于闭合状态的第二开关405向第一电容409和第二电容410充电。分频器201输出低电平信号时,第一开关404和第二开关405断开,第一电容409和第二电容410停止充电。充电的时间与第一相变器101输出第一功率信号的周期相同。这样,第一开关404和第二开关405便完成了对于第一功率信号周期的采集。分频器201输出高电平信号时,高电平信号经过第二反相器202处理后向第三开关406输出低电平信号,第三开关406、第四开关407和第五开关408均断开。分频器201输出低电平信号时,低电平信号经过第二反相器202处理后向第三开关406输出高电平信号,第三开关406闭合,第一电容409通过第三恒流源403缓慢放电,第一比较器306的负极输入端采集第一电容409的电压,第一比较器306的正极输入端采集第二电容410的电压,当第一电容409缓慢放电至电压小于第二电容410的电压时,则第一比较器306发生反转,向第一或门205输出目标信号,该目标信号可以使第一或门205输出第一脉冲信号。

89.本技术中,可选的,分频器201可以是d触发器,分频器201还可以是能够实现分频的逻辑电路,分频器201还可以是其他类型的分频器,具体此处不做限定。

90.本技术中,可选的,第一开关至第五开关可以是三极管,也可以是mos管,还可以是其他类型的开关,具体此处不做限定。

91.本技术提供的多项控制器中可以包括更多的电容、比较器和或门,进而可以输出更多的脉冲信号,具体此处不做限定。

92.本技术中,第二周期控制模块与上述实施例中说明的第一周期控制模块的工作原理相类似,具体此处不赘述。

93.本技术中,为了实现多项控制器输出脉冲信号的连续性,多项控制器包括的第一周期控制模块与第二周期控制模块交替进行工作,当第一周期控制模块中包括的第一电容和第二电容处于充电状态时,第一比较器306无法输出高电平信号。此时,第二周期控制中包括的电容于放电状态,第二周期控制模块中包括的比较器发生反转后便可以输出高电平信号,进而使得第一或门205输出脉冲信号。进而保证了多项控制器输出脉冲信号的连续性。

94.图5e为本技术提供的一种多项控制器的另一结构示意图。

95.请参阅图5e,图5e展示了本技术提供的多项控制器的拓扑结构,可选的,多项控制器包括分频器501、反相器502、反相器503、反相器504、恒流源505、恒流源506、恒流源507、恒流源508、开关509、开关510、开关511、开关512、开关513、开关514、开关515、开关516、开关517、开关518、开关519、开关520、开关521、开关522、电容523、电容524、电容525、电容526、比较器527、比较器528、或门529、触发器530和触发器531;

96.分频器501的输入端与相变器101的输出端电连接,分频器501的输出端通过第一连接点与恒流源505的第一端、反相器502的输入端、反相器503的输入端和触发器530的第一输入端电连接;

97.开关509的第一端、开关510的第一端和开关511的第一端与外部电源电连接,开关509的第二端与恒流源505的第二端电连接,开关510的第二端与电容523的第一端电连接,开关511的第二端与电容524的第一端电连接,开关509的第三端、开关510的第三端和开关511的第三端与恒流源505的第二端电连接,恒流源505的第三端接地,电容523的第二端接地,电容524的第二端接地;

98.恒流源506的第一端与反相器502的第二端电连接,恒流源506的第二端与外部电源电连接,恒流源506的第三端与开关512的第一端、开关512的第二端和开关513的第一端电连接,开关512的第三端接地,开关513的第二端与第一电容523的第一端和开关510的第三端电连接,开关513的第三端接地;

99.比较器527的负极输入端通过第二连接点a与电容523的第一端和开关519的第三端电连接,比较器527的正极输入端通过第三连接点b与电容524的第一端和开关511的第三端电连接,比较器527的输出端与或门529的第一输入端和触发器530的第二输入端电连接;

100.开关514的第一端与电容523的第一端和开关510的第三端电连接,开关514的第二端接地,开关514的第三端与触发器530的输出端电连接,开关515的第一端与电容524的第一端和开关511的第三端电连接,开关515的第二端接地,开关515的第三端与第一触发器530的输出端电连接;

101.反相器503的第二端与恒流源507的第一端、反相器508的第一端和第二触发器531的第一输入端电连接;

102.开关516的第一端、开关517的第一端和开关518的第一端与外部电源电连接,开关516的第二端与恒流源507的第二端电连接,开关517的第二端与电容525的第一端电连接,开关518的第二端与电容526的第一端电连接,开关516的第三端、开关517的第三端和开关518的第三端与恒流源507的第二端电连接,恒流源507的第三端接地,电容525的第二端接

地,电容526的第二端接地;

103.恒流源508的第一端与反相器504的第二端电连接,恒流源508的第二端与外部电源电连接,恒流源508的第三端与开关519的第一端、开关519的第二端和开关520的第一端电连接,开关519的第三端接地,开关520的第二端与电容525的第一端电和开关517的第三端电连接,开关520的第三端接地;

104.比较器528的负极输入端通过第四连接点c与电容525的第一端和开关517的第三端电连接,比较器528的正极输入端通过第五连接点d与电容526的第一端和开关518的第三端电连接,比较器528的输出端与或门529的第二输入端和触发器531的第二输入端电连接;

105.开关521的第一端与电容525的第一端和开关517的第三端电连接,开关521的第二端接地,开关521的第三端与触发器531的输出端电连接,开关522的第一端与电容526的第一端和开关518的第三端电连接,开关522的第二端接地,开关522的第三端与第二触发器531的输出端电连接。

106.本技术中,若分频器501接收到相变器发送的第一功率信号后,501输出高电平信号,多项控制器中包括的第一周期控制模块处于储能状态。恒流源505输入高电平,则恒流源505控制开关509、开关510和开关511闭合,即外部电源vcc向电容523以及电容524充电。分频器501输出低电平信号后,恒流源505控制开关509、开关510和开关511断开,外部电源vcc停止向电容523和电容524充电。分频器501输出的低电平信号经过反相器502后输出高电平信号,恒流源506控制开关512和开关513闭合,电容523通过开关523缓慢放电。比较器527的负极输入端采集电容523的电压,比较器的正极输入端采集电容524的电压。当电容523放电后电压低于电容524的电压时,比较器527发生反转,向或门529输出高电平信号,或门529向相变器输出第一脉冲信号。进而可以通过第一脉冲信号控制第二相变器输出第二功率信号。比较器527向触发器530输出高电平信号,则触发器530输出电信号控制开关514与开关515闭合,从而电容523与电容524可以通过开关514与开关515放电。

107.本技术中,为了实现多项控制器输出脉冲信号的连续性,多项控制器包括的第一周期控制模块与第二周期控制模块交替进行工作,当第一周期控制模块中包括的第一电容和第二电容处于充电状态时,比较器527无法输出高电平信号。此时,第二周期控制中包括的第三电容与第四电容处于放电状态,比较器528发生反转后便可以输出高电平信号,进而使得或门529输出脉冲信号。进而保证了多项控制器输出脉冲信号的连续性。

108.图6是本技术提供的一种多项控制器的一应用示意图。

109.请参阅图6,以多项控制器中包括八个电容来为例进行说明多项控制器输出脉冲信号的过程。其中,假设多项控制器的第一周期控制模块中包括电容1、电容2、电容3和电容4。多项控制器的第二周期控制模块中包括电容5、电容6、电容7和电容8。

110.如图6所示,以第一周期控制为例进行说明,cot并联电路输出第一功率信号后,分频器接收到第一功率信号后输出高电平信号。电容1、电容2、电容3和电容4开始充电。第一相变器再次输出第一功率信号后,分频器接收到第一功率信号后输出低电平信号。电容1开始放电,电容2、电容3和电容4电压维持不变。当电容1的电压低于电容2的电压时,对应采集电容1、电容2电压的比较器1发生反转,比较器1输出高电平信号(目标信号),与比较器1连接的或门1输出第一脉冲信号。相应的,第二相变器输出第二功率信号。同理可知,当电容1的电压分别低于电容3、电容4的电压时,对应采集电容3、电容4电压的比较器2、比较器3发

生反转,比较器2、比较器3输出高电平信号(目标信号),与比较器2、比较器3连接的或门2、或门3输出第三脉冲信号和第四脉冲信号。相应的,第三相变器、第四相变器输出第三功率信号和第四功率信号。此外,分频器接收到第一功率信号后输出低电平信号后,触发第二周期控制模块中的电容5进行放电,以便第一周期控制模块充电时多项控制器可以连续输出脉冲信号。

111.图7是本技术提供的一种cot并联电路的另一结构示意图。

112.请参阅图7,本技术中,的cot并联电路还包括信号处理模块106,信号处理模块106的输入端与滤波模块104的输出端电连接,信号处理模块106的输出端与第一相变器101的输入端电连接。

113.本技术中,信号处理模块106可以根据接收到的ramp信号和滤波模块输出的信号输出第二脉冲信号,第二脉冲信号用于指示第一相变器输出第一功率信号。

114.图8是本技术提供的一种cot并联电路的另一结构示意图。

115.请参阅图8,可选的,本技术中,信号处理模块106包括第一运算放大器601以及第二比较器602;第一运算放大器601的第一输入端输入第一参考信号,第一运算放大器601的第二输入端与滤波模块104的输出端电连接,第一运算放大器601的输出端与第二比较器602的第一输入端电连接;第二比较器602的第二输入端输入斜坡补偿ramp信号,第二比较器602的输出端与第一相变器101的输入端电连接;

116.本技术中,第一运算放大器用于可以根据第一参考信号和滤波模块输出的信号调整向第二比较器输出的信号的值。第二比较器可以确认ramp信号的值小于第一运算放大器输出信号的值时输出第一脉冲信号。

117.本技术中,第一运算放大器601用于反馈调节第二比较器602输出的脉冲信号的频率。第一参考信号用于调节信号eao的大小。若第一参考信号的值大于滤波模块104所输出的功率信号,则第一运算放大器601增大输出信号eao的值,则第二比较器602输出脉冲信号的频率加快。同理,若第一参考信号的值小于滤波模块104所输出的功率信号,则第一运算放大器601减小输出信号eao的值,则第二比较器602输出脉冲信号的频率减慢。进而,可以通过调节参考电压来调整第二比较器602输出脉冲信号的频率,进一步控制整个cot并联电路输出电流的强度。

118.图9是本技术提供的一种cot并联电路的另一结构示意图。

119.请参阅图9,本技术中,可选的,所述第一相变器包括第一导通计时器701、第一驱动电路702、第六开关703和第七开关704。

120.第一导通计时器701的第一输入端与信号处理模块106的输出端电连接,第一导通计时器701的第二输入端与第二相变器102的第二输入端电连接,第一导通计时器701的输出端与第一驱动电路702的输入端电连接;第一驱动电路702的第一输出端与第六开关703的第一端电连接,第一驱动电路702的第二输出端与第七开关704的第一端电连接;第六开关703的第二端与外部电源电连接,第六开关703的第三端与第一导通计时器701的第二输入端、第七开关704的第二端和滤波模块104的第一输入端电连接;第七开关704的第二端与滤波模块104的第一输入端电连接,第七开关704的第三端接地;

121.本技术中,第一导通计时器701可以根据信号处理模块106和第六开关703输出的信号输出第一信号和第二信号,第一信号用于指示第一驱动电路702闭合第六开关703且断

开第七开关704,第一相变器101中的外部电源通过处于闭合状态的第六开关703输出第一功率信号,第二信号用于指示第一驱动电路702闭合第七开关704且断开第六开关703,第一相变器101停止输出第一功率信号。

122.本技术中,第二相变器的结构与第一相变器的结构相类似,具体的实现方式请参照图9所示的结构进行理解,此处不做赘述。

123.本技术中,信号处理模块106根据滤波模块104输出的功率信号和接收到的ramp信号向第一导通计时器701输出脉冲信号,第一导通计时器701根据该脉冲信号a和vcc通过第六开关703输出的电流输出控制信号b,该控制信号b中的高电平信号可以控制第一驱动电路702闭合第六开关703,从而第六开关703连接的外部电源vcc向滤波模块104输入电流,即第一相变器输出第一功率信号,该控制信号b中的低电平信号可以控制第一驱动电路702断开第六开关703,闭合第七开关704。多项控制器103接收到第一功率信号,向第二导通计时器705输出第一脉冲信号,第二导通计时器705根据该脉冲信号c和vcc通过第八开关707输出的电流输出控制信号d,该控制信号d中的高电平信号可以控制第二驱动模块706闭合第八开关707,从而第八开关707连接的外部电源vcc向滤波模块104输入电流,即第二相变器输出第二功率信号,该控制信号d中的低电平信号可以控制第二驱动电路706断开第八开关707,闭合第九开关708。

124.图10是本技术提供的第一导通计时器的结构示意图。

125.请参阅图10,可选的,第一导通计时器可以包括第三开关模块801、第四电容802、第三比较器803和第三触发器804。

126.第三开关模块801的第一端与第一驱动电路702电连接,第三开关模块801的第二端与外部电源电连接,第三开关模块的第三端与第四电容的第一端电连接,第三开关模块的第四端接地;第四电容的第二端与第三比较器的正极输入端电连接,第四电容的第三端接地;第三比较器803的输出端与第三触发器804的第一输入端电连接;第三触发器803的第二输入端与信号处理模块106电连接,第三触发器804的输出端与第一驱动电路702电连接。

127.本技术中,第三开关模块可以根据第一驱动电路输出的信号控制外部电源向第四电容充电。当第一驱动电路输出的信号是控制第六开关闭合,控制第七开关断开时,第三开关模块中位于第四电容和地线之间的开关断开,此时第三开关模块中位于外部电源与第四电容之间的开关闭合,外部电源向第四电容充电。当第一驱动电路输出的信号是控制第六开关断开,控制第七开关闭合时,第三开关模块中位于第四电容和地线之间的开关闭合,此时第四电容清空电荷,第四电容的电压为零。

128.本技术中,第三比较器的正极输入端采集第四电容的电压值,第三比较器的负极输入端输入参考信号。若第四电容充电过程中电压值大于第三比较器器负极输入端输入的参考信号时,则第三比较器发生反转,向第三触发器输出高电平信号(第五信号)。当第三触发器的第一输入端接收到信号处理模块输出的高电平信号(第二脉冲信号)后输出第一信号,通过第一信号控制第一驱动电路闭合第六开关断开第七开关。当第三触发器的第二输入端接收到高电平信号后输出第二信号,第一驱动电路根据该第二信号断开第六开关,闭合第七开关。

129.图11是本技术提供的第一导通计时器的另一结构示意图。

130.请参阅图11,可选的,第一导通计时器还可以包括均流电路805和第三运算放大器

806。

131.均流电路的第一端与第六开关和第二相变器电连接,均流电路的输出端与第三运算放大器的正极输入端电连接。第三运算放大器的负极输入端与第一相变器电连接。

132.本技术中,均流电路可以对第一相变器和第二相变器输出的第一功率信号和第二功率信号做平均后得到均值信号。第三运算放大器可以确认第一功率信号小于均值信号后,减小第三比较器的第二端输入的参考信号的值,确认第一功率信号大于均值信号后,增加第三比较器的第二端输入的参考信号的值。

133.本技术中,第一导通计时器和第二导通计时器有具体的实现方式,下面以图12为例来说明第一导通计时器和第二导通计时器的具体工作过程。

134.图12是本技术提供的第一导通计时器和第二导通计时器的另一结构示意图。

135.请参阅图12,本技术中,可选的,第一导通计时器701包括开关901、开关902、电容903、均流电路904、运算放大器905、比较器906和触发器907;为了方便说明,图11中的第三开关模,801包括图12中的开关901和开关902,图12中的电容903即是图11中的第四电容802,图12中的比较器906即是图11中的第三比较器803,触发器907即是图11中的第三触发器804,均流电路904即是图11中的均流电路805,运算放大器905即是图11中的第三运算放大器806。

136.开关901的第一端与恒流源908的第一端电连接,开关901的第二端与外部电源vcc电连接,开关901的第三端与开关902的第一端和电容903的第一端电连接;开关902的第一端与电容903的第一端电连接,开关902的第二端与第一驱动电路702电连接,开关902的第三端接地;电容903的第二端接地;

137.均流电路904的输入端与第六开关703和第二相变器102电连接,均流电路904的输出端与运算放大器905电连接;

138.运算放大器905的输出端与比较器906的负极输入端电连接;

139.比较器906的正极输入端通过第六连接点与电容903的第一端和开关901的第三端电连接,比较器906的输出端与触发器907的第一输入端电连接;

140.触发器907的第二输入端与信号处理模块106的输出端电连接,触发器907的输出端与第一驱动电路702电连接。

141.可选的,第二导通计时器包括开关909、开关910、电容911、均流电路905、运算放大器912、比较器913和触发器914;

142.开关909的第一端与恒流源908的第一端电连接,开关909的第二端与外部电源vcc电连接,开关909的第三端与开关910的第一端和电容911的第一端电连接;开关910的第一端与电容911的第一端电连接,开关910的第二端与第二驱动电路706电连接,开关910的第三端接地;

143.电容911的第二端接地;

144.均流电路904的输入端与第八开关707和第一相变器101电连接,均流电路904的输出端与运算放大器912电连接;

145.运算放大器912的输出端与比较器913的负极输入端电连接;

146.比较器913的正极输入端通过第七连接点与电容911的第一端和开关609的第三端电连接,比较器913的输出端与触发器914的第一输入端电连接;

147.触发器914的第二输入端与多项控制器103的输出端电连接,触发器914的输出端与第二驱动电路706电连接。

148.本技术中,信号处理模块106向第一导通计时器701输出脉冲信号m,则第一导通计时器701通过触发器907的第二输入端接收脉冲信号m,触发器907输出高电平信号,即信号ton_102中的高电平部分,该高电平部分可以控制第一驱动电路702使第六开关703闭合,第七开关704断开。

149.本技术中,恒流源908控制开关901与开关909闭合,外部电源vcc通过开关901与开关909向电容903和电容911充电。若第六开关703处于断开状态,第七开关704处于闭合状态,则开关902会接到控制信号闭合,则电容903两端的电压为0,比较器906的正极采集到的电容903处的电压为0。比较器906负极采集到的参考电压的值大于比较器906正极处采集到的电容903的电压,比较器906不会发生反转。若第六开关703处于闭合状态,第七开关704处于断开状态,则开关902会接到控制信号断开,开关901闭合,外部电源向电容903充电。则电容903两端的电压逐渐上升,当比较器906负极采集到的参考电压的值小于比较器906的正极处采集到的电容903的电压时,比较器906发生反转,比较器906向触发器907的第一输入端输出高电平信号。则触发器907的输出端输出低电平信号,即输出端输出的ton_102中的低电平部分,该低电平部分可以控制第一驱动电路702使第六开关703断开,第七开关704闭合。

150.本技术中,相类似的,多项控制器103向第二导通计时器705输出脉冲信号n,则第二导通计时器705通过触发器914的第二输入端接收脉冲信号n,触发器914输出高电平信号,即信号ton_103中的高电平部分,该高电平部分可以控制第二驱动电路706使第八开关707闭合,第九开关708断开。

151.本技术中,恒流源908控制开关909闭合,外部电源vcc通过开关909向电容911充电。若第八开关707处于断开状态,第九开关708处于闭合状态,则开关610会接到控制信号闭合,则第七电容两端的电压为0,比较器913的正极采集到的电容911处的电压为0。比较器913的负极采集到的参考电压的值大于比较器913正极处采集到的电容911的电压,比较器913不会发生反转。若第八开关707处于闭合状态,第九开关708处于断开状态,则开关910会接到控制信号断开,则电容911两端的电压逐渐上升,当比较器913负极采集到的参考电压的值小于比较器913正极处采集到的电容911的电压时,比较器913发生反转,比较器913向触发器914的输入端输出高电平信号。则触发器914的输出端输出低电平信号,即输出端输出的ton_103中的低电平部分,该低电平部分可以控制第二驱动电路706使第八开关707断开,第九开关708闭合。

152.本技术中,均流电路采904集第一相变器中的第六开关703处的电流i_102与第二相变器中的第八开关707处的电流i_103,进而通过i_102和i_103获取第一相变器和第二相变器输出电流平均之后的均值电流p,并将该均值电流p分别输入运算放大器905和运算放大器912的正极输入端。若运算放大器905的负极输入端输入的电流i_102小于该均值电流p,则运算放大器906会增加输出端向比较器906的负极输入端输入的参考电压eao1的值,则比较器906正极需要更大的电压才可以使比较器906发生反转,比较器906反转的速度减缓,比较器906的输出端输出高电平信号的时间延长,第六开关703处的电流i_102会增大。同理,若运算放大器905的负极输入端输入的电流i_102大于该均值电流p,则运算放大器905

会减小输出端向比较器906的负极输入端输入的参考电压的值eao2,则比较器906正极输入更小的电压就可以使比较器906发生反转,比较器906反转的速度加快,比较器906的输出端输出高电平信号的时间缩短,第六开关703处的电流i_102会减小。同理可知,通过均流电路904、运算放大器912和比较器913调节第八开关707处电流i_103的方式与上述调节第六开关703处电流i_102的方式相类似,具体此处不做赘述。

153.本技术中,均流电路904具有具体的实现方式,下面的实施例将详细的阐述均流电路904的一种可能的实现方式。

154.图13是本技术提供的一种均流电路的一结构示意图。

155.请参阅图13,本技术中,均流电路904包括第一采样电路1001、第二采样电路1002、滤波器1003、滤波器1004、滤波器1005和滤波器1006,其中,滤波器1004和滤波器1006有共同的节点。

156.同理,为了方便说明,图13中的运算放大器1007和图12中的运算放大器905以及图11中的运算放大器806是同一放大器。

157.可选的,滤波器1003至滤波器1006可以是rc滤波器,也可以是其他滤波器,具体此处不做限定,图13仅以rc滤波器为例进行说明。

158.第一采样电路1001的输入端与第六开关703电连接,第一采样电路1001的第一输出端与滤波器1003的输入端电连接,第一采样电路1001的第二输出端与滤波器1004的输入端电连接。

159.滤波器1003的输出端与运算放大器1007的负极输入端电连接。

160.滤波器1004的输出端与运算放大器1007的正极输入端和运算放大器1008的正极输入端电连接。

161.第二采样电路1002的输入端与第八开关307电连接,第二采样电路1002的第一输出端与滤波器1005的输入端电连接,第二采样电路1002的第二输出端与滤波器1006的输入端电连接。

162.滤波器1005的输出端与运算放大器1008的负极输入端电连接。

163.滤波器1006的输出端与运算放大器1007的正极输入端和运算放大器1008的正极输入端电连接。

164.本技术中,第一采样电路1001采集到第六开关处的电流i_102,第一采样电路输出电流i_102,滤波器1003对电流i_102滤波后输入运算放大器1007的负极输入端。第二采样电路采集到第八开关307处的电流i_103,第二采样电路1002输出电流i_103,滤波器1005对电流i_103滤波后输入运算放大器1008的负极输入端。第一采样电路1001向滤波器1004输出电流i_102,滤波器1004对电流i_102滤波。由于滤波器1004的输出端与滤波器1006的输出端电连接,则滤波器1004输出的电流与滤波器1006输出的电流在j点与k点处均流,即j点和k点处向运算放大器1007和运算放大器1008输出的电信号p为电流i_102与电流i_103平均后的电信号p(均流信号)。若运算放大器1007的负极输入端输入的电流i_102的值小于电信号p的值,则运算放大器1007增加输出的电信号eao1的值。反之,若运算放大器1007的负极输入端输入的电流i_102的值大于电信号p的值,则运算放大器1007减小输出的电信号eao1的值。同理可知,若运算放大器1008的负极输入端输入的电流i_103的值小于电信号p的值,则运算放大器1008增加输出的电信号eao2的值。反之,若运算放大器1008的负极输入

端输入的电流i_103的值大于电信号p的值,则运算放大器1008减小输出的电信号eao2的值。

165.本技术中,cot并联电路中包括的滤波模块具有具体的实现方式,该种具体的实现方式将在下面的实施例中进行说明。

166.图14是本技术提供的cot多项并联电路的结构示意图。

167.请参阅图14,本技术中,可选的,滤波模块104可以包括第一电感1101、第二电感1102和第三电容1103。

168.第一电感1101的第一端与第六开关703的第三端和第七开关704的第二端电连接,第一电感1101的第二端与第二电感1102的第一端以及第三电容1103的第一端电连接;

169.第二电感1102的第一端有第八开关707的第三端和第九开关708的第四端电连接,第二电感1102的第二端与第三电容1103的第一端电连接;

170.第三电容1103的第二端接地。

171.本技术中,若第六开关703闭合,外部电源vcc可以通过第六开关703向第一电感1101充电。若第六开关703断开,第七开关704闭合,则第一电感1101向滤波模块104的输出端和第七开关704放电,第三电容1103对第一电感1101输出的电流进行滤波,以便滤波模块104可以输出稳定无波纹的功率信号。同理可知,若第八开关707闭合,外部电源vcc可以通过第八开关707向第二电感1102充电。若第八开关707断开,第九开关708闭合,则第二电感1102向滤波模块104的输出端和第九开关708放电,第三电容1103对第二电感1102输出的电流进行滤波,以便滤波模块104可以输出稳定无波纹的功率信号。

172.本技术中,可选的,若cot并联电路中包括更多的相变器,则滤波模块104中可以包括更多的电感,其他更多电感的连接方式与工作方式与图13实施例中说明的第二电感1102相类似,具体此处不做赘述。

173.本技术中,上述实施例所提供的cot并联电路除了应用在电源设备上之外,还可以应用在其他产品上,如:车载电源、基站电源或者其他或者其他涉及到直流转直流交换控制的产品中。

174.以上,仅为本技术实施例的具体实施方式,但本技术实施例的保护范围并不局限于此。

175.以上对本技术实施例所提供的cot并联电路以及电源设备进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想。同时,对于本领域的一般技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1