一种用于反熔丝FPGA中隔离电路的闭环控制结构的制作方法

一种用于反熔丝fpga中隔离电路的闭环控制结构

技术领域

1.本发明涉及集成电路技术领域,特别涉及一种用于反熔丝fpga中隔离电路的闭环控制结构。

背景技术:

2.反熔丝fpga是一种高可靠可编程门阵列电路,具有非易失性、功耗低、集成度高、性能稳定等优点,广泛应用于高可靠、高保密性的军用和航空航天领域。由于其特殊的应用领域,国外此类电路往往对国内处于禁运状态,而且进行技术封锁。

3.由于反熔丝fpga的重要作用,国内开展了包括反熔丝fpga设计技术、测试技术、编程方法、编程器设计技术等关键技术的研究和技术攻关。

4.本发明给出了一种适用于反熔丝fpga中的隔离电路的闭环控制结构。

技术实现要素:

5.本发明的目的在于提供一种用于反熔丝fpga中隔离电路的闭环控制结构,以解决系统上电之后芯片响应速度和工作时序问题,降低系统功耗,减少电荷泵的输出纹波的同时避免电荷泵的输出纹波对系统电源的影响。

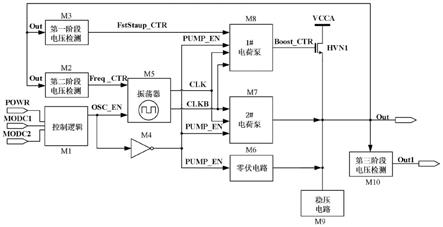

6.为解决上述技术问题,本发明提供了一种用于反熔丝fpga中隔离电路的闭环控制结构,包括控制逻辑模块m1、振荡器m5、反相器m4、1#电荷泵m8、2#电荷泵m7、零伏电路m6、nmos晶体管hvn1、稳压电路m9、第一阶段电压检测电路m3、第二阶段电压检测电路m2和第三阶段电压检测电路m10;控制逻辑模块m1的输出osc_en信号至振荡器m5和反相器m4,所述振荡器输出clk信号和clkb信号至1#电荷泵m8输入端和2#电荷泵m7输入端;所述反相器m4输出pump_en信号至零伏电路m6输入端、1#电荷泵m8输入端和2#电荷泵m7输入端;nmos晶体管hvn1的栅端连接所述1#电荷泵m8输出,漏端连接电源vcca,源端连接2#电荷泵m7输出、零伏电路m6输出和稳压电路m9输出;第一阶段电压检测电路m3、第二阶段电压检测电路m2和第三阶段电压检测电路m10的输入端均连接所述用于反熔丝fpga中隔离电路的闭环控制结构的输出out,所述第一阶段电压检测电路m3输出fststaup_ctr信号至1#电荷泵m8输入端,所述第二阶段电压检测电路m2输出freq_ctr信号至振荡器m5输入端,所述第三阶段电压检测电路m10输出逻辑模块使能信号out1。

7.可选的,所述零伏电路m6包括反相器g18和g19、nmos晶体管hvn2;反相器g18的输入端接入pump_en信号,输出端连接反相器g19的输入端,反相器g19的输出端连接nmos晶体管hvn2的源端,nmos晶体管hvn2的栅端连接反相器g19的输入端,nmos晶体管hvn2的漏端连接所述用于反熔丝fpga中隔离电路的闭环控制结构的输出out。

8.可选的,所述1#电荷泵m8包括nmos晶体管n20~n27、与门g29和g30、反相器g31和

g32;nmos晶体管n20的栅端连接pump_en信号,漏端连接电压vcca,源端连接nmos晶体管n21的栅端和漏端;nmos晶体管n21的源端连接nmos晶体管n22的栅端和漏端,nmos晶体管n22的源端连接nmos晶体管n26的漏端和nmos晶体管n27的漏端;nmos晶体管n23的栅端连接nmos晶体管n20的源端,源端和漏端共同连接与门g29的输出端,nmos晶体管n24的栅端连接nmos晶体管n23的源端,源端和漏端共同连接与门g30的输出端;nmos晶体管n25的栅端连接pump_en信号,漏端连接电源vcca,源端连接nmos晶体管n23的源端;nmos晶体管n26的栅端连接反相器g31的输出端,源端接地;nmos晶体管n27的栅端连接反相器g32的输出端,源端接地。

9.可选的,所述与门g29的输入端输入clk信号和fststaup_ctr信号;所述与门g30的输入端输入clkb信号和fststaup_ctr信号;所述反相器g31的输入端输入fststaup_ctr信号;所述反相器g32的输入端输入pump_en信号。

10.可选的,所述nmos晶体管hvn1和nmos晶体管hvn2均为高压nmos晶体管。

11.在本发明提供的用于反熔丝fpga中隔离电路的闭环控制结构中,具有以下有益效果:(1)采用1#电荷泵m8控制nmos晶体管hvn1开关通断,通过充电能力强的芯片工作电源vcca快速将隔离电路的栅电容上电压充电到芯片工作电源vcca电压值附近,解决了2#电荷泵m7在输出负载电容大的情况下升压慢的问题,从而解决了系统上电之后芯片响应的速度问题;(2)当2#电荷泵m7的输出电压值达到某一阈值时,关闭1#电荷泵m8,关断nmos晶体管hvn1的控制开关,防止2#电荷泵m7升压超过一定数值后对芯片电源vcca反向充电,同时避免2#电荷泵m7的输出纹波对系统电源的影响;(3)当2#电荷泵m7的输出电压值达到某一阈值时,振荡器m5降频工作,降低2#电荷泵m7的功耗,从而降低系统功耗;(4)当2#电荷泵m7的输出电压值达到某一阈值时,第三阶段电压检测电路m10输出信号out1翻转,反熔丝fpga逻辑模块的使能信号有效,解决反熔丝fpga逻辑模块的使能信号比隔离电路的控制信号先到问题,解决电路的工作时序问题,稳压电路m9启动,减少2#电荷泵m7的输出纹波。

附图说明

12.图1是反熔丝fpga中隔离电路将高电压和低电压进行隔离的示意图;图2是本发明提供的用于反熔丝fpga中隔离电路的闭环控制结构示意图;图3是本发明提供的用于反熔丝fpga中隔离电路的闭环控制结构中零伏电路的逻辑示意图;图4是本发明提供的用于反熔丝fpga中隔离电路的闭环控制结构中1#电荷泵的结构示意图;图5是本发明提供的用于反熔丝fpga中隔离电路的闭环控制结构中稳压电路的逻辑示意图。

具体实施方式

13.以下结合附图和具体实施例对本发明提出的一种用于反熔丝fpga中隔离电路的闭环控制结构作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

14.如图1,反熔丝fpga中隔离电路对高电压和低电压之间进行高低压隔离的示意图,隔离晶体管1和隔离晶体管2为反熔丝fpga器件内使用的隔离电路,隔离管控制电路负责隔离晶体管1和隔离晶体管2的打开与关闭。在反熔丝fpga编程时,隔离电路由0v电路负责关闭,对隔离晶体管1和隔离晶体管2两边的高电压和低电压进行隔离;反熔丝fpga编程完成后进入用户模式,隔离电路由电荷泵负责开启,打开数据进出逻辑模块的通道,也就是图1左边逻辑信号经过反熔丝fpga逻辑模块,再通过隔离晶体管1传输到布线网络,通过布线网络传输到隔离晶体管2,再将逻辑信号传输到右边的反熔丝fpga逻辑模块,最终实现用户定义逻辑。

15.如图2所示,所述用于反熔丝fpga中隔离电路的闭环控制结构包括控制逻辑模块m1、反相器m4、振荡器m5、1#电荷泵m8、2#电荷泵m7、零伏电路m6、nmos晶体管hvn1、稳压电路m9、第一阶段电压检测电路m3、第二阶段电压检测电路m2和第三阶段电压检测电路m10;控制逻辑模块输出osc_en信号至振荡器m5和反相器m4,所述振荡器m5输出clk信号和clkb信号至1#电荷泵m8和2#电荷泵m7;所述反相器m4输出pimp_en信号至零伏电路m6、1#电荷泵m8和2#电荷泵m7;nmos晶体管hvn1的栅端连接所述1#电荷泵m8的输出端,漏端连接电源vcca,源端连接2#电荷泵m7的输出端、零伏电路m6的输出端和稳压电路m9的输出端;第一阶段电压检测电路m3、第二阶段电压检测电路m2和第三阶段电压检测电路m10的输入端均连接所述用于反熔丝fpga中隔离电路的闭环控制结构的输出out,所述第一阶段电压检测电路m3输出fststaup_ctr信号至1#电荷泵m8的输出端,所述第二阶段电压检测电路m2输出freq_ctr信号至振荡器m5的输入端,所述第三阶段电压检测电路m10输出逻辑模块使能信号out1。

16.如图3所示,所述零伏电路m6包括反相器g18和g19、nmos晶体管hvn2;反相器g18的输入端接入pump_en信号,输出端连接反相器g19的输入端,反相器g19的输出端连接nmos晶体管hvn2的源端,nmos晶体管hvn2的栅端连接反相器g19的输入端,nmos晶体管hvn2的漏端连接所述用于反熔丝fpga中隔离电路的闭环控制结构的输出out。

17.如图4所示,所述1#电荷泵m8包括nmos晶体管n20~n27、与门g29和g30、反相器g31和g32;nmos晶体管n20的栅端连接pump_en信号,漏端连接电源vcca,源端连接nmos晶体管n21的栅端和漏端;nmos晶体管n21的源端连接nmos晶体管n22的栅端和漏端,nmos晶体管n22的源端连接nmos晶体管n26的漏端和nmos晶体管n27的漏端;nmos晶体管n23的栅端连接nmos晶体管n20的源端,源端和漏端共同连接与门g29的输出端,nmos晶体管n24的栅端连接nmos晶体管n23的源端,源端和漏端共同连接与门g30的输出端;nmos晶体管n25的栅端连接pump_en信号,漏端连接电源vcca,源端连接nmos晶体管n23的源端;nmos晶体管n26的栅端连接反相器g31的输出端,源端接地;nmos晶体管n27的栅端连接反相器g32的输出端,源端接地。所述与门g29的输入端输入clk信号和fststaup_ctr信号;所述与门g30的输入端输入clkb信号和fststaup_ctr信号;所述反相器g31的输入端输入fststaup_ctr信号;所述反相

器g32的输入端输入pump_en信号。

18.如图5所示,所述稳压电路m9包括nmos晶体管n31~n35;nmos晶体管n31的栅端和漏端均连接所述的用于反熔丝fpga中隔离电路的闭环控制结构,源端连接nmos晶体管n32的栅端和漏端;nmos晶体管n32的源端连接nmos晶体管n33的栅端和漏端;nmos晶体管n33的源端连接nmos晶体管n34的栅端和漏端;nmos晶体管n34的源端连接nmos晶体管n35的栅端和漏端,nmos晶体管n35的源端连接gnda信号。所述nmos晶体管n31~n35的衬底均连接地。

19.在反熔丝fpga编程时,控制逻辑模块m1的输出osc_en=1,作为电荷泵的时钟产生模块的振荡器m5禁止工作;反相器m4的输出pump_en=0,1#电荷泵m8和2#电荷泵m7都禁止工作;由于1#电荷泵m8禁止工作,由图4和图2可知,1#电荷泵m8的输出为0v,高压nmos晶体管hvn1的控制为0v,nmos晶体管hvn1禁止工作,所以nmos晶体管hvn1的输出为高阻态;由图3可知,由于pump_en=0,零伏电路m6的输出为0v;由图5可知,由于图2中所述用于反熔丝fpga中隔离电路的闭环控制结构的输出out信号没有高电压输出,稳压电路m9的输出是高阻态。所以在反熔丝fpga编程时,图2中的所述用于反熔丝fpga中隔离电路的闭环控制结构的输出out=0v,图1中的隔离晶体管1和隔离晶体管2都处于关闭状态,将隔离晶体管1和隔离晶体管2两边的高电压和低电压进行高低压隔离,提升反熔丝fpga可靠性。

20.反熔丝fpga编程完成后进入用户模式,隔离电路由电荷泵开启。如图2,在用户模式下,控制逻辑模块m1的输出osc_en=0,反相器m4输出pump_en=1,作为电荷泵的时钟产生模块的振荡器m5的使能工作,1#电荷泵m8和2#电荷泵m7同时启动工作;由于pump_en=1,由图3可知,零伏电路m6的输出为高阻态。

21.如图4,在用户模式下,1#电荷泵m8的级数决定了1#电荷泵m8输出可以瞬时达到高于vcca的电压,从而将图2中高压nmos晶体管hvn1快速开启,nmos晶体管hvn1通过充电能力强的芯片工作电源vcca快速将隔离电路的栅电容上电压充电到芯片工作电源vcca电压值vcca附近,解决2#电荷泵m7在输出负载电容大的情况下升压慢的问题,解决系统上电之后芯片响应速度问题。

22.如图2,在用户模式下,当2#电荷泵m7输出超过芯片工作电源vcca电压值vcca时,第一阶段电压检测电路的输出翻转,通过第一阶段电压检测电路的输出关闭1#电荷泵,1#电荷泵m8停止工作,由图4可知1#电荷泵m8输出为0v,通过1#电荷泵m8关断nmos晶体管hvn1的控制开关,防止2#电荷泵m7升压超过一定数值后对芯片电源反向充电,同时避免2#电荷泵m7输出纹波对系统电源的影响。

23.如图2,在用户模式下,当2#电荷泵m7输出满足隔离电路控制需求值时(根据设计需求设定),第二阶段电压检测电路的输出翻转,通过第二阶段电压检测电路的输出控制电荷泵的时钟产生模块(即振荡器m5)的输出频率,振荡器m5降频工作,降低2#电荷泵m7的功耗,降低系统功耗。

24.如图2,在用户模式下,当2#电荷泵m7的输出达到一定数值(根据设计需求设定),第三阶段电压检测电路m10的输出信号翻转,通过第三阶段电压检测电路m10的输出控制反熔丝fpga逻辑模块的使能信号,反熔丝fpga的使能信号有效,反熔丝fpga芯片进入工作状态,解决反熔丝fpga逻辑模块的使能信号比隔离电路的控制信号先到问题,解决电路的工作时序问题,同时稳压电路启动,减少2#电荷泵m7的输出纹波。

25.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发

明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1