一种抑制高频GaN功率器件dv/dt串扰的多电平驱动电路

一种抑制高频gan功率器件dv/dt串扰的多电平驱动电路

技术领域

1.本发明属于电力电子器件的驱动技术领域,具体涉及一种抑制高频gan功率器件dv/dt串扰的多电平驱动电路。

背景技术:

2.高频gan功率器件相比第一代半导体si功率器件具有更小的寄生电容,这使得其开关损耗进一步降低,且开关频率可达到mhz以上的级别,可有效降低磁性元件的体积,提高系统的变换效率和功率密度,因此被广泛应用于消费快充、汽车电子等功率变换领域。

3.由于开关速度快,gan功率器件漏源极之间的快速电压变化(dv/dt)常伴随在其直流高压电路应用中,这种dv/dt现象会在gan功率器件的栅极产生正向或负向串扰尖峰脉冲。此外,由于gan材料具有较高的电子迁移率,所以gan功率器件常应用在mhz以上级别的高频开关场合。目前商用gan功率器件的最小阈值电压约为0.8~1.1v,最小栅极安全负压仅为-4~-10v,开关频率可达10mhz以上。因此在高开关频率工况下,dv/dt正负串扰使高频gan功率器件在关断过程中极易出现误导通和反向击穿等问题,进而影响系统的高效可靠工作。

4.在已有抑制dv/dt串扰的多电平驱动方案中,包括但不限于高频gan功率器件驱动,基本技术路径主要包括:1)采用单个电源,多个控制信号,2)采用单个控制信号,多个电源(正电源、负电源和中间电平电源),3)采用单个电源,单个控制信号。

5.采用单个电源,多个控制信号的技术思路是借助电容电荷泵产生负压的原理,配合pwm控制信号产生驱动回路所需要的负电压,该思路在多电平驱动中仅需单个电压源,降低了设计成本,但辅助控制信号的引入增加了控制的复杂程度。采用单个控制信号,多个电源(正电源、负电源和中间电平电源)的技术思路是在高频gan功率器件关断期间通过辅助电路控制pmos管的通断,从而实现中间电平钳位,但多个电源的方式又增加了电路和板级设计的复杂程度及成本。采用单个电源,单个控制信号的技术思路是将上述两种方案的优势相结合,不仅能够抑制串扰同时电路设计简单,但在用以产生钳位中间电平控制信号的辅助电路中,通常采用的是rc延时电路的方案。

6.rc延时电路是利用电容充放电的电压变化波形控制pmos管的通断,进而实现中间电平的钳位。该电路虽然结构简单,但rc电路的电压变化缓慢,在已有方案中电平钳位的响应时间最快为100ns左右。对于具有高频开关优势的gan功率器件来说,100ns的响应速度会导致其在5mhz(t/2=100ns)及以上频率的开关应用中,仍然存在因负电平不能被及时抬升至零电平附近,同时叠加负向尖峰脉冲造成高频gan功率器件被反向击穿器件的风险。因此,采用rc延时电路产生中间电平钳位控制信号的方案难以发挥gan功率器件5mhz及以上频率的高频开关特性。

技术实现要素:

7.本发明的目的在于克服上述方案3)多电平驱动中所存在的问题,提出了一种改进

的、适用于gan功率器件5mhz及以上开关频率的多电平驱动电路。该电路不仅实现了方案3)单个电源和单个控制信号抑制dv/dt正负串扰的功能,而且借助低延迟的高速比较器产生用以控制pmos管通断的信号,实现了pmos管更快的开通速度,使多电平驱动适用于高频gan功率器件在5mhz及以上频率的开关应用中。此外,当该电路中的负压产生电路配合本发明所述比较器控制电路时,可稳定工作在更宽的工作频率范围内,使其可驱动的开关管包括但不限于高频gan功率器件,并具有降低驱动电路损耗的优势。

8.为实现上述目的,本发明采用的技术方案是:一种抑制高频gan功率器件dv/dt串扰的多电平驱动电路,所述驱动电路包括驱动信号选通电路、负压产生电路和比较器控制电路。所述驱动信号选通电路用于选通正负方波,以驱动gan功率器件,所述负压产生电路用于产生负电压,以防止gan功率器件关断期间的误导通,所述比较器控制电路用于实现中间电平钳位,以防止gan功率器件开通瞬间的反向击穿。本发明中间电平箝位响应速度更快,使得gan功率器件可安全工作在5mhz及以上开关频率,充分发挥gan功率器件高频应用的优势;负压产生电路结构简单且具有更宽的工作频率范围,使其可驱动的开关管包括但不限于高频gan功率器件;同时具有降低驱动电路损耗的优势。

9.进一步地,所述驱动信号选通电路,包括:pmos管m1和nmos管m2,其中所述pmos管m1的源极与半桥驱动ic的输出端相连,用于选通半桥驱动ic产生的正方波;所述nmos管m2的源极与负压产生电路的输出端相连,用于选通负压产生电路产生的负方波,所述pmos管m1的栅极与nmos管m2的栅极共同接地,用于为正负脉冲的选通做参考。

10.所述负压产生电路,包括:电容c1和肖特基二极管d1,其中所述电容c1的一端与半桥驱动ic的输出端相连,肖特基二极管d1的阴极与电路参考点相连,所述电容c1的另一端与肖特基二极管d1的阳极串联,且中间节点作为负压产生电路的输出端。

11.所述比较器控制电路,包括:高速比较器芯片u1、rc并联电路、限流电阻r1和r3、肖特基二极管d2和pmos管m3,其中所述rc并联电路的一端与高速比较器芯片u1的同相输入端相连,所述限流电阻r1和r3分别与高速比较器芯片u1的同相和反相输入端相连,所述pmos管m3的栅极与高速比较器芯片u1的输出端相连,漏极与肖特基二极管d3的阳极相连,所述肖特基二极管d3的阴极与被驱动高频gan功率器件的栅极相连。

12.需要说明的是,dv/dt现象存在的本质原因是应用直流电压高或器件开关速度快,因此,诸如sic mosfet、sic igbt等宽禁带器件尽管开关速度低于高频gan功率器件,但其应用的直流电压更高,dv/dt串扰问题依然是驱动中不可忽视的重要因素,所以本发明所述多电平驱动的拓扑及方法,适用范围包括所有在开关应用中存在dv/dt串扰影响的功率器件,而不局限于高频gan功率器件,并且具体电路参数由具体器件本身的特性所决定。

13.通过采用上述的技术方案,本发明的有益效果在于:

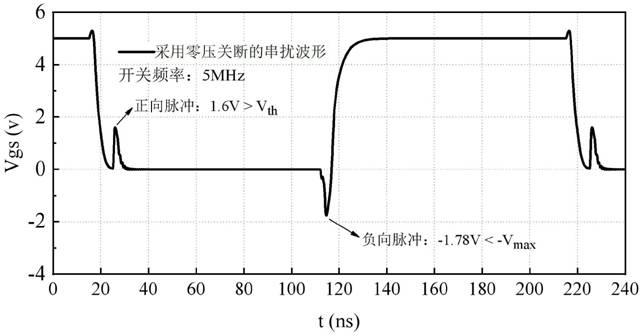

14.本发明提出了一种抑制高频gan功率器件dv/dt串扰的多电平驱动电路。该电路不仅实现了单个电源和单个控制信号抑制dv/dt正负串扰的功能,且具有以下优点:1)可抑制高频gan功率器件在5mhz及以上开关频率应用中的正负串扰影响,本发明所述比较器控制电路借助低延迟的高速比较器产生用以控制pmos管通断的信号,由于高速比较器的输出信号是一个快速跃变的方波信号,因此相对rc延时电路可实现pmos管更快的导通。经仿真验证,本发明实现了pmos管8ns的开通速度,相较于rc延时电路提高了十倍以上,可有效避免高频gan功率器件在5mhz及以上频率的开关应用中,因负电平不能及时抬起所造成高频gan

功率器件被反向击穿器件的风险;2)负压产生电路结构简单且具有更宽的工作频率范围,本发明所述负压产生电路仅由一个电容和一个肖特基二极管构成,结构更加简单,并可满足5mhz及以上开关频率应用的需要,而且当输出端接入本发明所述的比较器控制电路时,由于负载阻抗较大,电容所存储的负压能量难以快速泄放,在开关频率为百khz左右的低频应用中仍可稳定工作,因此具有更宽的工作频率范围,使其可驱动的开关管包括但不限于高频gan功率器件;3)可降低驱动电路损耗,本发明所述负压产生电路的输入端为半桥驱动ic产生的脉动的正压方波,所输出的负压并非恒定的负压,而是脉动的负压方波,且负电压仅在后级比较器控制电路和被驱动高频gan功率器件需要时才会产生,不需要时则几乎为零(很小pn结导通压降),相比恒定负压的电路而言,具有降低驱动电路损耗的优势。

附图说明

15.图1为本发明所述抑制dv/dt串扰的多电平驱动示意图

16.图2为本发明实施例中高频gan器件半桥应用示意图

17.图3为本发明实施例中半桥电路工作开关波形示意图

18.图4(a)-(b)为传统两电平驱动电路的栅源电压波形

19.图5为采用rc延时电路作控制电路的栅源电压波形

20.图6为采用本发明的高频gan功率器件栅源电压波形

21.图7为本发明所述负压产生电路所输出的脉动负压波形

具体实施方式

22.以下将结合附图和具体实施例对本发明作进一步地详细说明,以此来充分理解本发明如何解决实际工程中的技术问题,并实现相应技术目的的实施过程,最后据以实施。

23.同时,为了理解本发明且使本发明的上述目的、特征和优势更加显而易见,本文将在下文的阐述中结合附图和具体实施例对诸多细节进行详实阐述。但是,本发明可以通过许多不同的方式来实现,同时可以应用于任何存在dv/dt串扰的场合,并不局限于本文所列举的具体实施方式。因此,对本领域技术人员来说,可以在不违背发明内涵的情况下做出类似或相应的改进,因此本发明不受下面公开的具体实施例的限制。

24.本实施例提供一种基于高频gan功率器件的半桥dc-dc电路,其半桥应用拓扑如图2所示,包括上桥臂电路和下桥臂电路,本发明所述抑制高频gan功率器件dv/dt串扰的多电平驱动电路应用于下桥臂电路中,上桥臂电路采用传统驱动方式。

25.下桥臂电路中,如图2所示,本发明所述抑制高频gan功率器件dv/dt串扰的多电平驱动电路,包括驱动信号选通电路、负压产生电路和比较器控制电路。

26.进一步地,所述驱动信号选通电路,包括:pmos管m1和nmos管m2,其中所述pmos管m1的源极与半桥驱动ic的输出端相连,用于选通半桥驱动ic产生的正方波;所述nmos管m2的源极与负压产生电路的输出端相连,用于选通负压产生电路产生的负方波,所述pmos管m1的栅极与nmos管m2的栅极共同接地,用于为正负脉冲的选通做参考。

27.所述负压产生电路,包括:电容c1和肖特基二极管d1,其中所述电容c1的一端与半桥驱动ic的输出端相连,肖特基二极管d1的阴极与电路参考点相连,所述电容c1的另一端与肖特基二极管d1的阳极串联,且中间节点作为负压产生电路的输出端。

28.所述比较器控制电路,包括:高速比较器芯片u1、rc并联电路、限流电阻r1和r3、肖特基二极管d2和pmos管m3,其中所述rc并联电路的一端与高速比较器芯片u1的同相输入端相连,所述限流电阻r1和r3的一端分别与高速比较器芯片u1的同相和反相输入端相连,所述pmos管m3的栅极与高速比较器芯片u1的输出端相连,漏极与肖特基二极管d3的阳极相连,所述肖特基二极管d3的阴极与被驱动高频gan功率器件的栅极相连。

29.下面结合图2所示的半桥电路和图3所示的开关波形,阐述本发明所述抑制高频gan功率器件dv/dt串扰的多电平驱动电路工作原理:

30.t1阶段,当半桥驱动ic的下半桥控制信号lo输出为高时,pmos管m1导通,nmos管m2关断,节点1输出为高电平,驱动电压驱动半桥电路下桥臂高频gan功率器件q2,同时经限流电阻r1以及rc并联电路r2和c2为电容c2充电,此时高速比较器同相输入端即节点3为高电平,反相输入端即节点4为很小的正电压(肖特基二极管d1的压降),高速比较器输出即节点5为零电平,pmos管m3关断,比较器控制电路不起作用。此时,电容c1左侧为高电平。当半桥驱动ic的下半桥控制信号lo输出为低时,电容c1右侧,即节点2突变为负电压,且负压深度可由电容c1的容值调节(负电压绝对值与电容容值大小成正比关系)。

31.t2阶段,pmos管m1关断,nmos管m2开启,选通节点2电压,使节点1同为负电压,并快速关断半桥电路下桥臂高频gan功率器件q2。此时,半桥开关节点6(sw)处存在一个由低电压至母线电压的快速升压过程,该电压变化在米勒电容cgd_l上产生一个大的米勒电流,流经栅源电容cgs_l和栅极电阻rg_l时将产生一个正向串扰电压。该串扰电压随着开关频率和母线电压的增加而增大。采用负压关断的方式可有效抑制该串扰电压的误导通影响。同时处在该阶段的电容c2经电阻r1、r2放电,节点4处电压由很小的正电压跃变为负电压,且该阶段节点3处电压始终高于节点4处的基准电压。

32.t3阶段,电容c2经过一段时间的放电后,节点3处电压低于节点4处电压,节点5处电压由零迅速跃变为节点2处的负电压,pmos管m3开启。肖特基二极管d2阳极电压为0v,高于d2阴极电压为负电压,此时d2导通,并将q2栅极电压由负电压钳位至负d2导通电压,进而可有效避免由反向串扰电压(开关节点6(sw)处的快速降压变化所引起)带来的反向击穿高频gan管的风险。节点5处电压的快速跃变大大提高了中间电平钳位的响应速度,并由仿真结果得到其时间仅为8ns,适用于5mhz及以上频率的开关过程。

33.t4阶段,半桥电路上桥臂高频gan功率器件q1关断,开关节点6(sw)处电压存在一个由母线电压至低电压快速降压过程,并产生一个反向串扰电压。在该反向串扰电压到来之前的t3阶段迅速将负电压钳位至中间电平,可有效避免负电压与反向串扰电压叠加所造成的高频gan功率器件反向击穿风险。

34.t5阶段,半桥驱动ic的下半桥控制信号lo输出为高,pmos管m1导通,nmos管m2关断,选通lo信号,节点1为高电平,驱动电压驱动半桥电路下桥臂高频gan功率器件q2,进入下一个开关周期。

35.为了表明本发明在高频gan功率器件的半桥dc-dc电路应用中对dv/dt引入正负串扰的抑制效果以及5mhz及以上级别开关频率应用的优势,本实施例基于ltspice仿真软件,采用gan systems公司提供的gs66502b 650v增强型gan器件模型,进行了半桥电路的仿真,并与传统的两电平驱动以及采用rc延时做控制电路的驱动分别进行了对比。本实施例中,直流母线电压v1为48v,输入滤波电容c_i为3.3uf,输出滤波电容c_o为60nf,功率电感l1为

2.4uh,负载电阻r_load为4.8ohm。所述多电平驱动电路中,pwm信号由fpga、mcu、dsp或信号发生器提供,半桥驱动ic为ti公司提供的高频gan功率器件专用半桥驱动芯片lmg1210,驱动信号选通电路中m1选用bss84,m2为si1555dl_n;负压产生电路中的电容c1为1.5nf,肖特基二极管d1选用bat46wj,115;比较器控制电路中高速比较器为maxim提供的max9203esa+,rc并联电路r2为1kohm、c2为15pf,限流电阻r1为120kohm、r3为30kohm,pmos管m3选用si9400dy,肖特基二极管d2选用bat46wj,115。

36.得到的仿真波形分别如图4、图5、图6和图7所示,对比图4和图6可知,传统两电平驱动的正负串扰脉冲尖峰分别达到了1.6v和-4.8v,1.6v的正向脉冲电压已然超过高频gan功率器件gs66502b的最低阈值电压1.1v。随着直流母线电压的增大和开关频率的提升,高频gan功率器件的dv/dt串扰问题会更加严重,负串扰电压脉冲带来的负击穿风险随之增大。当采用本发明所述的驱动电路时,正串扰电压脉冲的相对峰值被降低,同时加快了高频gan功率器件的关断速度,减小了关断损耗;负串扰电压脉冲被削弱,有效降低了高频gan功率器件反向击穿的风险。对比图5和图6可知,采用rc延时电路做控制电路的电平钳位时间大于80ns,在5mhz的开关频率下,该响应速度已经不能及时地将负电压钳位至零电平,从而将会增加高频gan功率器件被反向击穿的风险。当采用本发明所述的驱动电路时,低延迟的高速比较器响应时间迅速,中间电平的钳位时间仅为8ns,相比rc延时电路的钳位时间提高了至少10倍,这表明本发明所述多电平驱动电路可以有效工作在高达10mhz以上的开关频率下,具有充分发挥gan功率器件高频特性的潜力,同时也为进一步减小电力电子设备体积、提高功率密度提供了可能。由图7可知,本发明所述负压产生电路仅在脉动正压为零,高频gan功率器件关断期间输出负压,而在脉动正压为正,高频gan功率器件导通期间输出为零,相比恒定负压电路方案,具有进一步降低驱动电路损耗的优势,提高系统变换效率。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1