一种多电压域开关控制电路的制作方法

1.本发明涉及多电压域传输控制,在一些特定电路中除了电源电压以外,还会有不同于电源电压值的一些电压,尤其是对高于电源电压的电压进行传输控制,需要合理设计电路。

背景技术:

2.一般情况下,集成电路芯片中会有1~2种电源电压,比如0.9~1.5v的逻辑电源电压,1.6~5.5v的模拟电源电压等,但是在一些特殊电路中会涉及到比电源电压高的电压值,比如通过charge pump产生10-20v的电压值,这样在一个芯片电路中连同电源电压就会产生几种不同的电压,形成了多电压域,不同电压域之间的互连控制就变的复杂了。为了避免在不同电压源之间产生不必要的漏电通路和耐压违反等问题,怎么利用较低的电源电压以最简单的时序合理控制高电压的传输,需要在电路设计时充分考虑各种情况。本发明在此背景下提出了一种在多电压域下进行控制传输不同电压的简单方便的电路结构,避免了复杂时序的控制,简化了电路设计。

技术实现要素:

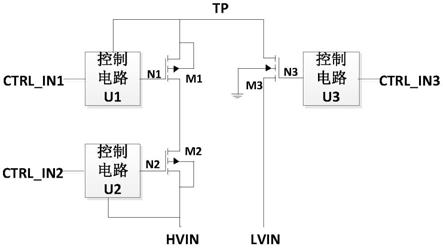

3.为实现多电压域的便利控制和传输,本发明提供一种多电压域传输控制电路,它利用mos开关管和电平移位器控制电路组成了两条传输通路,如附图1所示,根据控制信号ctrl_in1、控制信号ctrl_in2、控制信号ctrl_in3的控制时序来选择其中一条通路打开,实现了传输多电压域的功能。当控制信号ctrl_in1为高,控制信号ctrl_in2为低、控制信号ctrl_in3为低时,芯片引脚输入输出信号tp传输和芯片内部高电压输入输出信号hvin连通,可以进行高电压8~12v的传输。当控制信号ctrl_in1为低,控制信号ctrl_in2为高、控制信号ctrl_in3为高时,芯片引脚输入输出信号tp和芯片内部低电压输入输出信号lvin连通,可以进行低电压0~1.5v的传输。其中,由于传输高压时的mos管自身所承受的翻转导通耐压较低,所以传统结构的电平移位器无法直接在高电压域下进行翻转动作,再加上芯片引脚输入输出信号tp是芯片外部施加的电压(比如从外部测试机施加),芯片引脚输入输出信号tp上的电压施加时序与芯片电路内部时序很难对齐同步,这也大大限制了传统结构的电平移位器的使用,因此特意针对此点,本发明专门设计了一种跟电压施加时序完全无关的电平移位器控制电路,实现了便利的电压传输控制,大大简化了时序设计。

4.参考附图1、附图2及附图3,本发明电路由mos开关管m1、mos开关管m2、mos开关管m3、控制电路u1、控制电路u2、控制电路u3构成。

5.所述mos开关管均为普通5v工作电压的mos,其承受耐压大概12v,通过控制mos开关管的栅极电压即可控制mos开关管的导通和截止实现电压传输。

6.所述控制电路单元均为电平移位器,电平移位器的输入信号的幅度为低压逻辑控制信号,其幅度为0-1.5v,电平移位器的输出信号幅度可以为多种电压,取决于其连接的电源的电压范围,这样就通过电平移位器电路实现了低压控制逻辑信号幅度转换成高电压信

号幅度,实现对mos开关管栅极的控制。

7.由上述可知,本发明的优点在于利用此电路结构传输电压时,外部电压施加时序是任意的无任何制约,大大简化了对外部电压变化的特意时序控制,方便使用。

附图说明

8.图1是多电压域传输控制电路总体结构框图;

9.图2高压通路的电平移位器电路原理图;

10.图3低压通路的电平移位器电路原理图;

11.图4传统控制时序(a)与本发明控制时序(b)对比示意图。

具体实施方式

12.下面结合附图对本发明的技术方案作进一步详细说明。

13.图1为本发明多电压域传输控制电路总体结构框图,它展示了所述发明电路的基本结构,它由mos开关管和电平移位器控制电路构成。所述控制信号ctrl_in1、控制信号ctrl_in2和控制信号ctrl_in3,电压范围为0-1.5v;所述芯片引脚输入输出信号tp,电压范围为0-12v;所述芯片内部高电压输入输出信号hvin,电压范围为1-12v;所述芯片内部低电压输入输出信号lvin,电压范围为0-2.5v。在非工作状态,mos开关管m1,mos开关管m2,mos开关管m3均截止关闭,芯片引脚输入输出信号tp与芯片内部高电压输入输出信号hvin,芯片内部低电压输入输出信号lvin均不连通;在正常工作状态时,mos开关管m1/mos开关管m2组成的通路和mos开关管m3组成的通路,两条通路只有一条通路连通打开。当控制信号ctrl_in1为高,控制信号ctrl_in2为低、控制信号ctrl_in3为低时,mos开关管m1的栅极信号n1为低,mos开关管m2的栅极信号n2为低,mos开关管m3的栅极信号n3为低,mos开关管m1和mos开关管m2导通,mos开关管m3截止,芯片引脚输入输出信号tp传输和芯片内部高电压输入输出信号hvin连通;当控制信号ctrl_in1为低,控制信号ctrl_in2为高、控制信号ctrl_in3为高时,mos开关管m1的栅极信号n1为高,mos开关管m2的栅极信号n2为高,mos开关管m3的栅极信号n3为高,mos开关管m1和mos开关管m2截止,mos开关管m3导通,芯片引脚输入输出信号tp和芯片内部低电压输入输出信号lvin连通。这样就实现了电压传输功能,无需考虑芯片引脚输入输出信号tp的时序影响。

14.进一步说明如图2所示,所述电路本质上是一种电平移位器,由晶体管nm1、晶体管nm2、晶体管nm3、晶体管nm4、晶体管pm1、晶体管pm2、晶体管pm3、晶体管pm4、晶体管pm5、晶体管pm6组成,输入控制信号为ctrl_in,输出信号为out,电源信号为vdd,另一个电源为1.5v电源vdd15组成,输入控制信号ctrl_in幅度为逻辑电压幅度0~1.5v,输出信号out其电压幅度为2vth~12v,电源vdd15的电压为1.5v,电源vdd为高电压其幅度取决于外部连接的电源的电压范围,此电平移位器完成实现了1.5v电压幅度转换成高电压幅度的功能。图1中控制电路u1使用此电平移位器来实现。

15.进一步说明如图3所示,所述电路为电平移位器,由晶体管nm11、晶体管nm12、晶体管pm11、晶体管pm12和反相器i1组成,其输入信号ctrl_in的电压幅度为逻辑控制电压幅度0~1.5v,电源电压vdd电压为2.5v,此电平移位器完成实现了1.5v电压幅度转换成2.5v幅度的功能。图1中控制电路u2和控制电路u3使用此电平移位器来实现。

16.进一步说明如图4所示,4-a图是传统的时序控制方式,芯片引脚输入输出信号tp的电压在输入信号ctrl_in切换时需要特定电压值范围内(例如:1-5v),电路才能正常工作;4-b图是本发明的时序控制方式,芯片引脚输入输出信号tp的电压在输入信号ctrl_in切换时可以为任意值,无时序关系要求。这样就使时序设计简化,电路控制简单易行。

17.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的设计原则、技术方案之内,所做的任何修改、等同替换、改进等,均包含在本发明保护范围内。

技术特征:

1.一种多电压域开关控制电路,其特征在于,包括mos开关管m1、mos开关管m2、mos开关管m3、控制电路u1、控制电路u2、控制电路u3,其中:所述mos开关管m1:mos开关管m1的源极和衬底接芯片引脚输入输出信号tp,mos开关管m1的栅极接控制电路u1的输出信号n1,mos开关管m1的漏极接mos开关管m2的漏极;所述mos开关管m2:mos开关管m2的源极和衬底接芯片内部高电压输入输出信号hvin,mos开关管m2的栅极接控制电路u2的输出信号n2,mos开关管m2的漏极接mos开关管m1的漏极;所述mos开关管m3:mos开关管m3的源极接芯片引脚输入输出信号tp,mos开关管m3的衬底接地,mos开关管m3的栅极接控制电路u3的输出信号n3,mos开关管m3的漏极芯片内部低电压输入输出信号lvin;所述控制电路u1:输入端接控制信号ctrl_in1,输出端n1与mos开关管m1的栅极连接,电源端接芯片引脚输入输出信号tp;所述控制电路u2:输入端接控制信号ctrl_in2,输出端n2与mos开关管m2的栅极连接,电源端接芯片内部高电压输入输出信号hvin;所述控制电路u3:输入端接控制信号ctrl_in3,输出端n3与mos开关管m3的栅极连接。2.根据权利要求1所述的一种多电压域开关控制电路,其特征在于,所述控制电路u1,由晶体管nm1、晶体管nm2、晶体管nm3、晶体管nm4、晶体管pm1、晶体管pm2、晶体管pm3、晶体管pm4、晶体管pm5、晶体管pm6组成,输入控制信号为ctrl_in,输出信号为out,电源信号为vdd,另一个电源为1.5v电源vdd15,;晶体管nm1、晶体管nm3、晶体管pm1、晶体管pm3、晶体管pm5构成一条低电流通路,为晶体管pm2提供一个偏置电压;此条通路的具体连接关系为:晶体管nm1的源极和衬底接地,晶体管nm1的栅极和漏极接晶体管nm3的源极和衬底;晶体管nm3的源极和衬底接晶体管nm1的漏极和栅极,晶体管nm3的栅极接1.5v电源vdd15,晶体管nm3漏极接晶体管pm5的栅极和漏极;晶体管pm5的漏极和栅极接晶体管nm3的漏极,晶体管pm5的源极和衬底接晶体管pm3的栅极和漏极;晶体管pm3的漏极和栅极接晶体管pm5的源极和衬底,晶体管pm3的源极和衬底接晶体管pm1的栅极和漏极;晶体管pm1的漏极和栅极接晶体管pm3的源极和衬底,晶体管pm1的源极和衬底接电源vdd;晶体管nm2、晶体管nm4、晶体管pm2、晶体管pm4、晶体管pm6构成控制通路;此条通路的具体连接关系为:晶体管nm2的源极和衬底接地,晶体管nm2的栅极接输入控制信号ctrl_in,晶体管nm2的漏极接晶体管nm4的源极和衬底;晶体管nm4的源极和衬底接晶体管nm2的漏极,晶体管nm4的栅极接1.5v电源vdd15,晶体管nm4的漏极接晶体管pm6的栅极和漏极;晶体管pm6的栅极和漏极接晶体管nm4的漏极,晶体管pm6的源极和衬底接晶体管pm4的栅极和漏极;晶体管pm4的栅极和漏极接晶体管pm6的源极和衬底,晶体管pm4的源极和衬底接输出信号n1;晶体管pm2的漏极接输出信号n1,晶体管pm2的栅极接晶体管pm1的栅极和漏极,晶体管pm2的源极和衬底接电源vdd;控制信号ctrl_in为0时,输出信号n1输出高电平,控制信号ctrl_in为高电平时,输出信号n1输出一个2vth电平。3.根据权利要求1所述的一种多电压域开关控制电路,其特征在于,所述控制电路u2,由晶体管nm11、晶体管nm12、晶体管pm11、晶体管pm12和反相器i1构成,其输入控制信号为ctrl_in,输出信号为n2,电源为vdd;具体连接关系为:晶体管nm11的源极和衬底接地,晶体管nm11的栅极接输入控制信号ctrl_in,晶体管nm11的漏极接晶体管pm11的漏极和晶体管

pm12的栅极;晶体管pm11的漏极接晶体管nm11的漏极和晶体管pm12的栅极,晶体管pm11的源极和衬底接电源vdd,晶体管pm11的栅极接晶体管pm12的漏极和输出信号n2;晶体管nm12的源极和衬底接地,晶体管nm12的栅极接反相器i1的输出,晶体管nm12的漏极接晶体管pm12的漏极、晶体管pm11的栅极和输出信号n2;晶体管pm12的漏极接晶体管nm12的漏极、晶体管pm11的栅极和输出信号n2,晶体管pm12的栅极接晶体管nm11的漏极和晶体管pm11的漏极,晶体管pm12的源极和衬底接电源vdd。4.根据权利要求1所述的一种多电压域开关控制电路,其特征在于,所述控制电路u3的组成和实现与控制电路u2相同。

技术总结

本实用新型公开了一种多电压域开关控制集成电路,电路使用以1.5V为电源的输入信号来控制传输10V的高电压。工作时,此开关电路有两条传输通路,其中一条通路传输0~2.5V电压范围,另一条通路传输8~12V电压范围,此开关电路涉及多种不同的电压值,因此需要精确控制才能正常传输。本实用新型电路包括三个MOS开关管、三个开关控制电路:所述MOS开关管导通时可以传输正确的电压,关闭时电压不能传输为截止状态;所述开关控制电路为电平移位器功能的电路,其输出信号施加在MOS开关管的栅极来控制MOS开关管的导通或者关闭,本实用新型的优点在于采用此结构传输高电压时对高电压的时序无约束。无约束。无约束。

技术研发人员:许延华 陈艳 孟颖 白俊峰

受保护的技术使用者:北京中电华大电子设计有限责任公司

技术研发日:2021.11.12

技术公布日:2022/5/17

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1