一种低失调斩波运算放大器的制作方法

1.本实用新型涉及高精度运算放大器领域,尤其是指一种低失调斩波运算放大器。

背景技术:

2.斩波运算放大器(chopper amplifier)是一种基于斩波调制技术的低噪声、高精度放大器,主要应用在传感器系统中,用于前端传感器信号的放大,使之能够被后级的模拟系统精确识别。传感器是一种将某种物理量转换为电信号的元件,它有很多的种类,如温度传感器(热敏电阻、热电偶)、压电传感器(压电陶瓷)、光电传感器(光电二极管)、霍尔器件等等。尽管传感器的种类、形状、结构以及物理机理繁多,但其有一个共同的特点:传感器对于输入信号的响应(即传感器的输出信号)的幅度很小,通常不能直接使用,尤其是在有噪声的环境中。这就使得低噪声、低失调的高精度运放在此类系统中必不可少。

技术实现要素:

3.为解决上述技术问题,本实用新型的一种低失调斩波运算放大器,包含如下模块:振荡器模块、斩波开关模块、增益模块,所述的斩波开关模块包括有斩波开关ch1、ch2、cl1、cl2,所述的振荡器模块产生一个基本时钟信号,经分频器分频后产生两个不同频率的斩波频率f

ch

\f

cl

,输入信号经斩波开关cl1、ch1调制为ac信号送入增益模块,再由输出斩波开关ch2、cl2解调经过低通滤波器,即可得到精准放大的输入信号。

4.在本实用新型的一个实施例中,所述的斩波开关由振荡器产生的开关信号控制,其中的振荡器模块中采用的是张弛振荡器,该张弛振荡器包括恒流源i1和i2、可控开关switch1和switch2、高位比较器和低位比较器以及逻辑控制、电容c,恒流源i1设于vcc和可控开关switch1之间,恒流源i2设于接地和可控开关switch2之间,其中的电容c一端接地,另一端设于可控开关switch1和switch2、高位比较器和低位比较器之间,另外逻辑控制的部分与高位比较器和低位比较器输出端相连。

5.在本实用新型的一个实施例中,所述的增益模块由级联的运算放大器构成,增益模块采用的是三运放结构,第一级为增益级gm,第二级为跨阻r,第三级为共模补偿级以及消除前馈通路的米勒补偿。

6.在本实用新型的一个实施例中,所述的增益模块中两个放大器将差分输入信号施加在电阻反馈网络的输入端,该反馈网络为固定50增益,最终在输出端产生的输出电压为:v

out

=50*v

in

+v

ref

。

7.6.在本实用新型的一个实施例中,所述的斩波开关和增益模块中级联后的斩波放大器组成三级放大电路。

8.本实用新型的上述技术方案相比现有技术具有以下优点:本实用新型所述的通用的级联斩波运算放大器,电路实现一个级联斩波(nested-chopper)运放的功能,可以在一定频率范围内实现模拟信号的精确放大处理。电路基于bcd工艺设计制作,性能可靠,实用性强。

附图说明

9.为了使本实用新型的内容更容易被清楚的理解,下面根据本实用新型的具体实施例并结合附图,对本实用新型作进一步详细的说明。

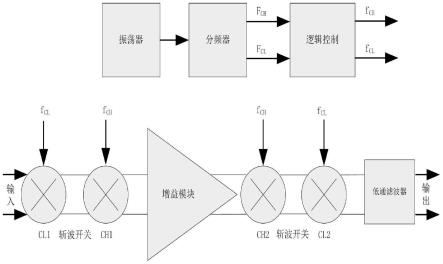

10.图1是本实用新型低失调斩波运算放大器的运行结构流程图;

11.图2是本实用新型所述放大器级联结构图;

12.图3是本实用新型所述振荡器模块的电路结构图;

13.图4是本实用新型所述斩波放大器整体电路结构。

具体实施方式

14.如图1所示,本实施例提供一种低失调斩波运算放大器,包含如下模块:振荡器模块、斩波开关模块、增益模块,所述的斩波开关模块包括有斩波开关ch1、ch2、cl1、cl2,所述的振荡器模块产生一个基本时钟信号,经分频器分频后产生两个不同频率的斩波频率f

ch

\f

cl

,输入信号经斩波开关cl1、ch1调制为ac信号送入增益模块,再由输出斩波开关ch2、cl2解调经过低通滤波器,即可得到精准放大的输入信号。

15.其中的振荡器模块,电路采用传统的张弛振荡器,通过周期性开关,对电容充放电,电容电压值输入比较器,通过设置比较器的阈值产生周期性振荡信号。斩波开关模块,开关由互补时钟信号控制,该频率称为斩波频率。增益模块由级联的斩波放大器构成,级联的斩波放大器,可以消除失调电压对输出的影响。

16.所述的斩波开关由振荡器产生的开关信号控制,其中的振荡器模块中采用的是张弛振荡器,如图3所示,该张弛振荡器包括恒流源i1和i2、可控开关switch1和switch2、高位比较器和低位比较器以及逻辑控制、电容c,恒流源i1设于vcc和可控开关switch1之间,恒流源i2设于接地和可控开关switch2之间,其中的电容c一端接地,另一端设于可控开关switch1和switch2、高位比较器和低位比较器之间,另外逻辑控制的部分与高位比较器和低位比较器输出端相连。

17.而进一步地,其工作原理为:刚上电时,电容电压vc为低,该电压输入至窗口比较器产生一个逻辑信号,控制开关1导通,开关2关断,即电流源对电容c进行充电,这时电容上的电压会不断上升,直至上升到高位比较器所设定的高阈值点vh;此时输出逻辑发生跳变,进而关断开关1,导通开关2,即电流源i2对电容c进行放电,这时电容电压会不断降低,直至降低到低位比较器所设定的v

l

,使得输出逻辑再次跳变,此时电路又进入充电状态,如此反复可在电容器上输出连续不断的振荡波形。

18.所述的增益模块由级联的运算放大器构成,增益模块采用的是三运放结构,第一级为增益级gm,第二级为跨阻r,第三级为共模补偿级以及消除前馈通路的米勒补偿。

19.如图2所示,所述的增益模块中两个放大器将差分输入信号施加在电阻反馈网络的输入端,该反馈网络为固定50(34db)增益,最终在输出端产生的输出电压为:v

out

=50*v

in

+v

ref

。

20.如图4所示,所述的斩波开关和增益模块中放大器组成三级放大电路,级联后的斩波放大器。其中失调电压更小,实现高精度信号放大功能。本实用新型低失调斩波放大器电路,能够完成微小信号的高精度、低失调放大。

21.与现有高精度放大器相比,本实用新型的低失调斩波放大器,失调电压更低,可以

级联多级斩波放大器,应用于传感器等高精度领域有很好的市场前景。

22.显然,上述实施例仅仅是为清楚地说明所作的举例,并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本实用新型创造的保护范围之中。

技术特征:

1.一种低失调斩波运算放大器,其特征在于,包含如下模块:振荡器模块、斩波开关模块、增益模块,所述的斩波开关模块包括有斩波开关ch1、ch2、cl1、cl2,所述的振荡器模块产生一个基本时钟信号,经分频器分频后产生两个不同频率的斩波频率f

ch

\f

cl

,输入信号经斩波开关cl1、ch1调制为ac信号送入增益模块,再由输出斩波开关ch2、cl2解调经过低通滤波器,即可得到精准放大的输入信号。2.根据权利要求1所述的低失调斩波运算放大器,其特征在于:所述的斩波开关由振荡器产生的开关信号控制,其中的振荡器模块中采用的是张弛振荡器,该张弛振荡器包括恒流源i1和i2、可控开关switch1和switch2、高位比较器和低位比较器以及逻辑控制、电容c,恒流源i1设于vcc和可控开关switch1之间,恒流源i2设于接地和可控开关switch2之间,其中的电容c一端接地,另一端设于可控开关switch1和switch2、高位比较器和低位比较器之间,另外逻辑控制的部分与高位比较器和低位比较器输出端相连。3.根据权利要求1所述的低失调斩波运算放大器,其特征在于:所述的增益模块由级联的运算放大器构成,增益模块采用的是三运放结构,第一级为增益级gm,第二级为跨阻r,第三级为共模补偿级以及消除前馈通路的米勒补偿。4.根据权利要求3所述的低失调斩波运算放大器,其特征在于:所述的增益模块中两个放大器将差分输入信号施加在电阻反馈网络的输入端,该反馈网络为固定50增益,最终在输出端产生的输出电压为:v

out

=50*v

in

+v

ref

。5.根据权利要求1所述的低失调斩波运算放大器,其特征在于:所述的斩波开关和增益模块中级联后的斩波放大器组成三级放大电路。

技术总结

本实用新型涉及一种低失调运算放大器,包括振荡器模块、斩波开关模块、增益模块。振荡器模块用于产生基本时钟信号,时钟信号经分频后变为两个不同频率的斩波信号,输入信号经斩波信号调制后,输入运算放大器,运算放大器级联后可以极大程度的降低输入失调电压,实现高精度放大。本实用新型设计的低失调斩波运算放大器,采用斩波调制技术,运放失调电压低至50uV。对比同类型的运算放大器,本文放大器的失调显著减小,开环增益达到130dB,具有较高增益的同时,保证了极小的失调漂移,用在传感器等微型电子设备中具有良好的应用前景。电子设备中具有良好的应用前景。电子设备中具有良好的应用前景。

技术研发人员:黄立朝 徐凯英 丁宁 章宇新

受保护的技术使用者:中国电子科技集团公司第五十八研究所

技术研发日:2022.05.18

技术公布日:2022/9/2

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1