用于时钟发射的嵌入式时刻接收器的制作方法

1.本发明涉及嵌入式时刻(etod)系统。更具体地,本发明涉及用于etod时钟恢复的接收器架构,该接收器架构使用编码时钟信息输出稳定时钟而不会引入额外噪声和漂移。

背景技术:

2.图1中示出了具有嵌入式时刻(etod)特征的典型系统。发射器10具有两个时钟参考输入(在附图标号12处的信号ref1和在附图标号14处的信号ref2)。

3.在以下描述中,时钟参考信号ref1被指定为正常本地参考时钟,并且时钟参考信号ref2以与诸如协调世界时间的时间标准同步的时钟信号(例如,1hz时钟信号)的形式提供更新的时刻信息。在附图标号40处的时钟输出out1被锁定到时钟参考信号ref1。图1中的附图标号52处的时钟输出out2是被锁定到时刻的时钟。

4.在附图标号12处呈现的时钟参考信号ref1和在附图标号14处呈现的时钟参考信号ref2均为50%占空比方波。时钟参考信号ref1和ref2的频率不需要彼此相关。在时钟参考输入ref1 12处呈现的时钟参考信号ref1被提供到相位捕获单元(pa)16,在该相位捕获单元处提取该时钟参考信号相对于发射器10内部的本地时钟的相位的时钟相位。在时钟参考输入ref2 14处呈现的时钟参考信号ref2被提供到相位捕获单元(pa)18,在该相位捕获单元处提取该时钟参考信号相对于发射器10内部的本地时钟的相位的时钟相位。

5.数字锁相环路(dppl0)20被锁相到ref1时钟参考信号ref1。该数字锁相环路的输出被呈现给时钟合成器22,该时钟合成器的输出因此被锁相到时钟参考信号ref1。dpll0 20的输出与相位捕获单元18的输出处的时钟参考信号ref2之间的相位差在减法器电路24中确定,并且在编码器26中编码。在编码器26的输出处的编码的相位差由调制器28用来通过改变来自dpll0 20的时钟合成器22的输出的占空比来调制时钟合成器22的输出,以在该调制器的输出处生成ref(编码的)信号。例如,可以使用25%占空比来表示

″

零

″

位,并且可以使用75%占空比来表示

″

一

″

数字位。调制器28的输出处的ref(编码的)信号也被锁相到时钟参考信号ref1。

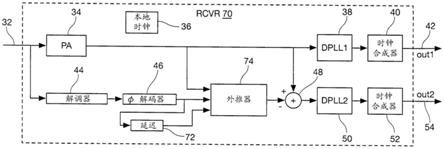

6.接收器30可被定位于距发射器10的随机距离处。在接收器端上,接收器30在输入32上接收来自发射器10中的调制器28的输出的ref(编码的)参考信号。ref(编码的)参考信号被呈现给相位捕获单元(pa)34,在该相位捕获单元处提取该ref(编码的)参考信号相对于接收器30内部的本地时钟36的相位的时钟相位。第一数字锁相环路(dppl1)38耦接到相位捕获单元34。该第一数字锁相环路的输出被呈现给时钟合成器40,该时钟合成器生成输出信号out1(在附图标号42处),该输出信号被锁相到所接收的ref(编码的)时钟参考输入信号。

7.编码在ref(编码的)信号中的时钟参考信号ref1与ref2之间的相位差信息由解调器44解调,并且在相位解码器46中解码。然后在减法器电路48中从ref(编码的)参考信号(其具有与ref1参考信号相同的相位)的相位中减去相位差信息,以获得被呈现给第二数字锁相环路dpll2 50的时钟参考信号ref2的(延迟)相位。dpll2 50的输出被呈现给时钟合成

器52,该时钟合成器生成输出信号out2(在附图标号54处),该输出信号被锁定到时钟参考信号ref2。因此,dpll2 50和时钟合成器52的组合表示用于生成恢复的第二信号的电路的实施方案。锁相电路(即,第一数字锁相环路(dppl1)38和第二数字锁相环路(dpll2)50)在本文被描述为数字锁相环路,应理解,这是锁相环路电路的特定非限制性实施方案。

8.在实际应用中,诸如在嵌入式时刻(etod)应用中,其中时钟参考信号ref1是用于同步输出(out1)42的时钟,并且时钟参考信号ref2包含关于在线路out2 54处输出的时刻的信息,需要一段时间将编码的数据从发射器10发射到接收器30。在本发明中,发射定义时钟参考信号ref1与ref2之间的相位差的数值中所包含的所有位所花费的时间t将在本文被称为解码帧。在发射器10中,在解码帧开始于时钟合成器22的输出处时计算相位差。取决于指定时钟参考信号ref1与ref2之间的相位差所需要的位数,表示时钟参考信号ref1与ref2信号之间的相位差的数值可能需要完全发射许多时钟周期。在接收器30中,相位解码器46开始于解码帧起始时间,并且相位差可以在延迟时间被完全解调,该延迟时间比解码帧起始时间晚td秒,其中td是完全解调以及解码相位差信息所花费的时间延迟。在载波时钟频率较低并且对时钟参考信号ref1与ref2之间的相位差进行编码所需要的位数较大以提供更好的相位差分辨率的情形下,此时间延迟td更长。此时间延迟td将增加第二数字锁相环路dpll2 50的锁定时间,并且在该时间延迟太长的情形下可导致第二dpll2 50变得不稳定。

9.图1的接收器30是在针对时钟参考信号ref1与ref2之间的相位差的编码器/解码器假设直接编码方法的情况下被使用。在使用直接编码方法的情况下,使用来自图1的相位解码器46的输出来通过在减法器电路48中从相位捕获单元34的输出中减去相位解码器46的输出来获得时钟参考信号ref2信号相位。

10.在大多数情况下,需要相位解码器46,这是因为可能使用间接编码方法(诸如增量调制编码)来进行更有效的数据发射,因为该间接编码方法需要发射比使用直接编码所需要的位数更少的位。解调器44的功能是提取表示编码的相位差的位并且将解调相位差数据呈现给相位解码器46。相位解码器46从解调器44获取解调位,并且从这些解调位生成是ref1信号与ref2信号之间的相位差的数。相位解码器46的详细功能取决于图1的编码器26所使用的调制方法,并且本领域普通技术人员将容易地能够为任何给定调制方法配置相位解码器46。

11.如先前所提及的,解码相位调整表示在发射器中的解码帧起始时间处的时钟参考信号ref1与ref2之间的相位差,并且在到达解码帧的开始之后在接收器处对相位差信息进行完全解码需要td秒的延迟。另外,pa 34的输出表示在样本时间相对于接收器30中的本地时钟的参考相位值,该本地时钟不与输入时钟周期(因此解码帧边界)对准。所有这些因素将在至第二dpll2 50的相位输入处引起噪声,该噪声将导致第二dpll2 50花费较长时间才被锁相。在一些情况下,如果时钟速率缓慢并且导致长解码帧周期,那么第二dpll2 50可能变得不稳定。最坏情况时间延迟td可以是一个解码帧周期。这是因为表示时钟参考信号ref1与ref2之间的相位差的所有数据可能需要发射整个解码帧周期。

技术实现要素:

12.根据本发明的方面,一种用于在接收单个输入信号的接收器中从该单个输入信号提取第一信号和第二信号的方法,该单个输入信号包括处于第一频率的第一信号,该第一

信号由表示处于第一频率的第一信号的第一相位与处于第二频率的第二信号的第二相位之间的编码的相位差的数据调制,该方法包括:接收单个输入信号;通过相对于在接收器内部的本地时钟的相位提取第一信号以及将该第一信号锁相来从所接收的单个输入信号生成恢复的第一信号;针对当前解码帧时间和紧接的前一解码帧时间两者,在解码帧时间期间对表示第一信号与第二信号之间的在该解码帧时间开始时的编码的相位差的数据进行解码;根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成该第一信号与该第二信号之间的相位差;从所生成的恢复的第一信号的相位中减去所生成的相位差以获得第二信号的恢复的第二相位;以及通过将处于第二频率的信号锁相在恢复的第二相位来生成恢复的第二信号。

13.根据本发明的方面,相对于在接收器内部的本地时钟的相位将该第一信号锁相包括在第一数字锁相环路中相对于在接收器内部的本地时钟的相位将第一信号锁相。

14.根据本发明的方面,通过将处于第二频率的信号锁相在恢复的第二相位来生成恢复的第二信号包括在第二数字锁相环路中相对于在接收器内部的本地时钟的相位将恢复的第二信号锁相。

15.根据本发明的方面,根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成该第一信号与该第二信号之间的相位差包括对表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据进行外推。

16.根据本发明的方面,针对当前解码帧时间和紧接的前一解码帧时间两者,在解码帧时间期间对表示第一信号与第二信号之间的在该解码帧时间开始时的编码的相位差的数据进行解码包括将解码的数据延迟一个解码帧时间的延迟时间。

17.根据本发明的方面,根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成该第一信号与该第二信号之间的相位差包括将该第一信号延迟解码帧时间,从所延迟的第一信号的相位中减去所生成的相位差,以及对表示在当前解码帧时间开始时的编码的相位差的解码的数据和在紧接的前一解码帧时间开始时的编码的相位差的解码的数据进行内插。

18.根据本发明的方面,根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成该第一信号与该第二信号之间的相位差包括对从第一信号的相位中减去的所生成的相位差进行低通滤波以获得第二信号的相位,以及对表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据进行线性外推。

19.根据本发明的方面,对从第一信号的相位中所减去的生成的相位差进行低通滤波以获得第二信号的相位包括使用基于乘法器的低通滤波器对从第一信号的相位中所减去的生成的相位差进行低通滤波。

20.根据本发明的方面,对从第一信号的相位中所减去的生成的相位差进行低通滤波以获得第二信号的相位包括使用基于加法器和移位器的低通滤波器对从第一信号的相位中所减去的生成的相位差进行低通滤波。

21.根据本发明的方面,一种用于从单个输入信号提取第一信号和第二信号的接收器包括:相位捕获单元和第一锁相环路电路,该相位捕获单元和第一锁相环路电路耦接到接收器的输入,以用于相对于在接收器内部的本地时钟的相位从单个信号提取第一信号以及将该第一信号锁相;相位解码器,该相位解码器用于针对当前解码帧时间和紧接的前一解码帧时间两者在解码帧时间期间对表示第一信号与第二信号之间的在该解码帧时间开始时的编码的相位差的数据进行解码;电路,该电路耦接到相位捕获单元和相位解码器,以用于根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成该第一信号与该第二信号之间的相位差;减法器电路,该减法器电路耦接到相位捕获单元和用于生成相位差的电路,以用于从恢复的第一信号的相位中减去所生成的相位差以获得第二信号的恢复的第二相位;和第二锁相环路电路,该第二锁相环路电路用于通过将处于第二频率的信号锁相在恢复的第二相位来生成恢复的第二信号。

22.根据本发明的方面,第一锁相环电路包括锁定到第一信号的数字锁相环路。

23.根据本发明的方面,用于通过将处于第二频率的信号锁相在恢复的第二相位来生成恢复的第二信号的第二锁相环路电路是被锁定到第二信号的数字锁相环路。

24.根据本发明的方面,解码器包括延迟电路,该延迟电路具有一个解码帧时间的延迟时间。

25.根据本发明的方面,其中耦接到相位捕获单元和解码器的用于根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成该第一信号与该第二信号之间的相位差的电路包括外推器电路。

26.根据本发明的方面,第一锁相环路电路包括通过第一信号延迟电路锁定到第一信号的数字锁相环路;耦接到相位捕获单元和解码器的用于根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成该第一信号与该第二信号之间的相位差的电路包括内插器电路,并且减法器电路通过第一信号延迟电路耦接到相位捕获单元。

27.根据本发明的方面,耦接到相位捕获单元和解码器用于根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成第一信号与第二信号之间的相位差的电路包括线性外推器电路。

28.根据本发明的方面,线性外推器电路直接耦接到解码器,并且线性外推器电路通过以下各项进一步耦接到解码器:延迟电路,该延迟电路具有输出;减法器电路,该减法器电路从解码器电路的输出中减去延迟电路的输出;和低通滤波器,该低通滤波器耦接在减法器电路与线性外推器之间。

附图说明

29.下面将参考实施方案和附图更详细地解释本发明,附图中示出:

30.图1是嵌入式时刻(etod)发射器和接收器的框图;

31.图2是示出根据本发明的方面的etod接收器的使用外推进行相位调整的部分的框图;

32.图3是示出根据本发明的方面的etod接收器的使用内插进行相位调整的部分的框图;

33.图4是示出根据本发明的方面的etod接收器的使用具有滤波的外推进行相位调整的部分的框图;

34.图5是示出可在根据本发明的etod接收器中采用的简单滤波器实施方式的框图;

35.图6是示出可在根据本发明的etod接收器中采用的无乘法器滤波器实施方式的框图;并且

36.图7是示出根据本发明的方面的用于从单个输入信号提取第一信号和第二信号的方法的流程图。

具体实施方式

37.本领域普通技术人员将认识到,以下描述仅是例示性的而非以任何方式进行限制。本领域技术人员将易于想到其他实施方案。

38.此类技术人员还将会知道,可以使用例如直接调制或增量调制来针对任何类etod编码、解码和调制方案来实现本发明。

39.根据本发明的方面,在耦接到发射器的接收器的输出处复制第一时钟参考信号ref1与呈现给发射器的输入的第二时钟参考信号ref2之间的相对相位。呈现若干技术,用于解决现有技术中呈现的延迟问题,而不会引起第二dpll2输出的额外漂移和噪声。

40.现在参见图2,示出了用于执行外推方法以在接收器中进行相位调整的接收器70的框图。将使用用于识别图1中的这些部件的相同附图标号来识别与图1的接收器30的部件相同的图2的接收器70的部件。接收器70接收线路32上的ref(编码的)信号,并且将该ref(编码的)信号呈现给pa 34和解调器44两者。解调器42的输出处的解调值驱动相位解码器46。相位解码器46的输出是当前解码帧起始时间的相位调整值。

41.图2示出用于对准相位调整和pa参考时钟相位的第一方法。如图1中所描绘的接收器区段中,相位解码器46将对当前解码帧起始时间的相位调整值进行解码。在时间t0,相位解码器46为由发射器10发送的当前解码帧提供解码相位调整值(p0)。延迟72引入一个解码帧延迟周期并且为先前解码帧提供解码相位调整值(p-1

)。pa 34在接收器本地时钟的样本时间(其为时间t0)提供关于信号ref1的参考相位信息。解码帧起始时间t

0-td以及时间t0的标识是接收器70已知的并且由该接收器提供。

42.在时间t0,相位解码器46提供在解码帧起始时间t

0-td的解码相位调整值(p0)。延迟72提供相位调整值(p-1

),该相位调整值是在先前解码帧起始时间t

0-t

d-t被解码的相位调整值,其中t是解码帧周期。

43.在外推器74中执行外推。外推器74具有从pa 34获取的输入,该输入提供从中提取td的时间信息t0和t

0-td。外推器74还具有从相位解码器46(p0)和延迟72(p-1

)获取的输入。外推器74将在时间t0的调整相位p

α

提供为:

[0044][0045]

因此,外推器74是电路的实施方案,该电路用于根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差

的解码的数据生成第一信号与第二信号之间的相位差。在减法器电路48中从由pa 34提供的参考相位中减去所调整的相位p

α

,以提供第二dpll250将锁定到的时钟参考信号ref2的等效相位。

[0046]

如果时钟参考信号ref2和ref1具有恒定相位偏移,p

0-p-1

将是恒定的,并且此方法提供用于在时间t0进行正确的相位调整的简单方式。然而,如果时钟参考信号ref1或时钟参考信号ref2在其中具有噪声或漂移,那么噪声或漂移将由于外推而增加。

[0047]

根据采样定理,已知,由于相位调整是每隔t(秒)进行,并且最大dpll采样率为1/t,因此最大噪声带宽或最高漂移频率必须小于奈奎斯特速率1/(2t)以便确保输出时钟被锁定到参考时钟。

[0048]

对于最坏情况,在td接近于t并且噪声或漂移的频率接近于1/(2t)时,输出时钟的噪声或漂移的量值是参考时钟的噪声或漂移的量值的两倍。

[0049]

现在参见图3,示出执行内插方法进行相位调整的接收器90。

[0050]

图3的电路具有一些与图2的电路的功能块相同的功能块,该功能块是使用图2中所使用的相同附图标号来识别。在图3的电路90中,从接收器输入32处的ref(编码的)信号导出的参考时钟相位在发送到第一dpll138之前在延迟92中被延迟一个解码帧周期,以使得可使用内插方法。

[0051]

在时间t0,到第二dpll2 50的输入是在时间t

0-t的pa 34的参考相位输出与由内插器94所提供的修改相位调整值之间的差值。相位解码器46提供在解码帧起始时间t

0-td的解码相位调整值(p0)。延迟72提供在先前解码帧起始时间t

0-t

d-t的相位调整值(p-1

)。由于t>td,因此需要获得在时间t

0-t的调整相位p

α

,该调整相位在p0与p-1

之间。使用在内插器94中执行的线性内插:

[0052][0053]

因此,内插器94是电路的实施方案,该电路用于根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成第一信号与第二信号之间的相位差。减法器电路48通过从由延迟电路92延迟的pa 34的信号输出中减去来自内插器94的内插相位差来提供时钟参考信号ref2的相位。

[0054]

图3中所示的方法将在适当时间提供准确的相位调整值而不增加参考时钟中的漂移和噪声。图3的方法的一个缺点是,参考路径中来自延迟电路92的额外延迟可能导致时钟未对准。在许多应用中,需要使发射器和接收器路径中的延迟最小化。此外,延迟可能影响系统中的dpll环路行为。

[0055]

现在参见图4,示出了接收器100,该接收器包括用于执行具有滤波的外推方法进行相位调整的电路。图4的方法是与低通滤波组合的线性外推。

[0056]

在图4的电路100中,线性外推器102将来自相位解码器46的当前解码相位调整值作为初始值(p0),并且将滤波后的相位调整差(α)作为斜率值(在由低通滤波器106滤波之后),该滤波后的相位调整差作为相位解码器46与延迟72的输出之间的差从两个相邻解码帧之间的减法器104获得。由相位解码器46输出的解码相位调整值是时钟参考信号ref1与ref2之间的相位差,该相位差包括两个时钟参考信号ref1与ref2之间的偏移和噪声(或漂

移),因为时钟参考信号ref1和ref2具有恒定频率偏移。两个相邻相位调整值之间的差对应于一个解码帧周期中两个时钟参考信号ref1与ref2之间的相位差,这是因为恒定频率偏移在不存在噪声的情况下是恒定值。低通滤波器104在一个解码帧周期中清除噪声并且输出滤波后的相位调整差(α)。

[0057]

在时间t0,在当前解码相位调整值(p0)表示在时间(t

0-td)的相位调整并且延迟相位调整值(p-1

)表示在时间(t

0-t

d-t)的相位调整的情况下,在时间t0的线性外推相位调整由线性外推器102计算为:

[0058]

p

α

=p0+α

×

td[0059]

其中α是滤波后的偏移p

0-p-1

。因此,线性外推器102是电路的实施方案,该电路用于根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据生成第一信号与第二信号之间的相位差。通过图5中所示的方法,仅使用由低通滤波器106提供的时钟参考信号ref1与ref2之间的稳定频率偏移进行外推以在时间t0获得正确的相位调整。根据以上方程式,可以观察到,处于p的噪声(或漂移)将与在时间t

0-td(解码帧起始时间)接收(解码)的处于p0的噪声(或漂移)相同,这是因为α上的噪声已被滤波。

[0060]

现在参见图5,图表示出了用滤波器系数β实现的低通滤波器电路110,该低通滤波器电路适合用作低通滤波器104。输入in(x)112在加法器114中与在输入116提供的常数β相加并且在乘法器118中乘以z-1

数字滤波器延迟电路120的输出,其中z-1

是数字滤波器的单位延迟,其中延迟时间与样本周期相同。z-1

电路120的输出在乘法器122中乘以常数1-β以产生低通滤波输出(在附图标号124处)以提供到线性外推电路106。

[0061]

滤波器输入(x)与输出(y)之间的滤波器响应是:

[0062][0063]

低通滤波器电路110滤除高频漂移和噪声。对于低频漂移和噪声,外推不会产生太多错误。滤波器系数β的一个合适选择是=1/64。

[0064]

现在参见图6,示出了无乘法器滤波器电路130,该无乘法器滤波器电路适合用作低通滤波器104。图6的滤波器电路130使用加法和移位运算代替乘法来实现。因此,在图6的滤波器130中使用右移6位移位器138来代替图6的滤波器110中的乘法器118。在图6的滤波器130中使用右移6位移位器140与加法器142的组合来代替图5的滤波器110中的乘法器122。

[0065]

现在参见图7,流程图示出了根据本发明的方面的用于从单个输入信号提取第一信号和第二信号的例示性方法150的流程图。该方法在附图标号152处开始。

[0066]

在附图标号154处,接收输入信号。在附图标号156处,通过提取第一信号以及将该第一信号锁相到本地时钟来生成恢复的第一输入信号。

[0067]

在附图标号158处,针对当前解码帧时间和紧接的前一解码帧时间两者,对表示第一信号与第二信号之间的在解码帧时间开始时的编码的相位差的数据进行解码。

[0068]

在附图标号160处,根据表示在当前解码帧时间开始时的编码的相位差的解码的数据和表示在紧接的前一解码帧时间开始时的编码的相位差的解码的数据,生成第一信号与第二信号之间的相位差。

[0069]

在附图标号162处,从所生成的恢复的第一信号的相位中减去所生成的相位差,以获得第二信号的恢复的第二相位。

[0070]

在附图标号164处,通过将处于第二频率的信号锁相在恢复的第二相位来生成恢复的第二信号。该方法在附图标号166处结束。

[0071]

本发明提供了具有用于使用单个发射线路发射两个时钟信号的接收器的系统。本发明非常适合于嵌入式时刻(etod)接收器设计。使用外推或内插来提供解码相位调整以改进dpll环路稳定性。外推与低通滤波器组合的使用可以改进dpll环路稳定性而不增加输出时钟漂移和噪声。

[0072]

虽然已经示出和描述了本发明的实施方案和应用,但是对于本领域技术人员来说显而易见的是,在不脱离本文的发明构思的情况下,可以进行比上述更多的修改。因此,除了所附权利要求的实质之外,本发明不受限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1