一种图像解码性能测试方法及装置与流程

1.本发明涉及电子设备测试技术领域,特别是涉及一种图像解码性能测试方法及装置。

背景技术:

2.电子设备通过硬件的图像处理单元进行图像解码,被称为图像硬解码,例如,上述图像处理单元可以为:gpu(graphics processing unit,图像处理器)、dsp(digital signal processor,数字信号处理器)、isp(image signal processor,图像信号处理器)、fpga(field

‑

programmable gate array,现场可编程门阵列)、asic(application specific integrated circuit,专用集成电路)等。

3.不同图像处理单元的性能不同,使得安装不同图像处理单元的电子设备对图像进行硬解码的速度不同,为了使得用户能够直观的了解电子设备进行硬解码的性能,需要对电子设备的图像解码性能进行测试。

技术实现要素:

4.本发明实施例的目的在于提供一种图像解码性能测试方法及装置,以测试电子设备的图像解码性能。具体技术方案如下:

5.第一方面,本发明实施例提供了一种图像解码性能测试方法,应用于电子设备中的处理器,所述电子设备安装有用于进行图像解码的图像处理单元和内存,所述内存包括:输入缓冲区和输出缓冲区,所述输入缓冲区用于存储所述图像处理单元待解码的图像,所述输出缓冲区用于存储所述图像处理单元解码后的图像,所述方法包括:

6.在所述图像处理单元处于运行状态、并以异步模式并行的对所述输入缓冲区中的图像进行图像解码的过程中,监测所述输出缓冲区是否存在图像;

7.在监测到所述输出缓冲区中存在图像后,将所述输出缓冲区中的图像移出所述输出缓冲区;

8.获得所述图像处理单元进行图像解码的累计时长,并获得向所述输出缓冲区输出解码后图像的累计数量;

9.根据所述累计时长以及累计数量,获得所述电子设备的图像解码性能的测试结果。

10.本发明的一个实施例中,所述获得所述图像处理单元进行图像解码的累计时长,包括:

11.检测所述图像处理单元第一次从所述输入缓冲区中获取图像的时刻,并开始计时;

12.检测所述图像处理单元最后一次向所述输出缓冲区写入解码后图像的时刻,并结束计时;

13.根据计时时长获得所述图像处理单元进行图像解码的累计时长。

14.本发明的一个实施例中,所述方法还包括:

15.在所述图像处理单元对所述输入缓冲区中的图像进行图像解码之前,从所述输入缓冲区中的图像中选择校验图像;

16.获得对所述校验图像进行解码得到的校验解码图像;

17.在所述获得所述电子设备的图像解码性能的测试结果之后,还包括:

18.根据所述校验解码图像与所述解码后图像间的对比结果,验证所述测试结果是否有效。

19.本发明的一个实施例中,在所述获得对所述校验图像进行解码得到的校验解码图像之后,还包括:

20.获得所述校验解码图像的校验值,作为第一校验值;

21.所述根据所述校验解码图像与所述解码后图像间的对比结果,验证所述测试结果是否有效,包括:

22.获得所述解码后图像的校验值,作为第二校验值;

23.检测所述第一校验值与第二校验值间的差异是否小于预设差异值;

24.若为是,确定所述测试结果有效。

25.本发明的一个实施例中,通过以下方式获得所述校验值;

26.从图像中选择用于进行校验值计算的目标像素点;

27.计算所选择的目标像素点的像素值的平均值;

28.获得包括各目标像素点的校验子值、且各校验子值按照预设顺序排列的校验值,其中,像素值大于等于所述平均值的目标像素点的校验子值为第一预设值,像素值小于所述平均值的目标像素点的校验子值为第二预设值,所述预设顺序为:预先设定的针对目标像素点位置的排列顺序。

29.第二方面,本发明实施例提供了一种图像解码性能测试装置,应用于电子设备中的处理器,所述电子设备安装有用于进行图像解码的图像处理单元和内存,所述内存包括:输入缓冲区和输出缓冲区,所述输入缓冲区用于存储所述图像处理单元待解码的图像,所述输出缓冲区用于存储所述图像处理单元解码后的图像,所述装置包括:

30.图像监测模块,用于在所述图像处理单元处于运行状态、并以异步模式并行的对所述输入缓冲区中的图像进行图像解码的过程中,监测所述输出缓冲区是否存在图像;

31.图像移出模块,用于在监测到所述输出缓冲区中存在图像后,将所述输出缓冲区中的图像移出所述输出缓冲区;

32.时长数量获得模块,用于获得所述图像处理单元进行图像解码的累计时长,并获得向所述输出缓冲区输出解码后图像的累计数量;

33.结果获得模块,用于根据所述累计时长以及累计数量,获得所述电子设备的图像解码性能的测试结果。

34.本发明的一个实施例中,所述时长数量获得模块,具体用于:

35.检测所述图像处理单元第一次从所述输入缓冲区中获取图像的时刻,并开始计时;

36.检测所述图像处理单元最后一次向所述输出缓冲区写入解码后图像的时刻,并结束计时;

37.根据计时时长获得所述图像处理单元进行图像解码的累计时长;

38.获得向所述输出缓冲区输出解码后图像的累计数量。

39.本发明的一个实施例中,所述装置还包括:

40.图像选择模块,用于在所述图像处理单元对所述输入缓冲区中的图像进行图像解码之前,从所述输入缓冲区中的图像中选择校验图像;

41.解码图像获得模块,用于获得对所述校验图像进行解码得到的校验解码图像;

42.结果验证模块,用于在所述结果获得模块获得所述测试结果之后,根据所述校验解码图像与所述解码后图像间的对比结果,验证所述测试结果是否有效。

43.本发明的一个实施例中,所述装置还包括:

44.校验值获得模块,用于在所述解码图像获得模块获得所述校验解码图像之后,获得所述校验解码图像的校验值,作为第一校验值;

45.所述结果验证模块,具体用于:

46.获得所述解码后图像的校验值,作为第二校验值;

47.检测所述第一校验值与第二校验值间的差异是否小于预设差异值;

48.若为是,确定所述测试结果有效。

49.本发明的一个实施例中,通过校验值确定模块获得所述校验值;

50.所述校验值确定模块,具体用于:

51.从图像中选择用于进行校验值计算的目标像素点;

52.计算所选择的目标像素点的像素值的平均值;

53.获得包括各目标像素点的校验子值、且各校验子值按照预设顺序排列的校验值,其中,像素值大于等于所述平均值的目标像素点的校验子值为第一预设值,像素值小于所述平均值的目标像素点的校验子值为第二预设值,所述预设顺序为:预先设定的针对目标像素点位置的排列顺序。

54.第三方面,本发明实施例提供了一种电子设备,包括处理器、通信接口、存储器和通信总线,其中,处理器,通信接口,存储器通过通信总线完成相互间的通信;

55.存储器,用于存放计算机程序;

56.处理器,用于执行存储器上所存放的程序时,实现第一方面任一所述的方法步骤。

57.第四方面,本发明实施例提供了一种计算机可读存储介质,所述计算机可读存储介质内存储有计算机程序,所述计算机程序被处理器执行时实现第一方面任一所述的方法步骤。

58.第五方面,本发明实施例还提供了一种包含指令的计算机程序产品,当其在计算机上运行时,使得计算机执行上述第一方面任一所述的方法步骤。

59.本发明实施例有益效果:

60.在电子设备安装有用于进行图像解码的图像处理单元和内存,上述内存包括:输入缓冲区和输出缓冲区,上述输入缓冲区用于存储图像处理单元待解码的图像,上述输出缓冲区,用于存储图像处理单元解码后的图像。电子设备中的处理器应用本发明实施例提供的方案测试电子设备的图像解码性能时,在图像处理单元处于运行状态、并以异步模式并行的对输入缓冲区中的图像进行图像解码的过程中,监测输出缓冲区中是否存在图像。在监测到输出缓冲区中存在图像后,将输出缓冲区中的图像移出输出缓冲区。获得图像处

理单元进行图像解码的累计时长,并获得向输出缓冲区输出解码后图像的累计数量。根据累计时长以及累计数量,获得电子设备的图像解码性能的测试结果。

61.由以上可见,由于在越短的累计时长内获得的越多的解码图像,说明电子设备的图像处理单元进行图像硬解码的效率越高,电子设备的图像解码性能越好,因此通过本发明实施例提供的方案能够实现对电子设备的图像解码性能的测试。并且,由于图像处理单元以异步模式并行的对图像进行图像解码,因此图像处理单元可以同时并行对多个图像进行图像解码,在进行图像解码的过程中图像处理单元绝大部分的图像处理资源可以被占用,因此通过本发明实施例提供的方案能够测试电子设备图像解码的最大性能。再者,由于在图像处理单元进行图像解码的过程中,会不断地将解码后图像写入输出缓冲区,若输出缓冲区的存储资源被占满,图像处理单元无法再将新生成的解码后图像输入输出缓冲区,则图像处理单元会暂停图像解码,等待输出缓冲区的存储资源释放。而本发明实施例提供的方案中将解码后图像移出输出缓冲区,可以释放解码后图像所占用的输出缓冲区的存储资源。因此在先生成的解码后图像不会占用输出缓冲区,不会影响图像处理单元对图像进行解码。使得所获得的累计时长中不包含由于解码后图像占用输出缓冲区造成的、图像处理单元等待输出缓冲区存储资源释放的时间,使得所得到的累计时长更准确,进而使得所获得的测试结果更准确。

附图说明

62.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

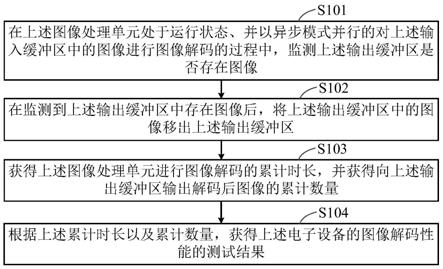

63.图1为本发明实施例提供的第一种图像解码性能测试方法的流程示意图;

64.图2为本发明实施例提供的第二种图像解码性能测试方法的流程示意图;

65.图3为本发明实施例提供的第三种图像解码性能测试方法的流程示意图;

66.图4为本发明实施例提供的第一种图像解码性能测试装置的结构示意图;

67.图5为本发明实施例提供的第二种图像解码性能测试装置的结构示意图;

68.图6为本发明实施例提供的第三种图像解码性能测试装置的结构示意图;

69.图7为本发明实施例提供的一种电子设备的结构示意图。

具体实施方式

70.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员基于本申请所获得的所有其他实施例,都属于本发明保护的范围。

71.为了测试电子设备的图像解码性能,本发明实施例提供了一种图像解码性能测试方法及装置。

72.本发明的一个实施例中,提供了一种图像解码性能测试方法,应用于电子设备中的处理器,上述电子设备安装有用于进行图像解码的图像处理单元和内存,上述内存包括:

输入缓冲区和输出缓冲区,上述输入缓冲区用于存储上述图像处理单元待解码的图像,上述输出缓冲区用于存储上述图像处理单元解码后的图像,上述方法包括:

73.在上述图像处理单元处于运行状态、并以异步模式并行的对上述输入缓冲区中的图像进行图像解码的过程中,监测上述输出缓冲区是否存在图像。

74.在监测到上述输出缓冲区中存在图像后,将上述输出缓冲区中的图像移出上述输出缓冲区。

75.获得上述图像处理单元进行图像解码的累计时长,并获得向上述输出缓冲区输出解码后图像的累计数量;

76.根据上述累计时长以及累计数量,获得上述电子设备的图像解码性能的测试结果。

77.由以上可见,由于在越短的累计时长内获得的越多的解码图像,说明电子设备的图像处理单元进行图像硬解码的效率越高,电子设备的图像解码性能越好,因此通过本发明实施例提供的方案能够实现对电子设备的图像解码性能的测试。并且,由于图像处理单元以异步模式并行的对图像进行图像解码,因此图像处理单元可以同时并行对多个图像进行图像解码,在进行图像解码的过程中图像处理单元绝大部分的图像处理资源可以被占用,因此通过本发明实施例提供的方案能够测试电子设备图像解码的最大性能。再者,由于在图像处理单元进行图像解码的过程中,会不断地将解码后图像写入输出缓冲区,若输出缓冲区的存储资源被占满,图像处理单元无法再将新生成的解码后图像输入输出缓冲区,则图像处理单元会暂停图像解码,等待输出缓冲区的存储资源释放。而本发明实施例提供的方案中将解码后图像移出输出缓冲区,可以释放解码后图像所占用的输出缓冲区的存储资源。因此在先生成的解码后图像不会占用输出缓冲区,不会影响图像处理单元对图像进行解码。使得所获得的累计时长中不包含由于解码后图像占用输出缓冲区造成的、图像处理单元等待输出缓冲区存储资源释放的时间,使得所得到的累计时长更准确,进而使得所获得的测试结果更准确。

78.下面再通过具体的实施例对本发明实施例提供的图像解码性能测试方法及装置进行说明。

79.参见图1,本发明实施例提供了第一种图像解码性能测试方法的流程示意图,应用于电子设备中的处理器,上述电子设备安装有用于进行图像解码的图像处理单元和内存,上述内存包括:输入缓冲区和输出缓冲区,上述输入缓冲区用于存储上述图像处理单元待解码的图像,上述输出缓冲区用于存储上述图像处理单元解码后的图像。

80.其中,上述图像处理单元可以为:gpu(graphics processing unit,图像处理器)、dsp(digital signal processor,数字信号处理器)、isp(image signal processor,图像信号处理器)、fpga(field

‑

programmable gate array,现场可编程门阵列)、asic(application specific integrated circuit,专用集成电路)等。

81.具体的,本发明实施例提供的方案用于测试电子设备的图像处理单元进行图像解码的性能,因此本发明实施例提供的方案适用于安装有图像处理单元的电子设备。若电子设备中未安装有图像处理单元,则可以直接将测试结果设置为0或无效,表示该电子设备中未安装有图像处理单元。其中,可以将电子设备进行图像解码的颜色格式设置为yuv420flexible、yuv444flexible或yuv420flexibl,由于以上述颜色格式进行的图像解码

需要通过图像处理单元完成,因此若电子设备不支持以上述颜色格式中的至少一种进行图像解码,可以认为上述电子设备中未安装图像处理单元。

82.另外,在上述图像处理单元进行图像解码的过程中,会从内存的输入缓冲区中获得待解码的图像进行图像解码,会将解码后的图像输出到输出缓冲区中。

83.具体的,上述输入缓冲区中包含输入缓存,每一输入缓存用于存储一张待解码的图像,上述输出缓冲区中包含输出缓存,每一输出缓存用于存储一张解码后的图像。上述输入缓冲区中包含的输入缓存的数量以及输出缓存区中包含的输出缓存的数量往往与图像处理单元中包含的计算核心的数量相同。上述待解码的图像在输入缓冲区中可以以二进制流的形式存储,上述解码后的图像在输出缓冲区中也可以以二进制流的形式存储。

84.此外,上述图像处理单元的延迟可以被设置为0,即无延迟,解码格式可以被设置为h.264,分辨率可以是4k,帧率可以是30fps,码率可以是20mbps。

85.上述方法包括以下步骤s101

‑

s104。

86.s101:在上述图像处理单元处于运行状态、并以异步模式并行的对上述输入缓冲区中的图像进行图像解码的过程中,监测上述输出缓冲区是否存在图像。

87.具体的,在上述电子设备中安装的操作系统为android操作系统的情况下,可以通过mediacodec工具控制图像处理单元进行图像解码。图像处理单元的状态可以包括停止状态、运行状态与释放状态,停止状态包括了三种子状态:未初始化子状态、配置子状态、错误子状态。运行状态在概念上会经历三种子状态:刷新子状态、运行子状态、流结束子状态。

88.在图像处理单元以异步模式对输入缓冲区中的图像进行图像解码的过程中,图像处理单元可以从配置子状态转换为运行子状态,也可以从刷新子状态转换为运行子状态。在通过mediacodec工具控制图像处理单元进行图像解码的情况下,可以调用mediacodec工具的start()函数将图像处理单元从配置子状态转换为运行子状态,或将图像处理单元从刷新子状态转换为运行子状态。

89.图像处理单元并行进行图像解码的数量可以为图像处理单元能够并行进行图像解码的最大数量,上述最大数量可以为图像处理单元中包含的计算核心的数量。

90.另外,图像处理单元也可以并行对预设数量张图像进行图像解码,若在上述情况下图像处理单元还拥有空闲的计算资源,则可以在上述预设数量的基础上提高并行进行图像解码的图像的数量,继续进行并行的图像解码,直至图像处理单元调用空闲的计算资源无法对更多数量的图像并行进行图像解码,从而确定上述最大数量。

91.再者,可以通过扫描上述输出缓冲区确定输出缓冲区中是否存在图像。

92.此外,上述图像可以为视频中的各个视频帧,则上述图像处理单元的解码形式可以被设置为视频解码。上述图像也可以为其他非视频帧的图像,上述图像的图像格式可以为yuv格式,也可以为其他格式。上述图像的图像内容可以相同,也可以不同。

93.s102:在监测到上述输出缓冲区中存在图像后,将上述输出缓冲区中的图像移出上述输出缓冲区。

94.具体的,由于图像处理单元在对图像进行图像解码之后,会将解码后图像输出至输出缓冲区,因此若监测到上述输出缓冲区中存在图像,说明图像处理单元完成了图像解码过程,得到了解码后图像。

95.另外,可以将上述输出缓冲区中的图像从输出缓冲区中直接删除,或者将输出缓

冲区中的图像从输出缓冲区中移出并存储至硬盘中,或对移出输出缓冲区的图像进行其他处理,本发明实施例对此不进行限定。

96.s103:获得上述图像处理单元进行图像解码的累计时长,并获得向上述输出缓冲区输出解码后图像的累计数量。

97.具体的,上述累计时长可以是图像处理单元将用于进行图像解码测试的各个图像均进行图像解码的累计时长,也可以为图像处理单元对预设图像数量张图像进行图像解码的累计时长。

98.另外,由于图像处理单元在成功对图像进行图像解码之后会将解码后图像输出至输出缓冲区,因此图像处理单元向上述输出缓冲区输出的解码后图像的累计数量即为图像处理单元成功进行图像解码的次数。

99.本发明的一个实施例中,可以通过以下步骤a

‑

步骤c获得图像处理单元进行图像解码的累计时长。

100.步骤a:检测上述图像处理单元第一次从上述输入缓冲区中获取图像的时刻,并开始计时。

101.具体的,可以通过第一检测线程检测图像处理单元是否从输入缓冲区中获取图像,在第一次检测到图像处理单元从输入缓冲区中获取图像的时刻调用计时器开始计时。

102.步骤b:检测上述图像处理单元最后一次向上述输出缓冲区写入解码后图像的时刻,并结束计时。

103.具体的,可以通过第二检测线程检测图像处理单元是否从输出缓冲区中获取图像,在最后一次检测到图像处理单元从输出缓冲区写入解码后图像的时刻结束计时器的计时。

104.步骤c:根据计时时长获得上述图像处理单元进行图像解码的累计时长。

105.由于上述计时时长是图像处理单元第一次从输入缓冲区中获取图像的时刻,也就是从图像处理单元开始进行图像解码的时刻开始,到图像处理单元最后一次向输出缓冲区写入解码后图像的时刻,也就是图像处理单元最后一次完成图像解码的时刻为止的时长,因此可以将上述计时时长作为上述累计时长。

106.也可以将上述计时时长减去预设的误差时长,得到上述累计时长。

107.本发明的另一个实施例中,可以检测上述图像处理单元第一次从上述输入缓冲区中获取图像的第一时刻,以及上述图像处理单元最后一次从上述输出缓冲区写入解码后图像的第二时刻,将上述第二时刻与第一时刻间的差值作为上述累计时长。

108.s104:根据上述累计时长以及累计数量,获得上述电子设备的图像解码性能的测试结果。

109.本发明的一个实施例中可以将累计数量除以累计时间,得到单位时间内电子设备的图像处理单元对图像进行解码的次数的计算结果,也就是fps(frames per second,每秒传输帧数)。上述计算结果越大,说明单位时间内电子设备的图像处理单元对图像进行解码的次数越高,说明图像处理单元的进行解码的效率越高,图像处理单元的性能越好,因此可以将上述计算结果作为上述测试结果。

110.也可以将累计数量除以累计时间得到的计算结果乘以预设系数,得到上述测试结果。

111.由以上可见,由于在越短的累计时长内获得的越多的解码图像,说明电子设备的图像处理单元进行图像硬解码的效率越高,电子设备的图像解码性能越好,因此通过本发明实施例提供的方案能够实现对电子设备的图像解码性能的测试。并且,由于图像处理单元以异步模式并行的对图像进行图像解码,因此图像处理单元可以同时并行对多个图像进行图像解码,在进行图像解码的过程中图像处理单元绝大部分的图像处理资源可以被占用,因此通过本发明实施例提供的方案能够测试电子设备图像解码的最大性能。再者,由于在图像处理单元进行图像解码的过程中,会不断地将解码后图像写入输出缓冲区,若输出缓冲区的存储资源被占满,图像处理单元无法再将新生成的解码后图像输入输出缓冲区,则图像处理单元会暂停图像解码,等待输出缓冲区的存储资源释放。而本发明实施例提供的方案中将解码后图像移出输出缓冲区,可以释放解码后图像所占用的输出缓冲区的存储资源。因此在先生成的解码后图像不会占用输出缓冲区,不会影响图像处理单元对图像进行解码。使得所获得的累计时长中不包含由于解码后图像占用输出缓冲区造成的、图像处理单元等待输出缓冲区存储资源释放的时间,使得所得到的累计时长更准确,进而使得所获得的测试结果更准确。

112.参见图2,为本发明实施例提供的第二种图像解码性能测试方法的流程示意图,与前述图1所示的实施例相比,上述方法还包括以下步骤s105

‑

步骤s106。

113.s105:在上述图像处理单元对上述输入缓冲区中的图像进行图像解码之前,从上述输入缓冲区中的图像中选择校验图像。

114.具体的,可以从上述输入缓冲区中包含的图像里随机选择预设数量个图像作为校验图像。

115.在上述图像为视频中的视频帧的情况下,可以从预设帧数区间内随机选择校验图像。其中,上述预设帧数区间可以为任意帧数区间,如第200帧到第400帧等。

116.s106:获得对上述校验图像进行解码得到的校验解码图像。

117.具体的,可以通过图像处理单元对上述校验图像进行解码,也可以通过cpu对上述校验图像进行解码。

118.本发明的一个实施例中,上述校验图像可以为png格式的图像。可以将校验图像解码为grb格式的二进制,并将所得到的grb格式的二进制转换为yuv格式。

119.与前述图1所示的实施例相比,在上述步骤s104之后,还包括以下步骤s107。

120.s107:根据上述校验解码图像与上述解码后图像间的对比结果,验证上述测试结果是否有效。

121.具体的,可以计算上述校验解码图像与解码后图像之间的相似度,若上述相似度大于预设相似度,则确定上述对比结果为校验解码图像与解码后图像相似,否则对比结果为校验解码图像与解码后图像不相似。

122.本发明的一个实施例中,可以通过现有技术中的图像相似度计算方法计算上述校验解码图像与解码后图像之间的相似度,在此不再赘述。

123.由于上述解码后图像是对校验图像进行图像解码之后得到的,校验解码图像也是对校验图像进行图像解码之后得到的,在理论上,对一张图像进行图像解码之后得到的图像相同。因此理论上上述校验解码图像与解码后图像之间的相似度较高。若上述校验解码图像与上述解码后图像之间相似,说明图像处理单元正常的对校验图像进行了图像解码,

可以认为上述图像处理单元在图像解码性能测试的过程中正常的进行了图像解码,测试结果有效。否则可以认为测试结果无效。

124.由以上可见,本发明实施例提供的方案在测试得到电子设备的图像解码性能的测试结果之后,还依据校验解码图像对图像处理单元在测试过程中是否正常的进行了图像解码进行了验证,也就是对测试结果的有效性进行了验证。只有在图像处理单元在测试过程中正常的进行图像解码的情况下,上述测试结果才有效,因此可以提高测试结果的准确度。

125.此外,为了防止上述验证测试结果是否有效的处理过程对图像解码的过程造成影响,上述步骤s107可以通过图像解码线程之外的其他线程实现。

126.参见图3,为本发明实施例提供的第三种图像解码性能测试方法的流程示意图,与前述图2所示的实施例相比,在上述步骤s106之后还包括以下步骤s108。

127.s108:获得上述校验解码图像的校验值,作为第一校验值。

128.具体的,可以将上述校验解码图像中各个像素点的像素值的平均值、和值、加权平均值等作为上述第一校验值。

129.另外,与前述图2所示的实施例相比,上述步骤s107可以通过以下步骤s107a

‑

s107b实现。

130.s107a:获得上述解码后图像的校验值,作为第二校验值。

131.具体的,可以将上述解码后图像中各个像素点的像素值的平均值、和值、加权平均值等作为上述第二校验值。

132.其中,为了保证相同的校验解码图像与解码后图像计算得到的校验值相同,计算得到第二校验值的方式与计算得到第一校验值的方式需要相同,例如,在上述第一校验值为上述校验解码图像中各个像素点的像素值的平均值的情况下,上述第二校验值同样为上述解码后图像中各个像素点的像素值的平均值。

133.s107b:检测上述第一校验值与第二校验值间的差异是否小于预设差异值。

134.具体的,可以计算第一校验值与第二校验值之间的差值的绝对值,作为上述第一校验值与第二校验值间的差异。也可以计算第一校验值与第二校验值之间的差值的绝对值与第一校验值之间的比值,作为第一校验值与第二校验值之间的差异。

135.若为是,则说明上述第一校验值与第二校验值之间的差异较小,也就是校验解码图像与解码后图像之间的差异较小,因此上述测试结果有效。

136.否则,则说明上述测试结果无效。

137.本发明的另一个实施例中,也通过以下步骤d

‑

步骤f获得上述校验值,包括第一校验值与第二校验值。

138.步骤d:从图像中选择用于进行校验值计算的目标像素点。

139.具体的,上述目标像素点可以为图像中任意位置处的预设像素点数量个像素点,也可以为图像中预设位置处的像素点。其中,上述预设像素点数量可以小于等于上述图像中像素点的总数。

140.在上述预设像素点数量小于像素点总数的情况下,在计算校验值的过程中仅选择部分目标像素点进行校验值计算,可以减少计算校验值的过程中所需的计算量,并缩小计算得到的校验值的大小。

141.其中,对于一张校验解码图像与该校验解码图像对应的解码后图像,在校验解码

图像中选择的目标像素点在校验解码图像中的位置与在解码后图像中选择的目标像素点在解码后图像中的位置相同,在校验解码图像中选择的目标像素点的数量与在解码后图像中选择的目标像素点的数量相同。

142.本发明的一个实施例中,可以将图像中除目标像素点之外的其他像素点去除,相当于仅保留上述目标像素点,从而可以缩小图像的尺寸。例如,可以将图像的尺寸缩小至8像素

×

8像素,共64个像素点。

143.步骤e:计算所选择的目标像素点的像素值的平均值。

144.具体的,上述像素值可以为亮度值、颜色值等,也可以为将上述目标像素点转换为灰度像素点之后得到的、上述目标像素点的灰度值,上述灰度值可以为64级灰度值。

145.步骤f:获得包括各目标像素点的校验子值、且各校验子值按照预设顺序排列的校验值。

146.其中,像素值大于等于上述平均值的目标像素点的校验子值为第一预设值。像素值小于上述平均值的目标像素点的校验子值为第二预设值。上述预设顺序为:预先设定的针对目标像素点位置的排列顺序。

147.具体的,上述第一预设值与第二预设值可以为数字、字符或其他值。例如,上述第一预设值可以为1,第二预设值可以为0。

148.上述预设排列顺序可以为:以目标像素点在图像中的横坐标值由小到大排列为优先,横坐标值相同的目标像素点按纵坐标值由小到大的顺序排列得到的顺序。

149.也可以为:以目标像素点在图像中的纵坐标值由小到大排列为优先,纵坐标值相同的目标像素点按横坐标值由小到大的顺序排列得到的顺序。

150.当然还可以为其他任意顺序。

151.另外,本发明实施例在通过以上步骤d

‑

步骤e获得上述第一校验值与第二校验值的情况下,可以分别检测第一校验值与第二校验值中位置相同的校验子值是否相同,若不相同的校验子值的数量小于预设位数,则确定第一校验值与第二校验值间的差异小于预设差异值。上述计算第一校验值与第二校验值中不同的校验子值的数量的过程可以被称为计算第一校验值与第二校验值之间的汉明距离。

152.具体的,可以分别确定第一校验值中第一位的校验子值与第二校验值的第一位的校验子值是否相同,再确定第一校验值中第二位的校验子值与第二校验值中第二位的校验子值是否相同,以此类推,从而确定第一校验值与第二校验值中不相同的校验子值的数量。

153.另外,上述预设位数可以为固定值,也可以为根据校验值中包含的校验子值的总数确定的位数,例如,上述预设位数可以为校验值中包含的校验子值的总数的10%等。

154.与前述图像解码性能测试方法相对应,参见图4,为本发明实施例提供的第一种图像解码性能测试装置的结构示意图,应用于电子设备中的处理器,所述电子设备安装有用于进行图像解码的图像处理单元和内存,所述内存包括:输入缓冲区和输出缓冲区,所述输入缓冲区用于存储所述图像处理单元待解码的图像,所述输出缓冲区用于存储所述图像处理单元解码后的图像,所述装置包括:

155.图像监测模块401,用于在所述图像处理单元处于运行状态、并以异步模式并行的对所述输入缓冲区中的图像进行图像解码的过程中,监测所述输出缓冲区是否存在图像;

156.图像移出模块402,用于在监测到所述输出缓冲区中存在图像后,将所述输出缓冲

区中的图像移出所述输出缓冲区;

157.时长数量获得模块403,用于获得所述图像处理单元进行图像解码的累计时长,并获得向所述输出缓冲区输出解码后图像的累计数量;

158.结果获得模块404,用于根据所述累计时长以及累计数量,获得所述电子设备的图像解码性能的测试结果。

159.由以上可见,由于在越短的累计时长内获得的越多的解码图像,说明电子设备的图像处理单元进行图像硬解码的效率越高,电子设备的图像解码性能越好,因此通过本发明实施例提供的方案能够实现对电子设备的图像解码性能的测试。并且,由于图像处理单元以异步模式并行的对图像进行图像解码,因此图像处理单元可以同时并行对多个图像进行图像解码,在进行图像解码的过程中图像处理单元绝大部分的图像处理资源可以被占用,因此通过本发明实施例提供的方案能够测试电子设备图像解码的最大性能。再者,由于在图像处理单元进行图像解码的过程中,会不断地将解码后图像写入输出缓冲区,若输出缓冲区的存储资源被占满,图像处理单元无法再将新生成的解码后图像输入输出缓冲区,则图像处理单元会暂停图像解码,等待输出缓冲区的存储资源释放。而本发明实施例提供的方案中将解码后图像移出输出缓冲区,可以释放解码后图像所占用的输出缓冲区的存储资源。因此在先生成的解码后图像不会占用输出缓冲区,不会影响图像处理单元对图像进行解码。使得所获得的累计时长中不包含由于解码后图像占用输出缓冲区造成的、图像处理单元等待输出缓冲区存储资源释放的时间,使得所得到的累计时长更准确,进而使得所获得的测试结果更准确。

160.本发明的一个实施例中,所述时长数量获得模块403,具体用于:

161.检测所述图像处理单元第一次从所述输入缓冲区中获取图像的时刻,并开始计时;

162.检测所述图像处理单元最后一次向所述输出缓冲区写入解码后图像的时刻,并结束计时;

163.根据计时时长获得所述图像处理单元进行图像解码的累计时长;

164.获得向所述输出缓冲区输出解码后图像的累计数量。

165.参见图5,为本发明实施例提供的第二种图像解码性能测试装置的结构示意图,与前述图4所示的实施例相比,上述装置还包括:

166.图像选择模块405,用于在所述图像处理单元对所述输入缓冲区中的图像进行图像解码之前,从所述输入缓冲区中的图像中选择校验图像;

167.解码图像获得模块406,用于获得对所述校验图像进行解码得到的校验解码图像;

168.结果验证模块407,用于在所述结果获得模块404获得所述测试结果之后,根据所述校验解码图像与所述解码后图像间的对比结果,验证所述测试结果是否有效。

169.由以上可见,本发明实施例提供的方案在测试得到电子设备的图像解码性能的测试结果之后,还依据校验解码图像对图像处理单元在测试过程中是否正常的进行了图像解码进行了验证,也就是对测试结果的有效性进行了验证。只有在图像处理单元在测试过程中正常的进行图像解码的情况下,上述测试结果才有效,因此可以提高测试结果的准确度。

170.参见图6,为本发明实施例提供的第三种图像解码性能测试装置的结构示意图,与前述图5所示的实施例相比,上述装置还包括:

171.校验值获得模块408,用于在所述解码图像获得模块406获得所述校验解码图像之后,获得所述校验解码图像的校验值,作为第一校验值;

172.所述结果验证模块407,具体用于:

173.获得所述解码后图像的校验值,作为第二校验值;

174.检测所述第一校验值与第二校验值间的差异是否小于预设差异值;

175.若为是,确定所述测试结果有效。

176.本发明的一个实施例中,通过校验值确定模块获得所述校验值;

177.所述校验值确定模块,具体用于:

178.从图像中选择用于进行校验值计算的目标像素点;

179.计算所选择的目标像素点的像素值的平均值;

180.获得包括各目标像素点的校验子值、且各校验子值按照预设顺序排列的校验值,其中,像素值大于等于所述平均值的目标像素点的校验子值为第一预设值,像素值小于所述平均值的目标像素点的校验子值为第二预设值,所述预设顺序为:预先设定的针对目标像素点位置的排列顺序。

181.本发明实施例还提供了一种电子设备,如图7所示,包括处理器701、通信接口702、存储器703和通信总线704,其中,处理器701,通信接口702,存储器703通过通信总线704完成相互间的通信,

182.存储器703,用于存放计算机程序;

183.处理器701,用于执行存储器703上所存放的程序时,实现上述图像解码性能测试方法任意所述的方法步骤。

184.应用本发明实施例提供的电子设备测试图像解码性能时,由于在越短的累计时长内获得的越多的解码图像,说明电子设备的图像处理单元进行图像硬解码的效率越高,电子设备的图像解码性能越好,因此通过本发明实施例提供的方案能够实现对电子设备的图像解码性能的测试。并且,由于图像处理单元以异步模式并行的对图像进行图像解码,因此图像处理单元可以同时并行对多个图像进行图像解码,在进行图像解码的过程中图像处理单元绝大部分的图像处理资源可以被占用,因此通过本发明实施例提供的方案能够测试电子设备图像解码的最大性能。再者,由于在图像处理单元进行图像解码的过程中,会不断地将解码后图像写入输出缓冲区,若输出缓冲区的存储资源被占满,图像处理单元无法再将新生成的解码后图像输入输出缓冲区,则图像处理单元会暂停图像解码,等待输出缓冲区的存储资源释放。而本发明实施例提供的方案中将解码后图像移出输出缓冲区,可以释放解码后图像所占用的输出缓冲区的存储资源。因此在先生成的解码后图像不会占用输出缓冲区,不会影响图像处理单元对图像进行解码。使得所获得的累计时长中不包含由于解码后图像占用输出缓冲区造成的、图像处理单元等待输出缓冲区存储资源释放的时间,使得所得到的累计时长更准确,进而使得所获得的测试结果更准确。

185.上述电子设备提到的通信总线可以是外设部件互连标准(peripheral component interconnect,pci)总线或扩展工业标准结构(extended industry standard architecture,eisa)总线等。该通信总线可以分为地址总线、数据总线、控制总线等。为便于表示,图中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。

186.通信接口用于上述电子设备与其他设备之间的通信。

187.存储器可以包括随机存取存储器(random access memory,ram),也可以包括非易失性存储器(non

‑

volatile memory,nvm),例如至少一个磁盘存储器。可选的,存储器还可以是至少一个位于远离前述处理器的存储装置。

188.上述的处理器可以是通用处理器,包括中央处理器(central processing unit,cpu)、网络处理器(network processor,np)等;还可以是数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、现场可编程门阵列(field

‑

programmable gate array,fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。

189.在本发明提供的又一实施例中,还提供了一种计算机可读存储介质,该计算机可读存储介质内存储有计算机程序,所述计算机程序被处理器执行时实现上述图像解码性能测试方法任意所述的方法步骤。

190.应用本实施例提供的计算机可读存储介质中存储的计算机程序测试图像解码性能时,由于在越短的累计时长内获得的越多的解码图像,说明电子设备的图像处理单元进行图像硬解码的效率越高,电子设备的图像解码性能越好,因此通过本发明实施例提供的方案能够实现对电子设备的图像解码性能的测试。并且,由于图像处理单元以异步模式并行的对图像进行图像解码,因此图像处理单元可以同时并行对多个图像进行图像解码,在进行图像解码的过程中图像处理单元绝大部分的图像处理资源可以被占用,因此通过本发明实施例提供的方案能够测试电子设备图像解码的最大性能。再者,由于在图像处理单元进行图像解码的过程中,会不断地将解码后图像写入输出缓冲区,若输出缓冲区的存储资源被占满,图像处理单元无法再将新生成的解码后图像输入输出缓冲区,则图像处理单元会暂停图像解码,等待输出缓冲区的存储资源释放。而本发明实施例提供的方案中将解码后图像移出输出缓冲区,可以释放解码后图像所占用的输出缓冲区的存储资源。因此在先生成的解码后图像不会占用输出缓冲区,不会影响图像处理单元对图像进行解码。使得所获得的累计时长中不包含由于解码后图像占用输出缓冲区造成的、图像处理单元等待输出缓冲区存储资源释放的时间,使得所得到的累计时长更准确,进而使得所获得的测试结果更准确。

191.在本发明提供的又一实施例中,还提供了一种包含指令的计算机程序产品,当其在计算机上运行时,使得计算机执行上述图像解码性能测试方法任意所述的方法步骤。

192.执行本实施例提供的计算机程序产品测试图像解码性能时,由于在越短的累计时长内获得的越多的解码图像,说明电子设备的图像处理单元进行图像硬解码的效率越高,电子设备的图像解码性能越好,因此通过本发明实施例提供的方案能够实现对电子设备的图像解码性能的测试。并且,由于图像处理单元以异步模式并行的对图像进行图像解码,因此图像处理单元可以同时并行对多个图像进行图像解码,在进行图像解码的过程中图像处理单元绝大部分的图像处理资源可以被占用,因此通过本发明实施例提供的方案能够测试电子设备图像解码的最大性能。再者,由于在图像处理单元进行图像解码的过程中,会不断地将解码后图像写入输出缓冲区,若输出缓冲区的存储资源被占满,图像处理单元无法再将新生成的解码后图像输入输出缓冲区,则图像处理单元会暂停图像解码,等待输出缓冲区的存储资源释放。而本发明实施例提供的方案中将解码后图像移出输出缓冲区,可以释放解码后图像所占用的输出缓冲区的存储资源。因此在先生成的解码后图像不会占用输出

缓冲区,不会影响图像处理单元对图像进行解码。使得所获得的累计时长中不包含由于解码后图像占用输出缓冲区造成的、图像处理单元等待输出缓冲区存储资源释放的时间,使得所得到的累计时长更准确,进而使得所获得的测试结果更准确。

193.在上述实施例中,可以全部或部分地通过软件、硬件、固件或者其任意组合来实现。当使用软件实现时,可以全部或部分地以计算机程序产品的形式实现。所述计算机程序产品包括一个或多个计算机指令。在计算机上加载和执行所述计算机程序指令时,全部或部分地产生按照本发明实施例所述的流程或功能。所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。所述计算机指令可以存储在计算机可读存储介质中,或者从一个计算机可读存储介质向另一个计算机可读存储介质传输,例如,所述计算机指令可以从一个网站站点、计算机、服务器或数据中心通过有线(例如同轴电缆、光纤、数字用户线(dsl))或无线(例如红外、无线、微波等)方式向另一个网站站点、计算机、服务器或数据中心进行传输。所述计算机可读存储介质可以是计算机能够存取的任何可用介质或者是包含一个或多个可用介质集成的服务器、数据中心等数据存储设备。所述可用介质可以是磁性介质,(例如,软盘、硬盘、磁带)、光介质(例如,dvd)、或者半导体介质(例如固态硬盘solid state disk(ssd))等。

194.需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

195.本说明书中的各个实施例均采用相关的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。尤其,对于装置、电子设备、计算机可读存储介质和计算机程序产品而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

196.以上所述仅为本发明的较佳实施例,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内所作的任何修改、等同替换、改进等,均包含在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1