用于处理图像数据的相机和方法与流程

database”中,合成了一个大型数据集,并通过cnn进行代码分割。但是,详细的网络架构和硬件实现没有介绍。

9.xiao yunzhe和zhong ming在应用科学9.16(2019):3268上发表的“1d barcode detection via integrated deep

‑

learning and geometric approach”,声称在无需手动调整参数的情况下,与先前的方法相比,条形码的定位至少提高了5%。

10.hansen daniel kold等人在ijcci.2017发表的“real

‑

time barcode detection and classification using deep learning”,利用intel i5

‑

6600 3.30ghz和nvidia geforce gtx 1080实时识别包括扭曲在内的代码区域。

11.zharkov andrey和zagaynov ivan在arxiv preprint arxiv:1906.06281,2019上发表的“universal barcode detector via semantic segmentation”,在cpu环境中识别条形码并识别代码类型。

12.然而,处理cnn又需要与上面示例性提到的常规预处理链完全不同的计算能力。对于嵌入式硬件,特别是在实时条件下,或至少在有限的时间窗口内,例如由于待记录的对象的传送运动,是不可行的。常规的解决方案是使用专用硬件或协处理器,如npu(neural processing unit神经处理单元)或gpu(graphics processing unit图形处理单元)。但是,这种组件通常也无法在嵌入式架构中使用。

13.us 9 858 496b2讨论了借助于特别的神经网络,即rpn(region proposal network区域建议网络)在图像中进行对象检测和分类。为了获得更强的计算能力,可以使用各种组件,包括asic(application

‑

specific integrated circuits专用集成电路)或fpga。但是,这与读取代码没有特别关系。

14.us 2018/0046903 a1总体上提出了一种使用cpu和fpga的异构架构,以加快cnn的处理。但其中只是提到了计算机视觉作为背景,并未指定更详细的实现,甚至未指定对代码读取上的应用。

15.he kaiming、zhang xiangyu、ren shaoqing和sun jian于2015年12月10日发表于arxiv:1512.03385上的“deep residual learning for image recognition”中论述了具有众多层的深度神经网络需要巨大的训练工作的问题。这可以通过所谓的"残余连接(residual connections)",即跳过层的连接来改进。这是一种非常通用与代码读取无关的技术。

16.ep 3 428 834 b1使用典型的解码器,该解码器利用没有机器学习的方法来工作,以便训练为机器学习设计的分类器,或更具体地说是训练神经网络。但是,该文档并没有详细论述预处理或发现代码区域。

17.在迄今为止已知的方法中,没有一种方法可以适当地减少或分配cnn处理高分辨率图像的巨大的计算负荷,使得也可以使用中低性能的硬件组件。

18.因此,本发明的任务在于改进利用神经网络对图像的处理,特别是用于代码读取。

19.该任务通过根据权利要求1或15的用于处理图像数据的相机和方法得以实现。优选地,该相机被构造成基于相机的读码器。图像传感器记录具有多个像素的图像数据,通常是具有几百万像素的高分辨率的图像数据。第一处理单元读取图像传感器的图像数据,即优选是高分辨率的原始图像。以相邻像素组为单位,读取作为相邻像素组中的图像数据流(streaming)进行。此外,该相机还包括用于处理图像数据的、但优选不直接连接到图像传

感器的第二处理单元,以及用于图像数据和处理结果的存储器。处理结果例如是处理后的图像数据和由此获得的特征和属性。

20.图像数据的处理至少部分地由神经网络来进行,该神经网络在第一处理单元、第二处理单元或两个处理单元上实现。优选地,神经网络是cnn(convolutional neural network卷积神经网络),以下通常如此提及。在迄今为止已知的实现中,第一处理单元首先将图像数据流式传输到存储器中,必要时在预处理之后利用典型的方法进行。随后,再由神经网络来进行处理,其中可以设想将负荷分配到第一和第二处理单元。

21.本发明基于以下基本思想,即在读取期间已经在神经网络中处理图像数据。为此,至少神经网络的第一层在第一处理层上实现,并且所读取的像点(bildpunkt)组已经被提供给该第一层,同时其他图像数据组被图像传感器读取。还可以在第一处理层(early layers早期层)上实现神经网络的第二层和其他层,然后一旦前一层产生了足够的中间结果,第二层和其他层就开始处理。这样,一旦有足够多的图像数据组被读取用于下一处理步骤,神经网络就开始或继续其处理。并行地或至少出于实际目的与此处理并行地,总是读取其他图像数据组,直到在某一时刻图像完整为止,并且只需要补回最后读取的图像数据的还剩余的处理步骤。神经网络“即时(on the fly)”工作或在图像流式传输期间已经工作了。

22.本发明的优点在于,以特别有利的方式将处理分配到多个处理单元上。异构硬件架构特别适合于此目的。由于在读取图像数据期间至少第一层就已经进行了早期和快速处理,因此至少第一层的中间结果或特征可以很快地,甚至在不断地处理时间之后可供使用。即使在硬件资源有限的系统上,特别是在具有嵌入式硬件的系统上,也能够实现利用神经网络来进行处理。根据本发明的任务分配和实现还解决了在引言讨论的文件中没有提及的另一个问题,即在处理神经网络的处理组件之间的数据传输需要巨大的带宽。即使自身有足够的计算能力,否则这也会成为瓶颈,该瓶颈有可能在所需时间框架条件下阻止处理。

23.优选地,相邻像点组是图像行或图像行的一部分,因此在读取其他图像行期间,已经在第一层处理了图像行。因此,图像从图像传感器被逐行读取或流式传输,并且处理是面向行来进行的。一旦为第一层的卷积核读取了足够的图像行,就可以进行下一处理步骤。为此,第一处理单元优选具有图像缓冲器,在该图像缓冲器中以滚动的方式临时存储相应数量的图像行。原则上,也可以用同样的方式用图像列代替图像行来工作。这里只是理解为坐标定义的不同,不作区分。

24.优选地,第一处理单元具有fpga(field programmable gat array现场可编程门阵列)和/或第二处理单元具有微处理器(cpu)。fpga特别适用于通过比较简单的单个计算操作来实时处理大数据量,例如在神经网络至少第一层中离散卷积的矩阵运算中出现的情况。而cpu则要灵活得多,能够独立完成更复杂的计算步骤,这对进一步处理是有利的。

25.优选地,神经网络被配置用于分割图像数据,通过分割发现感兴趣的区域,特别是代码区域。这个识别和定位代码区域或候选代码的任务(准备实际的代码读取)必须与高分辨率的图像配合使用,因此必须处理非常大的数据量。通过根据本发明在读取期间或“即时”进行处理,处理时间显著减少,因此是可管理的。此外,只需要通过找到的代码区域输出处理结果。除了原始图像数据外,不需要对第一处理单元的输入数据进行额外的数据传输,然而,在任何情况下这些原始图像数据都必须从图像传感器读取一次。

26.优选地,在第一处理单元上的神经网络的至少第一层生成特征图,该特征图作为处理结果被存储在存储器中。特征图(feature map)是cnn各层的结果。存储第一层的特征图,或者如果在第一处理单元上实现了多个层,则存储这些层的最后一层的特征图,以用于进一步处理,特别是由第二处理单元来进一步处理。然后,cnn的其他层、另一个cnn或者甚至典型方法都可以利用该特征图。

27.优选地,特征图包括概率图,其中代码位于图像数据中。因此,这是用于根据代码进行分割的结果的一种可能的输出格式。从该概率图中可以非常快速地检测到在有限的解码时间内最有可能用于成功读取尝试的区域。概率图每个位置可以包含一个以上的信息,例如不同代码类型的概率,例如1d代码和2d代码,或者根据不同的1d和2d代码类型来进一步区分。

28.优选地,特征图具有比图像传感器的图像数据低的分辨率。优选地,仅第一处理单元或神经网络的至少第一层应该必须用高分辨率原始图像数据工作。在进一步处理的过程中,分辨率会降低。待存储的特征图已经包含的数据量明显减少。这特别适用于概率图,因为不需要为每个单独的像素指定它是否属于代码,而是仅针对超过一定大小的区域即可。例如,可以将一个图像划分为n

×

m个像素块,并为每一个块存储一个特征,或者,如果要更好地区分特征,则在特征图中存储一组特征。

29.优选地,第一处理单元具有至少一个第一缓冲存储器,用于临时存储至少第一层的处理结果。优选地,所读取的相邻像素组被首先写入图像缓冲器。第一缓冲存储器不是用于原始图像数据的,而是用于神经网络的第一层的处理结果的。优选地,缓冲存储器的大小刚好这样设计使得可以存储足够的处理结果,以馈送给下一层的后续处理步骤。如果在第一处理单元上只实现了第一层,那么第一缓冲存储器就足以用于特征图的行,然后,该行被写入存储器并被重新填充。如果在第一处理单元上实现第二层,则第一缓冲存储器的大小优选基于第二层的卷积核的大小。然后,为第二层的处理结果提供第二缓冲存储器,相应地选择第二缓冲存储器的设计,即如果在第一处理单元上不再存在第三层,或者以其他方式适应其卷积核,则只有一行。这可以利用第三层和其他层以及缓冲存储器来继续。优选地,图像缓冲器和缓冲存储器根据fifo(first in,first out,先入先出)原则以滚动的方式写入,使得可获得当前所需的图像数据和中间结果。

30.优选地,在第一处理单元上实现的神经网络的至少一个层具有大于1的步长,即其卷积核每次移位超过一个像点。多个像点的步长(大步长)保证了层的输出数据的分辨率与输入数据相比迅速降低。因此,该措施优选已经在第一层中进行,但也可以涉及第一处理单元上的另一层、多个层或所有层。

31.优选地,在第一处理单元上实现的神经网络的至少一个层具有不处理直接相邻像素的延伸的卷积核(dilated convolution,扩张卷积)。这样的卷积核处理彼此间隔为i>1个像素的像素。由此,扩展了各自的检测范围。这又再次优选涉及第一层,并且可以设想可替代地用于第一处理单元的任何层。

32.优选地,第一处理单元被配置用于将读取的图像数据存储在存储器中,特别是在预处理之后。根据本发明,将读取的图像数据馈送给神经网络的第一层。根据本实施方式,这些图像数据还在第一处理单元的额外路径中被写入存储器。因此,原始的高分辨率图像被单独提供用于进一步处理,特别是提供给第二处理单元的解码器。第一层的图像缓冲器

可以为此目的一起使用,以便将同样较大的图像数据块写入存储器。可以设想在额外路径中使用典型的或学习的方法执行预处理步骤,例如图像压缩、亮度校正、生成二值图像等。这些预处理的结果不允许与第一处理单元上的神经网络的至少第一层的结果相混淆,该结果是附加数据。

33.优选地,神经网络的其他层和/或其他神经网络在第二处理单元上实现,以便进一步处理图像数据和/或第一处理单元的处理结果。因此,神经网络被划分为第一处理单元上的早期层和第二处理单元上的其他层。可替代地,其他层也可以理解为单独的神经网络,这最终只是语言上的差异。第二处理单元的其他层或其他神经网络基于由早期层存储在存储器中的特征图以及必要时额外存储的高分辨率图像工作。该处理不再在读取期间或“即时”进行,但是其中一旦所需的数据被存储在存储器中,就可以开始处理。

34.优选地,其他层和/或其他神经网络被配置用于基于至少第一层的处理结果来读取代码。特别地,例如以概率图的形式使用第一处理单元上的早期层的分割结果,以便发现额外存储在存储器中的高分辨率图像中的代码区域。然后,利用这些代码区域由其他层或其他神经网络来进行代码内容的读取尝试。

35.优选地,第二处理单元具有典型的解码器,该解码器没有用于读取代码的神经网络。典型的意思是,这里没有使用学习方法,特别是没有使用神经网络。典型解码器使用第一处理单元上早期层的结果,特别是根据代码区域进行分割的概率图。尝试用不同的解码器来读取代码是很常见的。因此,还可以设想利用神经网络的其他层或其他神经网络以及利用至少一个典型解码器来并行地或连续地处理代码区域。

36.优选地,在第二处理单元上实现至少两个神经网络,它们分别进一步处理第一处理单元的处理结果。这两个神经网络可以看作是第一处理单元上的早期层的后面层,其中可以说后者在经过训练后被冻结,然后以不同的方式在两个神经网络中继续。因此,第一处理单元的早期层的处理结果被多次重复使用,或者根据目标不同的情况进一步处理。例如,两个神经网络读取不同的代码类型,或者神经网络中的至少一个具有完全不同的目的。

37.该相机具有用于神经网络的处理步骤的至少一个附加的处理组件。因此,存在第三处理单元甚至更多的处理单元。这样可以更好地分配计算负荷。特别优选地,附加的处理组件是npu(neural processing unit神经处理单元)或gpu(graphics processing unit图形处理单元)。这样的组件在嵌入式硬件上通常不可用。但是,可以设想升级,然后可以实现更强性能的神经网络。

38.根据本发明的方法可以用类似的方式进一步发展并同时显示出类似的优点。这种有利的特征在从属于独立权利要求的从属权利要求中示例性地但不详尽地进行描述。

附图说明

39.下面将基于实施方式并参考附图对本发明的其他特征和优点进行更详细的阐述。在附图中:

40.图1示出了在传送带上方示例性安装相机的示意性概览图;

41.图2a

‑

图2b示出了在变化的背景下具有待读取的代码的示例图像;

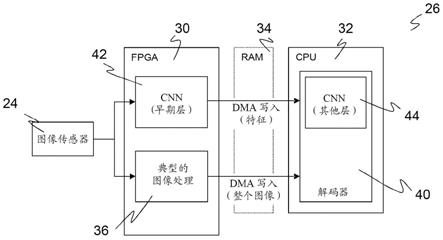

42.图3示出了现有技术中用神经网络对图像数据进行常规处理的示意图;

43.图4示出了在本发明的实施方式中神经网络已经在读取图像数据期间对图像数据

进行处理的示意图;

44.图5示出了用于已经在读取期间处理图像数据的神经网络的早期层的示例性图示;

45.图6示出了在本发明的其他实施方式中神经网络已经在读取图像数据期间利用附加的处理组件对图像数据进行处理的示意图;以及

46.图7示出了在本发明的其他实施方式中神经网络已经在读取图像数据期间对图像数据进行处理的示意图,其中早期层的结果被多个神经网络使用。

47.图1示出了安装在传送带12上方的相机10,如箭头16所示,该传送带12将对象14输送通过相机10的检测区域18。在本应用示例中,对象14在其外表面上携带代码20,这些代码被相机10检测和评估。只有当代码20附着在上侧或至少从上方可见时,才可以被相机10识别。因此,不同于图1中的展示,可以从不同的方向安装多个相机10,以用于读取例如附着在侧面或底部的代码22,从而实现所谓的从所有方向的全方位读取。在实践中,通常将多个相机10布置成读取系统作为读取通道。将相机10固定应用在传送带上在实践中非常常见。但是,本发明涉及图像数据的处理或相机10本身,因此该示例不应限制性地理解。同样,对相机10而言,也可以执行其他图像评估任务,例如用于测量或探测对象14的图像评估任务,来代替代码读取或被构造成基于相机的读码器的相机10。

48.相机10利用图像传感器24检测输送的对象14和代码20的图像数据,这些图像数据由评估单元26通过图像评估和解码方法进一步处理。优选地,评估单元26实现在嵌入式硬件中,并且具有多个评估组件。评估单元26的更详细的设计以及它对图像数据的处理将在后面参考图3至图7进行更详细的阐述。相机10通过接口28输出信息,例如读取的代码或图像数据。

49.图2a

‑

图2b示出了在不同背景下具有代码20的两个示例图像。用于读取代码20的第一步骤是分割,通过分割来识别和定位候选代码。成功分割的结果在图2a

‑

图2b中用白色框突出显示。在这里,预先给定的标准并不能可靠地导致成功。利用神经网络可以改进在不同背景下的识别率。代码20的分割是重要的应用示例。但是,利用现在描述的架构通过神经网络也可以找到其他图像特征。

50.图3示出了由评估单元26对图像传感器24的图像数据流进行的常规处理,该评估单元具有fpga 30、cpu 32和存储器34。图像数据由fpga 30读取,并作为整个高分辨率的图像被写入存储器34。与此同时,典型的预处理单元36可以已经对图像数据流进行了处理,例如对图像应用过滤器,或者还进行分割。但是,这种分割基于预先给定的标准和典型的方法,而没有机器学习,因此,对于未被识别的代码20或者反过来对被错误地识别为代码20的区域,仍有相当高的错误率。

51.用于处理图像的神经网络38也在fpga30上实现。该神经网络访问存储器34,以读取图像,并将神经网络38的处理结果写回存储器34。因此,神经网络38期望访问整个图像,使得在神经网络开始其处理之前,必须完成预处理单元36的图像检测。神经网络38帮助cpu 32的解码器40做准备工作(zuarbeiten),利用该解码器来读取代码20,或者可能神经网络本身已经读取了代码20,这样解码器40就被分配了更多的管理任务。

52.该方法有几个缺点。首先,由于在完全检测到了图像时神经网络38才可以开始处理,因此会损失时间。此外,fpga30必须利用其有限的计算资源将读取或预处理36和神经网

络38这两项任务结合起来。这可以通过性能特别强大的fpga 30、另一fpga或别的协处理器(如gpu、npu或dsp)来解决,但实际上应避免这种额外的花费。

53.此外,这并不能消除在图3的情况下也会出现的另一个缺点,即必须进行非常大量的数据交换,该数据交换需要相应的带宽或使系统速度变慢。这是因为整个图像必须首先由fpga30读取并被写入存储器34,然后,在完成图像传输后,必须再次从存储器传输到fpga 30或别的负责的组件,并在那里由神经网络38进行处理,因此处理结果也被存储在存储器34中。在实时系统中,或者甚至在下一个对象14还位于检测区域18中的根据图1的应用的有限处理时间窗口中,这代表了相当大的通信瓶颈。

54.图4示出了在本发明的实施方式中由评估单元26对图像传感器24的图像数据流进行的处理。原则上,使用如图3中的具有fpga 30、cpu 32和存储器34的类似硬件,但现在使用的方式不同。fpga 30是代表第一处理单元的硬件组件,该硬件组件优选具有实时能力并且在任何情况下都能够处理图像传感器24的数据量。相应地,cpu 32代表第二处理单元,该第二处理单元可以被尽可能灵活地编程,但不必具有适于在通常的帧率下读取具有百万像素分辨率的图像数据的接口。cpu 32访问在存储器34中由fpga 30提供的数据,以便利用其解码器40来读取代码20。

55.优选地,保留具有典型的预处理36的通道,fpga 30通过该通道将图像数据组合成完整的图像并存储在存储器34中。这样,解码器40就可以访问完整的、高分辨率的图像。在此,可以设想使用典型方法的预处理步骤。

56.但是,根据本发明,通过神经网络的处理以不同的方式进行组织。神经网络的早期层42(early layers)在fpga 30上实现。这也可以只是第一层。然后在cpu 32上实现其他层44。还可以将这些其他的层44视为单独的神经网络,该神经网络将早期层42的处理结果用作输入数据。此外,还可以设想解码器40不再利用神经网络工作,而是利用常规方法来工作。

57.在读取其他图像数据期间,神经网络的早期层42已经处理传入的图像数据流。早期层42的处理结果,更确切地说是早期层42的最后一层的处理结果,被存储在存储器34中。在此,省略了在神经网络中可以开始处理之前数据通过存储器34的绕行(umweg)。根据本发明的神经网络或其第一层并不期望完整的图像,而是已经处理了当前读取的部分图像数据。因此,通信瓶颈也消除了,因为不再需要将整个图像再次读入fpga 30中。仅需要存储器访问来逐段存储早期层42的处理结果,并且可选地通过典型的预处理36逐渐存储完整的图像。

58.图5示意性地示出了fpga 30上的早期层42,以便更详细地阐述在读取图像数据期间神经网络已经进行的处理。在此,首先应简单介绍一些专业术语。

59.优选使用cnn(convolutional neural network卷积神经网络)作为神经网络,这是特别适用于图像处理的深度神经网络的特色。cnn执行一系列的离散卷积(convolution),每个离散卷积都跟随有非线性激活函数。离散卷积和激活函数的相应组合形成cnn的层(layer)。层的输出是特征图(feature map)。

60.各个离散卷积是通过利用卷积核或卷积矩阵(convolutional kernel卷积核)的矩阵运算来实现的。卷积核的大小用[n,n,c1,c2]来表示,其中[n,n]是空间范围,c1是输入数据的通道数,以及c2是输出数据的通道数。当输入数据只包括一个通道时,如在灰度图像

的情况下,则卷积核的大小就变成[n,n,1,c2]或简称[n,n,c]。卷积核的大小由cnn的架构预先给定,并且在训练cnn时示教矩阵中的值。

[0061]

在图5中,在fpga 30上所示的早期层42(这里示例性地是两层)中的处理从左到右进行。图像传感器24的像素作为输入数据被读取。该图像数据作为相邻像素的图像数据流到达,优选作为图像行到达。所读取的像素被临时存储在图像缓冲器46中,因此每次读取操作有多少相邻的像素进入无关紧要。一旦在图像缓冲器46中存储了足够的图像行,就可以开始由第一层进行处理,并且可以通过对存储的图像行和第一层的第一卷积核48进行离散卷积或矩阵运算来计算第一输出行。单次计算类似于利用滤波核的常见图像滤波,其中虽然并行产生了多个输出图像,但每个滤波核产生一个输出图像。此外,术语是不同的,它不是实际的输出图像,而是特征图,该特征图通常不会有任何的光学改进,而是会根据学习到的卷积核的权重来改变。

[0062]

第一卷积核48的大小为[n1,n1,c1],因为在本示例中的输入图像被假定为只有一个通道的灰度图像。根据空间范围n1,离散卷积n1需要图像行。因此,图像缓冲器46的高度由第一卷积核48的高度n1来预定义,宽度由图像行来预定义。一旦第一层处理了第一批n条图像行,就不再需要第一图像行,因为第二输出行是由图像行2...n+1计算出来的。因此,图像缓冲器46优选根据fifo原则以滚动的方式得以使用。图像缓冲器46还可以额外保持一定的一个或几个图像行的储备,用于从图像传感器24读取和进一步处理第一层之间的延迟。

[0063]

输出行被收集在第一层的第一缓冲器50中。在可替代的实施方式中,早期层42根本只包括第一层,在该实施方式中,第一缓冲器50仅满足一条输出行,一旦完成该输出行,就将其传输到存储器34。在图5的具有两层的图示中,第一缓冲器50收集输出行,用于处理第二层。

[0064]

第二层的第二滤波核52的大小为[n2,n2,c1,c2]。毕竟,第一层已经从单通道的灰度图像c1生成了其输出的特征图的通道,并且第二滤波核52的空间范围n2基本上与第一滤波核48的空间范围n1无关。否则,第二层的处理与第一层类似。因此,一旦第一缓冲器50中有n2条行可用,就可以进行对第二层的输出行的计算。因此,第一缓冲器50应可以临时存储第一层的至少n2条输出行,并且与图像缓冲器一样,第一缓冲器50优选以滚动的方式使用。

[0065]

第二层的第二缓冲器54只记录第二层的最后计算的输出行。完成的输出行是代表fpga 30上的早期层42的处理结果的特征图的一部分,并被逐渐传输到存储器34中。当然,可替代地,在fpga将多个输出行存储在存储器34中之前,也可以临时存储这些输出行。

[0066]

与图5的图示不同,早期层42的第三层和其他层可以在fpga 30上实现,其中提供了第三滤波核、第三缓冲器以及必要时另外的滤波核和缓冲器。

[0067]

除了特征图之外,fpga 30还优选将原始图像行存储在存储器34中,以便在由cpu 32和解码器40进行的进一步处理中使用原始图像。在此,仍然可以进行典型的预处理,必要时也可以利用其他神经网络进行预处理。后者则不旨在再次分割图像或提取其他特征,而是旨在根据典型的预处理进行相应的准备。

[0068]

图5中cnn或其早期层42的架构被简化。一般来说,相对较小的cnn足以进行代码读取或代码分割,即这样的cnn具有的层数不会太多。尽管如此,已经指出,具体而言仅将fpga 30上的两个层理解为示例,其中无论如何,根据实施方式,cpu 32上还会增加其他层44,这些层对从存储器34中产生的特征图进行处理。哪些层42是在fpga 30上实现的,哪些层44是

在cpu 32上实现的,其分界线的定位是设计自由度。优选的设计方案提出在fpga 30上容纳多个层42,只要其计算和存储器能力允许。

[0069]

图5只示出了cnn的层中的卷积核48、52。此外,各层优选地具有典型的元素,如归一化和非线性的激活函数。cnn还有一系列其他设计选项,这些选项优选但不一定是单独或组合实现的:为了加速稍后阐述的训练,还提供了根据引言中引用的he等人论文的快速前向连接(残余连接)。cnn是完全卷积网络("fully convolutional"),其中没有完全连接的层。换句话说,特征图的分辨率会逐层降低。为了加速计算,层的输出通道数最多限制在1000。在第一层中,使用了步长不等于1(“大步长”)的滤波核,使得分辨率迅速下降。延伸的卷积核(“扩张卷积”)可以扩展各自的检测核。最后,可以通过解耦的卷积核(可分离的卷积核,特别是深度可分离的卷积核)来优化计算。

[0070]

通过在读取其他图像数据期间已对早期层42进行即时或流水线处理,计算负荷可以在fpga 30和cpu 32之间分配,同时数据传输减少了几个数量级。由此,cnn也可以在性能适中的硬件上,特别是在嵌入式硬件上实现。可用相机10满足了这样的硬件要求,而数据传输的带宽和计算能力对于结合图3所阐述的、利用cnn处理存储器34的整个高分辨率图像来说是不够的,至少不在诸如图1的应用所预先给定的时间窗口内。

[0071]

在相机10作为读码器的优选应用中,cnn的任务是定位预先给定的类型的代码20。然后,输出的特征图例如是概率图,在该概率图中,特定的代码类型的代码20,例如1d代码和2d代码或其他区分的代码类型,位于所记录的图像中。概率图的通道数和待区分的代码类型数相同。优选地,概率图的分辨率比高分辨率的输入图像的分辨率低得多。然后,可以说将输入图像划分为图像块,其中每个图像块而不是每个单个像素仅有代码20的一个概率值。

[0072]

在使用cnn之前,必须对其进行示教或训练。为此,需要合适的训练数据。通常执行监督训练(supervised learning,监督学习),在监督训练时预先给定正确的预期结果。对训练数据进行相应的注释或标记。这些训练数据必须覆盖广泛的可变性,以便cnn以后灵活应对应用情况,因此手动注释的成本非常高。因此,手动的训练数据集优选只作为起点进行注释。其他的训练图像是综合生成的,这些训练图像已经通过其产生而被注释了。在此基础上,可以通过模拟效果获得许多其他注释的训练图像。

[0073]

结果是一个较长的但不详尽的、训练图像可以如何生成或改变的清单:具有随机内容的代码、不同的代码类型(ean、代码128、代码39、datamatrix、pdf...)、具有随机极性或随机空白区域的代码、不完整的代码、不同模块宽度和高度的代码、不同姿势和透视变形的代码、印刷和冲压代码(dpm、直接部件打标)、同一图像中的多个不同代码。不涉及代码而涉及图像的变化效果例如是随机噪声(高斯、拉普拉斯、均匀、佩林)、模糊效果、非线性变形、随机背景纹理(纸、纸板、木材、塑料、金属...)、不同字体和字体大小的文本以及照明效果(均匀和非均匀、斑点...)。

[0074]

训练后,可以进行一些后处理步骤,以便优化后面的处理时间。离散卷积核中的学习权重可以用训练中的批量归一化系数进行缩放。此外,还优选对fpga 30和/或cpu 32量化权重,例如量化为8位或16位。

[0075]

图6示出了在本发明的其他实施方式中由评估单元26对图像传感器24的图像数据流进行的处理。与图4不同,这里还提供了评估单元26的至少一个附加的硬件组件56。在此,

该附加的硬件组件优选是特别适合于处理cnn的组件,如npu(neural processing unit神经处理单元)或gpu(graphics processing unit图形处理单元)。但是,也可以想象的是,附加的硬件组件56是另一个数字组件,特别是另一个fpga或另一个cpu。通过根据本发明的架构以及将cnn划分为在读取或流期间已经处理进入的图像数据的早期层42,附加的硬件组件56并不是绝对必要的,但可以由此加速处理,或者可以使用更复杂的cnn。在图6的图示中,cnn的一些其他层58被转移到附加的硬件组件56。可替代地,其他层44被完全从cpu 32移动到附加的硬件组件,或者附加的硬件组件56处理至少一个单独的cnn以用于其他任务。可以提供附加的硬件组件56对存储器34的单独访问。

[0076]

图7示出了在本发明的其他实施方式中由评估单元26对图像传感器24的图像数据流进行的处理。现在提供了访问早期层42的特征图的两个cnn 60、62。cnn60、62中的一个可以对应于其他实施方式中的其他层44。因此,产生了两个不同的cnn 60、62,例如为了读取不同的代码类型,但这两个cnn 60、62在早期层42的第一部分一致。在变型中,早期层42的达到的训练状态被冻结,并且分别被用作不同的cnn 60、62的训练的起点。在另一变型中,早期层42包括在扩展的训练中,因此,仍然允许在cnn 60、62各自训练时改变。还可以设想cpu 32的典型解码方法使用早期层42的特征图,以便发现代码区域,从而取代或补充其他层44或cnn 60、62。顺便提及,这不仅适用于根据图7的实施方式,也适用于其他实施方式。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1