半导体器件和解码方法与流程

半导体器件和解码方法

1.相关申请的交叉引用

2.于2020年6月3日提交的包括说明书、附图和摘要的的日本专利申请号2020

‑

096553的公开整体通过引用并入本文。

背景技术:

3.本技术涉及一种半导体器件,并且可适用于包括例如使用曼彻斯特(manchester)编码等的解码电路的半导体器件。

4.当发送参考时钟与接收参考时钟之间出现某些或更多差异时,通信系统会出现无法接收正常数据等的问题。

5.作为用于防止该问题的一种方法,例示一种高速数据采样。这是一种在一个时隙中设置多个采样定时并且根据采样定时的结果确定数据的方法。时隙是用于传输一位数据所花费的时间。

6.并且,采用曼彻斯特编码作为用于防止当由于发送参考时钟与接收参考时钟之间的频率或相位的差异而在其间出现某些或更多差异时无法接收正常数据的问题的方法。例如,在曼彻斯特编码中,电位被设置为在一个时隙中肯定改变,使得当电位从高电位变为低电位时,逻辑值变为“1”;而当电位在一个时隙中从低电位变为高电位(以产生中间边缘)时,逻辑值变为“0”。

7.下文列举了所公开的技术。

8.[专利文献1]日本未审查专利申请公开号2011

‑

61525。

技术实现要素:

[0009]

在数据传输时,数据被诸如抖动之类的噪声延迟,该噪声是沿时间轴方向的信号波形波动。延迟的数量并非恒定的,而是变化的。当采样频率不大于数据传输的频率时,由于该变化可能检测到错误边缘。如果可以在发送侧与接收侧之间进行时钟同步,或如果可以设置足够大的采样频率,则不会出现如上文所描述的问题。然而,由于电路设计的限制通常难以进行同步。

[0010]

根据本技术的一方面,一种半导体器件包括:数据接收电路,被配置为在第一时间接收第一数据并且在第二时间接收第二数据;以及边缘识别电路,被配置为设置范围并且检测该范围内的边缘。边缘识别电路包括测量电路,该测量电路被配置为测量从第一数据的接收到第二数据的接收所花费的第一时段,并且被配置为基于第一时段来确定用于检测由数据接收电路接收的数据中包含的边缘的范围。

[0011]

根据该半导体器件,当采样频率不大于数据传输的频率时,可以减少由于变化而导致的对错误边缘的检测。

附图说明

[0012]

图1是示出了要成为本技术的目标的信号的传播延迟模型的图。

[0013]

图2是示出了图1中所示的信号传播延迟模型中的传播延迟的图。

[0014]

图3是示出了在发生等于或大于数据周期的1/8的抖动的情况下的时序示例的图。

[0015]

图4a是在数据检测范围没有发生改变的情况下的时序图。

[0016]

图4b是在对数据检测范围进行校正的延迟校正的情况下的时序图。

[0017]

图4c是在对数据检测范围进行校正的超前校正的情况下的时序图。

[0018]

图5是用于解释延迟校正和超前校正的时序图。

[0019]

图6是示出了根据第一工作示例的通信系统的配置的框图。

[0020]

图7是示出了图6中所示的解码器的配置的框图。

[0021]

图8是示出了图7中所示的解码器的操作波形的时序图。

[0022]

图9是示出了在图7中所示的解码器检测到下降边缘的情况下的硬件处理的流程图。

[0023]

图10是示出了根据第二工作示例的解码器的操作波形的时序图。

[0024]

图11是示出了在根据第二工作示例的解码器检测到下降边缘的情况下的硬件处理的流程图。

[0025]

图12是示出了根据第三工作示例的解码器的配置的框图。

[0026]

图13是示出了三输入多数判定电路的电路图。

[0027]

图14是示出了图12中所示的用于移位的触发器、用于数据采样的触发器、噪声滤波器以及边缘检测电路的配置的框图。

[0028]

图15是示出了图12中所示的边缘识别电路的配置的一部分的框图。

[0029]

图16是示出了图12中所示的边缘识别电路的配置的一部分的框图。

[0030]

图17是图12中所示的时钟生成电路的框图。

[0031]

图18是示出了根据第三工作示例的解码器的操作的时序图。

[0032]

图19是示出了根据第三工作示例的解码器的操作的时序图。

[0033]

图20是示出了根据第三工作示例的解码器的操作的时序图。

[0034]

图21是示出了根据第三工作示例的解码器的操作的时序图。

[0035]

图22是示出了根据第三工作示例的解码器的操作的时序图。

[0036]

图23是示出了根据第三工作示例的解码器的操作的时序图。

[0037]

图24是示出了根据第三工作示例的解码器的操作的时序图。

[0038]

图25是示出了根据第四工作示例的边缘识别电路的配置的一部分的框图。

[0039]

图26是示出了根据第四工作示例的边缘识别电路的配置的一部分的框图。

[0040]

图27是示出了图26中所示的校正电路的真值表的图。

[0041]

图28是示出了根据第四工作示例的解码器的操作的时序图。

具体实施方式

[0042]

下文参考附图对实施例和工作示例进行描述。在以下描述中,相同的附图标记附于相同的元件,并且将省略其重复描述。

[0043]

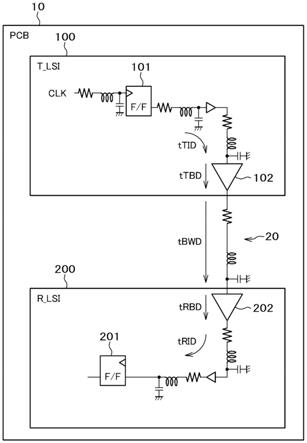

首先,参考图1和图2对抖动进行解释。图1是示出了要成为本技术的目标的信号的传播延迟模型的图。图2是示出了图1中所示的信号传播延迟模型的传播延迟的图。

[0044]

如图1中所示,发射器半导体器件(t_lsi)100和接收器半导体器件(r_lsi)200被

安装在印刷电路板(pcb)10上。半导体器件100和半导体器件200通过布线20彼此连接,该布线20形成在印刷板10中。在这种情况下,信号通过布线20从半导体器件100发送到半导体器件200。

[0045]

考虑到发射器侧上的时钟(clk)作为开始点,生成以下延迟,直至时钟到达触发器(f/f)201,该触发器201用作接收器侧上的输入逻辑电路的。

[0046]

时钟抖动(clk):ttcd

[0047]

半导体器件100的内部传播延迟:ttid

[0048]

半导体器件100的输出缓冲器102的延迟:ttbd

[0049]

pcb 10的布线20的延迟:tbwd

[0050]

半导体器件200的输入缓冲器202的延迟:trbd

[0051]

半导体器件200的内部传播延迟:trid

[0052]

在这种情况下,“tbwd”包括由于半导体器件100和半导体器件200的每个封装而引起的延迟。延迟中的每个延迟依据诸如温度、电压、制造噪声或环境噪声的变化之类的条件而发生变化。如图2中所示,在这些延迟的总和(td)的最小值的情况下的延迟(tde)与在该总和(td)的最大值的情况下的延迟(tdl)之间的差是输入信号的抖动。

[0053]

接着,参考图1和图3对本发明人所研究的曼彻斯特编码中的抖动的影响进行解释。图3是示出了在等于或大于数据周期的1/8的抖动发生的情况下的时序示例的图。下文对以100mbps(位/秒)的通信速度接收曼彻斯特编码的情况进行解释。

[0054]

当在半导体器件200中生成的具有最快频率的时钟是400mhz时,即使使用了时钟的上升边缘和下降边缘,在一个数据周期内也仅执行8次采样。因此,采样为1.25ns(纳秒),其精度比规格100mbps的精度更加粗糙。

[0055]

同时,在将lvds(低压差分信号)接口用于输入有曼彻斯特编码信号的端子的情况下,该信号作为差分输入从半导体器件200的外部输入到输入缓冲器202。因此,当为了减小功耗而减小电流数量时,输入缓冲器202的抖动增加。并且,当为了减少功耗和成本而使用具有低泄漏电流的cmos(互补金属氧化物半导体)工艺时,还减少了电源的电流数量。因此,这种情况易于受到噪声的影响,并且在半导体器件200的内部传播中具有大抖动。并且,供应时钟的诸如pll(锁相环)电路之类的时钟源存在抖动。除了它们之外,半导体器件200外的布线20以及发射器半导体器件100的电路也存在抖动,并且因此,总抖动值经常超过

±

1.25ns。

[0056]

例如,当周期为10ns的曼彻斯特编码信号的采样精度为1.25ns,同时引起的抖动超过

±

1.25ns时,则可能在同一位置对中间边缘和边界边缘进行采样。边界边缘是在编码时在数据/时钟周期的边界处(在数据边界处)生成的边缘,并且中间边缘是在数据/时钟周期的中间处(在数据中间处)生成的边缘。因此,不能识别中间边缘与边界边缘之间的差异,不能正确进行解码。例如,如图3所示,当引起

±

1.5ns的抖动并且在“a”点处对边缘进行采样时,该边缘不能被识别为由于抖动引起的中间边缘me的延迟而产生的边缘(使用点划线图示)或由边界边缘be的超前而产生的边缘(使用虚线图示)。

[0057]

如上文所描述的,数据传输由于诸如抖动之类的噪声而延迟。该延迟数量并非恒定而是发生变化。当采样频率不大于数据传输的频率时,可以检测到由于该变化而导致的错误边缘。

[0058]

如果在发送侧与接收侧之间进行时钟同步或如果通过使用专用于发送/接收的pll设置足够大的采样频率,则不会出现上文所描述的问题。然而,在一些情况下,由于电路设计的限制,难以进行同步。并且,在使用专用于发送/接收的pll的情况下,成本上的缺点非常大,并且仅用于进行振荡以锁定pll的时段(前导时段)也有必要。

[0059]

接着,下文对本技术的实施例进行解释。由于抖动而导致的相邻周期之间的移位值依据先前周期的延迟是大还是小而发生变化。例如,在抖动为2ns的情况下,当先前周期的延迟的总和(td)为平均值时,下一周期的延迟方向和超前方向都可以变化1ns(

±

1ns)。在这种情况下,总和(td)是平均值的状态意味着最早延迟(tde)与最晚延迟(tdl)之间的中间状态。

[0060]

同时,当先前周期的延迟的总和(td)比平均值小0.5ns时(当信号传输较早时),下一周期的超前数量可能为

‑

0.5ns,并且下一周期的延迟数量可能为+1.5ns。当先前周期的延迟的总和(td)最小时(最早情况(tde)),下一周期不能更早,同时延迟数量可以至多为+2ns。

[0061]

另一方面,当先前周期的延迟的总和(td)大于平均值时(当信号发送较晚时),可以说与小于平均值的情况相反。即,当先前周期的延迟数量较小时,下一周期的移位沿延迟方向较大,而沿超前方向较小。相反,当先前周期的延迟数量较大时,下一周期的移位沿超前方向较大,而沿延迟方向较小。

[0062]

在实施例中,为了接收包含抖动的该曼彻斯特编码信号,数据检测范围基于必须在曼彻斯特编码信号中生成的中间边缘来校正。在这种情况下,将数据检测范围的结束设置为早于正常检测结束的校正被称为“超前校正”。并且,将数据检测范围的开始设置为晚于正常检测开始的校正被称为“延迟校正”。

[0063]

通过对下一周期的数据检测范围进行校正,可以预测先前周期的延迟是大还是小。在对下一周期的数据检测范围进行校正的超前校正的情况下,可以确定先前周期的延迟至少不是最晚延迟,并且可以确定下一周期晚于先前周期。在用于对下一周期的数据检测范围进行校正的延迟校正的情况下,可以确定先前周期的延迟至少不是最晚延迟,并且可以确定下一周期早于先前周期。

[0064]

本实施例利用这些特点,预先存储对先前周期的数据检测范围的校正结果,然后,基于校正结果来校正下一周期的数据检测范围(w)。

[0065]

对数据检测范围的校正将参考图4a至图4c进行解释。图4a是在数据检测范围没有发生改变的情况下的时序图。图4b是在用于对数据检测范围进行校正的延迟校正的情况下的时序图。图4c是在用于对数据检测范围进行校正的超前校正的情况下的时序图。

[0066]

如图4a中所示,在没有对数据检测范围(w)进行校正的情况下,使用粗箭头图示的采样点“sp”处的边缘不能被识别为中间边缘me或边界边缘be。

[0067]

因此,如图4b中所示,在对先前周期的边缘检测进行超前校正(ac)的情况下,在下一周期内进行延迟校正。即,在下一周期的边缘检测中,延迟了数据检测范围(w)的中心,或缩短了超前侧的数据检测范围(w)的范围。以这种方式,使用粗箭头图示的采样点“sp”处的边缘可以被确定为边界边缘be。

[0068]

因此,如图4c中所示,在对先前周期的边缘检测进行延迟校正(dc)的情况下,在下一周期内进行超前校正。即,在下一周期的边缘检测中,使数据检测范围(w)的中心超前,或

缩短了延迟侧的数据检测范围(w)的范围。以这种方式,使用粗箭头图示的采样点“sp”处的边缘可以被确定为中间边缘me。

[0069]

接着,对与上文所描述的观点不同的观点的实施例进行解释。为了设置数据检测范围,根据本实施例的接收器半导体器件测量例如用于接收两个连续数据所花费的时间,并且基于所测量的时间来设置数据检测范围。如果数据接收之间的时间间隔很短,则下一到来数据可能会在比正常数据接收间隔的时间间隔更长的时间间隔过去之后到来。因此,进行用于将数据检测范围的开始设置为晚于正常检测开始的延迟校正。如果数据接收之间的时间间隔较长,则下一到来数据可能会在比正常数据接收间隔的时间间隔短的时间间隔过去之后到来。因此,进行用于将数据检测范围的结束设置为早于正常检测结束的超前校正。

[0070]

参考图5对延迟校正和超前校正的具体示例进行解释。图5是用于解释延迟校正和超前校正的时序图。图5的假设是在一些情况下由于抖动而以8ns的周期进行数据接收并且移位约

±

2ns。

[0071]

首先,对没有延迟校正和没有超前校正的情况(情况“a”)进行解释。由于抖动,所以第二中间边缘me2移位了大约

±

2ns。考虑到抖动,第三中间边缘me3的数据检测范围需要参考移位第二中间边缘me2而被设置在4ns至12ns的范围之内。

[0072]

接着,对在短数据间隔的情况(情况“b”)下的延迟校正的处理进行解释。在周期为8ns的通信中,当第一中间边缘me1与第二中间边缘me2之间的数据间隔为6ns时,主要出现以下原因。

[0073]

b1:data2超前2ns。

[0074]

b2:data1延迟2ns。

[0075]

在情况b1下,参考data2的第二中间边缘me2,data3的第三中间边缘me3可能在8ns至12ns的范围内。在情况b2下,参考data2的第二中间边缘me2,data3的第三中间边缘me3可能在6ns至10ns的范围内。因此,为了支持两种可能性,6ns至12ns的范围可以被设置为边缘检测范围。由于用于将数据检测范围的起点设置为延迟2ns的延迟校正,所以该数据检测范围可以比情况a下的4ns至12ns的范围更窄,并且因此,可以防止误差检测。

[0076]

接着,将对在长数据间隔的情况下(情况“c”)的超前校正进行解释。当第一中间边缘me1与第二中间边缘me2之间的数据间隔为10ns时,主要出现以下原因。

[0077]

c1:data1超前2ns。

[0078]

c2:data2延迟2ns。

[0079]

在情况c1下,参考data2的第二中间边缘me2,data3可能在6ns至10ns的范围内。在情况c2下,参考data2的第二中间边缘me2,data3可能在4ns至8ns的范围内。因此,为了支持两种可能性,4ns至10ns的范围可以被设置为边缘检测范围。由于用于将数据检测范围的结束设置为超前2ns的超前校正,所以该数据检测范围可以比情况a下的4ns至12ns的范围更窄,并且因此,可以防止误差检测。

[0080]

在该实施例中,接收器测量接收两个连续数据所花费的时间。数据检测范围基于数据接收之间的时间间隔来设置。如果数据接收之间的时间间隔短,则下一到来数据可能会在比正常数据接收间隔的时间间隔长的时间间隔过去之后到来。因此,数据检测范围的开始被设置为晚于正常检测开始。如果数据接收之间的时间间隔较长,则下一到来数据可

能会比正常数据接收间隔的时间间隔短的时间间隔过去之后到来。因此,数据检测范围的结束可以被设置为早于正常检测结束。

[0081]

根据实施例,即使当包含采样精度(定时器精度)的抖动等于或大于

±

1/8周期时,也可以正确恢复时钟和数据。以这种方式,即使当抖动等于或大于

±

1/8周期时,也可以通过具有低功率和低成本的电路来正确接收数据,而无需使用专用于发送/接收的pll。在本实施例中,例示了曼彻斯特编码信号的接收。然而,例如,本实施例还适用于例如叠加时钟和数据信号的通信(诸如8b/10b编码、rll(游程长度受限)编码和wfm)以及使用例如异步信号的异步通信。

[0082]

下文对该实施例的一些典型工作示例进行解释。在以下对工作示例的解释中,对配置和功能与上文所描述的配置和功能相似的部分使用与上文所描述的实施例的符号相同的符号标注。对于对部分的解释,可以在技术上不矛盾的范围内适当地利用对实施例的解释。上文所描述的实施例的一部分和多个工作示例的一部分或全部可以在技术上不矛盾的范围内适当地组合利用。

[0083]

(第一工作示例)

[0084]

图6是示出了根据第一工作示例的通信系统的配置的框图。

[0085]

在根据第一工作示例的通信系统1中,以曼彻斯特编码进行半导体器件100与半导体器件200之间的通信。半导体器件100也被称为主设备,并且由例如mcu(微控制器单元)构成。半导体器件200也称为从属设备,并且被连接到例如传感器或控制设备。通信由半导体器件100和半导体器件200的相应的通信模块110和通信模块210控制。通信模块110和通信模块210分别包括发送电路120和发送电路220以及接收电路140和接收电路240。发送电路120和发送电路220包括用于曼彻斯特编码的编码器130和编码器230,并且接收电路140和接收电路240分别包括用于曼彻斯特编码的解码器150和解码器250。用于曼彻斯特编码的编码器130和编码器230分别通过通信线21和通信线22连接到用于曼彻斯特编码的解码器150和解码器250。由于从曼彻斯特编码的信号再生时钟和数据,所以用于曼彻斯特编码的解码器150和解码器250中的每个解码器被称为cdr(时钟数据恢复)。

[0086]

在发送电路120与接收电路240之间以及在发送电路220与接收电路140之间进行异步串行通信。在异步串行通信中,单个字符的字符信息在被夹设在意味开始的“开始位”和意味结束的“停止位”之前被传输。并且,在停止位之前添加“奇偶校验位”,用于检查数据是否已经正确传输。要注意的是,已经在确保用于数据流的每个方向的信号线的全双工通信的示例中进行上述解释。然而,可以应用使用一条信号线的半双工通信,该信号线的通信方向被切换。

[0087]

要注意的是,用于传感器或控制设备的设置信号或控制信号从半导体器件100发送到半导体器件200。传感器或控制设备的数据、状态信息或误差信息从半导体器件200发送到半导体器件200。

[0088]

除了通信模块110之外,半导体器件100还包括cpu 160、计时器170、以及另一控制电路(cntr)180。通信模块110响应于来自这些电路的数据和控制而进行通信。半导体器件200包括控制未图示的传感器或控制设备的控制电路(cntr)260,并且通信模块210响应于来自控制电路260的数据和控制而进行通信。半导体器件200可以由mcu构成。

[0089]

接着,参考图7对用于曼彻斯特编码的解码器150和解码器250进行解释。图7是示

出了图6中所示的解码器的配置的框图。虽然下文对解码器150进行解释,但是解码器250具有与解码器150的配置类似的配置并且对此以类似方式操作。

[0090]

解码器150包括数据接收电路,该数据接收电路具有同步电路(sync)151、噪声滤波器(fltr)152和边缘检测电路(edc)153、以及时钟生成电路(cg)157。解码器150还包括边缘识别电路,该边缘识别电路具有边缘确定电路(ejc)154、边缘历史电路(ehc)155以及计数器(cntr)156。

[0091]

曼彻斯特编码的串行输入信号(si)通过同步电路151和噪声滤波器152,并且输入到边缘检测电路153。在这种情况下,同步电路151例如由多电平触发器(f/f)电路构成,用于避免出现亚稳态。噪声滤波器152例如由三输入多数判定电路构成。

[0092]

时钟信号(clk)是在半导体器件100中生成的时钟,并且通过对在pll等中生成的时钟进行分频而获得。然而,分频并非总有必要,并且时钟可能无法分频。对于时钟信号(clk),可以仅使用上升边缘或下降边缘,或者可以使用上升边缘和下降边缘。备选地,可以使用两相时钟信号(clk),其相位彼此反相180度。在这种情况下,时钟信号(clk)的数目为两个。

[0093]

边缘确定电路154基于由边缘检测电路153检测的边缘来生成接收数据(r_data)。边缘历史电路155是存储电路,该存储电路用于基于作为边缘确定电路154的输出的接收边缘信息(rei)来存储先前周期的相位移位(延迟)信息(ldi)。计数器156基于接收边缘信息(rei)来初始化,并且对时钟信号(clk)进行计数。

[0094]

时钟生成电路157基于接收边缘信息(rei)来生成接收时钟(r_clk)。

[0095]

参考图8对检测中间边缘的方法进行解释。图8是示出了图7所示的解码器的操作波形的时序图。当曼彻斯特编码的输入周期为10ns(100mbps)时,在小于

±

1.875ns(即,“采样周期

”×

3/2)的抖动中实现操作。下文将对采样周期为1.25ns且抖动为

±

1.5ns的系统进行解释。

[0096]

发送参考信号(t_ref)与用作图1的开始点的发送时钟(clk)相对应。接收输入信号(r_in)与图3中的曼彻斯特编码输入和用作图1中的输入第一级逻辑的触发器201的输入信号相对应。接收输入信号(r_in)是图7中的同步电路151的串行输入信号(si)或边缘检测电路153的输入信号。

[0097]

输入信号(s_in)是在对接收输入信号(r_in)进行采样之后获得的信号,并且与图3的曼彻斯特编码输入相对应。输入信号(s_in)是图7的同步电路151的输出信号、边缘检测电路153内的噪声滤波器152或f/f电路的输出信号。输入信号(s_in)是曼彻斯特编码信号,因此该信号始终具有中间边缘但经常没有边界边缘。

[0098]

在这种情况下,图8的输入信号(s_in)的(a)至(c)示出了以下情况下的信号波形。

[0099]

(a)小延迟(从平均值开始

‑

1.875ns至

‑

0.625ns)

[0100]

(b)中等延迟(从平均值开始

±

0.625ns之内)

[0101]

(c)大延迟(从平均值开始+0.625ns至+1.875ns)

[0102]

并且,情况(a)至(c)取决于抖动,并且因此可能针对每个边缘而发生改变。例如,即使当第一中间边缘me1处于情况(a)时,第二边界边缘be2也不局限于情况(a),而是可以处于情况(a)至(c)中的任何一种情况。并且,当第一中间边缘me1处于情况(b)或(c)时,第二边界边缘be2同样可以处于情况(a)至(c)中的任何一种情况。

[0103]

图8中的实线箭头指示对中间边缘的采样,而虚线箭头指示对边界边缘的采样。为了从曼彻斯特编码信号中提取时钟和数据,需要识别该中间边缘与该边界边缘之间的差异。

[0104]

当边缘确定电路154检测到边缘时,计数器(cntr)156的值被清除为“0”,并且在每个采样周期中将其递增1。然而,图8示出了为了便于理解值连续递增的情况(没有检测到第二中间边缘me2的情况)。

[0105]

对作为检测目标中间边缘的示例的第二中间边缘me2的检测方法进行解释。

[0106]

首先,将对存储在边缘历史电路155中的延迟信息(ldi)进行解释。存储在边缘历史电路155中的延迟信息(ldi)的值由“0”、“1”和“2”这三个值构成。

[0107]

延迟信息(ldi)为“0”的情况是未知延迟情况,并且表明输入信号(r_in)处于图8的情况(a)、(b)或(c)。第二中间边缘me2的数据检测范围被设置为使得计数器156的计数器值为6至10。延迟信息(ldi)为“0”的情况被称为“边缘历史0”,并且被表达为“eh=0”。

[0108]

延迟信息(ldi)为“1”的情况是小延迟情况或中等延迟情况,并且表明输入信号(r_in)处于图8的情况(a)或(b)。第二中间边缘me2的数据检测范围被设置为使得计数器值为7至10。延迟信息(ldi)为“1”的情况被称为“边缘历史1”,并且被表达为“eh=1”。

[0109]

延迟信息(ldi)为“2”的情况是中等延迟情况或大延迟情况,并且表明输入信号(r_in)处于图8的的情况(b)或(c)。第二中间边缘me2的数据检测范围被设置为使得计数器值为6至9。延迟信息(ldi)为“2”的情况被称为“边缘历史2”,并且被表达为“eh=2”。

[0110]

对第二中间边缘me2的边缘历史的检测操作和更新进行解释,该第二中间边缘me2是第一中间边缘me1的每个边缘历史的下一周期的中间边缘,该第一中间边缘me1是先前周期的中间边缘。

[0111]

边缘历史1(eh=1)中的操作:

[0112]

在第一中间边缘me1处于情况(a)或(b)的情况(eh=1)下,当计数器156的计数器值为7至10中的任何一个值时,第二中间边缘me2出现。尽管当计数器值为3至6或11至14时,可能会出现边缘,但是这些边缘由于是边界边缘(第二边界边缘be2或第三边界边缘be3)而可忽略。边缘确定电路154检测计数器值的7至10范围内的边缘。

[0113]

当该边缘从高电平(h)变为低电平(l)时,边缘确定电路154将接收数据(r_data)输出为“1”,或当该边缘从低电平(l)变为高电平(h)时,将接收数据(r_data)输出为“0”,并且输出接收时钟(r_clk)。在下文中,从高电平(h)到低电平(l)的改变被称为“h

→

l”,并且从低电平(l)到高电平(h)的改变被称为“l

→

h”。

[0114]

当边缘检测时的计数器值为7或8时,第二中间边缘me2处于情况(a)或(b)(eh=1),边缘确定电路154将值“1”存储到边缘历史电路155中,并且更新边缘历史。当边缘检测时的计数器值为9或10时,第二中间边缘me2处于情况(b)或(c)(eh=2),边缘确定电路154将值“2”存储到边缘历史电路155中,并且更新边缘历史。

[0115]

边缘历史2(eh=2)中的操作:

[0116]

在第一中间边缘me1处于情况(b)或(c)的情况下(eh=2),当计数器156的计数器值为6至9中的任何一个值时,第二中间边缘me2出现。尽管当计数器值为2至5或10至13时,可能会出现边缘,但是这些边缘由于是边界边缘(第二边界边缘be2或第三边界边缘be3)而可忽略。边缘确定电路154检测计数器值的6至9范围内的边缘。

[0117]

边缘确定电路154在该边缘的改变为“h

→

l”时将接收数据(r_data)输出为“1”,并且当该边缘的改变为“l

→

h”时,将接收数据(r_data)输出为“0”,并且输出接收时钟(r_clk)。

[0118]

当边缘检测时的计数器值为6或7时,第二中间边缘me2处于情况(a)或(b)(eh=1),并且边缘确定电路154将值“1”存储到边缘历史电路155中,并且更新边缘历史。当边缘检测时的计数器值为8或9时,第二中间边缘me2处于情况(b)或(c)(eh=2),边缘确定电路154将值“2”存储到边缘历史电路155中,并且更新边缘历史。

[0119]

边缘历史操作0(eh=0):

[0120]

在第一周期中的边缘的情况下,当假设开始位为“1”时,中间边缘的改变必然为“h

→

l”。因此,在移位“h

→

l”时,第一周期中的计数器值被清除为“0”,输出“1”作为接收数据(r_data),并且输出接收时钟(r_clk)。在第一周期中,无法确定中间边缘处于(a)至(c)情况中的哪种情况,因此设置“eh=0”。

[0121]

在包括第一周期的“eh=0”的情况下,第二中间边缘me2的可接受计数器值为6至10。如果仅在计数器值的6至10的范围内检测到单个边缘,则边缘确定电路154基于边缘检测时的计数器值来如下计算边缘历史。

[0122]

当计数器值为6或7时,边缘确定电路154确定第二中间边缘me2处于情况(a)或(b),将值“1”存储到边缘历史电路155中,并且更新边缘历史。

[0123]

当计数器值为8时,边缘确定电路154确定第二中间边缘me2与第一中间边缘me1的延迟相同,将值“0”存储到边缘历史电路155中,并且更新边缘历史。

[0124]

当计数器值为9或10时,边缘确定电路154确定第二中间边缘me2处于情况(b)或(c),将值“2”存储到边缘历史电路155中,并且更新边缘历史。

[0125]

在“eh=0”的情况下,很少会在计数器值6和10处检测到两个边缘。在“eh=0”的情况下,无法确定边缘中的哪个边缘是中间边缘或哪个边缘是边界边缘,因此,边缘确定电路154生成解码误差。当生成解码误差时,接收电路140在此之后停止接收,直至接收下一帧为止,并且完全丢弃该帧或丢弃在生成误差之后获得的位。当丢弃对整个帧或部分位的接收时,接收电路140中的接收缓冲器(bffr)141保留先前值。此外,即使在除了“eh=0”的情况之外的其他情况下,因为由于噪声等引起的误差操作也可能检测到两个或更多个边缘。即使在这些情况下,与上文描述相似,边缘确定电路154也生成解码误差。

[0126]

参考图9对解码器150的边缘检测操作进行解释。图9是示出了当图7中所示的解码器检测到下降边缘时执行的硬件处理的流程图。

[0127]

(步骤s0)

[0128]

边缘检测电路153检测到改变为“h

→

l”的边缘。

[0129]

(步骤s1)

[0130]

边缘确定电路154输出“1”作为输入信号(r_data),并且将接收边缘信息(rei)输出到边缘历史电路155、计数器156和时钟生成电路157。时钟生成电路156基于接收边缘信息(rei)来生成并输出接收时钟(r_clk)。计数器156基于接收边缘信息(rei)来将计数器值清除为“0”。边缘历史电路155基于接收边缘信息(rei)来存储边缘历史“0”。

[0131]

(步骤s2)

[0132]

边缘确定电路154基于边缘历史来设置检测范围。在该过程中,检测范围的下限为

“

wl”,而检测范围的上限为“wh”。

[0133]

(步骤s3)

[0134]

计数器156的计数器值通过时钟信号(clk)递增。

[0135]

(步骤s4)

[0136]

边缘确定电路154确定计数器156的计数器值是否等于或大于检测范围的下限(wl)。

[0137]

(步骤s5)

[0138]

边缘确定电路154确定计数器156的计数器值是否等于或小于检测范围的上限(wh)。

[0139]

(步骤s6)

[0140]

边缘确定电路154基于边缘检测电路153的输出来确定是否已经检测到边缘。

[0141]

(步骤s7)

[0142]

边缘确定电路154确定所检测的边缘是否为第一检测的边缘。

[0143]

(步骤s8)

[0144]

边缘确定电路154将边缘检测时的计数器156的计数器值设置为第一边缘位置。

[0145]

(步骤s9)

[0146]

边缘确定电路154输出输入信号(r_data),并且将接收边缘信息(rei)输出到边缘历史电路155、计数器156和时钟生成电路157。时钟生成电路156基于接收边缘信息(rei)来生成并输出接收时钟(r_clk)。边缘历史电路155基于接收边缘信息(rei)来更新边缘历史。

[0147]

(步骤s10)

[0148]

在步骤s5中,如果计数器值大于检测范围的上限,则计数器156将计数器值清除为“0”。

[0149]

(步骤11)

[0150]

在步骤s7中,如果所检测的边缘是第二检测的边缘,则边缘确定电路154输出解码误差。

[0151]

根据第一工作示例,当基于先前边缘历史来改变用于识别中间边缘的计数器值时,在曼彻斯特编码数据的周期的1/8的采样周期内并且以小于曼彻斯特编码数据周期的

±

(1/8

×

2/3)的抖动实现解码。

[0152]

(第二工作示例)

[0153]

参考图10对根据第二工作示例的第二中间边缘(me2)的检测方法进行解释。图10是示出了根据第二工作示例的解码器的操作波形的时序图。

[0154]

根据第二实施例的解码器在配置上与根据第一工作示例的解码器150和解码器250相同。然而,边缘确定电路154和边缘历史电路155的操作不同。当曼彻斯特编码信号的输入周期为10ns(100mbps)时,以小于

±

2.5ns的抖动(即,采样周期

×

2)实现操作。以下解释将在抖动为

±

1.5ns的系统中进行。

[0155]

在第二工作示例中,在以下情况下,输入信号(s_in)的(a)至(d)示出了信号波形。

[0156]

(a)小延迟(从平均值开始

‑

2.5ns至

‑

1.25ns)

[0157]

(b)稍小延迟(从平均值开始

‑

1.25ns至0ns)

[0158]

(c)稍大延迟(从平均值开始0ns至+1.25ns)

[0159]

(d)大延迟(从平均值开始1.25ns至+2.5ns)

[0160]

并且,情况(a)至(d)取决于抖动,因此可能针对每个边缘而发生改变。例如,即使当第一中间边缘me1处于情况(a)时,第二中间边缘me2也不是局限于情况(a),而是可以处于情况(a)至(d)中的任何一种情况。并且,处于情况(b)至(d)的第二中间边缘me2也是如此。

[0161]

图10中的实线箭头指示对中间边缘的采样,而虚线箭头指示对边界边缘的采样。为了从曼彻斯特编码信号中提取时钟和数据,需要识别该中间边缘与该边界边缘之间的差异。

[0162]

当边缘确定电路154检测到边缘时,计数器156的值被清除为”0”,并且在每个采样周期中将其递增1。然而,图10示出了为了便于理解值连续递增的情况(没有检测到第二中间边缘me2的情况)。

[0163]

对作为检测目标的第二中间边缘me2的检测方法进行解释。存储在边缘历史电路155中的延迟信息(ldi)的值由“0”至“9”的十个值构成。

[0164]

延迟信息(ldi)为“0”的情况是未知延迟情况,并且表明输入信号(r_in)处于图10的情况(a)、(b)、(c)或(d)。第二中间边缘me2的数据检测范围被设置为使得计数器156的计数器值为5至11。延迟信息(ldi)为“0”的情况被称为“边缘历史0”,并且被表达为“eh=0”。

[0165]

延迟信息(ldi)为“1”的情况是小延迟情况,并且表明输入信号(r_in)处于图10的情况(a)。第二中间边缘me2的数据检测范围被设置为使得计数器值为8至11。延迟信息(ldi)为“1”的情况被称为“边缘历史1”,并且被表达为“eh=1”。

[0166]

延迟信息(ldi)为“2”的情况是稍小延迟情况,并且表明输入信号(r_in)处于图10的情况(b)。第二中间边缘me2的数据检测范围被设置为使得计数器值为7至10。延迟信息(ldi)为“2”的情况被称为“边缘历史2”,并且被表达为“eh=2”。

[0167]

延迟信息(ldi)为“3”的情况是稍大延迟情况,并且表明输入信号(r_in)处于图10的情况(c)。第二中间边缘me2的数据检测范围被设置为使得计数器值为6至9。延迟信息(ldi)为“3”的情况被称为“边缘历史3”,并且被表达为“eh=3”。

[0168]

延迟信息(ldi)为“4”的情况是大延迟情况,并且表明输入信号(r_in)处于图10的情况(d)。第二中间边缘me2的数据检测范围被设置为使得计数器值为5至8。延迟信息(ldi)为“4”的情况被称为“边缘历史4”,并且被表达为“eh=4”。

[0169]

延迟信息(ldi)为“5”的情况是非大延迟情况,并且表明输入信号(r_in)处于图10的情况(a)、(b)或(c)。第二中间边缘me2的数据检测范围被设置为使得计数器值为6至11。延迟信息(ldi)为“5”的情况被称为“边缘历史5”,并且被表达为“eh=5”。

[0170]

延迟信息(ldi)为“6”的情况是非小延迟情况,并且表明输入信号(r_in)处于图10的情况(b)、(c)或(d)。第二中间边缘me2的数据检测范围被设置为使得计数器值为5至10。延迟信息(ldi)为“6”的情况被称为“边缘历史6”,并且被表达为“eh=6”。

[0171]

延迟信息(ldi)为“7”的情况是小延迟情况,并且表明输入信号(r_in)处于图10的情况(a)或(b)。第二中间边缘me2的数据检测范围被设置为使得计数器值为7至11。延迟信息(ldi)为“7”的情况被称为“边缘历史7”,并且被表达为“eh=7”。

[0172]

延迟信息(ldi)为“8”的情况是大延迟情况,并且表明输入信号(r_in)处于图10的情况(c)或(d)。第二中间边缘me2的数据检测范围被设置为使得计数器值为5至9。延迟信息

(ldi)为“8”的情况被称为“边缘历史8”,并且被表达为“eh=8”。

[0173]

延迟信息(ldi)为“9”的情况是非小延迟情况,并且表明输入信号(r_in)处于图10的情况(b)或(c)。第二中间边缘me2的数据检测范围被设置为使得计数器值为6至10。延迟信息(ldi)为“9”的情况被称为“边缘历史9”,并且被表达为“eh=9”。

[0174]

对第二中间边缘me2的边缘历史的检测操作和更新进行解释,该第二中间边缘me2是第一中间边缘me1的每个边缘历史的下一周期的中间边缘,该第一中间边缘me1是先前周期的中间边缘。

[0175]

边缘历史1(eh=1)中的操作:

[0176]

在第一中间边缘me1处于(a)的情况(eh=1)下,当计数器156的计数器值为8至11中的任何一个值时,第二中间边缘me2出现。尽管当计数器值为4至7或12至15时,可能会出现边缘,但是这些边缘由于是边界边缘(第二边界边缘be2或第三边界边缘be3)而可忽略。边缘确定电路154检测计数器值的8至11范围内的边缘。

[0177]

当该边缘的改变为“h

→

l”时,边缘确定电路154将接收数据(r_data)输出为“1”,或当该边缘的改变为“l

→

h”时,将接收数据(r_data)输出为“0”,并且输出接收时钟(r_clk)。

[0178]

边缘确定电路154基于该边缘检测时的计数器值来确定第二中间边缘me2的延迟状态,将该延迟信息存储到边缘历史电路155中,并且将该延迟信息用于确定又下一周期的第三中间边缘me3。

[0179]

在“计数器值=8”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a),将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0180]

在“计数器值=9”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b),将值“2”存储到边缘历史电路155中,并且更新边缘历史(eh=2)。

[0181]

在“计数器值=10”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(c),将值“3”存储到边缘历史电路155中,并且更新边缘历史(eh=3)。

[0182]

在“计数器值=11”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0183]

边缘历史2(eh=2)中的操作:

[0184]

在第一中间边缘me1处于情况(b)的情况(eh=2)下,当计数器156的计数器值为7至10中的任何一个值时,第二中间边缘me2出现。边缘确定电路154将在计数器值的范围7至10内检测的边缘确定为第二中间边缘me2,并且基于此时数据的改变来输出接收数据(r_data)和接收时钟(r_clk)。

[0185]

边缘确定电路154基于该边缘检测时的计数器值来确定第二中间边缘me2的延迟状态,将该延迟信息存储到边缘历史电路155中,并且将该延迟信息用于确定下一周期的第三中间边缘me3。

[0186]

在“计数器值=7”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a),将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0187]

在“计数器值=8”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b),将值“2”存储到边缘历史电路155中,并且更新边缘历史(eh=2)。

[0188]

在“计数器值=9”的情况下,边缘确定电路154确定第二中间边缘me2处于情况

(c),将值“3”存储到边缘历史电路155中,并且更新边缘历史(eh=3)。

[0189]

在“计数器值=10”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0190]

边缘历史3(eh=3)中的操作:

[0191]

在第一中间边缘me1处于情况(c)的情况(边缘历史3(eh=3))下,当计数器156的计数器值为6至9中的任何一个值时,第二中间边缘me2出现。边缘确定电路154将在计数器值的范围6至9内检测到的边缘确定为第二中间边缘me2,并且基于此时的数据改变来输出接收数据(r_data)和接收时钟(r_clk)。

[0192]

边缘确定电路154基于该边缘检测时的计数器值来确定第二中间边缘me2的延迟状态,将该延迟信息存储到边缘历史电路155中,并且将该延迟信息用于确定下一周期的第三中间边缘me3。

[0193]

在“计数器值=6”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a),将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0194]

在“计数器值=7”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b),将值“2”存储到边缘历史电路155中,并且更新边缘历史(eh=2)。

[0195]

在“计数器值=8”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(c),将值“3”存储到边缘历史电路155中,并且更新边缘历史(eh=3)。

[0196]

在“计数器值=9”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0197]

边缘历史4(eh=4)中的操作:

[0198]

在第一中间边缘me1处于情况(d)的情况(eh=4)下,当计数器156的计数器值为5至8中的任何一个值时,第二中间边缘me2出现。边缘确定电路154确定在计数器值的范围5至8内检测到的边缘作为第二中间边缘me2,并且基于此时数据的改变来输出接收数据(r_data)和接收时钟(r_clk)。

[0199]

边缘确定电路154基于该边缘检测时的计数器值来确定第二中间边缘me2的延迟状态,将该延迟信息存储到边缘历史电路155中,并且将该延迟信息用于确定下一周期的第三中间边缘me3。

[0200]

在“计数器值=5”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a),将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0201]

在“计数器值=6”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b),将值“2”存储到边缘历史电路155中,并且更新边缘历史(eh=2)。

[0202]

在“计数器值=7”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(c),将值“3”存储到边缘历史电路155中,并且更新边缘历史(eh=3)。

[0203]

在“计数器值=8”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0204]

边缘历史0(eh=0)中的操作:

[0205]

与第一工作示例相似,第一周期的边缘的情况是“eh=0”。并且,在情况(a)至(d)的任何一种情况下,其中先前周期的中间边缘(第一中间边缘me1)未知的情况也是“eh=0”。

[0206]

在情况(eh=0)下,第二中间边缘me2的可接受的计数器值为5至11。当在计数器值的范围5至11内仅检测到单个边缘时,边缘确定电路154基于此时数据的改变来输出接收数据(r_data)和接收时钟(r_clk)。然后,边缘确定电路154基于边缘检测时的计数器值来如下计算下一边缘历史。

[0207]

在“计数器值=5”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a),将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0208]

在“计数器值=6”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a)或(b),将值“7”存储到边缘历史电路155中,并且更新边缘历史(eh=7)。

[0209]

在“计数器值=7”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a)、(b)或(c),将值“5”存储到边缘历史电路155中,并且更新边缘历史(eh=5)。

[0210]

在“计数器值=8”的情况下,边缘确定电路154不能确定第二中间边缘me2处于情况(a)至(d)中的任何一种情况,将值“0”存储到边缘历史电路中155,并且更新边缘历史(eh=0)。

[0211]

在“计数器值=9”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b)、(c)或(d),将值“6”存储到边缘历史电路155中,并且更新边缘历史(eh=6)。

[0212]

在“计数器值=10”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(c)或(d),将值“8”存储到边缘历史电路155中,并且更新边缘历史(eh=8)。

[0213]

在“计数器值=11”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0214]

边缘历史5(eh=5)中的操作:

[0215]

在第一中间边缘me1被确定为处于情况(a)、(b)或(c)的情况(eh=5)下,第二中间边缘me2的计数器156的可接受计数器值为6至11。当在计数器值中仅检测到一个边缘时,边缘确定电路154基于此时数据的改变来输出接收数据(r_data)和接收时钟(r_clk)。

[0216]

边缘确定电路154基于边缘检测时的计数器值来如下计算下一边缘历史。

[0217]

在“计数器值=6”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a),将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0218]

在“计数器值=7”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a)或(b),将值“7”存储到边缘历史电路155中,并且更新边缘历史(eh=7)。

[0219]

在“计数器值=8”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a)、(b)或(c),将值“5”存储到边缘历史电路155中,并且更新边缘历史(eh=5)。

[0220]

在“计数器值=9”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b)、(c)或(d),将值“6”存储到边缘历史电路155中,并且更新边缘历史(eh=6)。

[0221]

在“计数器值=10”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(c)或(d),将值“8”存储到边缘历史电路155中,并且更新边缘历史(eh=8)。

[0222]

在“计数器值=11”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0223]

边缘历史6(eh=6)中的操作:

[0224]

在第一中间边缘me1被确定为处于情况(b)、(c)或(d)的情况下,第二中间边缘me2的计数器156的可接受计数器值为5至10。当在计数器值中仅检测到单个边缘时,边缘确定

电路154基于此时数据的改变来输出接收数据(r_data)和接收时钟(r_clk)。

[0225]

边缘确定电路154基于边缘检测时的计数器值来如下计算下一边缘历史。

[0226]

在“计数器值=5”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a),将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0227]

在“计数器值=6”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a)或(b),将值“7”存储到边缘历史电路155中,并且更新边缘历史(eh=7)。

[0228]

在“计数器值=7”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a)、(b)或(c),将值“5”存储到边缘历史电路155中,并且更新边缘历史(eh=5)。

[0229]

在“计数器值=8”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b)、(c)或(d),将值“6”存储到边缘历史电路155中,并且更新边缘历史(eh=6)。

[0230]

在“计数器值=9”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(c)或(d),将值“8”存储到边缘历史电路155中,并且更新边缘历史(eh=8)。

[0231]

在“计数器值=10”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0232]

边缘历史7(eh=7)中的操作:

[0233]

在第一中间边缘me1被确定为情况(a)或(b)的情况(eh=7)下,第二中间边缘me2的计数器156的可接受计数器值为7至11。在计数器值中仅检测到单个边缘时,边缘确定电路154基于此时数据的改变来输出接收数据(r_data)和接收时钟(r_clk)。

[0234]

边缘确定电路154基于边缘检测时的计数器值来如下计算下一边缘历史。

[0235]

在“计数器值=7”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a),将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0236]

在“计数器值=8”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a)或(b),将值“7”存储到边缘历史电路155中,并且更新边缘历史(eh=7)。

[0237]

在“计数器值=9”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b)或(c),将值“9”存储到边缘历史电路155中,并且更新边缘历史(eh=9)。

[0238]

在“计数器值=10”的情况下,边缘确定电路154确定第二中间边缘me2在情况(c)或(d),将值“8”存储到边缘历史电路155中,并且更新边缘历史(eh=8)。

[0239]

在“计数器值=11”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0240]

边缘历史8(eh=8)中的操作:

[0241]

在第一中间边缘me1被确定为情况(c)或(d)的情况(eh=8)下,第二中间边缘me2的计数器156的可接受计数器值为5至9。当在计数器值中仅检测到单个边缘时,边缘确定电路154基于此时数据的改变来输出接收数据(r_data)和接收时钟(r_clk)。

[0242]

边缘确定电路154基于边缘检测时的计数器值来如下计算下一边缘历史。

[0243]

在“计数器值=5”的情况下,边缘确定电路154确定第二中间边缘me2在情况(a)中,将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0244]

在“计数器值=6”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a)或(b),将值“7”存储到边缘历史电路155中,并且更新边缘历史(eh=7)。

[0245]

在“计数器值=7”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b)

或(c),将值“9”存储到边缘历史电路155中,并且更新边缘历史(eh=9)。

[0246]

在“计数器值=8”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(c)或(d),将值“8”存储到边缘历史电路155中,并且更新边缘历史(eh=8)。

[0247]

在“计数器值=9”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0248]

边缘历史9(eh=9)中的操作:

[0249]

在第一中间边缘me1被确定为情况(b)或(c)的情况(eh=9)下,第二中间边缘me2的计数器156的可接受计数器值为6至10。当在计数器值中仅检测到单个边缘时,边缘确定电路154基于此时数据的改变来输出接收数据(r_data)和接收时钟(r_clk)。

[0250]

边缘确定电路154基于边缘检测时的计数器值来如下计算下一边缘历史。

[0251]

在“计数器值=6”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a),将值“1”存储到边缘历史电路155中,并且更新边缘历史(eh=1)。

[0252]

在“计数器值=7”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(a)或(b),将值“7”存储到边缘历史电路155中,并且更新边缘历史(eh=7)。

[0253]

在“计数器值=8”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(b)或(c),将值“9”存储到边缘历史电路155中,并且更新边缘历史(eh=9)。

[0254]

在“计数器值=9”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(c)或(d),将值“8”存储到边缘历史电路155中,并且更新边缘历史(eh=8)。

[0255]

在“计数器值=10”的情况下,边缘确定电路154确定第二中间边缘me2处于情况(d),将值“4”存储到边缘历史电路155中,并且更新边缘历史(eh=4)。

[0256]

在“eh=0”或“eh=5至9”的情况下,可能检测到边缘两次。在这种情况下,如下文所描述的,可以通过结合先前周期的中间边缘的边缘历史和检测到下一周期的边缘的两个计数器值来确定哪个边缘是中间边缘。在该过程中,基于此时数据的改变来输出所确定的中间边缘处的接收数据(r_data)和接收时钟(r_clk),并且计算下一边缘历史。

[0257]

在“eh=0”的情况下以及在两个计数器值中的一个计数器值为8的情况下,计数器值8处的边缘被确定为中间边缘。

[0258]

在“eh=5”的情况下以及在两个计数器值中的一个计数器值为8或9的情况下,边缘确定电路154确定计数器值为8或9的边缘为中间边缘。

[0259]

在“eh=6”的情况下以及在两个计数器值中的一个计数器值为7或8的情况下,边缘确定电路154确定计数器值为7或8的边缘为中间边缘。

[0260]

在“eh=7”的情况下以及在两个计数器值中的一个计数器值为8、9或10的情况下,边缘确定电路154确定计数器值为8、9或10的边缘为中间边缘。

[0261]

在“eh=8”的情况下以及在两个计数器值中的一个计数器值为6、7或8的情况下,边缘确定电路154确定计数器值为6、7或8的边缘为中间边缘。

[0262]

在“eh=9”的情况下以及两个计数器值中的一个计数器值为7、8或9的情况下,边缘确定电路154确定计数器值为7、8或9的边缘为中间边缘。

[0263]

在“eh=0”的情况下或在“eh=5至9”的情况下,即使通过上文所描述的确定,也不能经常确定哪一个是中间边缘。在这种情况下,边缘确定电路154过程解码误差。当生成解码误差时,接收电路140停止后续接收,直至接收到下一帧,并且完全丢弃该帧或丢弃发生

误差之后获得的位。当丢弃整个帧或对部分位的接收时,接收电路140中的接收缓冲器141保留先前值,并且不执行更新。

[0264]

不管边缘历史如何,由于噪声或其他因素的影响,可能存在检测两个或更多个边缘的情况。即使在这种情况下,也不能确定由噪声引起的中间边缘、边界边缘和伪边缘中的哪个边缘是目标边缘,因此,边缘确定电路154生成解码误差。当生成解码误差时,接收电路140停止后续接收,直至接收到下一帧,并且完全丢弃该帧或丢弃发生误差之后获得的位。当丢弃整个帧或对部分位的接收时,接收电路140中的接收缓冲器141保持先前值,并且不执行更新。

[0265]

参考图6对根据第二实施例的解码器150的边缘检测操作进行解释。图11是示出了当根据第二工作示例的解码器检测到下降边缘时执行的硬件处理的流程图。

[0266]

根据第二工作示例的步骤s0至s6中的操作与第一工作示例的操作相同。

[0267]

(步骤s12)

[0268]

边缘确定电路154确定在所检测的边缘之前已经接收了多少个边缘。

[0269]

(步骤s13)

[0270]

如果所检测的边缘是第一边缘,则边缘确定电路154将计数器156的计数器值设置为第一边缘位置(t1)。

[0271]

(步骤s14)

[0272]

如果所检测的边缘是第二边缘,则边缘确定电路154将计数器156的计数器值设置为第二边缘位置(t2)。

[0273]

(步骤s15)

[0274]

在步骤s5中,如果计数器值大于检测范围的上限,则边缘确定电路154基于边缘历史以及t1和t2来如下执行。边缘确定电路154检查解码误差。并且,边缘确定电路154输出输入信号(r_data),并且将接收边缘信息(rei)输出到边缘历史电路155、计数器156和时钟生成电路157。时钟生成电路156基于接收边缘信息(rei)来生成并输出接收时钟(r_clk)。边缘历史电路155基于接收边缘信息(rei)来更新边缘历史。

[0275]

(步骤s16和步骤s17)

[0276]

在步骤s16中,边缘确定电路154确定是否存在解码误差。在步骤s17中,如果在步骤s16中未检测到解码误差,则计数器156将计数器值清除为“0”。

[0277]

(步骤18)

[0278]

如果在步骤s12中检测的边缘是第三边缘并且如果在步骤s16中已经确定了误差,则边缘确定电路154输出解码误差。

[0279]

根据第二工作示例,当用于识别中间边缘的计数器值通过先前边缘历史改变时,在作为曼彻斯特编码数据的周期的1/8的采样周期中并且以高达曼彻斯特编码数据的周期的

±

(1/8

×

2)的抖动实现解码。第二工作示例的抖动范围是第一工作示例的抖动范围的4/3倍。

[0280]

(第三工作示例)

[0281]

图12是示出了根据第三工作示例的解码器的配置的框图。图13是示出了三输入多数判定电路的电路图。图14是示出了图12中所示的用于移位的触发器、用于数据采样的触发器、噪声滤波器和边缘检测电路的配置的框图。图15是示出了图12中所示的边缘识别电

路的配置的一部分的框图。图16是示出了图12中所示的边缘识别电路的配置的一部分的框图。图17是图12中所示的时钟生成电路的框图。

[0282]

与第一工作示例类似,根据第三工作示例的解码器150包括同步电路(sync)151、噪声滤波器(fltr)152、边缘检测电路(edc)153和时钟生成电路(cg)157。根据第三工作示例的解码器150还包括边缘识别电路158,以代替根据第一工作示例的边缘确定电路(ejc)154、边缘历史电路(ehc)155和计数器(cntr)156。

[0283]

如图12中所示,同步电路(sync)151由移位触发器(s_f/f)151a和数据采样触发器(d_f/f)151b构成。400mhz的两相时钟(clkup_p和clkup_n)、曼彻斯特编码信号(mc_si)和100mhz的时钟(clk1)输入到同步电路(sync)151。时钟(clk1)是从曼彻斯特编码信号(mc_si)提取的时钟。使用400mhz的两相时钟(clkup_p和clkup_n)进行采样是使用800mhz的时钟进行采样。

[0284]

如图14中所示,移位触发器151a由串行连接的触发器构成,并且在使用两相时钟(clkup_p和clkup_n)的同时,顺序接收曼彻斯特编码信号(mc_si)。在该过程中,移位触发器151a由例如18个触发器构成。接收到触发器151a中的数据被称为“sin[*]”。数据采样触发器(d_f/f)151b由触发器构成,这些触发器的数目与移位触发器151a的数目相同。数据采样触发器151b以时钟(clk1)的上升时序并行采样已经被接收到触发器151a中的数据。已经接收到数据采样触发器151b中的数据被称为“data1[*]”。

[0285]

如图13中所示,噪声滤波器152由三输入多数判定电路构成。该电路是如果两个或更多条数据为“1”则输出“1”的电路。噪声滤波器152例如由16个三输入多数判定电路构成。

[0286]

边缘检测电路153从已经通过噪声滤波器152的data1[*]信号中提取具有不同的相邻位值的数据。指示检测到数据从“0”变为“1”的信号是“edge_r[*]”,而指示检测到数据从“1”变为“0”的信号是“edge_f[*]”。术语“edge_r[*]”也称为“edge_r[n:0],术语“edge_f[*]”也称为“edge_f[n:0]”。在这种情况下,“n”是自然数。例如,假设“n=14”。

[0287]

边缘识别电路158包括移位电路(shftr)1581和移位电路1582、窗口切断电路1583和窗口切断电路1584、以及边缘历史电路(edghs)1585。

[0288]

移位电路1581和移位电路1582输出通过将相应的信号“edges_r[n:0]”和信号“edges_f[n:0]”移位一移位量(sft[i:0])而获得的信号“edges_r[n:0]”和信号“edges_f[n:0]”。移位量(sft[i:0])由稍后描述的移位量生成电路1587生成。如果移位量(sft[i:0])的值为正,则移位电路1581和移位电路1582将相应的信号“edge_r[n:0]”和信号“edge_f[n:0]”向右(朝向低阶位)移位。如果移位量(sft[i:0])的值为负,则移位电路1581和移位电路1582将相应的信号“edge_r[n:0]”和信号“edge_f[n:0]”向左(朝向高阶位)移位。

[0289]

虽然下文对窗口切断电路1583进行了解释,但是窗口切断电路1584的操作与窗口切断电路1583的操作相似。窗口切断电路1583从“edges_r[n:0]”中提取5个位,并且设置“edgec_r[4:0]”,即,其中检测到中间边缘的范围(中间边缘检测范围)。中间边缘检测范围由“sft[i:0]”控制。例如,在检测到中间边缘之后,“edgec_r[4:0]”的任何位都变为“1”。边缘历史电路1585记录“edgec_r”,该“edgec_r”指示其中已经检测到中间边缘的先前周期的位置(中间边缘位置)。窗口切断电路1583基于在边缘历史电路1585中记录的先前周期的中间边缘位置(edgec_r)来校正中间边缘检测范围(edgec_r[4:0])。

[0290]

更具体地,如果先前周期的中间边缘位置(edgec_r)在中间边缘检测范围(edgec_

r[4:0])的高阶位,则窗口切断电路1583屏蔽最高阶位(位[4])。在该过程中,高阶位是位[3]或位[4]。即,中间边缘检测范围(edgec_r[4:0])的位[3:0]被设置为边缘检测范围。如果先前周期的中间边缘位置(edgec_r)处于其低阶位(位[0]或位[1]),则窗口切断电路1583屏蔽中间边缘检测范围(edgec_r[4:0])的最低阶位(位[0])。即,中间边缘检测范围(edgec_r[4:0])的位[4:1]被设置为边缘检测范围。如果先前周期的中间边缘位置(edgec_r)是另一位(位[2]),则要屏蔽位不变,换言之,要屏蔽位被设置为与先前周期的屏蔽位相同。

[0291]

如图15中所示,边缘识别电路158还包括数据检测电路1586。如果“edgec_r[4:0]”的任何位为1,则这意味着从“0”变为“1”的边缘存在于中间边缘检测范围,因此,数据检测电路1586将“data_1”信号设置为“1”。如果“edgec_f[4:0]”的任何位为1,则这意味着从“1”变为“0”的边缘存在于中间边缘检测范围内,因此,数据检测电路1586将“data_0”信号设置为“1”。然而,如果“edgec_r[4:0]”和“edgec_f[4:0]”两者都包含“1”,则不能识别出偏差,因此,数据检测电路1586将“cdr_error”信号设置为“1”。如果“edgec_r[4:0]”和“edgec_f[4:0]”的所有位均为“0”,则数据检测电路1586确定没有中间边缘,换言之,确定这并非该帧(帧结束),并且将“无源”信号设置为“1”。

[0292]

如图16中所示,边缘识别电路158还包括移位量生成电路1587和时钟控制电路1588。

[0293]

移位量生成电路1587包括触发器1587a,该触发器1587a存储指示移位量的“sft[*]”值。如果检测到帧中的第一下降边缘,则“edgef_f[4:0]”包含“1”。这被设置为初始值,并且在“edgef_f[4:0]”中具有“1”的位值被输入到触发器1587a。即,初始sft[*]值与在帧开始时叠加在曼彻斯特编码信号(mc_si)上的时钟与在帧开始时在解码器150中生成的具有相同频率的时钟(clk1)之间的相位差相对应。

[0294]

然后,在由于抖动而使800mhz的时钟(clkup_p/clkup_n)移位了一个周期的情况下,增减电路(inc/dec)1587b校正sft[*]值以变为“值+1”或“值

‑

1”。在该过程中,移位一个周期与“edgec_r[3]”、“edgec_f[3]”、“edgec_r[1]”或“edgec_f[1]”为“1”的情况相对应。如果“edgec_r[3]”或“edgec_f[3]”为“1”,则sft[*]值递增“1”(以变为“值+1”)。如果“edgec_r[1]”或“edgec_f[1]”为“1”,则sft[*]值递减“1”(以变为“值

‑

1”)。

[0295]

并且,在将800mhz的时钟(clkup_p/clkup_n)移位两个周期的情况下,加法器1587c仅将一个周期内的sft[*]值设置为“值+2”或“值

‑

2”。进一步地,在将800mhz的时钟(clkup_p/clkup_n)移位两个周期的情况下,如稍后所描述的,控制时钟(clk1)的时钟周期。在该过程中,移位两个周期与其中“edgec_r[4]”、“edgec_f[4]”、“edgec_r[0]”或“edgec_f[0]”为“1”的情况相对应。如果“edgec_r[4]”或“edgec_f[4]”为“1”,则sft[*]值递增“2”(以变为“值+2”)。如果“edgec_r[0]”或“edgec_f[0]”为“1”,则sft[*]值递减“2”(以变为“值

‑

2”)。

[0296]

时钟控制电路1588生成用于控制时钟生成电路157的分频比的信号(cdiv)。“四分频”通常被设置为时钟(clkup_p)的频率(400mhz)与波特率(100mhz)的分频比。在“四分频”的情况下,cdiv值变为“3”。在中间边缘检测时,在将800mhz的时钟(clkup_p/clkup_n)移位两个周期的情况下,时钟控制电路1588将时钟(clk1)的仅一个周期的cdiv值设置为“值+1”或“值

‑

1”。如果“edgec_r[0]”或“edgec_f[0]”为“1”,则时钟控制电路1588将cdiv值设置为

“

4”。如果“edgec_r[4]”或“edgec_f[4]”为“1”,则时钟控制电路1588将cdiv值设置为“2”。

[0297]

要注意的是,时钟控制电路1588包括两位寄存器ubrs[1:0]。在寄存器ubrs[1:0]中,“四分频”(8个周期)、“五分频”(10个周期)和“六分频”(12个周期)可以被设置为分频比。在“五分频”的情况下,cdiv值通常变为“4”。如果“edgec_r[0]”或“edgec_f[0]”为“1”,则cdiv值通常为“5”。如果“edgec_r[4]”或“edgec_f[4]”为“1”,则cdiv值通常为“3”。在“六分频”的情况下,cdiv值通常变为“5”。如果“edgec_r[0]”或“edgec_f[0]”为“1”,则cdiv值通常变为“6”。如果“edgec_r[4]”或“edgec_f[4]”为“1”,则cdiv值通常变为“4”。

[0298]

时钟生成电路157通过将时钟的频率(clkup_p)除以cdiv值来生成时钟(clk1)。下文对该过程进行具体解释。时钟生成电路157包括计数器1571、用于比较计数器1571的输出与cdiv值的比较器1572、以及用于存储比较结果的触发器1573。计数器1571通过使用递增电路1571b对每个时钟(clkup_p)从“0”到cdiv值的计数器值进行计数。比较器1572比较计数器1571的触发器1571a的输出(计数器值)与cdiv值,并且如果计数器值小于cdiv值,则输出“0”。如果计数器值等于cdiv值,则比较器1572输出“1”。如果作为触发器1573的输出的使能信号(en)为“0”,则计数器1571对计数器值进行计数。如果使能信号(en)为“1”,则计数器1571将计数器值清除为“0”。对于每个“cdiv的值+1”,使能信号(en)变为“1”。如果使能信号(en)为“1”,则时钟门控电路(icg)1574输出时钟(clkup_p)。在该过程中,输出通过基于时钟的脉冲(clkup_p)来将一个脉冲调整为与cdiv值相对应的脉冲数目而得到的值作为时钟(clk1)。通过改变cdiv值,可以改变时钟(clk1)的每个周期的采样数目。

[0299]

计数器1571对从“0”到cdiv值的计数器值进行计数,并且时钟生成电路157可以通过改变cdiv值来改变时钟(clk1)的周期。注意,计数器1571可以对从除了“0”以外的设置值到cdiv值的计数器值进行计数,以改变时钟(clk1)的周期。

[0300]

参考图18至图24对根据第三工作示例的解码器的操作进行解释。图18至图24中的每个图示出了根据第三工作示例的解码器的操作的时序图。

[0301]

首先,对图18至图24的符号进行解释。术语“edgebit”指示“edgec_r”或“edgec_f”中的哪个位为“1”。即,如果“edgec_r[0]”或“edgec_f[0]”包含“1”,则“edgebit”变为

“‑

2”。如果“edgec_r[1]”或“edgec_f[1]”包含“1”,则“edgebit”变为

“‑

1”。如果“edgec_r[2]”或“edgec_f[2]”包含“1”,则“edgebit”变为“0”。如果“edgec_r[3]”或“edgec_f[3]”包含“1”,则“edgebit”变为“+1”。如果“edgec_r[4]”或“edgec_f[4]”包含“1”,则“edgebit”变为“+2”。如果“无源”值为“1”,则“edgebit”变为“0”。

[0302]

术语“data2_pre”指示已经在图15中所示的数据检测电路1586中设置了“dadta_0”、“data_1”、“无源”或“cdr_error”中的哪个。“data_0”的情况下的值为“0”,而“dadta_1”的情况下的值为“1”。术语“data2”指示最终数据值。并且,每个图的垂直实线指示曼彻斯特编码信号(mc_si)的位边界,并且该图的垂直虚线指示曼彻斯特编码信号(mc_si)的位中点。

[0303]

垂直箭头指示作为从“sin[*]”到“data_1”的加载时序时钟(clk1)的上升边缘。要注意的是,时钟(clk1)的波形被图示为具有接近50%的占空比。然而,在图17中所示的时钟生成电路157中生成的时钟(clk1)的波形中,上升边缘位于图中的位置,使得时钟具有时钟(clkup_p)的脉冲宽度,并且下降边缘的位置与图中的位置不同。

[0304]

图18示出了在时钟(clkup_n)的“h”时段包含开始位的中间边缘的情况下具有噪

声但抖动在位周期的1/8之内的波形(稳态)。

[0305]

在周期t2中采样时,检测到曼彻斯特编码信号(mc_si)的第一边缘,并且生成以下数据。在该过程中,最右边是位[0]。“data1”是具有18位长度的数据,并且fltr是具有16位长度的数据。“edge_f”、“edge_r”、“edges_f”和“edges_r”中的每个都是具有15位长度的数据。

[0306]

data1=11_11111111_11111000

[0307]

fltr=11111111_11111100

[0308]

edge_f=

‑

0000000_00000010

[0309]

edge_r=

‑

0000000_00000000

[0310]

edges_f=

‑

0000000_00000010

[0311]

edges_r=

‑

0000000_00000000

[0312]

第一采样时,触发器1587a通过到触发器1587a的未图示的清除端子的输入信号清除为“0”。因此,由于sft值为“0”,所以建立“edge_f=edges_f”。此时,检测到边缘的位是“edges_f[1]”,因此,“edgebit”变为“2”,即,“edge_f”的检测位。因此,在触发器1587a中,“2”被设置为初始sft值。下一周期t3的sft值变为“2”。周期t2的“data2_pre”与周期t1的“无源”之后的边缘检测相对应,因此变为“无源”。

[0313]

在周期t3之后的周期中,移位电路1581和移位电路1582通过将“edge_f”和“edge_r”分别移位sft值来生成“edges_f”和”edges_r”。如果sft值为正,则移位电路1581和移位电路1582将它们向右移位(移位到低阶位侧);并且如果sft值为负,则将它们向左移位(移位到高阶位侧)。移位量生成电路1587通过将先前周期的“edgebit”值与先前周期的sft值相加来生成下一周期的sft值。在该过程中,中间边缘检测范围(edgec_r[4:0]和edgec_f[4:0])分别与edges_r[9:5]和edges_f[9:5]相对应。

[0314]

例如,在周期t3中,生成以下数据。在该数据中,

“×”

指示无意义数据。

[0315]

data1=11_11111000_01111000

[0316]

fltr=11111100_00111100

[0317]

edge_f=

‑

0000010_00000010

[0318]

edge_r=

‑

0000000_00100000

[0319]

edges_f=

‑××

00000_10000000

[0320]

edges_r=

‑××

00000_00001000

[0321]

edgec_f[4:0]=00100

[0322]

edgec_r[4:0]=00000

[0323]

在周期t3中,作为从“edge_f”向右移位两个位的“edges_f[9:5]”的中间位置的“edges_f[7]”为“1”。即,由于edgec_f[2]值为“1”,所以“edgebit”值变为“0”,并且在下一周期t4中不对中间边缘检测范围进行校正。并且,下一周期t4的sft值不会改变并且仍然为“2”。由于在“edges_f”中检测到“1”,因此data_1值变为“1”,data2_pre值变为“1”,并且下一周期t4中的data2值变为“1”。

[0324]

在周期t3之后,sft值与“2”相同,并且周期t4之后的周期以相似方式进行。当抖动在1/8周期内时,作为“edges_r”或“edges_f”的中间位的“edgec_r[2]”或“edgec_f[2]”必须变为“1”。

[0325]

在周期t7的操作中,宽度等于或小于1/8周期的“h”噪声叠加在曼彻斯特编码信号(mc_si)上。并且,在周期t8的操作中,宽度等于或小于1/8周期的“l”噪声叠加在曼彻斯特编码信号(mc_si)上。尽管噪声加载到“data1”中,但是1位的噪声通过噪声滤波器(fltr)清除,然后对此后的数据进行正常处理。

[0326]

在时钟(clkup_p)的“h”时段包含开始位的中间边缘的情况下的波形与图18的波形相同。尽管已经对“sin[*]”的奇数位和偶数位的波形进行切换,但所采样的“data1”中的次序由时钟(clk1)校正,该时钟(clk1)的时序与时钟(clkup_p)的时序相同。在“data1”之后,执行与图18的操作相同的操作。与图18相似,在具有噪声的情况下在周期t7和周期t8中进行的操作还与通过噪声滤波器fltr在没有噪声的情况下进行的操作相同。

[0327]

图19示出了在时钟(clkup_n)的“h”时段包含开始位的中间边缘的情况下抖动超前了位周期的1/8的波形。曼彻斯特编码信号(mc_si)的向左箭头指示边缘超前1/8周期,而其向右箭头指示边缘返回到原始边缘。直到周期t4的操作与图18的操作相同。周期t5首先受到抖动的影响。

[0328]

在周期t5中,生成以下数据。

[0329]

data1=00_00001111_10000111

[0330]

fltr=00000111_11000011

[0331]

edge_f=

‑

0000000_00100000

[0332]

edge_r=

‑

0000100_00000010

[0333]

edges_f=

‑××

00000_00001000

[0334]

edges_r=

‑××

00001_00000000

[0335]

edgec_f[4:0]=00000

[0336]

edgec_r[4:0]=01000

[0337]

在周期t5中,在从“edges_r[9:5]”的中间位置向左移位一个位的“edges_r[8]”处检测到“1”。即,由于“edgec_r[3]”为“1”,因此“edgebit”值变为“+1”,并且下一周期t6的sft值从“2”改变为“3”。由于“edgec_r[3]”为“1”,所以窗口切断电路1583在下一周期t6中屏蔽最高阶位(位[4])。即,中间边缘检测范围(“edgec_r[4:0]”、“edgec_f[4:0]”)的位[3:0]被设置为边缘检测范围。

[0338]

因此,在周期t6中,生成以下数据。在该数据中,“edgec_f”和“edgec_r”的每个中的术语”m”指示所屏蔽的位。

[0339]

data1=11_10000111_11110000

[0340]

fltr=10000011_11111000

[0341]

edge_f=

‑

1000000_00000100

[0342]

edge_r=

‑

0000010_00000000

[0343]

edges_f=

‑×××

1000_00000000

[0344]

edges_r=

‑×××

0000_01000000

[0345]

edgec_f[4:0]=m0000

[0346]

edgec_r[4:0]=m0010

[0347]

在周期t6中,在从“edges_r[9:5]”的中间位置向右移位一个位的“edges_r[6]”处检测到“1”。即,由于“edgec_r[1]”为“1”,所以“edgebit”值变为

“‑

1”,并且下一周期t7的

sft值从“3”返回“2”。由于“edgec_r[1]”为“1”,所以窗口切断电路1583在下一周期t7中屏蔽最低阶位(位[0])。即,中间边缘检测范围(“edgec_r[4:0]”、“edgec_f[4:0]”)的位[4:1]被设置为边缘检测范围。

[0348]

因此,在周期t7中,生成以下数据。

[0349]

data1=11_11110000_00001111

[0350]

fltr=11111000_00000111

[0351]

edge_f=

‑

0000100_00000000

[0352]

edge_r=

‑

0000000_00000100

[0353]

edges_f=

‑××

00001_00000000

[0354]

edges_r=

‑××

00000_00000001

[0355]

edgec_f[4:0]=0100m

[0356]

edgec_r[4:0]=0000m

[0357]

在周期t7中,在从“edges_f[9:5]”的中间位置向左移动一个位的“edges_f[8]”处检测到“1”。即,由于“edgec_f[3]”为“1”,所以“edgebit”值变为“+1”,并且下一周期t8的sft值再次从“2”改变为“3”。

[0358]

因此,在周期t8中,生成以下数据。

[0359]

data1=00_00001111_11111000

[0360]

fltr=00000111_11111100

[0361]

edge_f=

‑

0000000_00000010

[0362]

edge_r=

‑

0000100_00000000

[0363]

edges_f=

‑×××

0000_00000000

[0364]

edges_r=

‑×××

0000_10000000

[0365]

edgec_f[4:0]=m0000

[0366]

edgec_r[4:0]=m0010

[0367]

在周期t8中,以与周期t7相同的相位对中间边缘进行采样。然而,在作为“edges_r[9:5]”的中间位的“edges_r[7]”处检测到“1”。即,由于“edgec_r[2]”为“1”,所以“edgebit”值变为“0”,并且下一周期t9的sft值不变并且为“3”。

[0368]

因此,在周期t9中,生成以下数据。

[0369]

data1=11_01111000_00000111

[0370]

fltr=11111100_00000011

[0371]

edge_f=

‑

0000010_00000000

[0372]

edge_r=

‑

0000000_00000010

[0373]

edges_f=

‑×××

0000_10000000

[0374]

edges_r=

‑×××

0000_00000000

[0375]

edgec_f[4:0]=0010m

[0376]

edgec_r[4:0]=0000m

[0377]

在周期t9中,在从“edges_f[9:5]”的中间位置向右移位一个位的“edges_f[6]”处检测到“1”。即,由于“edgec_f[1]”为“1”,所以“edgebit”值变为

“‑

1”,并且下一周期的sft值再次从“3”返回到“2”。

[0378]

其中时钟(clkup_p)的“h”时段包含开始位的中间边缘的情况下的波形与图19的波形相同。尽管已经切换了“sin[*]”的奇数位和偶数位的波形,但是所采样的“data1”中的次序由时钟(clk1)校正,该时钟(clk1)的时序与时钟(clkup_p)的时序相同。在“data1”之后,执行与图19的操作相同的操作。

[0379]

图20示出了在时钟(clkup_n)的“h”时段包含开始位的中间边缘的情况下抖动延迟了位周期的1/8的波形。曼彻斯特编码信号(mc_si)的向右箭头指示边缘延迟1/8个周期,而其向左箭头指示边缘返回到原始边缘。直到周期t4的操作与图18的操作相同。周期t5首先受到抖动的影响。

[0380]

在周期t5中,生成以下数据。

[0381]

data1=00_00000011_10000111

[0382]

fltr=00000001_11000011

[0383]

edge_f=

‑

0000000_00100000

[0384]

edge_r=

‑

0000001_00000001

[0385]

edges_f=

‑××

00000_00001000

[0386]

edges_r=

‑××

00000_01000000

[0387]

edgec_f[4:0]=00000

[0388]

edgec_r[4:0]=00010

[0389]

在周期t5中,在从“edges_r[9:5]”的中间位置向右移位一个位的“edges_r[6]”处检测到“1”。即,由于“edgec_r[1]”为“1”,所以“edgebit”值变为

“‑

1”,并且下一周期t6的sft值从“2”改变为“1”。

[0390]

因此,在周期t6中,生成以下数据。

[0391]

data1=11_10000111_11111100

[0392]

fltr=10000011_11111110

[0393]

edge_f=

‑

1000000_00000001

[0394]

edge_r=

‑

0000010_00000000

[0395]

edges_f=

‑×××

1000_00000000

[0396]

edges_r=

‑×××

0001_00000000

[0397]

edgec_f[4:0]=0000m

[0398]

edgec_r[4:0]=1000m

[0399]

在周期t6中,在从“edges_r[9:5]”的中间位置向左移位一个位的“dges_r[8]”处检测到“1”。即,由于“edgec_r[3]”为“1”,所以“edgebit”值变为“+1”,并且下一周期t7的sft值从“1”返回到“2”。

[0400]

因此,在周期t7中,生成以下数据。

[0401]

data1=11_11111100_00000011

[0402]

fltr=11111110_00000001

[0403]

edge_f=

‑

1000001_00000000

[0404]

edge_r=

‑

0000000_00000001

[0405]

edges_f=

‑×××

0000_01000000

[0406]

edges_r=

‑×××

0000_00000000

[0407]

edgec_f[4:0]=m0001

[0408]

edgec_r[4:0]=m0000

[0409]

在周期t7中,在从“edges_f[9:5]”的中间位置向右移位一个位的“edges_f[6]”处检测到“1”。即,由于“edgec_f[1]”为“1”,所以“edgebit”值变为

“‑

1”,并且下一周期t8的sft值再次从“2”改变为“1”。

[0410]

因此,在周期t8中,生成以下数据。

[0411]

data1=00_00000011_11111000

[0412]

fltr=00000001_11111100

[0413]

edge_f=

‑

0000000_00000010

[0414]

edge_r=

‑

0000001_00000000

[0415]

edges_f=

‑×

000000_00000000

[0416]

edges_r=

‑×

000000_10000000

[0417]

edgec_f[4:0]=0000m

[0418]

edgec_r[4:0]=0010m

[0419]

在周期t8中,以与周期t7的相位相同的相位对中间边缘进行采样。然而,在作为“edges_r[9:5]”的中间位的“edges_r[7]”处检测到“1”。即,由于“edgec_r[2]”为“1”,所以“edgebit”值变为“0”,并且下一周期t9的sft值不变,并且仍为“1”。

[0420]

因此,在周期t9中,生成以下数据。

[0421]

data1=11_01111000_00000111

[0422]

fltr=11111100_00000011

[0423]

edge_f=

‑

0000010_00000000

[0424]

edge_r=

‑

0000000_00000010

[0425]

edges_f=

‑×

000001_00000000

[0426]

edges_r=

‑×

000000_00000000

[0427]

edgec_f[4:0]=1000m

[0428]

edgec_r[4:0]=0000m

[0429]

在周期t9中,在从“edges_f[9:5]”的中间位置向左移位一个位的“edges_f[8]”处检测到“1”。即,由于“edgec_f[3]”为“1”,所以“edgebit”值变为“+1”,并且下一周期的sft值再次从“1”返回到“2”。

[0430]

在时钟(clkup_p)的“h”时段包含开始位的中间边缘的情况下的波形与图20的波形相同。尽管已经切换了“sin[*]”的奇数位和偶数位的波形,但是所采样的“data1”中的次序由时钟(clk1)校正,该时钟(clk1)的时序与时钟(clkup_p)的时序相同。在“data1”之后,执行与图20的操作相同的操作。

[0431]

图21示出了在时钟(clkup_n)的“h”时段包含开始位的中间边缘的情况下抖动超前了位周期的1/4的波形。曼彻斯特编码信号(mc_si)的向左箭头指示边缘超前1/4,而其向右箭头指示边缘返回原始边缘。直到周期t4的操作与图18的操作相同。周期t5首先受到抖动的影响。

[0432]

在周期t5中,生成以下数据。

[0433]

data1=00_00011111_10000111

[0434]

fltr=00001111_11000011

[0435]

edge_f=

‑

0000000_00100000

[0436]

edge_r=

‑

0001000_00000010

[0437]

edges_f=

‑××

00000_00001000

[0438]

edges_r=

‑××

00010_00000000

[0439]

edgec_f[4:0]=00000

[0440]

edgec_r[4:0]=10000

[0441]

在周期t5中,在从“edges_r[9:5]”的中间位置向左移位两个位的“edges_r[9]”处检测到“1”。即,由于“edgec_r[4]”为“1”,所以“edgebit”值变为“+2”,并且下一周期t6的sft值暂时从“2”改变为“4”。并且,通过将

“‑

1”与“3”相加,cdiv值暂时变为“2”,并且下一周期t6的范围减小到时钟(clkup_p)的三个周期。

[0442]

因此,在周期t6中,生成以下数据。

[0443]

data1=11_10000111_11100000

[0444]

fltr=10000011_11110000

[0445]

edge_f=

‑

1000000_00001000

[0446]

edge_r=

‑

0000010_00000000

[0447]

edges_f=

‑××××

100_00000000

[0448]

edges_r=

‑××××

000_00100000

[0449]

edgec_f[4:0]=m0000

[0450]

edgec_r[4:0]=m0001

[0451]

在周期t6中,在从“edges_r[9:5]”的中间位置向右移位两个位的“edges_r[5]”处检测到“1”。即,由于“edgec_r[0]”为“1”,所以“edgebit”值变为

“‑

2”,并且下一周期t7的sft值暂时从作为原始值的“2”改变为“0”。并且,通过将“+1”与“3”相加,cdiv值暂时变为“4”,并且下一周期t7的范围增加到时钟(clkup_p)的五个周期。

[0452]

因此,在周期t7中,生成以下数据。

[0453]

data1=11_11111000_00000111

[0454]

fltr=11111100_00000011

[0455]

edge_f=

‑

0000010_00000000

[0456]

edge_r=

‑

0000010_00000010

[0457]

edges_f=

‑

0000010_00000000

[0458]

edges_r=

‑

0000000_00000000

[0459]

edgec_f[4:0]=1000m

[0460]

edgec_r[4:0]=0000m

[0461]

在周期t7中,在从“edges_f[9:5]”的中间位置向左移位两个位的“edges_f[9]”处检测到“1”。即,由于“edgec_f[4]”为“1”,所以“edgebit”值变为“+2”,并且下一周期t8的sft值暂时从“2”改变为“4”。并且,通过将

“‑

1”与“3”相加,cdiv值暂时变为“2”,并且下一周期t8的范围减小到时钟(clkup_p)的三个周期。

[0462]

因此,在周期t8中,生成以下数据。

[0463]

data1=00_00011111_11111000

[0464]

fltr=00001111_11111100

[0465]

edge_f=

‑

0000000_00100010

[0466]

edge_r=

‑

0001000_00000000

[0467]

edges_f=

‑××××

000_00000000

[0468]

edges_r=

‑××××

000_10000000

[0469]

edgec_f[4:0]=m0000

[0470]

edgec_r[4:0]=m0100

[0471]

在周期t8中,以与周期t7的相位相同的相位对中间边缘进行采样。在作为“edges_r[9:5]”的中间位的“edges_r[7]”处检测到“1”。即,由于“edgec_r[2]”为“1”,所以“edgebit”值变为“0”,并且下一周期t9的sft值返回到作为原始值的“2”。并且,cdiv值变为“3”,并且下一周期t9的范围返回到时钟(clkup_p)的四个周期。

[0472]

因此,在周期t9中,生成以下数据。

[0473]

data1=11_11111110_00011110

[0474]

fltr=11111111_00001111

[0475]

edge_f=

‑

0000000_10000000

[0476]

edge_r=

‑

0000000_00001000

[0477]

edges_f=

‑××

00000_00100000

[0478]

edges_r=

‑××

00000_00000010

[0479]

edgec_f[4:0]=m0001

[0480]

edgec_r[4:0]=m0000

[0481]

在周期t9中,在从“edges_f[9:5]”的中间位置向右移位两个位的“edges_f[5]”处检测到“1”。即,由于“edgec_f[0]”为“1”,所以“edgebit”值变为

“‑

2”,并且下一周期t10中的sft值暂时从作为原始值的“2”改变为“0”。并且,通过将“+1”与“3”相加,cdiv值暂时变为“4”,并且下一周期t10的范围增加到时钟(clkup_p)的五个周期。

[0482]

因此,在周期t10中,生成以下数据。

[0483]

data1=10_00011110_00000001

[0484]

fltr=10001111_00000000

[0485]

edge_f=

‑

1000000_10000000

[0486]

edge_r=

‑

0001000_00000000

[0487]

edges_f=

‑

0000000_10000000

[0488]

edges_r=

‑

0001000_00000000

[0489]

edgec_f[4:0]=0010m

[0490]

edgec_r[4:0]=0000m

[0491]

在周期t10中,在作为“edges_f[9:5]”的中间位的“edges_f[7]”处检测到“1”。即,由于“edgec_f[2]”为“1”,所以“edgebit”值变为“0”,并且下一周期t11的sft值返回到作为原始值的“2”。并且,cdiv值变为“3”,并且下一周期t11的范围返回到时钟(clkup_p)的四个周期。

[0492]

其中时钟(clkup_p)的“h”时段包含开始位的中间边缘的情况下的波形与图21的波形相同。尽管已经切换了“sin[*]”的奇数位和偶数位的波形,但是所采样的“data1”中的

次序由时钟(clk1)校正,该时钟(clk1)的时序与时钟(clkup_p)的时序相同。在“data1”之后,执行与图21的操作相同的操作。

[0493]

图22示出了在时钟(clkup_n)的“h”时段包含开始位的中间边缘的情况下抖动延迟了位周期的1/4的波形。曼彻斯特编码信号(mc_si)的向右箭头指示边缘延迟1/4个周期,而其向左箭头指示边缘返回到原始边缘。直到周期t4的操作与图18的操作相同。周期t5首先受到抖动的影响。

[0494]

在周期t5中,生成以下数据。

[0495]

data1=00_00000001_10000111

[0496]

fltr=00000000_11000011

[0497]

edge_f=

‑

0000000_00100000

[0498]

edge_r=

‑

0001000_10000000

[0499]

edges_f=

‑××

00000_00001000

[0500]

edges_r=

‑××

00000_00100000

[0501]

edgec_f[4:0]=00000

[0502]

edgec_r[4:0]=00001

[0503]

在周期t5中,在从“edges_r[9:5]”的中间位置向右移位两个位的“edges_r[5]”处检测到“1”。即,由于“edgec_r[0]”为“1”,所以“edgebit”值变为

“‑

2”,并且下一周期t6的sft值暂时从“2”改变为“0”。并且,通过将“+1”与“3”相加,cdiv值暂时变为“4”,并且下一周期t6的范围增加到时钟(clkup_p)的五个周期。

[0504]

因此,在周期t6中,生成以下数据。

[0505]

data1=11_10000111_11111110

[0506]

fltr=10000011_11111111

[0507]

edge_f=

‑

1000000_00000000

[0508]

edge_r=

‑

0000010_00000000

[0509]

edges_f=

‑

1000000_00000000

[0510]

edges_r=

‑

0000010_00000000

[0511]

edgec_f[4:0]=0000m

[0512]

edgec_r[4:0]=1000m

[0513]

在周期t6中,在从“edges_r[9:5]”的中间位置向右移位两个位的“edges_r[9]”处检测到“1”。即,由于“edgec_r[4]”为“1”,所以“edgebit”值变为“+2”,并且下一周期t7的sft值暂时从“2”改变为“4”。并且,通过将

“‑

1”与“3”相加,cdiv值暂时变为“2”,并且下一周期t7的范围减小到时钟(clkup_p)的三个周期。

[0514]

因此,在周期t7中,生成以下数据。

[0515]

data1=11_11111000_00000111

[0516]

fltr=11111100_00000011

[0517]

edge_f=

‑

0000010_00000000

[0518]

edge_r=

‑

0000000_00000010

[0519]

edges_f=

‑××××

000_00100000

[0520]

edges_r=

‑××××

000_00000000

[0521]

edgec_f[4:0]=m0001

[0522]

edgec_r[4:0]=m0000

[0523]

在周期t7中,在从“edges_f[9:5]”的中间位置向右移位两个位的“edges_f[5]”处检测到“1”。即,由于“edgec_f[0]”为“1”,所以“edgebit”值变为

“‑

2”,并且下一周期t8的sft值暂时从作为原始值的“2”改变为“0”。并且,通过将“+1”与“3”相加,cdiv值暂时变为“4”,并且下一周期t8的范围增加到时钟(clkup_p)的五个周期。

[0524]

因此,在周期t8中,生成以下数据。

[0525]

data1=10_00000001_11111000

[0526]

fltr=00000000_11111100

[0527]

edge_f=

‑

0000000_00000010

[0528]

edge_r=

‑

0000000_10000000

[0529]

edges_f=

‑

0000000_00000010

[0530]

edges_r=

‑

0000000_10000000

[0531]

edgec_f[4:0]=0000m

[0532]

edgec_r[4:0]=0010m

[0533]

在周期t8中,以与周期t7的相位相同的相位对中间边缘进行采样。在作为“edges_r[9:5]”的中间位的“edges_r[7]”处检测到“1”。即,由于“edgec_r[2]”为“1”,所以“edgebit”值变为“0”,并且下一周期t9的sft值返回作为原始值的“2”。并且,cdiv值变为“3”,并且下一周期t9的范围返回到时钟(clkup_p)的四个周期。

[0534]

因此,在周期t9中,生成以下数据。

[0535]

data1=11_11100001_11100000

[0536]

fltr=11110000_11110000

[0537]

edge_f=

‑

0001000_00000000

[0538]

edge_r=

‑

0000000_10000000

[0539]

edges_f=

‑××

00010_00000000

[0540]

edges_r=

‑××

00000_00100000

[0541]

edgec_f[4:0]=10000

[0542]

edgec_r[4:0]=00001

[0543]

在周期t9中,在从“edges_f[9:5]”的中间位置向左移位两个位的“edges_f[9]”处检测到“1”。即,由于“edgec_f[4]”为“1”,所以“edgebit”值变为“+2”,并且下一周期t10的sft值暂时从“2”改变为“4”。并且,通过将

“‑

1”与“3”相加,cdiv值暂时变为“2”,并且下一周期t10的范围减小到时钟(clkup_p)的三个周期。

[0544]

因此,在周期t10中,生成以下数据。

[0545]

data1=11_11100000_00011110

[0546]

fltr=11110000_00001111

[0547]

edge_f=

‑

0001000_00000000

[0548]

edge_r=

‑

0000000_00001000

[0549]

edges_f=

‑××××

000_10000000

[0550]

edges_r=

‑××××

000_00000000

[0551]

edgec_f[4:0]=m0100

[0552]

edgec_r[4:0]=m0000

[0553]

在周期t10中,在作为“edges_f[9:5]”的中间位的“edges_f[7]”处检测到“1”。即,由于“edgec_f[2]”为“1”,所以“edgebit”值变为“0”,并且下一周期t11的sft值返回到作为原始值的“2”。并且,cdiv值变为“4”,并且下一周期t11的范围返回到时钟(clkup_p)的四个周期。

[0554]

其中时钟(clkup_p)的“h”时段包含开始位的中间边缘的情况下的波形与图22的波形相同。尽管已经切换了“sin[*]”的奇数位和偶数位的波形,但是所采样的“data1”中的次序由时钟(clk1)校正,该时钟(clk1)的时序与时钟(clkup_p)的时序相同。在“data1”之后,执行与图22的操作相同的操作。

[0555]

图23示出了在时钟(clkup_n)的“h”时段包含开始位的中间边缘的情况下抖动超前了位周期的1/4但在两个周期期间改变了1/8的波形。曼彻斯特编码信号(mc_si)的向左箭头指示边缘由于抖动而超前了1/8或1/4,而其向右箭头指示边缘返回到原始边缘1/8或1/4。直到周期t4的操作与图18的操作相同。周期t5首先受到抖动的影响。

[0556]

在周期t5中,生成以下数据。

[0557]

data1=00_00001111_10011111

[0558]

fltr=00000111_11001111

[0559]

edge_f=

‑

0000000_00100000

[0560]

edge_r=

‑

0000100_00001000

[0561]

edges_f=

‑××

00000_00001000

[0562]

edges_r=

‑××

00001_00000010

[0563]

edgec_f[4:0]=00000

[0564]

edgec_r[4:0]=01000

[0565]

在周期t5中,在从“edges_r[9:5]”的中间位置向左移位一个位的“edges_r[8]”处检测到“1”。即,由于“edgec_r[3]”为“1”,所以“edgebit”值变为“+1”,并且下一周期t6的sft值从“2”改变为“3”。

[0566]

因此,在周期t6中,生成以下数据。

[0567]

data1=11_10011111_11111000

[0568]

fltr=11001111_11111100

[0569]

edge_f=

‑

0100000_00000010

[0570]

edge_r=

‑

0001000_00000000

[0571]

edges_f=

‑×××

0100_00000000

[0572]

edges_r=

‑×××

0001_00000000

[0573]

edgec_f[4:0]=m0000

[0574]

edgec_r[4:0]=m1000

[0575]

在周期t6中,以第二次超前1/4周期的抖动进行确定。在从“edges_r[9:5]”的中间位置向左移位一个位的“edges_r[8]”处检测到“1”。即,由于“edgec_r[3]”为“1”,所以“edgebit”值变为“+1”,并且下一周期t7的sft值从“3”改变为“4”。

[0576]

因此,在周期t7中,生成以下数据。

[0577]

data1=11_11111000_00011111

[0578]

fltr=11111100_00001111

[0579]

edge_f=

‑

0000010_00000000

[0580]

edge_r=

‑

0000000_00001000

[0581]

edges_f=

‑××××

000_00100000

[0582]

edges_r=

‑××××

000_00000000

[0583]

edgec_f[4:0]=m0001

[0584]

edgec_r[4:0]=m0000

[0585]

在周期t7中,在一次返回第一1/8周期的情况下进行确定。从“edges_f[9:5]”的中间位置向右移位两个位的“edges_f[5]”处检测到“1”。即,由于“edgec_f[0]”为“1”,所以“edgebit”值变为

“‑

2”,并且下一周期t8的sft值暂时从“4”改变为“2”。并且,通过将“+1”与“3”相加,cdiv值暂时变为“4”,并且下一周期t8的范围增加到时钟(clkup_p)的五个周期。

[0586]

因此,在周期t8中,生成以下数据。

[0587]

data1=00_00001111_11110000

[0588]

fltr=00000111_11111000

[0589]

edge_f=

‑

0000000_00000100

[0590]

edge_r=

‑

0000100_00000000

[0591]

edges_f=

‑××

00000_00000001

[0592]

edges_r=

‑××

00001_00000000

[0593]

edgec_f[4:0]=0000m

[0594]

edgec_r[4:0]=0100m

[0595]

在周期t8中,在返回第二1/8周期的情况下进行确定。从“edges_r[9:5]”的中间位置向左移位一个位的“edges_r[8]”处检测到“1”。即,由于“edgec_r[3]”为“1”,所以“edgebit”值变为“+1”,并且下一周期t9的sft值从作为原始值的“4”改变为“5”。并且,cdiv值变为“3”,并且下一周期t9的范围返回到时钟(clkup_p)的四个周期。

[0596]

因此,在周期t9中,生成以下数据。

[0597]

data1=11_11000001_11100000

[0598]

fltr=11100000_11110000

[0599]

edge_f=

‑

0010000_00001000

[0600]

edge_r=

‑

0000000_10000000

[0601]

edges_f=

‑×××××

00_10000000

[0602]

edges_r=

‑×××××

00_00000100

[0603]

edgec_f[4:0]=m0100

[0604]

edgec_r[4:0]=m0000

[0605]

在周期t9中,在作为“edges_f[9:5]”的中间位置的“edges_f[7]”处检测到“1”。即,由于“edgec_f[2]”为“1”,所以“edgebit”值变为”0”,并且下一周期t10的sft值不变并且仍为“5”。cdiv值不变并且仍为“3”,周期t10不变,并且仍与时钟(clkup_p)的四个周期相对应。

[0606]

因此,在周期t10中,生成以下数据。

[0607]

data1=11_11100000_00011110

[0608]

fltr=11110000_00001111

[0609]

edge_f=

‑

0001000_00000000

[0610]

edge_r=

‑

0000000_00001000

[0611]

edges_f=

‑×××××

00_01000000

[0612]

edges_r=

‑×××××

00_00000000

[0613]

edgec_f[4:0]=m0010

[0614]

edgec_r[4:0]=m0000

[0615]

在周期t10中,在从“edges_f[9:5]”的中间位置向右移位一个位的“edges_f[6]”处检测到“1”。即,由于“edgec_f[1]”为“1”,所以“edgebit”值变为

“‑

1”,并且下一周期t11的sft值从“5”改变为“4”。

[0616]

其中时钟(clkup_p)的“h”时段包含开始位的中间边缘的情况下的波形与图23的波形相同。尽管已经切换了“sin[*]”的奇数位和偶数位的波形,但是所采样的“data1”中的次序由时钟(clk1)校正,该时钟(clk1)的时序与时钟(clkup_p)的时序相同。在“data1”之后,执行与图23的操作相同的操作。

[0617]

图24示出了在时钟(clkup_n)的“h”时段包含开始位的中间边缘的情况下抖动延迟了位周期的1/4但在两个周期期间改变了1/8周期的波形。曼彻斯特编码信号(mc_si)的向右箭头指示由于抖动而使边缘延迟1/8或1/4,而其向左箭头指示因边缘返回1/8或1/4。直到周期t4的操作与图18相同。周期t5首先受到抖动的影响。

[0618]

在周期t5中,生成以下数据。

[0619]

data1=00_00000011_10000001

[0620]

fltr=00000001_11000000

[0621]

edge_f=

‑

0000000_00100000

[0622]

edge_r=

‑

0000001_00000000

[0623]

edges_f=

‑××

00000_00001000

[0624]

edges_r=

‑××

00000_01000000

[0625]

edgec_f[4:0]=00000

[0626]

edgec_r[4:0]=00010

[0627]

在周期t5中,在一次返回第一1/4周期的情况下进行确定。在从“edges_r[9:5]”的中间位置向右移位一个位的“edges_r[6]”处检测到“1”。即,由于“edgec_r[1]”为“1”,所以“edgebit”值变为

“‑

1”,并且下一周期t6的sft值从“2”改变为“1”。

[0628]

因此,在周期t6中,生成以下数据。

[0629]

data1=11_10000001_11111000

[0630]

fltr=11000000_11111100

[0631]

edge_f=

‑

0100000_00000010

[0632]

edge_r=

‑

0000000_10000000

[0633]

edges_f=

‑×

010000_00000001

[0634]

edges_r=

‑×

000000_01000000

[0635]

edgec_f[4:0]=0000m

[0636]

edgec_r[4:0]=0001m

[0637]

在周期t6中,以延迟第二1/4周期的边缘来进行确定。在从“edges_r[9:5]”的中间位置向右移位一个位的“edges_r[6]”处检测到“1”。即,由于“edgec_f[1]”为“1”,所以“edgebit”值变为

“‑

1”,并且下一周期t7的sft值从“1”改变为“0”。

[0638]

因此,在周期t7中,生成以下数据。

[0639]

data1=11_11111000_00000001

[0640]

fltr=11111100_00000000

[0641]

edge_f=

‑

0000010_00000000

[0642]

edge_r=

‑

0000000_00000000

[0643]

edges_f=

‑

0000010_00000000

[0644]

edges_r=

‑

0000000_00000000

[0645]

edgec_f[4:0]=1000m

[0646]

edgec_r[4:0]=0000m

[0647]

在周期t7中,在返回1/8周期的情况下进行确定。在从“edges_f[9:5]”的中间位置向左移位两个位的“edges_f[9]”处检测到“1”。即,由于“edgec_f[4]”为“1”,所以“edgebit”值变为“+2”,并且下一周期t8的sft值暂时从“0”改变为“2”。并且,通过将

“‑

1”与“3”相加,cdiv值暂时变为“2”,并且下一周期t10的范围减小到时钟(clkup_p)的三个周期。

[0648]

因此,在周期t8中,生成以下数据。

[0649]

data1=00_00000001_11111100

[0650]

fltr=00000000_11111110

[0651]

edge_f=

‑

0000000_00000001

[0652]

edge_r=

‑

0000000_10000000

[0653]

edges_f=

‑××

00000_00000000

[0654]

edges_r=

‑××

00000_00100000

[0655]

edgec_f[4:0]=m0000

[0656]

edgec_r[4:0]=m0001

[0657]

在周期t8中,在返回下一1/4周期的情况下进行确定。在从“edges_r[9:5]”的中间位置向右移位两个位的“edges_r[5]”处检测到“1”。即,由于“edgec_r[0]”为“1”,所以“edgebit”值变为

“‑

2”,并且下一周期t9的sft值暂时从作为原始值的“0”改变为

“‑

2”。并且,通过将“+1”与“3”相加,cdiv值暂时变为“4”,并且下一周期t9的范围增加到时钟(clkup_p)的五个周期。

[0658]

因此,在周期t9中,生成以下数据。

[0659]

data1=00_01111111_00011110

[0660]

fltr=00111111_10001111

[0661]

edge_f=

‑

0000000_01000000

[0662]

edge_r=

‑

0100000_00001000

[0663]

edges_f=

‑

0000001_00000000

[0664]

edges_r=

‑

0000000_00100010

[0665]

edgec_f[4:0]=0100m

[0666]

edgec_r[4:0]=0000m

[0667]

在周期t9中,在从“edges_f[9:5]”的中间位置向左移位一个位的“edges_f[8]”处检测到“1”。即,由于“edgec_f[3]”为“1”,所以“edgebit”值变为“+1”,并且下一周期t10的sft值从作为原始值的“0”改变为“1”。并且,cdiv值变为“3”,并且下一周期t10的范围返回到时钟(clkup_p)的四个周期。

[0668]

因此,在周期t10中,生成以下数据。

[0669]

data1=00_01111000_00000111

[0670]

fltr=00111100_00000011

[0671]

edge_f=

‑

0000010_00000000

[0672]

edge_r=

‑

0000000_00000010

[0673]

edges_f=

‑×

000001_00000000

[0674]

edges_r=

‑×

000000_00000001

[0675]

edgec_f[4:0]=m1000

[0676]

edgec_r[4:0]=m0000

[0677]

在周期t10中,在从“edges_f[9:5]”的中间位置向左移位一个位的“edges_f[8]”处检测到“1”。即,由于“edgec_f[3]”为“1”,所以“edgebit”值变为“+1”,并且下一周期t11的sft值从“1”改变为“2”。

[0678]

其中时钟(clkup_p)的“h”时段包含开始位的中间边缘的情况下的波形与图24的波形相同。尽管已经切换了“sin[*]”的奇数位和偶数位的波形,但是所采样的“data1”中的次序由时钟(clk1)校正,该时钟(clk1)的时序与时钟(clkup_p)的时序相同。在“data1”之后,执行与图24的操作相同的操作。

[0679]

与第一工作示例和第二工作示例相比较,第三工作示例仅包括移位触发器151a作为在高速采样时钟下操作的电路,并且不包括在高速采样时钟下操作的用于加法、移位、比较等的计算器。因此,实现了频率和波特率都高于第一工作示例和第二工作示例的频率和波特率的操作。换言之,在相同的频率和波特率的情况下,可以通过无需微制造的廉价的制造技术以较低的功率实现操作。

[0680]

(第四工作示例)

[0681]

图25是示出了根据第四工作示例的边缘识别电路的配置的一部分的框图。图26是示出了根据第四工作示例的边缘识别电路的配置的一部分的框图。图27是图26中所示的校正电路的真值表。

[0682]

除了边缘识别电路158之外,根据第四工作示例的解码器150的配置与第三工作示例的配置相同。因此,省略了对同步电路(sync)151、噪声滤波器(fltr)152、边缘检测电路(edc)153和时钟生成电路(cg)157的解释。

[0683]

根据第四工作示例的边缘识别电路158包括移位电路(shftr)1581和移位电路1582以及窗口切断电路(wndw)1583和窗口切断电路1584。移位电路1581和移位电路1582在配置上与第三工作示例的移位电路1581和移位电路1582相同并且执行与第三工作示例的移位电路1581和移位电路1582的配置和操作相同的操作。

[0684]

虽然下文对窗口切断电路1583进行解释,但是窗口切断电路1584的操作与窗口切断电路1583的操作相似。窗口切断电路1583从“edges_r[n:0]”中提取7个位,并且设置

“

edgec_r[7:0]”,即,中间边缘检测范围。根据第四工作示例的中间边缘检测范围比第三工作示例的中间边缘检测范围宽。窗口切断电路1583基于先前周期的中间边缘位置(edgec_r)来校正中间边缘检测范围(edgec_r[6:0])。

[0685]

更具体地,如果先前周期的中间边缘位置(edgec_r)处于中间边缘检测范围(edgec_r[6:0])的高阶位,则窗口切断电路1583屏蔽高阶位(位[5]或位[6])。在该过程中,高阶位是位[4]、位[5]或位[6]。即,中间边缘检测范围(edgec_r[6:0])的位[4:0]被设置为边缘检测范围。如果先前周期的中间边缘位置(edgec_r)处于中间边缘检测范围的低阶位(edgec_r[6:0]),则窗口切断电路1583屏蔽中间边缘检测范围(edgec_r[6:0])的低阶位(位[0]或位[1])。在该过程中,低阶位是位[0]、位[1]或位[2]。即,中间边缘检测范围(edgec_r[6:0])的位[6:2]被设置为边缘检测范围。如果先前周期的中间边缘位置(edgec_r)处于另一位(位[3]),则要屏蔽位不变,换言之,要屏蔽位被设置为与先前周期的屏蔽位相同。

[0686]

如图25所示,边缘识别电路158还包括数据检测电路1586。数据检测电路1586在配置上与根据第三工作示例的数据检测电路1586相同,并且执行与根据第三工作示例的数据检测电路1586的配置和操作相同的操作。

[0687]

如图26所示,边缘识别电路158还包括移位量生成电路1587和时钟控制电路1588。

[0688]

移位量生成电路1587包括帧开始时存储初始移位值(i_sft[*])的触发器1587a以及存储校正移位值(c_sft[*])的触发器1587d。检测到帧中的第一下降边缘时,“edgef_f[4:0]”包含“1”。这被设置为初始值,并且其中“edgef_f[4:0]”中存在“1”的位值输入到触发器1587a。即,i_sft[*]的初始值与帧开始时叠加在曼彻斯特编码信号(mc_si)上的时钟与具有相同频率并帧开始时在解码器150中生成的时钟(clk1)之间的相位差。

[0689]

校正移位值(c_sft[*])是接收帧时的校正值。加法器1587c通过帧开始时将校正移位值(c_sft[*])与初始移位值(i_sft[*])相加来计算指示移位量的sft[*]值。

[0690]

移位量生成电路1587还包括校正电路1587e。校正电路1587e具有先前周期的位移位值(校正移位值)输入到其中的端子“d”以及“edgec_r[6:0]”或“edgec_f[6:0]”输入到其中的端子“in(

‑

3、

‑

2、

‑

1、0、+1、+2、+3)”。“edgec_r[6:0]”或“edgec_f[6:0]”被称为边缘校正输入,并且“1”输入到七个端子in中的任何一个端子。校正电路1587e还具有从中输出下一移位值(校正移位值)的端子“q1”以及从中输出计数器移位值的端子“q2”。校正电路1587e使用输入到端子in和端子d的数据,并且按照图20中所示的真值表从端子q1和端子q2输出数据。

[0691]

即,在由于抖动而使800mhz的时钟(clkup_p/clkup_n)移位一个周期的情况下,如果先前未校正数据(c_sft[*]=0),则

“‑

1”或“+1”被认为输入到端子in,而“0”输入到端子d。此时,从端子q1输出

“‑

1”或“+1”。因此,下一校正移位值(c_sft[*])变为

“‑

1”或“+1”。如果数据已经被校正(c_sft[*]=

‑

1或+1),则

“‑

1”或“+1”被认为输入到端子in,而

“‑

1”或“+1”输入到端子d。此时,“0”从端子q1输出。因此,下一校正移位值(c_sft[*])变为“0”(意味着没有校正)。

[0692]

与根据第三工作示例的时钟控制电路1588类似,时钟控制电路1588生成用于控制时钟生成电路157的分频比的信号(cdivc)。通常设置时钟(clkup_p)的频率(400mhz)与波特率(100mhz)的分频比。即,在“四分频”的情况下,cdiv值变为“3”。然而,时钟控制电路

1588基于从校正电路1587e的端子q1输入的计数器校正值来临时增大/减小该值。

[0693]

在该过程中,如果边缘校正输入的符号和先前校正移位值彼此相同,则这意味着移位一个400mhz的周期,因此时钟(clk1)的范围暂时增大/减小400mhz的时钟(clkup_p)的一个周期。该控制基于输入到时钟控制电路1588的端子“cor”的计数器校正值,并且通过将计数器校正值与由分频比确定的值(“四分频”情况下的“3”)相加来生成cdiv值。

[0694]

在移位800mhz的时钟(clkup_p/clkup_n)的两个周期的情况下,仅对cdiv值进行调整,而不改变c_sft[*]值。在移位800mhz的时钟(clkup_p/clkup_n)的三个周期的情况下,对cdiv值和c_sft[*]值两者进行调整。

[0695]

要注意的是,与第三工作示例相似,时钟控制电路1588包括两位寄存器ubrs[1:0]。在寄存器ubrs[1:0]中,“四分频”(8个周期)、“五分频”(10个周期)和“六分频”(12个周期)可以被设置为分频比。在”五分频”的情况下,cdiv值通常变为“4”,并且cdiv值调整为与计数器校正值相加。在“六分频”的情况下,cdiv值通常变为“5”,并且cdiv值调整为与计数器校正值相加。

[0696]

与第三工作示例相似,时钟生成电路157通过将时钟(clkup_p)的频率除以cdiv值来生成时钟(clk1)。

[0697]

参考图28对根据第四工作示例的解码器的操作进行解释。图28是示出了根据第四工作示例的解码器的操作的时序图。图18至图24中的每个图是示出了根据第三工作示例的操作的时序图,并且在第四工作示例中也执行相同的操作。

[0698]

图28示出了在发送频率稍晚于接收频率的情况下的波形。曼彻斯特编码信号(mc_si)的向右箭头指示稍后的发送频率所延迟的波形。

[0699]

在周期t2中的采样时检测到第一边缘,并且以下数据在周期t2中生成。

[0700]

data1=11_11111111_11111000

[0701]

fltr=11111111_11111100

[0702]

edge_f=

‑

0000000_00000010

[0703]

edge_r=

‑

0000000_00000000

[0704]

第一采样时,触发器1587a的值通过到触发器1587a的未图示的清除端子的输入信号清除为“0”,并且i_sft值变为“0”。并且,触发器1587d的值通过到触发器1587d的未图示的清除端子的输入信号清除为“0”,并且c_sft值变为“0”。因此,由于sft值为“0”,所以建立“edge_f=edges_f”。此时检测到边缘的位是“edges_f[1]”,因此,“edge_f”的检测位变为“2”。因此,“2”在触发器1587a处被设置为初始i_sft值。并且,c_sft值不变并且为“0”。因此,下一周期t3的sft值变为“2”。周期t2的“data2_pre”与周期t1的“无源”之后的边缘检测相对应,因此变为“无源”。

[0705]

在周期t3之后的周期中,移位电路1581和移位电路1582通过将“edges_f”和“edges_r”分别移位sft值来生成“edge_f”和“edge_r”。如果sft值为正,则移位电路1581和移位电路1582向右移位它们;并且如果sft值为负,则向左移位它们。移位量生成电路1587通过将先前周期的c_sft值与先前周期的i_sft值相加来生成下一周期的sft值。中间边缘检测范围(edgec_r[6:0]和edgec_f[6:0])与edges_r[10:4]和edges_f[10:4]相对应。

[0706]

例如,在周期t3中,生成以下数据。

[0707]

data1=11_11111000_01111000

[0708]

fltr=11111100_00111100

[0709]

edge_f=

‑

0000010_00000010

[0710]

edge_r=

‑

0000000_00100000

[0711]

edges_f=

‑××

00000_10000000

[0712]

edges_r=

‑××

00000_00001000

[0713]

edgec_f[6:0]=0001000

[0714]

edgec_r[6:0]=0000000

[0715]

在周期t3中,作为“edges_f[10:4]”的中间位置的“edges_f[7]”为“1”。即,由于“edgec_f[3]”为“1”,而先前周期t2的c_sft值为“0”,所以“c_sft=0”基于图27中所示的真值表来建立。由于在“edges_f”中检测到“1”,所以data_1值变为“1”,data2_pre值变为“1”,并且下一周期t4的data2值变为“1”。

[0716]

周期t5首先受到延迟的影响。在周期t5中,生成以下数据。

[0717]

data1=00_00000011_11000111

[0718]

fltr=00000011_11000001

[0719]

edge_f=

‑

0000000_00100000

[0720]

edge_r=

‑

0000001_00000001

[0721]

edges_f=

‑××

00000_00001000

[0722]

edges_r=

‑××

00000_01000000

[0723]

edgec_f[6:0]=0000000

[0724]

edgec_r[6:0]=0000100

[0725]

在周期t5中,从“edges_r[10:4]”的中间位置向右移位一个位的“edges_r[6]”为“1”。即,“edgec_r[2]”为“1”,先前周期t4的c_sft值为“0”,因此,基于图27中所示的真值表,c_sft值变为

“‑

1”。由于i_sft值为“2”,所以下一周期t6的sft值从“2”改变为“1”。由于“edgec_r[3]”为“1”,所以窗口切断电路1583在下一周期t6中屏蔽最低阶位(位[0]和位[1])。即,中间边缘检测范围(“edgec_r[6:0]”、“edgec_f[6:0]”)的位[6:2]被设置为边缘检测范围。

[0726]

因此,在周期t6中,生成以下数据。

[0727]

data1=11_11000101_11111110

[0728]

fltr=11100001_11111111

[0729]

edge_f=

‑

0100000_00000000

[0730]

edge_r=

‑

0000001_00000000

[0731]

edges_f=

‑×

010000_00000000

[0732]

edges_r=

‑×

000000_10000000

[0733]

edgec_f[6:0]=00000mm

[0734]

edgec_r[6:0]=00010mm

[0735]

在周期t6中,作为“edges_r[10:4]”的中间位置的“edges_r[7]”为“1”。即,“edgec_r[3]”为“1”,先前周期t5的c_sft值为

“‑

1”,因此,基于图27中所示的真值表,c_sft值变为

“‑

1”。由于i_sft值为“2”,所以下一周期t7的sft值不变并且为“1”。

[0736]

因此,在周期t7中,生成以下数据。

[0737]

data1=01_11111110_00000001

[0738]

fltr=11111111_00000000

[0739]

edge_f=

‑

0000001_00000000

[0740]

edge_r=

‑

0000000_00000000

[0741]

edges_f=

‑×

010000_10000000

[0742]

edges_r=

‑×

000000_00000000

[0743]

edgec_f[6:0]=00010mm

[0744]

edgec_r[6:0]=00000mm

[0745]

在周期t7中,作为“edges_f[10:4]”的中间位置的“edges_f[7]”为“1”。即,“edgec_f[3]”为“1”,先前周期t6的c_sft值为

“‑

1”,因此,基于图27中所示的真值表,c_sft值变为

“‑

1”。由于i_sft值为“2”,所以下一周期t8的sft值不变并且为“1”。

[0746]

因此,在周期t8中,生成以下数据。

[0747]

data1=10_00000001_11111111

[0748]

fltr=00000000_11111111

[0749]

edge_f=

‑

0000000_00000000

[0750]

edge_r=

‑

0000000_10000000

[0751]

edges_f=

‑×

010000_00000000

[0752]

edges_r=

‑×

000000_01000000

[0753]

edgec_f[6:0]=00000mm

[0754]

edgec_r[6:0]=00001mm

[0755]

在周期t8中,从“edges_r[10:4]”的中间位置向右移位一个位的“edges_r[6]”为“1”。即,“edgec_r[2]”为“1”,先前周期t7的c_sft值为

“‑

1”,因此,基于图27中所示的真值表,c_sft值变为“0”。由于i_sft值为“2”,因此下一周期t9的sft值从“1”改变为“2”。进一步地,先前周期t7的c_sft值为

“‑

1”,因此,基于图27中所示的真值表,计数器校正值变为“+1”。即,通过将“+1”与“3”相加,cdiv值变为“4”,周期t8的范围增加到时钟(clkup_p)的五个周期,并且时钟(clk1)的周期暂时被扩展。

[0756]

在第三工作示例中,如果发生波特率公差(即,接收频率与发送频率之间的差),则连续增加/减小sft[*]值,因此,需要用于支持连续的资源。在叠加在曼彻斯特编码信号(mc_si)上的时钟与具有相同频率的并且在解码器中生成的时钟(clk1)之间的频率不完全匹配的情况下,发生波特率公差。在第四工作示例中,移位值的校正值仅为

±

1。因此,即使在接收侧与发送侧之间出现波特率公差,也仅需要依据每个周期的采样数目准备sft[*]值和c_sft[*]值,而与帧长度无关。因此,第四工作示例无需取决于帧长度的资源,因此与第三工作示例相比较,可以通过使用最少资源来支持操作。

[0757]

在上文中,已经基于实施例和工作示例对发明人所做出的本技术的发明进行了具体描述。然而,不用说,本技术的发明不局限于前述实施例和工作示例,并且可以进行各种修改。

[0758]

例如,在一个时隙中从高电位移位到低电位时曼彻斯特编码信号的逻辑值为“1”并且在一个时隙中从低电位移位到高电位时其逻辑值是“0”的情况下,已经对实施例和工作示例进行了解释。然而,实施例和工作示例也可适用于在一个时隙中从高电位移位到低

电位时逻辑值为“0”或在一个时隙中从低电位移位到高电位时逻辑值为“1”的曼彻斯特编码信号。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1