一种量子密钥分发的同步修正系统的制作方法

1.本发明涉及量子信息与量子密钥分发领域,具体涉及一种量子密钥分发的同步修正系统。

背景技术:

2.在量子密钥分发系统中,由于同步信号光和量子信号光的波长不同或者光传输路径的差异,到达bob端(qkd系统接收方)的同步信号光脉冲和量子信号光脉冲之间的可能存在延时,导致bob端接收到的同步信号光和量子信号光的时间可能与alice端(qkd系统发送方)的原始信号存在一定的偏差。为了保证alice和bob之间能够正常分发密钥,必须确保alice端与bob端完全时间同步,因此需要补偿这个偏差。

3.现有技术中,在时间同步修正阶段,alice在同步光后固定的时间t发送一个光子,bob端探测到这个光子后,计算出其落后于同步光的时间t

′

,则t

′

与t的差值δt即为要修正的时间差。

4.现有的同步修正,需要借助于专用的校准设备,操作过程需要人工参与测量。当qkd链路出现故障或升级更换光缆后,要使qkd恢复运行,还需要人工借助专用校准设备重新进行同步修正,整个操作过程复杂,且测量修正的精度不高。

5.因此,需要对现有的技术进行进一步地改进,做到无须借助专业校准设备就可以实现bob端自动同步修正,提高修正精度高,提高灵活性。

技术实现要素:

6.为了解决上述技术问题,提出了一种无须借助专业校准设备就可以实现bob端自动同步修正,精度高,灵活性好的量子密钥分发的同步修正系统。

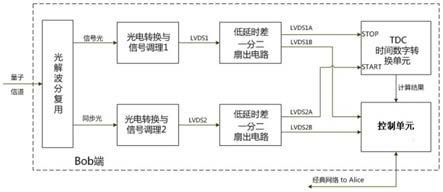

7.为实现上述目的,本发明采取的技术方案如下:一种量子密钥分发的同步修正系统,包括光解波分复用设备、第一光电转换与信号调理电路,第一低延时差一分二扇出电路、时间数字转换单元、控制单元、第二低延时差一分二扇出电路和第二光电转换与信号调理电路,其中:

8.所述光解波分复用设备通过光纤分别与所述第一光电转换与信号调理电路、第二光电转换与信号调理电路连接;

9.所述第一光电转换与信号调理电路、第一低延时差一分二扇出电路和时间数字转换单元通过电信号依次顺序连接;所述第一低延时差一分二扇出电路以及时间数字转换单元的输出端又与所述控制单元连接;

10.所述第二光电转换与信号调理电路、第二低延时差一分二扇出电路和控制单元通过电信号依次顺序连接;

11.所述光解波分复用设备将接收的信号光与同步光分开,其中信号光通过第一光电转化与信号调理电路转换为lvds1信号,lvds1信号通过第一低延时差一分二扇出电路延时处理后分别输入到时间数字转换单元和控制单元;

12.所述同步光通过第二光电转换与信号调理转换为lvds2信号,lvds2信号通过第二低延时差一分二扇出电路延时处理后产生lvds2a信号和lvds2b信号;

13.所述lvds2a信号输入到时间数字转换单元中,通过时间数字转换单元测量lvds2a信号与lvds1a信号的时间差;所述lvds2b信号与lvds1b信号输入到fpga控制单元用于同步光与信号光数据采集。

14.优选地,所述第一光电转化与信号调理电路包括单光子探测器和电平转换电路;

15.优选地,所述单光子探测器用于接收信号光并将接收到的信号光输入到电平转换电路进行光电转化。

16.优选地,所述第二光电转化与信号调理电路包括光电转化管、放大电路和比较电路;

17.优选地,所述光电转化管接收同步光,并将其进行光电转化后依次输入到放大电路和比较电路。

18.优选地,所述控制单元采用fpga控制单元。

19.优选地,所述时间数字转换单元包括tdc芯片和转换芯片,所述fpga控制单元输出复位信号经过转换芯片转换为lvds信号后,复位所述tdc芯片。

20.优选地,所述tdc芯片将所述外部晶振通过片上锁相环倍频到工作时钟。

21.优选地,所述tdc芯片的计算结果,传送给fpga控制单元,fpga控制单元存储接收到的计算结果,用于设置同步修正参数。

22.本发明有益的技术效果:本发明以tdc时间数字转换单元为核心器件,并通过光电转换与信号电路、低延时差一分二扇电路和配合fpga主控制单元配合,实现了整个系统自动同步修正,本系统无须借助外界校准设备,可自动触发,精确度高,灵活性好。

附图说明

23.图1为本发明的整体原理结构框图;

24.图2为本发明中nb6l11系列芯片内部逻辑框图;

25.图3为本发明tdc芯片时间测量原理图;

26.图4为本发明tdc时间数字转换单元电子电路原理图。

具体实施方式

27.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合实施例对本发明进行进一步详细说明,但本发明要求保护的范围并不局限于下述具体实施例。

28.如图1

‑

4所示,一种量子密钥分发的同步修正系统,包括光解波分复用设备、第一光电转换与信号调理电路,第一低延时差一分二扇出电路、时间数字转换单元、控制单元、第二低延时差一分二扇出电路和第二光电转换与信号调理电路,其中,时间数字转换单元采用tdc时间数字转换单元,控制单元采用fpga控制单元:

29.各个部件的连接关系如下:

30.所述光解波分复用设备通过光纤分别与所述第一光电转换与信号调理电路、第二光电转换与信号调理电路连接;

31.所述第一光电转换与信号调理电路、第一低延时差一分二扇出电路和tdc时间数

字转换单元通过电信号依次顺序连接,所述第一低延时差一分二扇出电路以及tdc时间数字转换单元的输出端又与所述fpga控制单元;

32.所述第一光电转换与信号调理电路、第一低延时差一分二扇出电路和fpga控制单元通过电信号依次顺序连接;

33.所述光解波分复用设备将接收的信号光与同步光分开,其中信号光通过第一光电转化与信号调理电路转换为lvds1(low

‑

voltage differential signaling,低电平差分信号1)信号,lvds1信号通过第一低延时差一分二扇出电路处理后产生lvds1a(低电平差分信号a1)信号和lvds2a(低电平差分信号a2)信号,所述lvds1a信号输入到tdc时间数字转换单元中,lvds1b输入到fpga控制单元。

34.lvds1a信号输入到tdc时间数字转换单元后,与lvds2a信号一起作为tdc的输入激励,由tdc时间数字转换单元计算出lvds1a与lvds2a的时间差值。lvds1b输入到fpga控制单元后,与lvds2b一起被fpga控制单元采集。

35.具体地,所述第一光电转化与信号调理电路包括单光子探测器和电平转换电路。

36.所述信号光进入第一光电转化与信号调理电路后,经过单光子探测器输出信号lvpecl1(low voltage positive emitter

‑

couple logic,低压正发射极耦合逻辑1),lvpecl1经过电平转换电路后输出lvds1。单光子探测器负责信号光的探测,将光信号转化为电信号。电平转换电路负责电平转换,将单光子探测器输出的lvpecl1转换为lvds1。

37.所述同步光通过第二光电转换与信号调理转换为lvds2((low

‑

voltage differential signaling,低电平差分信号2)信号,lvds2信号通过第二低延时差一分二电路扇出,处理后产生lvds2a(low

‑

voltage differential signaling低电平差分信号2a)信号和lvds2b(low

‑

voltage differential signaling,低电平差分信号2b)信号,所述lvds2a信号输入到tdc时间数字转换单元中,通过tdc时间数字转换单元测量lvds2a信号与lvds1a的时间差,lvds2a信号连接tdc时间数字转换单元的start信号,lvds1a信号连接tdc时间数字转换单元的stop信号,时间差的计算原理如图3所示,图3中t1等于stop#1与start#1的时间差,t2等于stop#2与start#1的时间差,t3等于stop#3与start#2的时间差。tdc时间数字转换单元自动计算start信号上升沿与stop信号上升沿之间的时间差。所述lvds2b与lvds1b信号输入到fpga控制单元用于同步与信号数据采集。

38.具体地,第二光电转化与信号调理电路包括光电转化管、放大电路和比较电路,比较电路由比较器组成,所述比较器采用差分比较器。

39.所述同步光经过光电转化管后输出模拟信号a2_1,模拟信号a2_1经过放大电路,输出模拟信号a2_2,放大后的模拟信号a2_2经过lvds输出特性的差分比较器,输出lvds2脉冲信号。

40.光电转化管的作用是将光信号转换成电信号,放大电路的作用是将模拟信号放大到后级比较器的输入范围,比较电路的比较器将模拟信号转换成矩形波,输出脉冲信号。

41.具体地,第一低延时差一分二扇出电路和第二低延时差一分二扇出电路均包括一分二扇出芯片,所述一分二扇出芯片采用nb6l系列的芯片,nb6l系列芯片包括引脚vtd、lvds1a、lvds1b和lvds1,其中引脚与vtd连接,由于与vtd连接,芯片内r1与r2串联得到100欧姆电阻,lvds1输入信号使用此片内100欧姆电阻阻抗匹配。输出引脚lvds1a

和lvds1b是输入引脚lvds1的复制,通过复制,将输入信号lvds1一分二输出lvds1a和lvds1b,另外nb6l系列芯片内部特性保障lvds1a和lvds1b两个信号之间的片内延时差可以忽略不计。这里低延时差特性很重要,可以认为lvds1a与lvds1b信号特性完全相同。该电路保障去tdc测量的信号lvds1a与去fpga数据采集的lvds1b信号完全一样。这样tdc计算的lvds1a与lvds2a的延时差,与实际中fpga用于数据采集的lvds1b与lvds2b的延时差完全一样,这样就可以利用tdc时间数字转换单元计算结果去调整fpga控制单元数据采集的延时参数,达到正确采集lvds1b和lvds2b的目的。

42.所述tdc时间数字转换单元包括tdc芯片和转换芯片,所述fpga控制单元输出复位信号经过转换芯片转换为lvds信号后,再复位所述tdc芯片。

43.tdc芯片采用tdc

‑

gpx系列型号芯片,转换芯片采用dslvds100x系列型号的芯片。

44.tdc芯片(tdc

‑

gpx系列芯片)的start和stop输入,可接收高速lvds信号触发,具体地,信号lvds2a连接tdc芯片的start引脚,信号lvds1a连接tdc芯片的stop引脚。利用tdc芯片的内部功能测量了lvds2a上升沿与lvds1a上升沿之间的延时差,该延时差可以反映出同步光与信号光在经过信道传输后,两者的延时的差异。其中tdc芯片的测量分辨率可达到皮秒级,适合1hz到ghz频率信号的时间间隔测量。

45.tdc芯片的计算结果,通过spi接口传送给fpga控制单元。fpga控制单元将接收到的tdc时间数字转换单元计算值保存下来,当qkd初始化同步时,用保存值修正时间同步系统。

46.如图4所示,采用本修正系统,alice(发送端)和bob端(接收端)的修正过程如下:系统软件通知alice和bob进入同步修正状态,在alice通过经典网络告诉bob即将发送的同步光、信号光预设的延时时间t,在同步修正阶段,约定alice(发送端)在发送同步光后固定的延时时间t发送一个信号光,fpga控制单元计算出在bob端(接收端)探测到信号光时,同步光与信号光的实际延时差t

′

,t与t

′

的差别

△

t=(t

′‑

t)反映出同步光与信号光在经过信道后的延时差别,bob保存修正值

△

t,将

△

t补偿进alice与bob之间的实际通信,完成同步修正,保障alice与bob间的量子比特位置一一对应。这是基矢比对的前提,也是整个qkd密钥生成的基础。

47.根据上述说明书的揭示和教导,本发明所属领域的技术人员还可以对上述实施方式进行变更和修改。因此,本发明并不局限于上面揭示和描述的具体实施方式,对发明的一些修改和变更也应当落入本发明的权利要求的保护范围内。此外,尽管本说明书中使用了一些特定的术语,但这些术语只是为了方便说明,并不对发明构成任何限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1