用于具有使用频率信息的载频偏移校正的接收器的设备和相关联方法与流程

用于具有使用频率信息的载频偏移校正的接收器的设备和相关联方法

1.相关申请的交叉引用

2.本技术涉及美国专利申请序列号_______,该专利申请提交于_______,标题为“apparatus for receiver with carrier frequency offset correction using phase and frequency information and associated methods”,代理人案号sila428。

技术领域

3.本公开总体涉及通信设备和相关联方法。更具体地说,本公开涉及具有载频偏移(cfo)校正的用于射频(rf)的设备诸如rf接收器,以及相关联方法。

背景技术:

4.随着技术的进步,越来越多的电路元件已被集成到装置诸如集成电路(ic)中。此外,越来越多的装置,诸如ic,或子系统,已被集成到产品中。随着诸如物联网(iot)的发展,这种趋势预计将继续下去。

5.一些设备,诸如iot设备,至少部分地无线操作。换句话说,此种设备使用射频(rf)接收器(rx)和/或发射器(tx)。如本领域普通技术人员所理解的,rf接收器通常受到载频偏移(cfo)的影响。

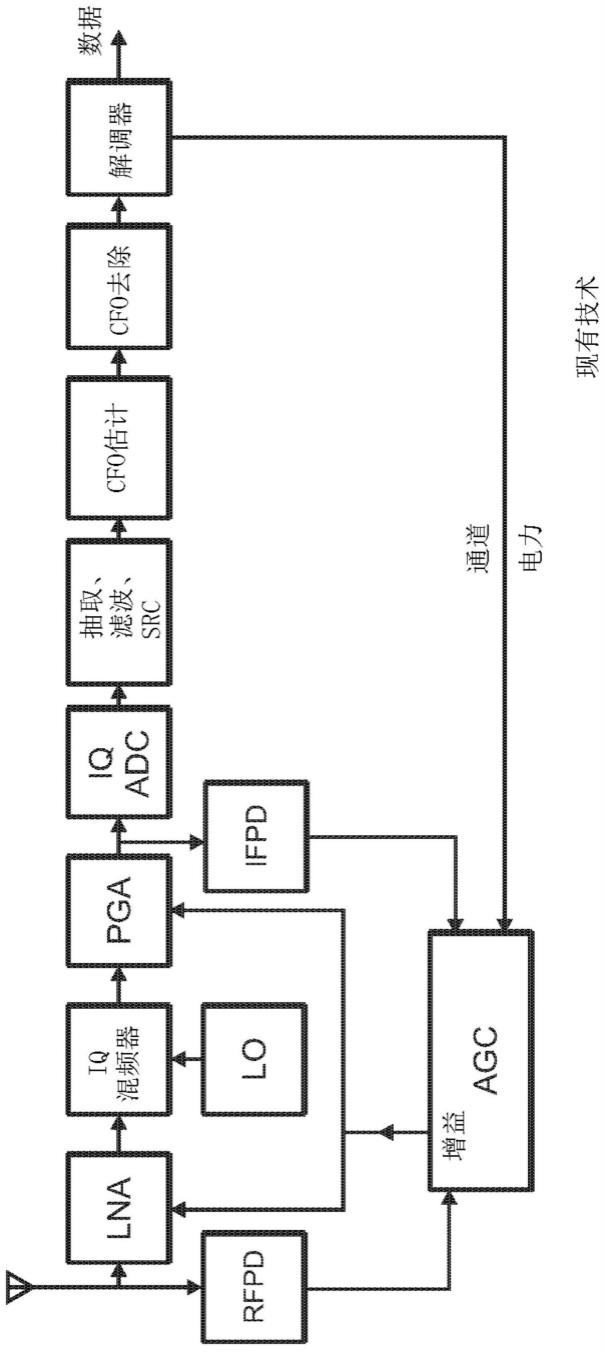

6.图1示出了包括cfo估计和去除的传统rf接收器。图2示出了传统cfo估计电路和传统cfo去除电路的细节。图1和图2中的电路系统是本领域普通技术人员已知的。因此,它们的操作的细节为本领域普通技术人员所理解,并因此在此不再进一步描述。

7.本节中的描述和任何对应的(一个或多个)图都是作为背景信息材料包括的。本节中的材料不应视为承认此类材料构成本专利申请的现有技术。

技术实现要素:

8.根据示例性实施例,设想了用于rf设备的各种设备和相关联方法。根据一个示例性实施例,一种设备包括用于使用多个天线接收rf信号的rf接收器。rf接收器包括解调器以提供开关信号,从而使rf接收器使用多个天线中的一个天线。rf接收器进一步包括估计和去除载频偏移的cfo校正电路。

9.根据另一个示例性实施例,一种设备包括用于使用多个天线接收rf信号的rf接收器。rf接收器包括解调器以提供开关信号,从而使rf接收器使用多个天线中的天线。rf接收器进一步包括:cfo估计电路,其使用开关信号来提供载频偏移的估计;耦合到cfo估计电路的相位差去除(pdr)电路;耦合到cfo估计电路的cfo去除电路,其使用载频偏移的估计来去除载频偏移。

10.根据另一个示例性实施例,一种校正使用多个天线的射频(rf)接收器中的cfo的方法包括使用解调器提供开关信号以使rf接收器使用多个天线中的天线,以及使用cfo校正电路来估计和去除载频偏移。

附图说明

11.附图只是示出了示例性实施例,并因此不应视为限制本技术或要求保护的主题的范围。本领域普通技术人员将理解,所公开的概念使其自身适用于其他等效实施例。在附图中,在多于一张图中使用的相同数字标号表示相同、类似或等同的功能、部件或块。

12.图1示出了传统rf接收器。

13.图2示出了图1的传统rf接收器中的传统cfo估计和cfo去除电路系统的细节。

14.图3示出了用于无天线分集(单天线)的接收器的码片相位的曲线图。

15.图4-图5示出了根据示例性实施例的用于具有天线分集的rf接收器的码片相位的曲线图。

16.图6示出了根据示例性实施例的rf接收器的电路布置。

17.图7示出了根据示例性实施例的用于cfo校正的电路布置。

18.图8a-图8b示出了根据示例性实施例的用于cfo校正方法的流程图。

19.图9示出了根据示例性实施例的rf接收器中的码片相位的曲线图。

20.图10示出了根据示例性实施例的用于rf接收器的电路布置。

21.图11示出了根据示例性实施例的用于cfo校正的电路布置。

22.图12a-图12c示出了根据示例性实施例的用于cfo校正方法的流程图。

23.图13示出了根据示例性实施例的用于cfo校正的电路布置。

24.图14a-图14c示出了根据示例性实施例的用于cfo校正方法的流程图。

25.图15示出了根据示例性实施例的用于rf接收器的电路布置。

26.图16示出了根据示例性实施例的用于cfo校正的电路布置。

27.图17a-图17c示出了根据示例性实施例的用于cfo校正方法的流程图。

28.图18示出了根据示例性实施例的用于无线电通信的系统。

29.图19示出了根据示例性实施例的用于ic的电路布置,其包括rf接收器。

30.图20示出了根据示例性实施例的用于ic的电路布置,其包括rf接收器和rf发射器。

具体实施方式

31.本公开总体涉及通信设备和相关联方法。更具体地说,本公开涉及具有cfo校正的用于rf通信的设备,诸如rf接收器,以及与此类设备相关的相关联方法。在示例性实施例中,为使用天线分集的rf接收器和/或收发器提供cfo校正。

32.如本领域普通技术人员已知的,天线分集允许接收器使用多于一个天线。基于一个或多个标准,诸如与由rf接收器接收的信号相关的一个或多个质量度量或指标,rf接收器可以在任何给定时间从一组天线中使用一个天线。如本领域普通技术人员还已知的,用于rf接收器的天线的选择可以随时间推移而改变,例如,响应于上述一个或多个质量度量或指标的改变。

33.传统rf接收器使用单个天线,例如,如图1所示,即它们不使用天线分集。图3示出了用于此种接收器的码片时间的曲线图10。更具体地说,曲线图10示出了接收器的码片相位作为时间的线性函数,没有不连续或“跳跃”。cfo估计和去除电路系统可以在单天线接收器中利用线性相位作为时间的函数。结果是相对简单的cfo估计和去除方案。

34.然而,当使用两个或更多个天线,即天线分集时,用于每个天线的数据的非连续“区段”会导致码片相位与时间的曲线图。(码片,有时也称为样本,是符号的构成部分或片段。例如,由1010构成的符号具有1和0交替的四个码片)。因为使用多个天线,所以码片(或样本)相位与时间的函数中存在不连续性。

35.图4-图5示出了根据示例性实施例的用于具有天线分集的rf接收器的码片相位的曲线图。例如,rf接收器可以构成图6中的rf接收器20,其使用两个天线:天线23和天线26。取决于接收信号质量的一个或多个度量,诸如接收信号强度指示(rssi),接收器20可以使用天线23或天线26。换句话说,随着使用一个天线的接收信号质量的一个或多个度量下降,接收器20切换到使用另一个天线,诸如天线26。天线之间的切换可以作为时间的函数发生多次。

36.参考图4,作为时间的函数的码片相位的曲线图包括区段13和区段16。区段13对应于使用一个天线(例如,天线23)的码片相位,并且区段16对应于使用另一个天线(例如,天线26)的码片相位。作为cfo校正的一部分,rf接收器20使用来自天线的区段,该天线提供接收信号质量的(一个或多个)更好度量。

37.例如,如图5所示,可以使用区段16。图5示出了包括区段16的码片相位作为拼接时间的函数的曲线图。换句话说,图4中的区段13被去除,并且区段16被联接,以得出图5中的码片相位曲线图。拼接(去除区段13并将区段16联接在一起)引起了图5中码片相位的曲线图中的不连续或“跳跃”。术语“天线开关(antenna switch)”是指相对于拼接时间而不是正常时间的开关/切换。换句话说,在图5中,示出两个此类开关/切换,其对应于码片相位不连续,即区段16之间的两个不连续。

38.鉴于频率是相位相对于时间的导数,参考晶体的特性差异和其他非理想情况会引起载频偏移(cfo)。当存在噪声相位值时,该现象会进一步加剧。cfo可能导致各种不期望的结果。例如,cfo可能导致通常在单位圆(unit circle)上的+1点处的+1符号围绕单位圆旋转。cfo的其他影响为本领域普通技术人员所理解,并且不再进一步讨论。

39.当在天线分集接收器中切换天线时,如上所述,码片的多符号序列由多个不连续区间组成。为了在这种情况下校正cfo,在示例性实施例中,cfo参数相对可靠地被计算。理想情况下,cfo计算精度不会成为rf接收器灵敏度的限制因素。在天线分集的情况下,这些cfo校正技术提供的灵敏度与频率偏移曲线在理想的非cfo情况下的分贝数的几分之一内。

40.根据各种实施例的设备和方法提供了cfo校正,如上所述。当rf接收器中用于每个同相(i)和正交(q)样本的相位测量是有噪声的时候,根据示例性实施例的cfo校正是有效的。在此类情况下,较简单的方案(例如,用于单天线系统的那些方案)可能完全失败,或可能无法运作,或无法与具有百万分之20(20ppm)或更差的准确度或精度的锁相环(pll)一起良好运作。

41.噪声相位值在一些特别应用中往往很明显,诸如物联网(iot)设备(例如ic)和系统。此类系统往往对功耗和成本两者都有相对严格的约束。在此类系统中使用根据各种实施例的cfo校正技术提供了优于传统方法的优点。

42.在示例性实施例中,相位的不连续性被单独估计和去除。因此,此类实施例中的cfo校正使用两个单独的环路,而不是传统使用的一个环路。下面的描述提供了此类实施例的示例。

43.图6示出了根据示例性实施例的用于rf接收器20的电路布置。rf接收器20包括cfo校正电路系统,如下面详细描述。rf接收器20经由切换器/开关29分别使用两个天线23和26。开关29由解调器电路59控制,即经由由解调器59提供的控制信号,开关29将由天线23或天线26接收的信号提供给低噪声放大器(lna)32。天线的选择可以如上所述进行,即基于一个或多个标准,诸如与由rf接收器接收的信号相关的一个或多个质量度量或指标。

44.lna 32放大了开关29接收的信号。放大的量取决于由自动增益控制(agc)电路62提供的增益信号。lna32向iq混频器38提供放大的信号。iq混频器将放大的信号与来自lo电路35的本地振荡器(lo)信号混频,以生成下变频信号。

45.下变频信号被提供给可编程增益放大器(pga)电路41。响应于来自agc电路62的增益信号,pga电路41放大下变频信号以生成用于iq模数转换器(adc)电路44的输入信号。

46.adc电路44将来自pga电路41的iq信号转换为数字iq信号。数字iq信号被提供给抽取、滤波和采样率转换(src)电路50,顾名思义,抽取、滤波和采样率转换(src)电路50对从adc电路44接收的信号进行抽取、滤波和src操作。抽取、滤波和src操作的细节取决于各种因素,诸如给定应用的设计和操作规范、成本、复杂性、调制方案、频率计划等,如本领域普通技术人员将理解的。

47.rf接收器20中的cfo校正电路52包括cfo估计电路53和cfo去除电路56。抽取、滤波和src(dfs)电路50的输出馈送cfo校正电路52的输入。cfo估计电路53的输出馈送cfo去除电路56的输入,而cfo去除电路56的输出驱动解调器电路59的输入(如下面详细描述)。

48.如下所述,cfo估计电路53响应于来自解调器59的控制信号,向cfo去除电路56提供cfo的估计。控制信号提供天线或码片相位切换点(见图4-图5)。

49.cfo去除电路56去除(或几乎去除,在具有非理想电路系统的实际实施方式中,如本领域普通技术人员将理解的)cfo。换句话说,cfo估计电路53和cfo去除电路的设计目标中的一个是使多天线情况(见图5)看起来与单天线情况(见图3)类似。

50.图7示出了根据示例性实施例的用于cfo校正电路52的电路布置。更具体地说,该图示出了图6的接收器中使用的cfo估计电路53和cfo去除电路56的细节。cfo估计电路和cfo去除电路56通过去除“跳跃”或不连续,使多天线情况看起来与单天线情况相似(例如,见图5)。

51.再次参考图7,cfo去除电路80包括乘法器80,其接收i和q(iq_in)信号,这些信号从抽取、滤波和src(dfs)电路50提供给cfo校正电路52。乘法器80将d-锁存器98(如下所述)的输出与iq_in信号相乘,以生成输出i和q(iq_out)信号。iq_out信号被提供给解调器59(见图6)。

52.再次参考图7,解调器59经由寄存器块137向cfo校正电路52中的各个块提供控制信号。例如,解调器59经由寄存器块137,向消旋器(derotator)83、解多路复用器(demux)86和平均化电路128提供控制信号。来自解调器59的控制信号指示例如从一个天线到另一个的切换点,例如,从天线23到天线26(见图6)。注意,平均化是指n个元素的总和除以n,其中n代表大于1的正整数。消旋器本质上是添加/减去固定的相位序列(由给定的无线标准或协议的规范确定,rf接收器根据该标准或协议进行操作),使得所有码片具有理想的相同相位。

53.再次参考图7,乘法器80的输出被馈送到cfo估计电路53中的消旋器83。不考虑cfo

的影响,消旋器83确保所有的码片具有相同的相位(或在实际的现实生活实施方式中几乎相同的相位)。响应于来自解调器59的控制信号(经由寄存器块电路137提供),demux 86将消旋器83的输出提供给平均化电路89、平均化电路107或平均化电路116,这取决于对使用特定天线的哪个区间执行cfo估计。寄存器块持有来自解调器59的配置信息和控制信号,并将那些信号提供给cfo估计电路53中的各个块。

54.平均化电路89、平均化电路107和平均化电路116是cfo估计电路53中的三个分支或环路的一部分,该分支或环路中的每个包括相位平均化,之后是相位到频率的转换,之后是频率平均化。在第一分支中,平均化电路89对消旋器83的相位输出信号进行平均化,并将所得信号提供给乘法器95。

55.由平均化电路89(以及类似地由平均化电路107和116)执行的平均化改善了相位样本的信噪比(snr)。乘法器95与延迟电路92一起提供相位到频率转换。乘法器95的频率输出信号被提供给平均化电路101。平均化电路101提供对频率值进行平均化,并提供cfo值,cfo1。

56.第二分支(相位平均化电路107、相位到频率转换器(乘法器110和延迟电路104),以及频率平均化电路113类似地操作,以提供cfo值,cfo2。最后,第三分支(相位平均化电路116、相位到频率转换器(乘法器122和延迟电路119),以及频率平均化电路125类似地操作,以提供cfo值,cfo3。

57.cfo1、cfo2和cfo3值,对应于使用特定天线时的时间段,在图9中示出。再次参考图7,相位和/或频率样本的数量由三个分支中的平均化电路平均化,例如,可以由解调器59或控制器等配置或编程。如本领域普通技术人员将理解的,取决于诸如设计和性能规格、成本、目标性能、目标市场等因素,可以使用其他数量的电路分支,诸如两个或多于三个。

58.三个分支的输出,即频率平均化电路101、113和123的输出,分别作为输入提供给平均化电路128。在解调器59的控制下,经由寄存器块137,平均化电路128改善频率样本的snr。

59.坐标旋转数字计算机(cordic)131将来自平均化电路128的iq样本转换为频率样本,并然后创建具有估计的恒定频率的iq样本。求幂块134将从cordic 131接收的相位增量转换为相位增量的复数矢量。按期望,求幂块134可以使用cordic实施。换句话说,对于每个相位ph,cordic计算exp(i*ph)=cos(ph)+i*sin(ph),其中i是虚单位或-1的平方根。在示例性实施例中,按期望,求幂块134可以使用cordic实施。

60.求幂块134的输出(旋转系数)被提供给d-锁存器98。标记为“迭代clk”的时钟信号为锁存器98计时(解调器或控制器(未示出)可以向锁存器98提供时钟信号)。锁存器98的输出作为输入被提供给乘法器80。在每次锁存器98被计时之前,经由寄存器块137,解调器59通过增加由平均化电路128执行的平均化操作的数量,即通过增加n来提高滤波的水平。

61.图8a-图8b示出了根据示例性实施例的用于cfo校正方法的流程图。更具体地说,图8a-图8b说明了图6-图7的示例性实施例的流程图。参考图8a,在153处,由rf接收器(例如,图6中的接收器)检测分组。在156处,估计并存储cfo(例如,图9中的cfo1)。

62.在159处,检查天线开关计数是否超过阈值n,其中n表示正整数。如果否,则控制返回156。然而,如果计数超过n,则在162处对cfo进行平均化,并且在165处去除cfo。注意,天线开关的数量乘以开关时间不能超过前导码时间。因此,仅仅作为一个示例,在zigbee规范

的情况下,前导码中有8个零符号。如果每个开关持续时间是1个符号,则8/(天线数)是n的绝对最大值,并且开关计数器将确定何时退出循环。

63.图8b示出了在图8a中的156处估计并存储cfo的细节。参考图8b,在156a处,执行iq符号消旋。在156b处,执行固定相位平均化。在156c处,从相位样本导出频率。在156d处,执行频率平均化。

64.图10示出了根据示例性实施例的用于rf接收器20的电路布置。图10中的rf接收器20类似于图6中的rf接收器20,但在cfo校正电路52中有所差异。参考图10,cfo校正电路包括cfo估计电路53、cfo去除电路56和相位增量(delta)去除或相位差去除(pdr)电路175。

65.图11示出了根据示例性实施例的用于cfo校正的电路布置。更具体地说,图11示出了图10中的cfo校正电路52的细节。再次参考图11,cfo去除电路56与图7所示的相同。

66.此外,图11中的cfo估计电路53类似于图7中的cfo估计电路。然而,在图11中的实施例中,使用了一个分支或环路(而不是图7中的三个)。更具体地说,图11中的实施例使用了图7中所示的第一分支,省略了平均化电路101。

67.此外,像图7中那样使用求幂电路134。与图7中的实施例不同,图11中的cordic 131的输出驱动pdr电路175的输入。

68.pdr电路175包括demux 178,其接收cordic 131的输出。响应于来自解调器(未示出)的经由寄存器块137提供的控制信号,demux 176将其输入信号提供给乘法器178或多路复用器(mux)181。

69.如果将demux 176的输入信号提供给乘法器178,那么乘法器178将频率样本乘以32,其表示每个符号的码片数。然而,如本领域普通技术人员将理解的,在其他实施例中,每个符号的码片数可能不同于32,这取决于诸如设计和性能规格等因素。此外,乘以32假设为每个符号切换天线,因此在上面讨论的zigbee示例的情况下,每32个码片。

70.作为另一个选项,取决于来自寄存器块137的控制信号,demux 176提供其输入信号给mux 181,而不进行修改。实际上,demux电路176确定是使用未经修改的频率样本还是使用已乘以每个符号的码片数的频率样本。

71.响应于来自解调器(未示出)的经由寄存器块137提供的控制信号,mux 181将其输入信号中的一个提供给求幂电路134。如上所述,求幂块134可以按期望使用cordic来实施。

72.图12a-图12c示出了根据示例性实施例的用于cfo校正方法的流程图。更具体地说,图12a-图12c示出了用于图10-图11的示例性实施例中的cfo校正的流程图。

73.参考图12a,在153处,由rf接收器(例如,图10中的接收器)检测分组。在203处,估计并存储cfo(例如,图9中的cfo1)。在206处,去除相位差。在209处,执行非恒定频率去除。在212处,检查迭代计数是否超过阈值n,其中n表示正整数。如果否,则控制返回203。然而,如果计数超过n,则cfo校正结束。

74.图12b示出了在图12a中203处估计并存储cfo的细节。参考图12b,在203a处,执行iq符号消旋。在203b处,执行固定相位平均化。在203c处,从相位样本导出频率。在203d处,执行频率平均化。图12c示出了在图12a中206处去除相位差的细节。

75.在206a处,检查迭代计数是否等于每个天线切换时间的码片数,即,在用于zigbee示例的每个符号的切换的情况下为(32)。如果是,则频率样本乘以每个符号的码片数(例如32)。如果否,则控制传递到206c,其中结果被组合。在206d处,检查迭代计数是否超过总码

片数。如果是,则过程继续进行(例如,到图12a中的209),否则控制返回206a。

76.图10中所示的rf接收器20可以与图11中所示的示例性实施例以外的cfo校正电路52一起使用。图13示出了此种可替代cfo校正电路52的框图。图13中的cfo去除电路与图11中所示的相同,并在上面描述。

77.cfo估计电路53类似于图11中所示的对应电路,但在图13中的实施例中,pdr电路175(下面详细描述)耦合在乘法器95的输出和平均化电路128的输入之间。更具体地说,乘法器95的输出馈送pdr电路175的输入,并且pdr电路175的输出馈送平均化电路128的输入。

78.尽管pdr电路175在频率样本上操作,但在功能上,pdr电路175执行相位差去除。相位差去除包括将一些频率样本归零(经由到mux 220的二进制0输入)。pdr电路175包括计数器223和mux 220。mux 220的一个输入接收二进制逻辑0电平。mux 220的另一个输入接收乘法器95的输出。

79.计数器223提供mux 220的选择或控制信号。更具体地说,在解调器59的控制下,经由寄存器块137,计数器223响应于标记“样本clk”的时钟信号进行计数。计数器223由寄存器块134编程,因为样本归零(凭借到mux 220的二进制0输入设置为零)的位置取决于天线开关(例如,图10中的开关29)的位置和当前的迭代数(信息已经由cfo校正电路52中的环路被处理的次数)。

80.基本上,pdr电路175将一些频率样本归零(凭借应用于mux 220的输入的二进制0)。更具体地说,经由来自解调器59的选择信号(经由寄存器块134提供),mux 220在存在“跳跃”或不连续时提供二进制0作为其输出。计数器223由寄存器块137编程,因为样本归零的位置取决于天线开关的位置,以及迭代数(“迭代clk”信号已经有多少个周期被应用于锁存器98)。解调器59向寄存器块137提供这两个数量。

81.图14a-图14c示出了根据示例性实施例的用于cfo校正方法的流程图。更具体地说,图14a-图14c示出了用于图10和图13的示例性实施例中的cfo校正的流程图。

82.参考图14a,在153处,由rf接收器(例如,图10中的接收器)检测分组。在223处,进行初始频率计算。在236处,天线开关值被归零化(设置为0,如上所述)。更具体地说,计算差分相位值(频率值),并且对应于转变的值被归零化。在239处,估计并存储cfo。

83.在242处,检查迭代计数是否超过阈值n,其中n表示正整数。如果是,则cfo校正结束。否则,控制传递到248,其中改变零点。此后,在245处,平均化操作的数量m增加,其中m表示正整数,并且控制返回233。

84.图14b示出了在图14a中233处执行的初始频率计算的细节。参考图14b,在233a处,码片被消旋。在233b处,执行m样本相位平均化操作。在233c处,从相位样本导出频率值。

85.图14c示出了在图14a中239处执行的cfo估计和去除的细节。在239a处,执行频率平均化。在239b处,执行恒定频率去除。

86.图15示出了根据示例性实施例的用于rf接收器20的电路布置。图15中的rf接收器20类似于图10中的rf接收器20,但在cfo校正电路52中有所差异。参考图15,cfo校正电路包括cfo估计电路53、cfo去除电路56、pdr电路262和相位增量估计或相位差估计(pde)电路260。

87.图16示出了根据示例性实施例的用于cfo校正的电路布置。更具体地说,图16示出了图15中的cfo校正电路52的细节。再次参考图16,cfo去除电路56与图7所示的相同。

88.此外,图16中的cfo估计电路53类似于图7中的cfo估计电路。然而,在图16中的实施例中,使用了一个分支或环路(而不是图7中的三个)。更具体地说,图16中的实施例使用了图7中所示的第一分支,省略了平均化电路101、消旋器83和demux 86。因此,图16中的cfo估计电路53包括相位平均化电路279、相位到频率转换器电路(包括乘法器285和延迟电路282)、频率平均化电路288、cordic 131和求幂电路134。

89.再次参考图16,pde电路260类似于cfo估计电路53,但有以下差异。第一,没有使用第二平均化电路(cfo估计电路53中的平均化电路288)。第二,代替cfo估计电路53中的一个分支或环路,pde电路260使用两个分支或环路,即两个电路分支,其(响应于来自寄存器块137的控制信号)对由mux 86提供的消旋器83的输出进行操作和修改,并将结果提供给pdr电路262。mux 86还(响应于来自寄存器块137的控制信号)将消旋器83的输出提供给pdr电路262。第一分支包括平均化电路89a、乘法器95a、延迟电路92a、cordic 131a和求幂电路134a。第二分支包括平均化电路89b、乘法器95b、延迟电路92b、cordic 131b和求幂电路134b。

90.第三,demux 86接收消旋器83的输出,并(经由寄存器块134)在解调器59的控制下将该输出提供给上述两个分支中的一个。消旋器83从乘法器80的输出接收其输入。第四,第一分支和第二分支中的每个中的相位到频率转换器分别响应于(由解调器59经由寄存器块137提供的)控制信号137d和137c,对k个样本而不是固定的样本操作(因此为延迟电路92a和92b使用了记号z-k)。

91.pdr电路262类似于cfo去除电路56,但有以下差异。第一,pdr电路262使用mux 276,其(经由寄存器块134)在解调器59的控制下将其三个输入信号中的一个提供给cfo估计电路53。

92.第二,pdr电路262的两个乘法器,273a和273b。乘法器273a将求幂电路134a的输出与乘法器273b的输出相乘,并将所得输出提供给mux 276。乘法器273b将求幂电路134b的输出与消旋器83的输出(如由demux 86提供)相乘,并将所得输出提供给mux 276作为第二输入。

93.最后,消旋器83的输出(如由demux 86提供)驱动mux 276的第三输入。mux 276的三个输入对应于三个区间,第一区间对应于没有任何修改的消旋器83的输出,第二区间已旋转了一次(乘法器273b的输出),并且第三区间已旋转了两次(乘法器273a的输出)。如本领域普通技术人员将理解的,可以使用其他数量的电路分支,这取决于诸如设计和性能规格、成本、目标性能、目标市场等因素。

94.图17a-图17c示出了根据示例性实施例的用于cfo校正方法的流程图。更具体地说,图17a-图17c示出了用于图15-图16的示例性实施例中的cfo校正的流程图。

95.参考图17a,在153处,由rf接收器(例如,图15中的接收器)检测分组。在303处,执行iq符号消旋。在309处,估计并去除相位差。在312处,估计并存储cfo。

96.在315处,检查迭代计数是否超过阈值n,其中n表示正整数。如果是,则cfo校正结束。否则,控制传递到306,其中平均化操作的数量(m和n)增加,并且控制传递到303。

97.图17b示出了在图17a中309处执行的估计和去除相位差的细节。参考图17b,在309a处,相位差被计算为天线开关点后n个样本的均值(平均)相位减去天线开关点前n个样本的均值(或平均)相位。

98.在309b处,执行恒定相位去除操作。在309c处,执行检查迭代计数是否超过天线开关的数量。如果是,则控制传递到312(见图17a),否则,控制返回309a(即,执行另一个迭代)。

99.图17c示出了在图17a中312处执行的估计和去除cfo的细节。参考图17b,在312a处,执行m样本相位平均化。在312b处,频率值从平均化相位值导出。在312c处,对频率值执行平均化操作。在312d处,执行恒定频率去除。

100.根据示例性实施例的接收器可以按期望用于各种通信布置、系统、子系统、网络等。图18示出了根据示例性实施例的用于无线电通信的系统500。该系统包括rf接收器5,如上所述。

101.系统500包括耦合到天线10a的发射器515。经由天线10a,发射器515传输rf信号。rf信号可以由接收器20b经由天线10b接收。此外,或可替代地,收发器520a和/或收发器520b可以(分别经由接收器20c和20d)接收传输的rf信号。

102.除了接收能力外,收发器520a和收发器520b还可以传输rf信号。传输的rf信号可以由接收器20接收,要么在独立的接收器(20b)中,要么经由非传输的收发器(20c或20d)的接收器电路系统。

103.还设想了具有不同配置和/或能力的其他系统或子系统。例如,在一些示例性实施例中,两个或更多个收发器(例如,收发器520a和收发器520b)可形成网络,诸如ad-hoc网络或网状网络。作为另一个示例,在一些示例性实施例中,收发器520a和收发器520b可形成网络的一部分,例如,与发射器515结合。

104.rf接收器,诸如上面描述的rf接收器20,可以用于各种电路、块、子系统和/或系统中。例如,在一些实施例中,此类rf接收器可以集成在ic中,诸如微控制器单元(mcu)。图19示出了根据示例性实施例的ic 550的框图。图20类似于图19的实施例,并示出了ic 550,除了rf接收器5外,该ic还包括rf发射器515。因此,图20中的实施例具有rf收发器能力。

105.参考图19,ic 550构成或包括mcu。ic 550包括若干个块(例如,(一个或多个)处理器565、数据转换器605、i/o电路系统585等),它们使用链路560彼此通信。在示例性实施例中,链路560可以构成耦合机构,诸如总线、一组导体或半导体元件(例如迹线、装置等),以用于传送信息,诸如数据、命令、状态信息等。

106.ic 550可以包括耦合到一个或多个处理器565、时钟电路系统575和电源管理电路系统或电源管理单元(pmu)580的链路560。在一些实施例中,(一个或多个)处理器565可以包括用于提供信息处理(或数据处理或计算)功能的电路系统或块,诸如中央处理单元(cpu)、算术逻辑单元(alu)等。在一些实施例中,此外,或作为替代,(一个或多个)处理器565可以包括一个或多个dsp。dsp可以按期望提供各种信号处理功能,诸如算术功能、滤波、延迟块等。

107.时钟电路系统575可以生成一个或多个时钟信号,该信号促进或控制ic550中一个或多个块的操作的定时。时钟电路系统575也可以按期望控制使用链路560的操作的定时。在一些实施例中,时钟电路系统575可以经由链路560向ic 550中的其他块提供一个或多个时钟信号。

108.在一些实施例中,pmu 580可以关于电路的一部分或电路的所有部件,诸如ic 550中的一个或多个块,降低设备(例如ic 550)的时钟速度、关闭时钟、降低功率、关闭电源、禁

用(或断电或置于较低的功耗或睡眠或非活动或空闲状态)、启用(或上电或置于较高的功耗或正常或活动状态)或上述的任何组合。此外,pmu 580可以响应于从非活动状态转变到活动状态(包括但不限于当(一个或多个)处理器565从低功率或空闲或睡眠状态转变到正常工作状态时)而打开时钟、提高时钟速率、打开电源、提高功率或上述的任何组合。

109.链路560可以通过串行接口595耦合到一个或多个电路600。通过串行接口595,耦合到链路560的一个或多个电路或块可以与电路600通信。电路600可以使用一个或多个串行协议进行通信,例如smbus、i2c、spi等,如本领域普通技术人员将理解的。

110.链路560可以通过i/o电路系统585耦合到一个或多个外围设备590。通过i/o电路系统585,一个或多个外围设备590可以耦合到链路560,并因此可以与耦合到链路560的一个或多个块通信,例如,(一个或多个)处理器565、存储器电路625等。

111.在示例性实施例中,外围设备590可以包括各种电路系统、块等。示例包括i/o装置(小键盘、键盘、扬声器、显示装置、存储装置、计时器、传感器等)。注意,在一些实施例中,一些外围设备590可以在ic 550的外部。示例包括小键盘、扬声器等。

112.在一些实施例中,就一些外围设备而言,i/o电路系统585可以被绕过。在此类实施例中,一些外围设备590可以耦合到链路560并与之通信而不使用i/o电路系统585。在一些实施例中,此类外围设备可以在ic 550的外部,如上所述。

113.链路560可以经由(一个或多个)数据转换器605耦合到模拟电路系统620。(一个或多个)数据转换器605可以包括一个或多个adc 605a和/或一个或多个dac 605b。

114.(一个或多个)adc 605a从模拟电路系统620接收(一个或多个)模拟信号,并将该(一个或多个)模拟信号转换为数字格式,它们将其传送至耦合到链路560的一个或多个块。相反,(一个或多个)dac 605b从耦合到链路560的一个或多个块接收(一个或多个)数字信号,并将该(一个或多个)数字信号转换为模拟格式,它们将其传送至模拟电路系统620。

115.模拟电路系统620可以包括提供和/或接收模拟信号的各种电路系统。示例包括传感器、换能器等,如本领域普通技术人员将理解的。在一些实施例中,模拟电路系统620可以与ic 550外部的电路系统通信,以按期望形成更复杂的系统、子系统、控制块或系统、反馈系统和信息处理块。

116.控制电路系统570耦合到链路560。因此,控制电路系统570可以通过提供控制信息或信号与耦合到链路560的各种块进行通信和/或控制其操作。在一些实施例中,控制电路系统570还接收来自耦合到链路560的各种块的状态信息或信号。此外,在一些实施例中,控制电路系统570促进(或控制或监督)耦合到链路560的各种块之间的通信或协作。

117.在一些实施例中,控制电路系统570可以启动或响应复位操作或信号。复位操作可以引起ic 550的耦合到链路560的一个或多个块等的复位,如本领域普通技术人员将理解的。例如,控制电路系统570可以引起pmu 580,以及电路系统诸如rf接收器5或其各种块、电路或部件复位到初始或已知状态。

118.在示例性实施例中,控制电路系统570可以包括各种类型和块的电路系统。在一些实施例中,控制电路系统570可以包括逻辑电路系统、有限状态机(fsm)或其他电路系统,以执行操作,诸如上述操作。

119.通信电路系统640耦合到链路560,并且也耦合到ic 550外部的电路系统或块(未示出)。通过通信电路系统640,耦合到链路560的各种块(或ic 550,笼统来说)可以经由一

个或多个通信协议与外部电路系统或块(未示出)通信。通信的示例包括usb、以太网等。在示例性实施例中,可以使用其他通信协议,这取决于诸如用于给定应用的设计或性能规格等因素,如本领域普通技术人员将理解的。

120.如上所述,存储器电路625耦合到链路560。因此,存储器电路625可以与耦合到链路560的一个或多个块通信,诸如(一个或多个)处理器565、控制电路系统570、i/o电路系统585等。

121.存储器电路625为ic 550中的各种信息或数据提供存储,诸如操作数、标志、数据、指令等,如本领域普通技术人员将理解的。存储器电路625可以按期望支持各种协议,诸如双数据速率(ddr)、ddr2、ddr3、ddr4等。

122.在一些实施例中,通过存储器电路625的存储器读和/或写操作涉及使用ic 550中的一个或多个块,诸如(一个或多个)处理器565。直接存储器访问(dma)布置(未示出)允许在一些情况下提高存储器操作的性能。更具体地说,dma(未示出)提供了一种机制,以用于在数据的源头或目的地和存储器电路625之间直接执行存储器读和写操作,而不是通过块,诸如(一个或多个)处理器565。

123.存储器电路625可以包括各种存储器电路或块。在所示的实施例中,存储器电路625包括非易失性(nv)存储器635。此外或代替地,存储器电路625可以包括易失性存储器(未示出),诸如随机存取存储器(ram)。nv存储器635可以用于存储与ic 550中的一个或多个块的性能、控制或配置相关的信息。例如,nv存储器635可以存储与rf接收器20的操作相关的配置信息,诸如用于rf接收器20的各种块、电路、部件等的配置信息。

124.rf接收器20耦合到链路560。通过链路560,rf接收器20可以从ic 550中的一个或多个块接收控制和/或状态信息。反之,通过链路560,rf接收器20可以提供信息,诸如控制和/或状态信息,以及经由天线10通过rf信号接收的信息。

125.包括上面描述的和在示例性实施例中使用的数字和/或混合信号电路系统的各种电路和块可以以各种方式和使用各种电路元件或块实施。例如,adc 35、抽取、滤波和src(dfs)电路50、cfo校正电路系统52(包括cfo估计电路、cfo去除电路、pde电路和pdr电路)、解调器59等通常可以使用数字电路系统实施。按期望并且如本领域普通技术人员将理解的,数字电路系统可以包括电路元件或块,诸如门、数字多路复用器(mux)、锁存器、触发器、寄存器、有限状态机(fsm)、处理器、可编程逻辑(例如现场可编程门阵列(fpga)或其他类型的可编程逻辑)、算术逻辑单元(alu)、标准单元、定制单元、定制模拟单元等。此外,按期望,模拟电路系统或混合信号电路系统或两者都可以被包括,例如电源转换器、分立装置(晶体管、电容器、电阻器、电感器、二极管等)等。按期望并且如本领域普通技术人员将理解的,模拟电路系统可以包括偏置电路、去耦电路、耦合电路、电源电路、电流镜、电流和/或电压源、滤波器、放大器、转换器、信号处理电路(例如乘法器)、检测器、换能器、分立部件(晶体管、二极管、电阻器、电容器、电感器)、模拟mux等。如上所述并且如本领域普通技术人员将理解的,除了模拟电路系统和数字电路系统之外,混合信号电路系统可以包括模数转换器(adc)、数模转换器(dac)等。对于给定的实施方式,电路系统的选择取决于各种因素,如本领域普通技术人员将理解的。此类因素包括设计规格、性能规格、成本、ic或装置面积、可用技术诸如半导体制造技术、目标市场、目标最终用户等。

126.包括上面描述的和在示例性实施例中使用的模拟电路系统的各种电路和块可以

以各种方式和使用各种电路元件或块实施。例如,lna 32、混频器38、lo 35和pga 41通常可以使用模拟电路系统实施。按期望并且如本领域普通技术人员将理解的,模拟电路系统可以包括偏置电路、去耦电路、耦合电路、电源电路、电流镜、电流和/或电压源、滤波器、放大器、转换器、信号处理电路(例如乘法器)、传感器或检测器、换能器、分立部件(晶体管、二极管、电阻器、电容器、电感器)、模拟mux等。此外,可以包括数字电路系统或混合信号电路系统或两者。按期望并且如本领域普通技术人员将理解的,数字电路系统可以包括电路元件或块,诸如门、数字多路复用器(mux)、锁存器、触发器、寄存器、有限状态机(fsm)、处理器、可编程逻辑(例如现场可编程门阵列(fpga)或其他类型的可编程逻辑)、算术逻辑单元(alu)、标准单元、定制单元、定制模拟单元等。如上所述并且如本领域普通技术人员将理解的,除了模拟电路系统和数字电路系统之外,混合信号电路系统可以包括模数转换器(adc)、数模转换器(dac)等。对于给定的实施方式,电路系统的选择取决于各种因素,如本领域普通技术人员将理解的。此类因素包括设计规格、性能规格、成本、ic或装置面积、可用技术诸如半导体制造技术、目标市场、目标最终用户等。

127.参考附图,本领域普通技术人员将注意到,所示的各种块可能主要描绘了概念性的功能和信号流。实际的电路实施方式可以包含或可以不包含用于各种功能块的可单独识别的硬件,并且可以使用或可以不使用所示的特定电路系统。例如,人们可以按期望将各种块的功能组合到一个电路块中。此外,人们可以按期望在几个电路块中实现单个块的功能。对于给定的实施方式,电路实施方式的选择取决于各种因素,诸如特定的设计和性能规格。除了本公开中的实施例外,其他的修改和可替代实施例对于本领域普通技术人员来说将是明显的。因此,本公开向本领域技术人员教导了根据示例性实施例执行所公开的概念的方式,并应被理解为仅仅是说明性的。在适用的情况下,附图可以或可以不按比例绘制,如本领域普通技术人员将理解的。

128.示出和描述的特定形式和实施例仅构成示例性实施例。本领域技术人员可以在不脱离本公开的范围的情况下对零件的形状、大小和布置进行各种改变。例如,本领域技术人员可以用等效元件代替示出和描述的元件。此外,本领域技术人员可以在不脱离本公开的范围的情况下,独立于使用其他特征来使用所公开的概念的某些特征。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1