音频收发电路及相关设备、方法、装置和存储介质与流程

1.本技术涉及电子信息技术领域,特别是涉及一种音频收发电路及相关设备、方法、装置和存储介质。

背景技术:

2.随着信息化技术的不断发展,人们越来越倾向于使用多人对话系统来实现线上会议、商务洽谈等。通过多人对话系统结合相应算法,可以在一定程度上解决很多房间声学问题,比如声源定位、去混响、语音增强、盲源分离等,故有助于提升多人对话质量。

3.目前,市面上多人对话系统一般通过集成麦克风阵列以及诸如dsp(digital signal processor,数字信号处理器)、arm(即advanced risc machines)、mcu(micro control unit,微控制单元)、adc(analog to digital converter,模拟数字转换器)等元器件实现。然而,这些方式均存在时钟不同步的问题,故很难实现所有通道数据同步且对齐,继而直接影响后续上述算法的正常执行。有鉴于此,如何实现所有通道数据同步且对齐成为亟待解决的问题。

技术实现要素:

4.本技术主要解决的技术问题是提供一种音频收发电路及相关设备、方法、装置和存储介质,能够实现所有通道数据同步且对齐。

5.为了解决上述技术问题,本技术第一方面提供了一种音频收发电路,包括:数据收发模组、传输总线和主控模组,数据收发模组,包括时钟管理模块和并行设置的多个音频收发模块,音频收发模块用于通过音频总线耦接至拾音电路和/或扬声电路,且时钟管理模块的输出端连接至各个音频收发模块,以同步各个音频收发模块的时钟参数;传输总线,包括主控接口、数据接口和第一配置接口,多个音频收发模块均耦接至数据接口,且时钟管理模块的配置端连接至第一配置接口;主控模组,连接至主控接口,以通过主控接口实现与数据收发模组之间的数据互通。

6.为了解决上述技术问题,本技术第二方面提供了一种多媒体设备,包括:拾音电路、扬声电路和上述第一方面中的音频收发电路;其中,拾音电路、扬声电路通过音频总线耦接至音频收发电路。

7.为了解决上述技术问题,本技术第三方面提供了一种音频收发方法,音频收发方法应用于上述第一方面中的音频收发设备,音频收发方法包括:主控模组通过传输总线同步各个音频收发模块的时钟参数;基于音频收发任务,通过传输总线获取各个音频收发模块收取的第一音频数据,和/或,准备第二音频数据,由各个音频收发模块通过传输总线取走并发出第二音频数据。

8.为了解决上述技术问题,本技术第四方面提供了一种音频收发装置,音频收发装置集成于上述第一方面中的音频收发电路,音频收发装置包括:时钟同步模块和数据传输模块,时钟同步模块,用于驱使主控模组通过传输总线同步各个音频收发模块的时钟参数;

数据传输模块,用于驱使主控模组基于音频收发任务,通过传输总线获取各个音频收发模块收取的第一音频数据,和/或,准备第二音频数据,由各个音频收发模块通过传输总线取走并发出第二音频数据。

9.为了解决上述技术问题,本技术第五方面提供了一种计算机可读存储介质,存储有能够被处理器运行的程序指令,程序指令用于实现上述第三方面中的音频收发方法。

10.上述方案,音频收发电路包括数据收发模组、传输总线和主控模组,数据收发模组用于通过音频总线耦接至拾音电路和/或扬声电路,时钟管理模块的输出端连接至各个音频收发模块,以同步各个音频收发模块的时钟参数,传输总线包括主控接口、数据接口和第一配置接口,多个音频收发模块均耦接至数据接口,且时钟管理模块的配置端连接至第一配置接口,主控模组连接至主控接口,以通过主控接口实现与数据收发模组之间的数据互通,一方面通过传输总线的主控接口和数据接口,能够有利于实现多个音频收发模块统一的数据收发调度,另一方面通过传输总线的主控接口和第一配置接口,能够同步各个音频收发模块的时钟参数,故能够实现所有通道数据同步且对齐。

附图说明

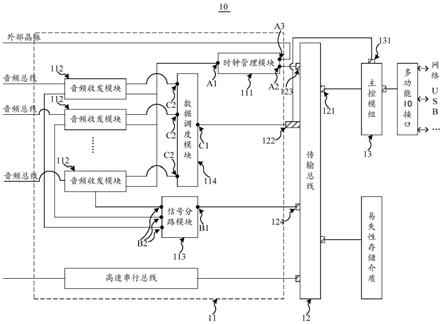

11.图1是本技术音频收发电路一实施例的框架示意图;

12.图2是易失性存储介质的存储空间示意图;

13.图3是音频收发模块一实施例的框架示意图;

14.图4是本技术多媒体设备一实施例的框架示意图;

15.图5是本技术音频收发方法一实施例的流程示意图;

16.图6是本技术音频收发装置一实施例的框架示意图;

17.图7是本技术计算机可读存储介质一实施例的框架示意图。

具体实施方式

18.下面结合说明书附图,对本技术实施例的方案进行详细说明。

19.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、接口、技术之类的具体细节,以便透彻理解本技术。

20.本文中术语“系统”和“网络”在本文中常被可互换使用。本文中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本文中字符“/”,一般表示前后关联对象是一种“或”的关系。此外,本文中的“多”表示两个或者多于两个。

21.请参阅图1,图1是本技术音频收发电路10一实施例的框架示意图。音频收发电路10包括:数据收发模组11、传输总线12和主控模组13,数据收发模组11包括时钟管理模块111和并行设置的多个音频收发模块112,音频收发模块112用于通过音频总线耦接至拾音电路(未图示)和/或扬声电路(未图示),且时钟管理模块111的输出端a1连接至各个音频收发模块112,以同步各个音频收发模块112的时钟参数;传输总线12包括主控接口121、数据接口122和第一配置接口123,多个音频收发模块112均耦接至数据接口122,且时钟管理模块111的配置端a2连接至第一配置接口123;主控模组13连接至主控接口121,以通过主控接口121实现与数据收发模组11之间的数据互通。

22.在一个实施场景中,传输总线12可以包括但不限于axi(即advanced extensible interface)等,在此不做限定。

23.在一个实施场景中,时钟管理模块111可以包括但不限于:pll(phase locked loop,锁相环)、mmcm(mixed-mode clock manager,混合模式时钟管理器)等,在此不做限定。时钟管理模块111的工作原理,可以参阅诸如pll、mmcm等相关技术细节,字词不再赘述。故此,通过时钟管理模块111来配置音频收发模块112关于音频总线的时钟信号,例如,对于i2s而言,通过时钟管理模块111可以配置mclk/lrck/sck三个时钟信号的频率,有利于适应不同算法场景。

24.在一个实施场景中,音频总线可以包括但不限于i2s(inter-ic sound,集成电路内置音频总线)等,在此不做限定。需要说明的是,标准i2s总线电缆由3根串行导线组成,其中一根为时分多路复用数据线,另一根是字选择线,最后一根是时钟线。i2s总线接口可以作为一个编码解码接口与外部16/20/24位的立体声音频编解码电路(codec ic)相连。其可以支持i2s数据格式和msb-justified数据格式。i2s总线解耦为先进先出队列的访问提供dma(direct memory access,直接存储器访问)传输模式来取代中断模式,可以同时发送和接收数据,也可以只发送或接收数据。

25.在一个实施场景中,数据接口122可以包括但不限于axi-hp接口等,在此不做限定。此外,第一配置接口123可以包括但不限于axi-lite接口等,在此不做限定。

26.在一个实施场景中,传输总线12还可以包括第二配置接口124,数据收发模组11还包括信号分路模块113,信号分路模块113包括信号汇集端b1和多个信号分路端b2,信号汇集端b1与第二配置接口124连接,多个信号分路端b2分别连接至不同音频收发模块112,以配置各个音频收发模块112的语音参数。需要说明的是,信号分路模块113具体用于主控模组13发送给音频收发模块112的相关信号分为多路,以使各个音频收发模块112均可以接收到该信号。此外,语音参数的具体含义,可以参阅下述音频收发方法实施例中相关描述,在此暂不赘述。故此,通过第二配置接口124以及信号分路模块113,能够配置各个音频收发模块112的语音参数,有利于适应于不同算法场景。

27.在一个实施场景中,数据收发模组11还包括数据调度模块114,数据调度模块114包括数据汇集端c1和多个数据分路端c2,数据汇集端c1与数据接口122连接,多个数据分路端c2分别连接至不同音频收发模块112,以调度各个音频收发模块112的数据收发操作。具体而言,数据调度模块114所包含的数据分路端c2的数量可以等于音频收发模块112的数量,也可以多于音频收发模块112的数量。

28.在一个实施场景中,数据接口122还耦接于主控模组13的中断接口131,多个音频收发模块112均完成数据传输之后,数据接口122处产生中断信号,以通过中断接口131通知主控模组13执行数据处理操作。具体可以参阅下述音频收发方法实施例中相关描述,在此暂不赘述。

29.在一个实施场景中,音频收发电路10还包括易失性存储介质14,易失性存储介质14与传输总线12连接。此外,音频收发模块112在收取第一音频数据时,通过数据接口122将第一音频数据缓存至易失性存储介质14,主控模组13从易失性存储介质14取走第一音频数据。不同于音频接收过程,在音频发送过程中,主控模组13在发出第二音频数据时,通过主控接口121将第二音频数据缓存于易失性存储介质14,音频收发模块112通过数据接口122

从易失性存储介质14取走并发出第二音频数据。

30.在一个具体的实施场景中,易失性存储介质14可以包括但不限于ddr(double data rate,双倍数据速率)等,如ddr3、ddr4等等,在此不做限定。

31.在一个具体的实施场景中,各个音频收发模块112分别设有不同序位,以音频收发电路10包含16个音频收发模块112为例,第1个音频收发模块112其序位可以标记为0,第2个音频收发模块112其序位可以标记为1,以此类推,在此不再一一举例。在此基础上,可以分别设有各个音频收发模块112在易失性存储介质14中的存储地址,而存储地址是基于基地址、地址偏移以及音频收发模块112的序位所确定的,且地址偏移与音频收发模块112所配置的语音参数相关。需要说明的是,上述存储空间可以是连续的,且可以循环使用。示例性地,以采样时间4ms、采样频率16khz、语音深度16bit为例,每路语音数据的大小是128字节,则可以确定每路语音数据之间的地址偏移为128。在此基础上,第1个音频收发模块112对应的存储空间的偏移地址为0~127,第2个音频收发模块112对应的存储空间的偏移地址为128~255,以此类推,第n个音频收发模块112对应的存储空间的偏移地址为128*(n-1)~128*n-1。请结合参阅图2,图2是易失性存储介质14的存储空间示意图。如图2所示,当前语音被取走之后,可以再次通过上述步骤,将下一组语音存入到非易失性存储介质14中,以循环复用。

32.在一个实施场景中,请结合参阅图3,图3是音频收发模块112一实施例的框架示意图。如图2所示,音频收发模块112包括时钟产生单元1121、串并转换单元1122和并串转换单元1123。进一步地,时钟产生单元1121包括时钟输入端d1和时钟输出端d2,时钟输入端d1与时钟管理模块111的输出端a2连接,串并转换单元1122包括第一输入端e1、第一输出端e2和第一时钟配置端e3,第一输入端e1用于耦接至拾音电路,第一输出端e2耦接至数据接口122,且第一时钟配置端e3与时钟输出端d2连接,并串转换单元1123包括第二输入端f1、第二输出端f2和第二时钟配置端f3,第二输出端f2用于耦接至扬声电路,第二输入端f1耦接至数据接口122,且第二时钟配置端f3与时钟输出端d2连接。

33.在一个具体的实施场景中,如图3所示,音频收发模块112还可以包括数据重组单元1124、乒乓缓存单元1125、数据分发单元1126和数据缓存单元1127。在主控模组13通过传输总线12将数据收发模组11初始化完成之后,数据收发模组11中各个音频收发模块112可根据设定的音频参数,执行录音和播音操作。具体过程,可以参阅下述相关描述。

34.在一个具体的实施场景中,录音时,串并转换单元1122将接收到的串行数据组合成16bit~24bit的并行数据,并通过数据重组单元1124将并行数据分成左右声道数据,以及缓存至后端的乒乓缓存单元1125,待乒乓缓存单元1125中数据量达到预设阈值(如,64)时,向数据调度模块114发送请求,数据调度模块114可以根据是否已有其他音频收发模块112在等待以及当前音频收发模块112的排队序号,将乒乓缓存单元1125中数据调度至数据接口122的写端口,以待缓存至易失性存储介质14。进一步地,在所有音频收发模块112的语音数据均传输完成之后,可以产生中断信号,并通过中断接口131通知主控模组13执行数据处理操作。在此情况下,主控模组13可以从易失性存储介质14中取走音频数据,并进行诸如声源定位、去混响、语音增强、盲源分离等下一步处理,在此不做限定。

35.在一个具体的实施场景中,播音时,主控模组13将待播音数据写入到非易失性存储介质14中,并通知数据收发模组11取数据,多个音频收发模块112通过数据接口122从非

易失性存储介质14读取数据,并将数据写入到数据缓存单元1127中,并进一步通过数据分发单元1126判断出数据缓存单元1127非空,以及将读出数据分为左右两个声道,传递至并串转换单元1123,将其转换为串行数据流输出,完成播音操作。

36.在一个实施场景中,时钟管理模块111还包括输入端a3,用于与外部晶振连接。

37.在一个实施场景中,数据收发模组11为ip核(即知识产权核),从而可以授权使用。

38.在一个实施场景中,音频收发电路10由可编程化系统单芯片(programmable system on chip,psoc)实现,且数据收发模组11由可编程化系统单芯片的可编程逻辑(programmable logic,pl)部分实现,主控模组13由可编程化系统单芯片的处理系统(processing system,ps)部分实现,传输总线12由可编程化系统单芯片的片内总线实现。示例性地,片内总线可以包括但不限于axi等,在此不做限定。故此,通过ps侧高端处理器(如,双核arm cortex a9内核),能够支持复杂语音处理算法,如语音识别、合成、增强以及多成员对话的数据交换,有利于提升通用性和灵活性。此外,由于psoc平台通常具有丰富的接口,如网口、usb(universal serial bus,通用串行总线)、串口、can(即controller area network)、pcie(peripheral component interconnect express,高速串行计算机扩展总线标准)、srio(即serial rapid i/o)等,故能够应用于不同场景,即可以作为插卡,也可作为专用功能的独立板卡存在。

39.在一个具体的实施场景中,音频收发电路10具体可以基于诸如xilinx核心板而实现,其尺寸不超过40mm*35mm,可以实现5个16路i2s ip核功能,且该核心板的硬件成本较低,故有利于降低硬件成本,同时降低硬件尺寸,以及硬件功耗。

40.在一个具体的实施场景中,上述ip核还可以在任意fpga(field programmable gate array,现场可编程逻辑门阵列)实现,或者,还可以作为专用的硬核流片嵌入到通用处理器中。

41.在一个实施场景中,音频收发电路10还可以包括音频降噪模块(未图示),用于对拾取的音频数据先进行降噪处理,并在降噪处理之后,由音频收发模块112继续通过数据调度模块114、数据接口122传输至易失性存储介质14。

42.上述方案,音频收发电路10包括数据收发模组11、传输总线12和主控模组13,数据收发模组11包括时钟管理模块111和并行设置的多个音频收发模块112,音频收发模块112用于通过音频总线耦接至拾音电路和/或扬声电路,时钟管理模块111的输出端a1连接至各个音频收发模块112,以同步各个音频收发模块112的时钟参数,传输总线12包括主控接口121、数据接口122和第一配置接口123,多个音频收发模块112均耦接至数据接口122,且时钟管理模块111的配置端a2连接至第一配置接口123,主控模组13连接至主控接口121,以通过主控接口121实现与数据收发模组11之间的数据互通,一方面通过传输总线12的主控接口121和数据接口122,能够有利于实现多个音频收发模块112统一的数据收发调度,另一方面通过传输总线12的主控接口121和第一配置接口123,能够同步各个音频收发模块112的时钟参数,故能够实现所有通道数据同步且对齐。

43.请参阅图4,图4是本技术多媒体设备40一实施例的框架示意图。多媒体设备40包括:拾音电路41、扬声电路42以及上述任一公开实施例中的音频收发电路43,且拾音电路41、扬声电路42通过音频总线(如,i2s)耦接至音频收发电路43。此外,多媒体设备40可以包括多个(如,2个、3个、4个、5个等)拾音电路41;多媒体设备40也可以包括多个(如,2个、3个、

4个、5个等)扬声电路42。拾音电路41可以包括但不限于:全指向麦克风、单指向麦克风等,在此不做限定。扬声电路42可以包括但不限于高保真扬声器等,在此不做限定。需要说明的是,多媒体设备40可以包括但不限于:飞机话务设备、会议对话设备等,在此不做限定。

44.上述方案,多媒体设备40包括拾音电路41、扬声电路42以及上述任一公开实施例中的音频收发电路43,故能够实现所有通道数据同步且对齐,有利于提升语音对话质量。

45.请参阅图5,图5是本技术音频收发方法一实施例的流程示意图。本公开实施例具体应用于上述任一公开实施例中的音频收发电路,具体可以结合参阅前述公开实施例中相关描述,在此不再赘述。具体而言,本公开实施例可以包括如下步骤:

46.步骤s51:主控模组通过传输总线同步各个音频收发模块的时钟参数。

47.在一个实施场景中,在音频收发电路上电之后,即可执行初始化操作,此时,主控模组可以通过主控接口,透过传输总线从其第一配置接口向时钟管理模块发送音频收发模块的时钟参数,时钟管理模块在接收到时钟参数之后,即可将各个音频收发模块进行同步。

48.在一个具体的实施场景中,时钟参数可以包括但不限于分频系数clk_div等,在此不做限定。以时钟参数包括分频系数为例,根据分频系数clk_div,即可将外部时钟的频率进行分频,并将分频之后的频率作为音频收发模块的时钟频率。其他情况可以以此类推,在此不再一一举例。

49.在一个实施场景中,除了同步时钟参数之外,主控模组还可以基于音频收发任务,通过传输总线配置各个音频收发模块的语音参数,且在音频收发任务为音频收取任务的情况下,语音参数包括第一参数,在音频收发任务为音频发出任务的情况下,语音参数包括第二参数,且第一参数与第二参数不完全相同。上述方式,基于音频收发任务来配置音频收发模块的语音参数,且音频收取任务下的第一参数和音频发出任务下的第二参数不完全相同,故能够根据具体任务自定义地配置语音参数,有利于提升语音参数的准确性和灵活性。

50.在一个具体的实施场景中,第一参数包括以下至少一者:输入通道选择参数(reg_aud_in_chn_sel)、输入通道有效个数(valid_chn_in_num)、输入数据长度(aud_in_data_size)、采样频率(sample_freq)等,在此不做限定。需要说明的是,输入通道选择参数表示选择哪几个音频收发模块来拾取音频,输入通道有效个数表示有效拾取音频的音频收发模块的个数,输入数据长度表示一个数据的采样点个数(如,64、256等),采样频率表示音频采样频率(如,16khz等)。上述方式,通过配置第一参数包括以下至少一者:输入通道选择参数、输入通道有效个数、输入数据长度、采样频率,能够有利于提升音频收发模块的配置灵活性。

51.在一个具体的实施场景中,第二参数包括以下至少一者:输出通道选择参数(aud_out_chn_sel)、输出数据长度(aud_out_data_size)、传输总线许可状态(aud_out_xfen)。需要说明的是,输出数据长度和输出通道选择参数的含义可以分别参考前述输入数据长度和输入通道选择参数的含义,在此不再赘述。此外,传输总线许可状态表示当前传输总线是否处于被许可使用的状态。上述方式,通过配置第二参数包括以下至少一者:输出通道选择参数、输出数据长度、传输总线许可状态,能够有利于提升音频收发模块的配置灵活性。

52.在一个实施场景中,在初始化之后,主控模组还可以配置拾取到的音频数据是否需先进行降噪处理,若需先进行降噪处理,可以由音频手收发电路的音频降噪模块对拾取到的音频数据进行降噪,具体可以参阅前述公开实施例中相关描述,在此不再赘述。

53.步骤s52:基于音频收发任务,通过传输总线获取各个音频收发模块收取的第一音频数据,和/或,准备第二音频数据,由各个音频收发模块通过传输总线取走并发出第二音频数据。

54.在一个实施场景中,在音频收发任务为音频收取任务的情况下,可以判断在中断接口处是否检测到中断信号,若未检测到,则重新执行上述判断在中断接口处是否检测到中断信号的步骤,直至在中断接口处检测到中断信号为止,反之,若检测到,则可以确定各个音频收发模块均已通过传输总线,将第一音频数据缓存至非易失性存储介质,并通过传输总线从非易失性存储介质取走第一音频数据,以及重新执行判断在中断接口处是否检测到中断信号的步骤以及后续步骤。需要说明的是,第一音频数据是基于音频收发模块的拾取音频经串并转换、数据重组等操作而得到的音频数据,具体可以参阅前述关于音频收发模块的相关描述,在此不再赘述。上述方式,在音频收发任务为音频收取任务的情况下,通过检测中断接口处是否检测到中断信号来确定是否第一音频数据均已经通过传输总线传输至易失性存储介质,有利于提升音频收取的鲁棒性以及有序性,提升音频收取效率。

55.在一个实施场景中,在音频收发任务为音频发出任务的情况下,可以通过传输总线将第二音频数据缓存至易失性存储介质,并将准备完成字段设置为第一数值,且各个音频收发模块在检测到准备完成字段为第一数值(如,1)的情况下,通过传输总线从易失性存储介质取走并发出第二音频数据,并重置准备完成字段为第二数值(如,0)。需要说明的是,在音频发出过程中,主控模组一旦检测到准备完成字段被重置为第二数值,即可以再次通过传输总线将新的第二音频数据缓存至易失性存储介质,并将准备完成字段重新置为第一数值,以使音频收发模块能够不断从易失性存储介质取走第二音频数据。上述方式,在音频收发任务为音频发出任务的情况下,通过将传输总线将第二音频数据缓存至易失性存储介质,并将准备完成字段设置为第一数值,且各个音频收发模块在检测到准备完成字段为第一数值的情况下,通过传输总线从易失性存储介质取走并发出第二音频数据,并重置准备完成字段为第二数值,有利于提升音频发出的鲁棒性以及有序性,提升音频发出效率。

56.需要说明的是,在现实场景中,音频收发任务可以为音频收取任务、音频发出任务中任一者,当然,音频收发任务也可以同时包括音频收取任务和音频发出任务,在此不做限定。

57.上述方案,主控模组通过传输总线同步各个音频收发模块的时钟参数,并基于音频收发任务,通过传输总线获取各个音频收发模块收取的第一音频数据,和/或,准备第二音频数据,由各个音频收发模块通过传输总线取走并发出第二音频数据,能够实现所有通道数据同步且对齐。

58.请参阅图6,图6是本技术音频收发装置60一实施例的框架示意图。音频收发装置60集成于前述任一公开实施例中的音频收发电路,具体可以参阅前述公开实施例中相关描述,在此不再赘述。音频收发装置60包括:时钟同步模块61和数据传输模块62,时钟同步模块61,用于驱使主控模组通过传输总线同步各个音频收发模块的时钟参数;数据传输模块62,用于驱使主控模组基于音频收发任务,通过传输总线获取各个音频收发模块收取的第一音频数据,和/或,准备第二音频数据,由各个音频收发模块通过传输总线取走并发出第二音频数据。

59.上述方案,主控模组通过传输总线同步各个音频收发模块的时钟参数,并基于音

频收发任务,通过传输总线获取各个音频收发模块收取的第一音频数据,和/或,准备第二音频数据,由各个音频收发模块通过传输总线取走并发出第二音频数据,能够实现所有通道数据同步且对齐。

60.在一些公开实施例中,音频收发装置60包括参数配置模块,用于基于音频收发任务,通过传输总线配置各个音频收发模块的语音参数;其中,在音频收发任务为音频收取任务的情况下,语音参数包括第一参数,在音频收发任务为音频发出任务的情况下,语音参数包括第二参数,且第一参数和第二参数不完全相同。

61.因此,基于音频收发任务来配置音频收发模块的语音参数,且音频收取任务下的第一参数和音频发出任务下的第二参数不完全相同,故能够根据具体任务自定义地配置语音参数,有利于提升语音参数的准确性和灵活性。

62.在一些公开实施例中,第一参数包括以下至少一者:输入通道选择参数、输入通道有效个数、输入数据长度、采样频率,和/或,第二参数包括以下至少一者:输出通道选择参数、输出数据长度、传输总线许可状态。

63.因此,通过配置第一参数包括以下至少一者:输入通道选择参数、输入通道有效个数、输入数据长度、采样频率,能够有利于提升音频收发模块的配置灵活性,而通过配置第二参数包括以下至少一者:输出通道选择参数、输出数据长度、传输总线许可状态,能够有利于提升音频收发模块的配置灵活性。

64.在一些公开实施例中,数据传输模块62包括音频收取子模块,具体用于通过传输总线获取各个音频收发模块收取的第一音频数据,音频收取子模块包括判断单元,用于判断在中断接口处是否检测到中断信号;音频收取子模块包括第一循环单元,用于在未检测到中断信号的情况下,结合判断单元重新执行判断在中断接口处是否检测到中断信号的步骤,音频收取子模块读取单元和第二循环单元,读取单元用于在检测到中断信号的情况下,确定各个音频收发模块均已通过传输总线,将第一音频数据缓存至非易失性存储介质,并通过传输总线从非易失性存储介质取走第一音频数据,第二循环单元用于结合判断单元、第一循环单元、读取单元重新执行判断在中断接口处是否检测到中断信号的步骤以及后续步骤。

65.因此,在音频收发任务为音频收取任务的情况下,通过检测中断接口处是否检测到中断信号来确定是否第一音频数据均已经通过传输总线传输至易失性存储介质,有利于提升音频收取的鲁棒性以及有序性,提升音频收取效率。

66.在一些公开实施例中,数据传输模块62包括音频发出子模块,具体用于准备第二音频数据,由各个音频收发模块通过传输总线取走并发出第二音频数据,音频发出子模块包括缓存单元,用于通过传输总线将第二音频数据缓存至易失性存储介质;音频发出子模块包括设置单元,用于将准备完成字段设置为第一数值;其中,各个音频收发模块在检测到准备完成字段为第一数值的情况下,通过传输总线从易失性存储介质取走并发出第二音频数据,并重置准备完成字段为第二数值。

67.因此,在音频收发任务为音频发出任务的情况下,通过将传输总线将第二音频数据缓存至易失性存储介质,并将准备完成字段设置为第一数值,且各个音频收发模块在检测到准备完成字段为第一数值的情况下,通过传输总线从易失性存储介质取走并发出第二音频数据,并重置准备完成字段为第二数值,有利于提升音频发出的鲁棒性以及有序性,提

升音频发出效率。

68.请参阅图7,图7是本技术计算机可读存储介质70一实施例的框架示意图。计算机可读存储介质70存储有能够被处理器运行的程序指令71,程序指令71用于实现上述任一音频收发方法实施例中的步骤。

69.上述方案,一方面通过传输总线的主控接口和数据接口,能够有利于实现多个音频收发模块统一的数据收发调度,另一方面通过传输总线的主控接口和第一配置接口,能够同步各个音频收发模块的时钟参数,故能够实现所有通道数据同步且对齐。

70.在一些实施例中,本公开实施例提供的装置具有的功能或包含的模块可以用于执行上文方法实施例描述的方法,其具体实现可以参照上文方法实施例的描述,为了简洁,这里不再赘述。

71.上文对各个实施例的描述倾向于强调各个实施例之间的不同之处,其相同或相似之处可以互相参考,为了简洁,本文不再赘述。

72.在本技术所提供的几个实施例中,应该理解到,所揭露的方法和装置,可以通过其它的方式实现。例如,以上所描述的装置实施方式仅仅是示意性的,例如,模块或单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性、机械或其它的形式。

73.作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施方式方案的目的。

74.另外,在本技术各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

75.集成的单元如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)或处理器(processor)执行本技术各个实施方式方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、磁碟或者光盘等各种可以存储程序代码的介质。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1