一种基于四象限探测器的信号处理装置的制作方法

1.本实用新型涉及光电探测技术领域,尤其涉及一种基于四象限探测器的信号处理装置。

背景技术:

2.四象限探测器广泛用于激光制导、激光告警和激光测角等领域。为了更准备地获得四象限光电信息,信号处理装置的设置非常关键。

3.现有基于四象限探测器的信号处理装置普遍采用分立元器件,集成度低,易受干扰,且动态响应范围有限,探测器采集灵敏度低,采样速率低,实时性差。

技术实现要素:

4.鉴于上述的分析,本实用新型旨在提供一种基于四象限探测器的信号处理装置,用以解决现有技术集成度差、动态响应范围受限、灵敏度低、采样速率低的问题。

5.本实用新型的目的主要是通过以下技术方案实现的:

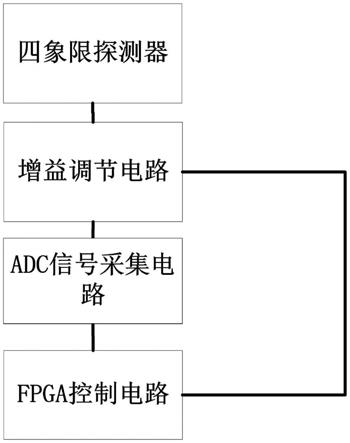

6.一种基于四象限探测器的信号处理装置,包括四象限探测器、增益调节电路、adc信号采集电路、fpga控制电路;其中,

7.所述增益调节电路为2路或4路,且结构相同;四象限探测器的4 个输出端分别经一路增益调节电路与adc信号采集电路的相应输入端连接;adc信号采集电路的输出端与fpga控制电路的输入端连接,fpga 控制电路的输出端与每路增益调节电路的控制端连接。

8.上述方案的有益效果如下:通过增益调节电路的增益控制,四象限探测器的动态响应范围可达到102db,有效地提高了现有四象限探测器的信号响应范围,克服了探测器灵敏度低的问题。通过高速的adc信号采集电路和高速的fpga控制电路,解决了现有四象限探测器采样速率过低的问题。由于fpag控制电路端的数字信号处理及控制具有很强的抗干扰能力,解决现有四象限探测器后向散射的问题。

9.基于上述方案的进一步改进,每一所述增益调节电路均包括参数相同的主放电路;

10.所述主放电路包括:线性可变增益运算放大器,以及相应的外围电路一。

11.上述进一步改进方案的有益效果是:对增益调节电路的结构进行了限定,主放电路的主要功能是将四象限探测器输出的微弱的单端信号转化为可检测的差分信号。设置主放电路,能够有效提高四象限探测器检测信号的灵敏度。

12.进一步,每一所述增益调节电路还包括设置于主放电路之前且参数相同的主衰电路;四象限探测器经所述主衰电路与主放电路连接;四象限探测器经所述主衰电路与主放电路连接;

13.所述主衰电路包括:cmos模拟开关,以及相应的外围电路二。

14.上述进一步改进方案的有益效果是:对增益调节电路的结构进行了进一步限定,除了主放电路还包括主衰电路。主衰电路通过cmos模拟开关器件的开通,启动分压,达到衰

接电源二;vps2引脚经电感l7接电源二,并经电容c

44

接地;vps3引脚经电感l8接电源二,并经电容c

45

接地;vps4引脚经电容c

15

接地,并经电感l4接电源二;gain12引脚经电容c6接地,gain34引脚经电容c

16

接地,并且,gain12、gain34引脚作为主放电路的控制端接fpga控制电路; clmp12引脚经电容c7接地;clmp34引脚经电容c

17

接地;hil0引脚接地;en12引脚与en34引脚连接,并接电源二;vcm1引脚经电容c8接地,vcm2引脚经电容c9接地,vcm3引脚经电容c

19

接地,vcm4 引脚经电容c

18

接地,并且,vcm1~vcm4引脚连接;com3x引脚、 com12引脚、mode引脚、com34引脚接地;vps34引脚经电容c

35

接地,并经电感l6接电源二;npsv2引脚经电容c

28

接地,并经电感l5接电源二;voh1引脚依次经电容c

25

、电阻r9后输出,作为主衰电路中与所述输入端一对应的差分输出一的一端;vol1引脚依次经电容c

26

、电阻r

10

后输出,作为所述差分输出一的另一端;差分输出一的一端与另一端之间接电容c

27

;voh2引脚依次经电容c

30

、电阻r

12

后输出,作为主衰电路中与所述输入端二对应的差分输出二的一端;vol2引脚依次经电容c

29

、电阻r

11

后输出,作为所述差分输出二的另一端;差分输出二的一端与另一端之间接电容c

31

;voh3引脚经电容c

32

、电阻r

13

后输出,作为主衰电路中与所述输入端三对应的差分输出三的一端;vol3引脚经电容c

33

、电阻r

14

后输出,作为所述差分输出三的另一端;差分输出三的一端与另一端之间之间接电容c

34

;voh4引脚依次经电容c

37

、电阻 r

16

后输出,作为主衰电路中与所述输入端四对应的差分输出四的一端; vol4引脚依次经电容c

36

、电阻r

15

后输出,作为所述差分输出四的另一端;差分输出四的一端与另一端之间之间接电容c

38

。

24.上述进一步改进方案的有益效果是:通过ad8334型号四通道线性可变增益运算放大器的使用,使得理论上的四路主放电路共用一个可变增益运算放大器,减少了器件,大大提高了电路的集成度,缩减了制造成本。ad8334型号四通道线性可变增益运算放大器可将四象限探测器输出的微弱信号放大成adc信号采集电路可检测的信号。

25.进一步,所述adc信号采集电路包括:ads58c48x芯片,以及相应的外围电路三。

26.上述进一步改进方案的有益效果是:通过一个ads58c48x芯片可对主放电路的四个输出通道进行采样,减少了器件,大大提高了电路的集成度,缩减了制造成本。该芯片的采样速率最高能达到200mhz,以保证提供给fpga控制电路信号的实时性。

27.进一步,所述外围电路三包括电阻r

19

~r

23

、电容c

51

、电源三;其中,

28.ads58c48x芯片的drvdd、avdd引脚接电源三,sdout、sclk、 sdata、sen为spi管脚,与fpga控制电路连接;ina_p与主放电路中差分输出一的一端连接,ina_m与主放电路中差分输出一的另一端连接,inb_p与主放电路中差分输出二的一端连接,inb_m与主放电路中差分输出二的另一端连接,inc_p与主放电路中差分输出三的一端连接; inc_m与主放电路中差分输出三的另一端连接;ind_p与主放电路中差分输出四的一端连接ind_m引脚与主放电路中差分输出四的另一端连接;clkout_p引脚经电阻r

22

与fpga控制电路连接;clkout_m引脚经电阻r

23

与fpga控制电路连接;snrb_1、snrb_2引脚接地;cm 引脚经电阻r

19

分别与ad8334型号可变增益运算放大器的 vcm1~vcm4引脚连接,并经电容c51接地;clkp引脚经电阻r

21

与 fpga控制电路连接;clkp引脚经电阻r

20

与fpga控制电路连接;cha、 chb、chc、chd引脚分别为四路11位数字信号输出端,输出至fpga 控制电路。

29.上述进一步改进方案的有益效果是:电路设计简单,集成度高。

30.进一步,所述fpga控制电路包括fpga芯片、计时模块、存储芯片;其中,

31.adc信号采集电路的输出端与fpga芯片的输入端连接;fpga芯片的数据端与存储芯片连接,输出端分别与主衰电路、主放电路、adc 信号采集电路的对应控制端连接。

32.上述进一步改进方案的有益效果是:计时模块为fpga芯片提供采样时钟,ads58c48芯片正常工作后,在激光未到来时,采集1024组四个通道(四路11位数字信号输出端)输出电压的均值作为门限阈值。当激光脉冲到来时,将采集到的激光信号电压与门限阈值比较。大于门限阈值的时间即为激光脉冲的时间,若大于门限阈值,将四个通道采集的最大电压值通过emif总线输出给主机。

33.进一步,该信号处理装置还包括dac电路;fpga芯片通过所述 dac电路与adc采集电路连接;

34.所述dac电路进一步包括max5531转换芯片、电源四、电阻r

24

、电容c

52

;其中,

35.max5531转换芯片的cs、sclk、din作为输入管脚,与fpga芯片的输出端连接;gnd引脚接地;vdd引脚接电源四;outa引脚经电容c

52

接地,并经电阻r

24

与ad8334型号可变增益运算放大器的gain12、 gain34引脚连接。

36.上述进一步改进方案的有益效果是:dac电路采用max5531作为转换芯片,通过fpga芯片对spistea、spiclka、spisimoa管脚写入数据,通过outa管脚输出相应电压,该电压提供给ad8334的agc 管脚,作为agc电压型号四通道线性可变增益运算放大器。

37.本实用新型中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本实用新型的其他特征和优点将在随后的内容中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本实用新型而了解。本实用新型的目的和其他优点可通过文字以及附图中所特别指出的内容中来实现和获得。

附图说明

38.附图仅用于示出具体实施例的目的,而并不认为是对本实用新型的限制,在整个附图中,相同的参考符号表示相同的部件。

39.图1为本发明实施例1基于四象限探测器的信号处理装置组成示意图;

40.图2为本发明实施例2主衰电路结构示意图;

41.图3为本发明实施例2主放电路结构示意图;

42.图4为本发明实施例2adc信号采集电路结构示意图;

43.图5为本发明实施例2fpga控制电路结构示意图;

44.图6为本发明实施例2dac电路结构示意图。

45.附图标记:

46.ax、bx

‑

主衰电路的两路输入;

47.axfd、bxfd、cxfd、dxfd

‑

主衰电路的四路输出,或主放电路的四路输入;

48.zk、zk/

‑

主衰电路的控制端,zk/接入zk的反电平;

49.inpa、inpma,inpb、inpmb,inpc、inpmc,inpd、inpmd

‑

主放电路的四路差分输出,或adc信号采集电路的四路差分输入;

50.cm

‑

主放电路的公共端;

51.agc

‑

主放电路的增益控制端;

52.cha、chb、chc、chd

‑

adc信号采集电路的四路11位数字信号输出端;

53.clockoutp、clockoutm、clkinm、clkinp

‑

adc信号采集电路的四个时钟输入端;

54.spistea、spiclka、spisimoa

‑

dac电路的输入信号。

具体实施方式

55.下面结合附图来具体描述本实用新型的优选实施例,其中,附图构成本技术一部分,并与本实用新型的实施例一起用于阐释本实用新型的原理,并非用于限定本实用新型的范围。

56.实施例1

57.本实用新型的一个具体实施例,公开了一种基于四象限探测器的信号处理装置,如图1所示,包括四象限探测器、增益调节电路、adc信号采集电路、fpga控制电路。

58.其中,所述增益调节电路为2路或4路,且结构相同;四象限探测器的4个输出端分别经一路增益调节电路与adc信号采集电路的相应输入端连接;adc信号采集电路的输出端与fpga控制电路的输入端连接, fpga控制电路的输出端与每路增益调节电路的控制端连接。

59.四象限探测器,用于获得4个象限上的光电信号。比较4个光电信号的幅度大小可以获得目标的方位。

60.增益调节电路,用于对上述光电信号的增益进行调节,并将四象限探测器输出每路微弱的单个信号转换为可检测的差分信号。

61.adc信号采集电路,用于将所述差分信号转换为数字信号。

62.fpga控制电路,用于在每个时钟周期获取adc信号采集电路输出的数字信号,将所述数值信号的均值与门限阈值比较,如果大于门限阈值,控制增益调节电路对其输入的光电信号进行衰减,以排除后向散射或者杂光干扰,如果小于门限阈值,将数字信号传输至主机。

63.与现有技术相比,本实施例提供的装置通过增益调节电路的增益控制,四象限探测器的动态响应范围可达到102db,有效地提高了现有四象限探测器的信号响应范围,克服了探测器灵敏度低的问题。通过高速的adc信号采集电路和高速的fpga控制电路,解决了现有四象限探测器采样速率过低的问题。由于fpag控制电路端的数字信号处理及控制具有很强的抗干扰能力,解决现有四象限探测器后向散射的问题。

64.实施例2

65.在实施例1的基础上进行优化,四象限探测器选用光敏面直径10mm 的p型激光探测器,具有高灵敏度特征。

66.该器件内部集成前置放大电路,可以减少外围设计,同时有效地提高了信噪比。探测器具有三级增益衰减功能,第一级增益衰减起控后信号链路衰减25db,第二级增益衰减起控后信号链路衰减23db,第三级增益衰减起控后信号链路衰减15db。探测器的增益衰减启动由fpga控制电路控制。四象限探测器收到激光信号后,分别将四个通道的光信号转换为四路电信号,经过探测器内四路前置放大电路后,将四路信号输出给增益调节电路(具体为后面的主衰电路)。

67.优选地,每一所述增益调节电路包括依次连接的主衰电路、主放电路。主衰电路中将四象限探测器四路输出电压衰减,主放电路是对主衰电路衰减后电压信号增益进行调

节。主衰电路和主放电路的配合使用可以提高系统的动态响应范围。

68.所有主衰电路的参数相同,所有主放电路的参数也相同。

69.当采用两路增益调节电路时,每路的主衰电路包括:adg1411a型号四通道cmos模拟开关、电阻r1~r6、电源一、电感l1~l2、电容c1~c4。主衰衰减倍数可设置为14db。如图2所示。

70.adg1411a型号四通道cmos模拟开关的a1~a4引脚作为控制端,与fpga控制电路连接;s1引脚经电阻r1接地;s2引脚经电阻r2接地; d1引脚与s4引脚连接,并经电阻r3与四象限探测器的第二象限输出端连接(图2中bx);s4引脚还经电阻r5分别接d4引脚、电容c1的一端;电容c1的另一端作为主衰电路的输出端二(图2中bxfd),与主放电路的相应输入端连接;d2引脚与s3引脚连接,并经电阻r4接四象限探测器的第一象限输出端连接(图2中的ax);s3引脚还经电阻r6分别与d3引脚、电容c2的一端连接;电容c2的另一端作为主衰电路的输出端一(图2中axfd),与主放电路的相应输入端连接;vdd引脚经电容c3接地,并经电感l1接电源一的正极;vss引脚经电容c4接地,并经电感l2接电源一的负极;gnd引脚接地。

71.两路增益调节电路的主放共用一个线性可变增益运算放大器。主放电路包括ad8334型号四通道超低噪声可变增益运算放大器、电阻 r7~r

18

、电源二、电感l3~l8、电容c5~c

50

。如图3所示。

72.ad8334型号四通道线性可变增益运算放大器的ep引脚悬空; com1~com4引脚连接,并接地;inh1引脚作为主衰电路的输入端一(图3中axfd),与电容c2的另一端连接,并经电容c

10

与电阻r7的一端、经电容c

11

与nc引脚连接;inh2引脚作为主衰电路的输入端二(图3 中bxfd),与电容c1的另一端连接,并经电容c

39

与电阻r17的一端、经电容c

40

与com2x引脚连接;inh3引脚作为主衰电路的输入端三(图 3中cxfd),经电容c

48

与电阻r

18

的一端连接,并经电容c

49

与com3x 引脚连接;inh4引脚作为主衰电路的输入端四(图3中dxfd),经电容c

21

与电阻r8的一端连接,并经电容c

20

与com4x引脚连接;lmd1 引脚经电容c

13

与nc引脚连接;lmd2引脚经电容c

41

与com2x引脚连接;lmd3引脚经电容c

50

与com3x引脚连接;lmd4引脚经电容c

22

与com4x引脚连接;nc、com2x、com3x、com4x引脚均接地; lon1引脚与电阻r7的另一端连接,并经电容c

12

与cin1引脚连接; lon2引脚与电阻r

17

的另一端连接,并经电容c

42

与vip2引脚连接; lon3引脚与电阻r

18

的另一端连接,并经电容c

46

与vin3引脚连接; lon4引脚与电阻r8的另一端连接,并经电容c

24

与vin4引脚连接;lop1 引脚经电容c

14

与vip1引脚连接;lop2引脚经电容c

43

与vin2引脚连接;lop3引脚经电容c

47

与vip3引脚连接;lop4引脚经电容c

23

与vip4 引脚连接;vps1引脚经电容c5接地,并经电感l3接电源二;vps2引脚经电感l7接电源二,并经电容c

44

接地;vps3引脚经电感l8接电源二,并经电容c

45

接地;vps4引脚经电容c

15

接地,并经电感l4接电源二;gain12引脚经电容c6接地,gain34引脚经电容c

16

接地,并且, gain12、gain34引脚作为主放电路的控制端(图3中agc)接fpga 控制电路;clmp12引脚经电容c7接地;clmp34引脚经电容c

17

接地; hil0引脚接地;en12引脚与en34引脚连接,并接电源二;vcm1引脚经电容c8接地,vcm2引脚经电容c9接地,vcm3引脚经电容c

19

接地, vcm4引脚经电容c

18

接地,并且,vcm1~vcm4引脚连接(图3中cm); com3x引脚、com12引脚、mode引脚、com34引脚接地;vps34 引脚经电容c

35

接地,并经电感l6接电源二;npsv2引脚经电容c

28

接地,并经电感l5接电源二;voh1引脚依次经电容c

25

、电阻r9后输出,作为主衰电路中与所述输入端一对应的差分输出一的一端(图3中 inpa);vol1引脚依次经电容c

26

、电阻r

10

后输

出,作为所述差分输出一的另一端(图3中inpma);差分输出一的一端与另一端之间接电容c

27

;voh2引脚依次经电容c

30

、电阻r

12

后输出,作为主衰电路中与所述输入端二对应的差分输出二的一端(图3中inpb);vol2引脚依次经电容c

29

、电阻r

11

后输出,作为所述差分输出二的另一端(图3中inpmb);差分输出二的一端与另一端之间接电容c

31

;voh3引脚经电容c

32

、电阻r

13

后输出,作为主衰电路中与所述输入端三对应的差分输出三的一端(图3中inpc);vol3引脚经电容c

33

、电阻r

14

后输出,作为所述差分输出三的另一端(图3中inpmc);差分输出三的一端与另一端之间之间接电容c

34

;voh4引脚依次经电容c

37

、电阻r

16

后输出,作为主衰电路中与所述输入端四对应的差分输出四的一端(图3中 inpd);vol4引脚依次经电容c

36

、电阻r

15

后输出,作为所述差分输出四的另一端(图3中inpmd);差分输出四的一端与另一端之间之间接电容c

38

。

73.ad8334型号四通道超低噪声可变增益运算放大器将四象限探测器输出的微弱信号放大成ad可检测的信号。图3中的inpa/inpma、 inpb/inpmb、inpc/inpmc、inpd/inpmd为经过运算放大后的差分输出管脚,agc引脚是增益控制管脚。

74.优选地,adc信号采集电路包括ads58c48x芯片、电阻r

19

~r

23

、电容c

51

、电源三,如图4所示。ads58c48芯片作为转换芯片,其采样通道为四通道,采样速率最高能达到200mhz,以保证提供给fpga信号的实时性。sdo、sclk、sdata、sen为spi管脚,在fpga上电后,发送串口信息以配置ads58c48的采样模式。inpa/inpma、 inpb/inpmb、inpc/inpmc、inpd/inpmd为差分模拟输入信号管脚。 cha、chb、chc、chd分别为四路11位数字信号输出。

75.ads58c48x芯片的drvdd、avdd引脚接电源三,sdout、sclk、 sdata、sen为spi管脚,与fpga控制电路连接;ina_p与主放电路中差分输出一的一端连接,ina_m与主放电路中差分输出一的另一端连接,inb_p与主放电路中差分输出二的一端连接,inb_m与主放电路中差分输出二的另一端连接,inc_p与主放电路中差分输出三的一端连接;inc_m与主放电路中差分输出三的另一端连接;ind_p与主放电路中差分输出四的一端连接ind_m引脚与主放电路中差分输出四的另一端连接;clkout_p引脚经电阻r

22

与fpga控制电路连接;clkout_m引脚经电阻r

23

与fpga控制电路连接;snrb_1、snrb_2引脚接地;cm 引脚经电阻r

19

分别与ad8334型号可变增益运算放大器的 vcm1~vcm4引脚连接,并经电容c51接地;clkp引脚经电阻r

21

与 fpga控制电路连接;clkp引脚经电阻r

20

与fpga控制电路连接;cha、 chb、chc、chd引脚分别为四路11位数字信号输出端,输出至fpga 控制电路。

76.优选地,fpga控制电路包括fpga芯片、计时模块、存储芯片,如图5所示。

77.adc信号采集电路的输出端与fpga芯片的输入端连接;fpga芯片的数据端与存储芯片连接,输出端分别与主衰电路、主放电路、adc 信号采集电路的对应控制端连接,以及与计时模块的输入端连接。

78.计时模块,用于为fpga芯片提供时钟。

79.优选地,该信号处理装置还包括dac电路。fpga芯片通过所述 dac电路与adc采集电路连接,如图6所示。

80.dac电路进一步包括max5531转换芯片、电源四、电阻r

24

、电容 c

52

。其中,max5531转换芯片的cs、sclk、din作为输入管脚,与 fpga芯片的输出端连接;gnd引脚接地;vdd引脚接电源四;outa 引脚经电容c

52

接地,并经电阻r

24

与ad8334型号可变增益运算放大器的gain12、gain34引脚连接。

81.ads58c48正常工作后,在激光未到来时,采集1024组四路输入电压的均值作为门限阈值。当激光脉冲到来时,将采集到的激光信号电压与门限阈值比较。大于门限阈值的时间即为激光脉冲的时间,大于门限阈值的最大电压值通过emif总线输出给fpga芯片进行后续运算。

82.实施时,四象限探测器输出的窄脉冲信号进入主衰电路,通过cmos 模拟开关器件的开通,打开分压电路,达到衰减信号的目的;再通过主放电路,主放电路采用超低噪声、四通道线性可变增益放大器ad8334 芯片完成,相比传统电路集成度更高,增益范围更大,主要功能是将四象限探测器出来的微弱的单端信号转化为可检测的差分信号;adc采集电路采用ads58c48芯片,相比传统电路集成度更高,采样速率更高,其主要功能是将差分信号转化为数字信号,并通过emif总线将数据传给fpga;dac电路将fpga控制电路发送的数字信号转化为模拟信号,实现调节agc电压的目的。fpga控制电路的主要功能是在每个时钟周期,采集adc采集电路输出的数据,并将均值处理过的数据与门限阈值进行比较,以排除后向散射或者杂光干扰;以及,将四象限的值进行解算,例如可得到偏差角度。

83.与实施例1相比,本实施例提供的装置采用超低噪声、增益可控的运放ad8334和具有snrboost功能的四通道11位高速模数转换器 ads58c48,能够在宽范围内能够检测出四象限信号探测器,并且保证四路信号具有一致性,同时满足高速信号采集的要求。

84.本领域技术人员可以理解,上述实施例中fpga所涉及的程序/软件为现有技术常见的方法,本实用新型不涉及任何软件方面的改进。本实用新型仅需要将各个具有相应功能的装置通过本实用新型实施例所给出的连接关系进行连接即可,其中并不涉及任何程序软件方面的改进。而至于各个相应功能的硬件装置之间的连接方式,均是本领域技术人员可以采用现有技术实现的,在此不做详细说明。

85.以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1