一种基于HDMI2.1协议8K音视频数据流多路分配器的制作方法

一种基于hdmi2.1协议8k音视频数据流多路分配器

技术领域

1.本实用新型属于8k音视频数据流传输技术领域,尤其涉及一种基于hdmi2.1协议8k音视频数据流多路分配器。

背景技术:

2.目前,adv7672是一款高清多媒体接口收发器,具有交叉点矩阵开关、视频镜像、视频分割和视频合并功能。adv7672支持40gbps固定速率链路(frl)和18gbps过渡最小化差分信号(tmds)视频速率,并提供两个独立的hdmi接收芯片端口、两个独立的hdmi变送器端口、两个音频端口和一个增强的音频返回通道(earc)接口。每个hdmi接收芯片和变送器都支持8k30 rgb/ycbcr 4:4:4、10位视频、8k60 ycbcr 4:2:0、10位高清视频和4k120 4:4:4、10位高帧率视频。每个音频端口都可以独立配置为音频提取端口或音频插入端口。音频端口支持8通道、192khz、24位脉冲编码调制(pcm)和压缩音频格式,包括高比特率格式。earc接口可以配置为earc变送器或earc接收器。earc接口支持8通道192khz pcm音频和高比特率音频(hbr)压缩音频格式,包括dolby truehd

tm

和dts

‑

hd

tm

。earc接口还支持音频返回通道(arc)。adv7672支持显示流压缩(dsc)1.2a数据直通和用于hdmi动态hdr、hdr10+和dolby vision

tm

的高动态范围(hdr)元数据直通。adv7672实施高带宽数字内容保护(hdcp)2.3规范,以保护优质内容的交付。hdcp 2.3适用于变送器、接收器和中继器配置。hdcp 2.3向后兼容hdcp 2.2。还支持hdcp 1.4,以提供与旧套件的互操作性。adv7672使用高级主机控制器接口(api),并通过i2c进行配置。adv7672采用108引脚、引线框架芯片级封装(lfcsp),带有裸露焊盘,额定温度范围为0℃至70℃。

3.随着人工智能技术的发展,特别是8k超高清视频产业链技术的快速成熟,大量的现代人工智能技术,被应用到了电子产品当中。其中,micro led技术应用使得户外led大屏,急需要8k超高清视频传输系统为解码器和led大屏架起一座高速桥梁,实现高速互联互通,呈现8k超高清音视频前所未有的体验效果。

4.现有专利(cn201621418626.5)公开了一种hdmi极清4k60hz多路分配器,包括一个分配器,分配器通过一条hdmi线缆把高清信号源和分配器的输入口连接起来,分配器的输出端与显示器之间通过hdmi线缆连接,12v的电源和分配器连接起;分配器包括一路hdmi输入模块、至少两路hdmi输出模块、一个hdmi音视频处理分配模块、一个电源模块以及一个mcu控制模块,hdmi输入模块、hdmi输出模块、hdmi音视频处理分配模块均与mcu控制模块连接,电源模块给整个分配器供电。上述现有专利采取hdmi音视频处理分配模块,通过将mcu控制模块实现将一路tmds信号分配成多路tmds信号在支持hdmi信号的显示设备或投影仪上显示,达到无信号衰减的效果;但是该现有设备结构复杂,制造成本高。

5.因此市场需要一种结构简单,采用hdmi2.1协议接收解码器输出的hdmi2.1协议的8k音视频数据流,再由adv7672做数据镜像复用处理,并输出2路hdmi2.1协议的8k音视频数据流,分别传送至下一级adv7672,同上原理由2路输入变成4路输出,通过上述方法处理后得到4路hdmi2.1协议的8k音视频数据流,满足户外led大屏视频信号接收端口需求,实现多

屏演播同放。

6.通过上述分析,现有技术存在的问题及缺陷为:现有设备结构复杂,制造成本高。

技术实现要素:

7.为了解决现有技术存在的问题,本实用新型提供了一种音视频数据流多路分配器。本实用新型音视频数据流多路分配器为一种基于hdmi2.1协议8k音视频数据流多路分配器,该分配器是基于hdmi2.1协议8k音视频数据流单路输入,复用8k音视频数据流后实现多路输出,处理实时动态视觉数据传输。

8.本实用新型是这样实现的,一种音视频数据流多路分配器,所述音视频数据流多路分配器设置有:

9.用以为各个adv7672芯片提供电源的电源系统;

10.通过adv7672芯片进行数据镜像处理的数据镜像复用处理模块。

11.进一步,所述第一adv7672芯片分别与第二adv7672芯片和第三adv7672芯片连接,第一adv7672芯片与hdmi2.1 8k音视频数据流输入端连接。

12.进一步,所述第一adv7672芯片、第二adv7672芯片和第三adv7672芯片为阶梯型分布。

13.进一步,所述第二adv7672芯片分别与第一输出端口和第二输出端口连接。

14.进一步,所述第三adv7672芯片分别与第三输出端口和第四输出端口连接。

15.进一步,所述电源系统分别通过导线与第一adv7672芯片、第二adv7672芯片和第三adv7672芯片连接。

16.结合上述的所有技术方案,本实用新型所具备的优点及积极效果为:

17.本实用新型采用hdmi2.1协议的8k音视频数据流由1路变成4路,且4流hdmi2.1协议的8k音视频数据流重现在4个大屏上,节目同步一致。

18.本实用新型采用hdmi2.1协议接收解码器输出的hdmi2.1协议的8k音视频数据流,再由adv7672做数据镜像复用处理,并输出2路hdmi2.1协议的8k音视频数据流,分别传送至下一级adv7672,同上原理由2路输入变成4路输出,通过上述处理后得到4路hdmi2.1协议的8k音视频数据流。

19.本实用新型能够满足户外led大屏视频信号接收端口需求,同时也丰富了市场多屏演播同一个视频节目的需求。

20.本实用新型实现了hdmi2.1协议传输8k音视频数据流从无到有,实现1路hdmi2.1协议传输8k音视频数据流输入,输出4路hdmi2.1协议传输8k音视频数据流,解决目前市场上还没有hdmi2.1协议传输8k多路分配器的问题。

附图说明

21.为了更清楚地说明本技术实施例的技术方案,下面将对本技术实施例中所需要使用的附图做简单的介绍,显而易见地,下面所描述的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下还可以根据这些附图获得其他的附图。

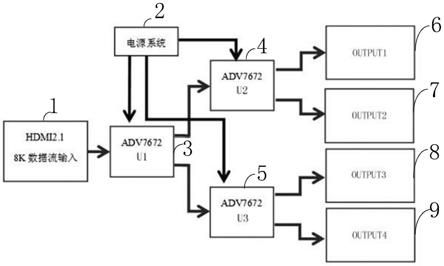

22.图1是本实用新型实施例提供的音视频数据流多路分配器结构示意图。

23.图中:1、hdmi2.1 8k音视频数据流输入端;2、电源系统;3、第一adv7672芯片;4、第二adv7672芯片;5、第三adv7672芯片;6、第一输出端口;7、第二输出端口;8、第三输出端口;9、第四输出端口。

24.图2是本实用新型实施例提供的三颗adv7672芯片u1、u2和u3实施例的连接方框图。

25.图3是本实用新型实施例提供的电源系统连接方框图。

26.图4是本实用新型实施例提供的五颗adv7672芯片u1、u2、u3、u4和u5实施例的连接方框图。

27.图5是本实用新型实施例提供的u1、u4、u6、u7连接结构电路示意图。

28.图6是本实用新型实施例提供的u28、u30、u26、u29、u22连接结构电路示意图。

29.图7是本实用新型实施例提供的hdmi input电路示意图。

30.图8是本实用新型实施例提供的hdmi input另一部分电路示意图。

31.图9是本实用新型实施例提供的adv7672 input/output第一部分电路示意图。

32.图10是本实用新型实施例提供的adv7672 input/output第二部分电路示意图。

33.图11是本实用新型实施例提供的adv7672 input/output第三部分电路示意图。

34.图12是本实用新型实施例提供的adv7672 power电路示意图。

35.图13是本实用新型实施例提供的adv7672 power另一部分电路示意图。

36.图14是本实用新型实施例提供的adv7672 audio&b2b con电路示意图。

37.图15是本实用新型实施例提供的hdmi output hdmio另一部分电路示意图。

38.图16是本实用新型实施例提供的hdmi output hdmio电路示意图。

39.图17是本实用新型实施例提供的hdmi output hdmi1另一部分电路示意图。

40.图18是本实用新型实施例提供的hdmi output hdmi1电路示意图。

41.图19是本实用新型实施例提供的adv7672 input/output hdmi txo/hdmi tx1电路示意图。

42.图20是本实用新型实施例提供的adv7672 input/output另一部分电路示意图。

43.图21是本实用新型实施例提供的adv7672 power电路示意图。

44.图22是本实用新型实施例提供的adv7672 power另一部分电路示意图。

45.图23是本实用新型实施例提供的adv7672 audio&b2b con电路示意图。

46.图24是本实用新型实施例提供的adv7672 input/output hdmi tx2/hdmi tx3电路示意图。

47.图25是本实用新型实施例提供的adv7672 input/output hdmi tx2/hdmi tx3另一部分电路示意图。

48.图26是本实用新型实施例提供的adv7672 power电路示意图。

49.图27是本实用新型实施例提供的adv7672 power另一部分电路示意图。

50.图28是本实用新型实施例提供的adv7672 audio&b2b con电路示意图。

51.图29是本实用新型实施例提供的hdmi2另一部分电路示意图。

52.图30是本实用新型实施例提供的hdmi2电路示意图。

53.图31是本实用新型实施例提供的hdmi3另一部分电路示意图。

54.图32是本实用新型实施例提供的hdmi3电路示意图。

55.图33是本实用新型实施例提供的mcu i/o电路示意图。

56.图34是本实用新型实施例提供的usb poper电路示意图。

57.图35是本实用新型实施例提供的jtag/swd电路示意图。

58.图36是本实用新型实施例提供的mcu power电路示意图。

59.图37是本实用新型实施例提供的power supply_1第一部分电路示意图。

60.图38是本实用新型实施例提供的power supply_1第二部分电路示意图。

61.图39是本实用新型实施例提供的power supply_1第三部分电路示意图。

62.图40是本实用新型实施例提供的power supply_2第一部分电路示意图。

63.图41是本实用新型实施例提供的power supply_2第二部分电路示意图。

64.图42是本实用新型实施例提供的power supply_2第三部分电路示意图。

具体实施方式

65.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

66.针对现有技术存在的问题,本实用新型提供了一种音视频数据流多路分配器,下面结合附图对本实用新型作详细的描述。

67.如图1所示,本实用新型实施例提供的音视频数据流多路分配器包括:

68.电源系统:提供各个adv7672芯片供电电源;

69.数据镜像复用处理模块:由adv7672芯片数据镜像处理。

70.数据镜像复用处理模块包括:hdmi2.1 8k音视频数据流输入端1、第一adv7672芯片3、第二adv7672芯片4、第三adv7672芯片5、第一输出端口6、第二输出端口7、第三输出端口8和第四输出端口9;第一adv7672芯片3与hdmi2.1 8k音视频数据流输入端1连接,第一adv7672芯片3分别与第二adv7672芯片4和第三adv7672芯片5连接;第二adv7672芯片4分别与第一输出端口6和第二输出端口7连接,第三adv7672芯片5分别与第三输出端口8和第四输出端口9连接。电源系统分别通过导线与第一adv7672芯片3、第二adv7672芯片4和第三adv7672芯片5连接。其中,第一adv7672芯片3、第二adv7672芯片4和第三adv7672芯片5为阶梯型分布。

71.下面结合具体实施例对本实用新型的技术方案作进一步的描述。

72.本实用新型中基于hdmi2.1协议8k音视频数据流多路分配器的设计构思是:

73.由adv7672做算法数据镜像复用处理,镜像复用输出2路hdmi2.1协议的8k音视频数据流。通过adv7672芯片在2级做算法数据镜像复用处理成4路hdmi2.1协议的8k音视频数据流输出。

74.如图1所示,一种基于hdmi2.1协议8k音视频数据流多路分配器,包含三颗支持hdmi2.1协议的adv7672芯片,即adv7672芯片u1、adv7672芯片u2和adv7672芯片u3组成阶梯型,由adv7672芯片u1接收端hdmi2.1输入8k音视频数据流,经adv7672芯片u1镜像复用8k音视频数据流输出两路hdmi2.1协议8k高清数据流,其中,一路高清数据流送至adv7672芯片u2,另一路高清数据流送至adv7672芯片u3接收端,供电单元分别给adv7672芯片u1、adv7672芯片u2和adv7672芯片u3供电,组成8k音视频数据流最基本电路。

75.由adv7672芯片u1接收端hdmi2.1输入8k音视频数据流input1(7680x4320p),经adv7672芯片u1镜像复用8k音视频数据流输出两路hdmi2.1协议8k高清数据流txo和tx1,其中,一路高清数据流txo(7680x4320p)送至adv7672芯片u2的端口rx0,另一路高清数据流tx1(7680x4320p)送至adv7672芯片u3接收端rxo。

76.adv7672芯片u2从tx0(7680x4320p)输出端口输出至output1,从tx1(7680x4320p)输出端口输出至output2。

77.adv7672芯片u3从tx0(7680x4320p)输出端口输出至output3,从tx1(7680x4320p)输出端口输出至output4。

78.供电单元分别给adv7672芯片u1、adv7672芯片2和adv7672芯片3供电,组成8k音视频数据流最基本电路。

79.图3为图2实施例的电源系统连接方框图。如图3所示,由adv7672芯片2接收端hdmi2.1输入8k音视频数据流u输出4路hdmi2.1协议输出8k音视频数据流。

80.adv7672三颗芯片分别连接到三颗flash的w25x40芯片,w25x40芯片预制了adi公司(纳斯达克代码:adi)又名亚德诺半导体技术(上海)有限公司的驱动程序。

81.单片机stm32f429vit6通过i2c协议端口输出控制信号分别连接adv7672三颗芯片的i2c接收端口,接受stm32f429vit6的指令,并响应指令完成8k音视频数据流相应的处理。

82.电源系统:12v直流电源输入到ti公司的tps54429电源芯片转换5v/5a,分别送至ltc3616、ltc3614、lp38501三颗电源转换芯片以及hdmi插座电源5v输出。ltc3616转换输出1v/6a的直流电压分别送至三颗adv7672数字端供电入口。ltc3614转换输出1.35v/4a的直流电压送至lt3071芯片接收端,lt3071转换输出低噪纹波1.0v/5a直流电压,分别送至三颗adv7672模拟端供电入口。lp38501转换输出3.3v/3a直流电压,分别送至adv7672芯片i/o端口以及flash芯片,时钟多路输出芯片。

83.3)时钟系统:由ti公司的cdce913多路输出时钟信号芯片连接一颗25mhz的晶振,输出3路25mhz的信号分别送至adv7672三颗芯片时钟接收端口,解决时钟同步时序问题。

84.图4为本实用新型五颗adv7672芯片u1、u2、u3、u4和u5实施例的连接方框图,如图4所示,一种基于hdmi2.1协议8k音视频数据流多路分配器,包含三颗支持hdmi2.1协议的adv7672芯片,即adv7672芯片u1、adv7672芯片u2和adv7672芯片u3组成阶梯型,由adv7672芯片u1接收端hdmi2.1输入8k音视频数据流,经adv7672芯片u1镜像复用8k音视频数据流输出两路hdmi2.1协议8k高清数据流,其中,一路高清数据流送至adv7672芯片u2,另一路高清数据流送至adv7672芯片u3接收端,供电单元分别给adv7672芯片u1、adv7672芯片2和adv7672芯片3供电,组成8k音视频数据流最基本电路。

85.由adv7672芯片u3接收端hdmi2.1输入8k音视频数据流,经adv7672芯片u3镜像复用8k音视频数据流输出两路hdmi2.1协议8k高清数据流txo和tx1,其中,一路高清数据流经输出端txo送至adv7672芯片u4的接收端rx0,另一路高清数据流经输出端tx1送至adv7672芯片u5接收端rxo。

86.adv7672芯片u4从tx0(1920x4320p)输出端口输出至output3,从tx1(1920x4320p)输出端口输出至output4。

87.adv7672芯片u5从tx0输出端口输出至output5,从tx1输出端口输出至output6。

88.附图中英文和代码的中文含义是:

89.表1 英文和代码的中文含义

90.英文或代码中文含义英文或代码中文含义input输入input porto输入端口rxo接收端口0output输出端口rx1接收端口1spi串行协议tx0发送端口0flash储存芯片tx1发送端口1cystal石英晶振reset复位i2c1内部集成电路总线1i2c0内部集成电路总线0i2c2内部集成电路总线2

91.本实用新型的工作原理为:由adv7672做算法数据镜像复用处理,并将镜像复用处理后输出2路hdmi2.1协议的8k音视频数据流,输出分别接入2颗adv7672接收端,再次进行算法数据镜像复用处理,同时输出4路hdmi2.1协议的8k音视频数据流。

92.在本实用新型的描述中,除非另有说明,“多个”的含义是两个或两个以上;术语“上”、“下”、“左”、“右”、“内”、“外”、“前端”、“后端”、“头部”、“尾部”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。此外,术语“第一”、“第二”、“第三”等仅用于描述目的,而不能理解为指示或暗示相对重要性。

93.以上所述,仅为本实用新型的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1