一种Quartet轻量级加密算法的实现装置及方法

一种quartet轻量级加密算法的实现装置及方法

技术领域

1.本发明涉及加密算法技术领域,特别涉及一种quartet轻量级加密算法的实现装置及方法。

背景技术:

2.轻量级密码凭借着高安全性、设计紧凑等优点成为近年来密码学的研究热点之一,备受物联网安全应用领域关注。然而,随着物联网应用的普及,计算能力较弱的终端设备急需专门面向资源受限环境设计的面积更小、速度更快、安全水平更高的加密算法,而quartet轻量级密码在设计时就以资源受限环境为目标,因而在物联网环境下具有天然的良好实现性能。

3.quartet轻量级序列密码于2019年被提出,这种密码的密钥长度为128位,内部状态为256比特,是一种新型结构的序列密码,兼具序列密码和分组密码的特点,即加密时将明文序列划分为长度均为64-bit的组,而每个明文分组又与每轮产生的64-bit密钥逐位异或获得密文。密码借鉴了sha-3标准的keccak哈希算法,使用4个64-bit的并行状态,提高了硬件实现的效率,并运用5个ascon算法的扩散函数,增加了状态内的差分传播,可降低伪造或篡改攻击的成功机率。此外,quartet算法还具备关联数据加密认证(aead)功能,可通过加密后生成的认证标签来判断是否需要进行解密,如果标签错误,则不会输出解密结果,避免了有用信息的泄露。

4.quartet作为轻量级序列密码,有着比传统序列密码更加高效的面向资源受限环境的算法结构,在物联网等场景下有着广泛的应用。然而,目前尚无高效的quartet硬件实现策略。为了能在对面积、成本和实时性要求高的终端上实现,应该设计高效的quartet实现装置及方法。

技术实现要素:

5.为解决上述技术问题,本发明提供了一种quartet轻量级加密算法的实现装置及方法,具有资源占用少、吞吐率高的特点,既能满足物联网紧凑终端安全需求,也能满足边缘传感网络高速数据传输需求。

6.为达到上述目的,本发明的技术方案如下:

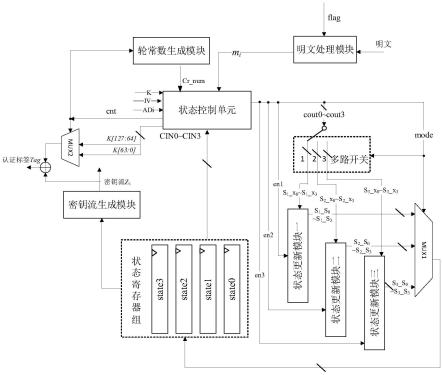

7.一种quartet轻量级加密算法的实现装置,包括明文处理模块、状态更新模块、状态寄存器组、状态控制单元、轮常数生成模块、密钥流生成模块、多路开关、数据选择器mux1和数据选择器mux2;

8.所述明文处理模块接收用户输入的指示信号flag和明文,输出处理后的64-bit明文给状态控制单元;

9.所述状态更新模块包括三个,用于在状态控制单元输出的使能信号的驱动下进行3种不同的扩散运算,为加密算法计算不断更新的内部状态,并将更新后的状态送入状态寄存器组中;

10.所述状态寄存器组由4个状态寄存器state0-state3组成,负责存储加密算法运行过程中生成并不断更新的状态,每个时刻4个状态寄存器state0-state3的取值称为该时刻的状态,分别记作x

0-x3;

11.所述状态控制单元的输入端k和输入端iv分别用于接收用户输入的初始化密钥和初始化向量,输入端adi用于接收用户输入的8-bit关联数据,输入端mi与明文处理模块的输出相连,接收处理过的64-bit明文;所述状态控制单元的输入端cin0~cin3分别与4个状态寄存器state0~state3的输出一一对应相连,用于每个时刻读取一组状态;所述状态控制单元的输出cnt与所述轮常数生成模块的输入、以及数据选择器mux2的地址端相连,分别为轮常数生成模块提供计数值和为数据选择器mux2提供地址;所述状态控制单元将读入的128-bit的初始化密钥按照高低64位分成两组,即k[127:64]和k[63:0],直接连线输出给数据选择器mux2的数据输入端,供生成认证标签时使用;

[0012]

所述轮常数生成模块由26选1的数据选择器mux3组成,可根据输入端的输入选择输出对应地址的轮常数,用于初始化阶段中的状态更新;

[0013]

所述密钥流生成模块与状态寄存器组的输出相连,密钥流生成模块根据状态寄存器组的取值与数据选择器mux2的输出异或生成密钥流;

[0014]

所述多路开关的数据输入端与状态控制单元的输出cout0~cout3相连,地址输入端与状态控制单元中状态指示寄存器mode相连,数据输出端分别与三个状态更新模块的输入相连,可根据地址输入端的输入将状态控制单元的输出给某个状态更新模块;

[0015]

所述数据选择器mux1的数据输入端与三个状态更新模块的输出相连,地址输入端与状态控制单元中状态指示寄存器mode相连,输出与状态寄存器组相连,可根据地址输入端的输入将某个状态更新模块的输出给状态寄存器组;

[0016]

所述数据选择器mux2的两个数据输入端分别与状态控制单元输出的两组初始化密钥k[127:64]和k[63:0]相连,地址输入端与状态控制单元的输出cnt相连,可根据地址输出初始化密钥的部分位,用于与密钥流逐位异或生成认证标签。

[0017]

上述方案中,所述状态更新模块包括执行ascon线性扩散函数的扩散运算单元和二选一的数据选择器mux4,所述数据选择器mux4具备使能端记作enable,enable取值为0或者1;当其值为1时,4个64-bit数据通过输入端口si_x0~si_x3被送入扩散运算单元中,1≤i≤3,i代表状态更新模块号;每个64-bit数据均需经过4个ascon线性扩散函数获得运算结果,通过输出端口si_s0~si_s3输出,1≤i≤3,i代表状态更新模块号;当enable取值为0时,状态更新模块的输出等于输入的数据。

[0018]

进一步的技术方案中,所述扩散运算单元由非门、与门、异或门及循环移位单元一、循环移位单元二、循环移位单元三组成,功能是对输入的数据进行扩散运算,所述循环移位单元一、循环移位单元二、循环移位单元三的功能是对输入的数据进行循环向左移动2位;

[0019]

所述扩散运算单元的具体逻辑如下:

[0020]

χ函数:outi←

ini^(~in

i+2

)&in

i+1

;0≤i≤3

[0021]

ρ函数:outi←

{ini[63-ni:32],ini[63:64-ni],ini[31-ni:0],ini[31:32-ni]};0≤i≤3

[0022]

λ函数:outi←

ini^{ini[r

i,1-1∶0],ini[63:r

i,1

]}^{ini[r

i,2-1∶0],ini[63:r

i,2

]};0

≤i≤3

[0023]

其中,ini代表输入的64比特数据,^表示逐位异或,逻辑值相同则结果为0,不同则结果为1;~表示逐位取反,逻辑值1取反为0,逻辑值0取反为1;&表示逐位相与;ini[:]表示64比特中的某些比特位,{}表示拼接,即将几个不同位宽的信号拼接为一个信号,而最终信号的位宽等于各个信号位宽的和;ni代表ascon线性扩散函数中ρ函数使用的参数值;在算法运行的不同阶段,ni的取值始终是固定的;r

i,1

,r

i,2

代表ascon线性扩散函数中χ函数使用的参数值,在算法运行的不同阶段,r

i,1

,r

i,2

的取值是可变的。

[0024]

上述方案中,所述密钥流生成模块由异或门、非门和循环移位单元四组成;所述密钥流生成模块每轮将状态x1逐位取反,状态x0循环右移nz比特,二者相与的结果再和状态x2、x3逐位异或,最终生成64-bit的密钥流z

t

用于加密。

[0025]

上述方案中,所述明文处理模块包括一个二选一的数据选择器mux5和一个七选一的数据选择器mux6,所述数据选择器mux6具备一个输入端flag,用于接收指示输入的明文是否完整;所述数据选择器mux5具有一个输入端length(`m),用于接收不完整明文的长度;所述数据选择器mux5具有一个输出端mi,用于输出64-bit的明文mi;所述明文处理模块的功能是对用户输入的明文进行处理,如果flag取值为1,表示输入的明文是完整的64-bit,此时数据选择器mux5将直接按照用户输入的明文进行输出;如果flag取值为0,则表示输入的明文是不完整的,需要进行填充,数据选择器mux5将通过数据选择器mux6选择与不完整明文长度对应的填充完成的序列输出。

[0026]

上述方案中,所述状态控制单元包括一个9比特计数器,三个比较器,三个使能信号寄存器en1~en3,一个状态指示寄存器mode以及三个数据选择器mux7~mux9,用于指示硬件装置依次进入五个阶段:载入阶段、初始化阶段、处理关联数据阶段、加密数据及密钥流生成阶段、生成认证标签阶段;所述计数器具备复位端rst,其取值为0或1,当取值为1时为有效状态,计数器清零,否则计数器计数并输出计数值cnt。

[0027]

进一步的技术方案中,所述计数器用于计算加密算法消耗的周期数,并通过比较器控制改变使能信号寄存器en1~en3和状态指示寄存器mode的值;其中,使能信号寄存器en1~en3取值为0或1,当取值为1时为有效状态,否则为无效状态;状态指示寄存器mode可取8个值,范围为0~7,不同的取值代表对输入数据进行不同的逻辑操作,而三个数据选择器mux7~mux9通过状态指示寄存器mode的值选择对输入的4个64-bit数据cin0~cin3做不同逻辑操作并输出。

[0028]

上述方案中,所述多路开关根据状态控制单元中状态指示寄存器mode的值,将状态控制单元的输出cout0~cout3送入某个状态更新模块的输入,当mode取值为0、1、2、4、5、6时;将状态控制单元的输出cout0~cout3送入状态更新模块1的输入;当mode取值为3时;将状态控制单元的输出cout0~cout3送入状态更新模块2的输入;当mode取值为7时;将状态控制单元的输出cout0~cout3送入状态更新模块3的输入。

[0029]

上述方案中,所述数据选择器mux1根据状态控制单元中状态指示寄存器mode的值,将某个状态更新模块的输出送入状态寄存器组;当mode取值为0、1、2、4、5、6时;将状态更新模块一的输出送入状态寄存器组;当mode取值为3时;将状态更新模块二的输出送入状态寄存器组;当mode取值为7时;将状态更新模块三的输出送入状态寄存器组。

[0030]

一种quartet轻量级加密算法的实现方法,采用如上所述的一种quartet轻量级加

密算法的实现装置,包括如下过程:

[0031]

(1)载入阶段:

[0032]

算法开始前,状态控制单元将三个使能信号寄存器en1~en3全部置为低电平无效状态,状态指示寄存器mode取值为0,此时三个状态更新模块关闭,位于状态控制单元的输入端k和输入端iv多轮读入初始化密钥和初始化向量,状态寄存器state0~state3根据k和iv的部分位进行指定组合并形成初值,载入阶段结束;

[0033]

(2)初始化阶段:

[0034]

状态控制单元通过输入端cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,同时计数器开始计数,使能信号寄存器en1的值为高电平有效,使能信号寄存器en2和en3为低电平无效,状态指示寄存器mode取值为1,则状态控制单元对输入数据进行如下操作:

[0035]

cou t0=cin0

[0036]

cout1=cin1

[0037]

cout2=cin2

[0038]

cout3=cin3^cr_hum

[0039]

其中,cr_num是轮常数生成模块根据状态控制单元中计数器输出的计数值cnt而产生的初始化每轮需要的轮常数;cout0~cout3为状态控制单元的输出;

[0040]

多路开关根据状态指示寄存器mode的值将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3;状态更新模块一接收到有效使能信号后,通过扩散运算单元的与或非操作及循环移位,获得一次扩散运算的结果;而数据选择器mux1根据状态指示寄存器mode的取值将状态更新模块一的输出s1_s0~s1_s3与状态寄存器state0~state3一一对应相连,进而更新一次状态寄存器组的值;

[0041]

当下一次时钟到达时,使能信号寄存器en1仍然有效,使能信号寄存器en2和en3均无效,状态指示寄存器mode的值为1,状态控制单元继续通过端口cin0~cin3从状态寄存器组读入4个64-bit的数据,操作同上;多路开关仍将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3,状态更新模块一重复进行扩散运算及与轮常数异或的计算,数据选择器mux1根据状态指示寄存器mode的取值将状态更新模块一的输出s1_s0~s

1-s3送入状态寄存器state0~state3,如此循环直至当计数器计数值到达24时,状态控制单元将使能信号寄存器en1置为低电平,状态指示寄存器mode的值为2,状态控制单元对读入的cin0~cin3进行如下操作:

[0042]

cout0=cin0^k[63:0]

[0043]

cout1=cin1^k[127:64]

[0044]

cout2=cin2

[0045]

cout3=cin3

[0046]

其中,k为载入阶段多轮读入的初始化密钥key;

[0047]

根据状态指示寄存器mode的取值,多路开关仍将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3;由于状态控制单元一已被关闭,所以最终计算结果不会进行扩散运算而是被直接输出;数据选择器mux1根据状态指示寄存器mode的取值将状态更新模块一的输出s1_s0~s1_s3送入状态寄存器state0~state3中,至此初

始化阶段结束;

[0048]

(3)处理关联数据阶段:

[0049]

状态控制单元通过端口cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,通过位于状态控制单元的端口adi读入用户输入的8-bit关联数据adi,并将使能信号寄存器en2置为高电平有效,使能信号寄存器en1和en3置为低电平无效,状态指示寄存器mode取值置为3,则状态控制单元对输入数据进行如下操作:

[0050]

cout0=cin0

[0051]

cout1=cin1^adi

[0052]

cout2=cin2

[0053]

cout3=cin3

[0054]

多路开关根据状态指示寄存器mode的值,将状态控制单元的输出cout0~cout3连接到状态更新模块二的输入s2_x0~s2_x3;状态更新模块二接收到有效使能信号后通过扩散运算单元的与或非操作及循环移位,获得一次扩散运算的结果;而数据选择器mux1根据状态指示寄存器mode的取值,将状态更新模块二的输出s2_s0~s2_s3与状态寄存器state0~state3一一对应相连,进而更新一次状态寄存器组的值;如此循环直至当关联数据全部处理完成后,此时计数器计数值到达指定数,状态控制单元将使能信号寄存器en2置为低电平,使能信号寄存器en1置为高电平,此时状态指示寄存器mode的值变为4,状态控制单元通过端口cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,并根据状态指示寄存器mode的取值做如下操作:

[0055]

cout0=cin0

[0056]

cout1=cin1

[0057]

cout2=cin2

[0058]

cout3=cin3

[0059]

多路开关将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3,由于状态更新模块二已被关闭,而状态更新模块一接收到了有效使能信号,因此状态更新模块一开始进行扩散运算,数据选择器mux1根据状态指示寄存器mode的取值将状态更新模块一的输出s

1_

s0~s1_s3送入状态寄存器state0~state3中,如此循环12个时钟周期;12轮状态更新结束后,状态控制单元将使能信号寄存器en1~en3全部置为低电平无效,状态指示寄存器mode取值为5,此时对获取的4个64-bit的数据cin0~cin3做如下操作:

[0060]

cout0=cin0

[0061]

cout1=cin1

[0062]

cout2=cin2

[0063]

cout3=cin3^1

′

b1

[0064]

其中,1’b1代表1位二进制数1;多路开关仍将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3;由于状态更新模块一已被关闭,因此最终计算结果不会进行扩散运算而是被数据选择器mux1直接送入状态寄存器state0~state3中,至此,处理关联数据阶段结束;

[0065]

(4)加密数据及密钥流生成阶段:

[0066]

关联数据处理结束后,明文处理模块接收到外部用户输入的高电平flag信号,状

态控制单元通过端口mi读入完整的64-bit明文,并将使能信号寄存器en2、en3均置为低电平无效,使能信号寄存器en1置为高电平有效,状态指示寄存器mode取值为6;状态控制单元通过端口cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,并根据状态指示寄存器mode的取值做如下操作:

[0067]

cout0=cin0^mi[0068]

cout1=cin1

[0069]

cout2=cin2

[0070]

cout3=cin3

[0071]

多路开关根据mode的取值将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3;状态更新模块一接收到有效使能信号后,进行一次扩散运算;而数据选择器mux1根据mode的取值,将状态更新模块一的输出s2_s0~s2_s3与状态寄存器state0~state3一一对应相连,进而更新一次状态寄存器组的值,此时密钥流生成模块开始工作,从状态寄存器组中取值,并根据其内部逻辑生成密钥流;如此循环直至完整明文全部处理完成,此时计数器计数值到达指定数,flag输入即将变为0;此后,flag输入变为低电平,明文处理模块对不完整明文进行处理,根据不完整明文的长度length(`m),明文处理模块选择对应填充好的64-bit明文输出,由于使能信号寄存器en1仍为高电平,使能信号寄存器en2、en3为低电平,状态指示寄存器mode的值仍为6,因此状态控制单元对读入数据cin0~cin3的操作以及状态更新模块以的工作过程与对完整明文处理时的完全相同;

[0072]

当明文全部处理完毕后,状态控制单元将使能信号寄存器en1、en2置为低电平无效,使能信号寄存器en3置为高电平有效,状态指示寄存器mode取值为7,状态控制单元通过端口cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,并根据mode的取值做如下操作:

[0073]

cout0=cin0

[0074]

cout1=cin1

[0075]

cout2=cin2

[0076]

cout3=cin3

[0077]

多路开关根据状态指示寄存器mode的取值将状态控制单元的输出cout0~cout3连接到状态更新模块三的输入s3_x0~s3_x3,状态更新模块一和状态更新模块二关闭,状态更新模块三接收到有效使能信号后进行一次扩散运算,数据选择器mux1根据状态指示寄存器mode的取值,将状态更新模块三的输出s3_s0~s3_s3与状态寄存器state0~state3一一对应相连,进而更新一次状态寄存器组的值,密钥流生成模块继续从状态寄存器组中取值,并根据其内部逻辑生成密钥流,如此循环共需24轮;

[0078]

(5)生成认证标签阶段:

[0079]

当进行至第23轮时,数据选择器mux2将状态控制单元输出的初始化密钥k[63:0]选择输出,与生成的密钥流逐位异或,生成认证标签tag的低64位;第24轮时,数据选择器mux2将状态控制单元输出的初始化密钥k[127:64]选择输出,与生成的密钥流逐位异或,生成认证标签tag的高64位,至此认证标签生成结束。

[0080]

通过上述技术方案,本发明提供的一种quartet轻量级加密算法的实现装置及方法具有如下有益效果:

[0081]

本发明提出的实现装置及方法,具有资源占用少、吞吐率高的特点,既能满足物联网紧凑终端安全需求,也能满足边缘传感网络高速数据传输需求,具体体现在本发明的面积优化方案:

[0082]

第一,在quartet算法中通过位拼接的方式,实现quartet硬件装置中的循环移位,可有效降低资源占用,减少消耗的时钟周期数。例如:假设64位状态循环移位数为a(a《64,a为正整数),对64位状态循环移动后的结果就是将第(a-1)位到第0位对应的值取出,将其赋给第63位到第(64-a)位,剩余的(64-a)位补充到第(63-a)到第0位;同理,对于32位数据,假设循环移位数为b(b《32,b为正整数),对32位数据循环移动的结果就是将第(b-1)位到第0位对应的值取出,将其赋给第31位到第(32-b)位。

[0083]

第二,quartet算法的不同运行阶段设计了不同的状态更新函数,具体表现为状态循环移动的位数不同。在分析比较使用参数后,将初始化阶段、处理关联数据阶段的最后12个周期、加密阶段的状态更新模块复用,将处理关联数据的剩余周期、生成认证标签阶段的状态更新模块复用,进一步降低资源的占用。

[0084]

第三,quartet算法的不同运行阶段占用的周期数不同,具体地,初始化阶段24个周期,处理关联数据占用周期数与关联数据长度有关,加密占用周期数与明文长度有关,生成认证标签占用2个周期。如果给每一个阶段设置不同大小的计数器,那么将造成大量的资源浪费。通过共用状态控制单元中的9比特计数器,同时将计数器的低5位赋予轮常数模块,可以有效降低资源消耗。

[0085]

第四,quartet算法需要读入128位的初始化密钥key和96位的初始化向量initial vector,还需要读入一定长度的关联数据associated data及明文message,如果将这些数据一次性全部读入,虽然可以减小加密算法运行占用的周期数目,提高加密的速度,但会消耗大量的io资源,进而使得资源消耗成倍增长,同时也限制了加密算法部署的fpga类型。因此,可通过一个周期读入一定数目比特的方式,将不同阶段需要读入的数据分几个周期读入,降低io资源的消耗和对适配板型的要求。本发明可在一个周期读入8-bit的数据,这样可分别通过16个周期和12个周期将初始化密钥key和初始化向量initial vector全部读入。

[0086]

第五,quartet算法对明文的处理分为两个阶段,第一阶段是对64-bit分组的完整明文的处理,即每个周期读入64-bit的明文,明文参与状态更新,如此循环往复直至将所有明文吸收进入状态中或者直至剩余明文不足64-bit;第二阶段是对剩余明文的处理,在剩余明文前补充一位1,然后用多个0将其补充为64-bit的组。本发明利用case结构展开剩余明文的7种情况,可以减少取余运算的次数,降低补1和0的实现逻辑的复杂程度。如当剩余1个字节(即8位)时,可通过拼接的形式,在剩余明文前补充一位1,剩余55位全部用0表示;当剩余2个字节(即16位)时,在剩余明文前补充一位1,剩余的47位全部用0表示,以此类推。

[0087]

在上述方案中,quartet内部状态更新所用的反馈函数尽可能地复用,以降低组合逻辑资源消耗。同时,在对状态进行循环移位时,将状态的部分位直接取出,以连线的形式组合输出,减少移位寄存器的数量;使用同一个计数器控制quartet在运行过程中各阶段的轮数计数,降低计数器占据的资源数量;在顶层模块中使用状态机控制算法流程的切换,减少各个底层模块之间的信号交互,降低硬件实现的复杂度。

[0088]

效果:

[0089]

在xilinx7系列fpga上(virtex-7):

[0090]

不使用面积优化策略时,quartet轻量级加密算法硬件实现装置使用了4690个查找表(lut),3156个寄存器(flip-flop),面积为1475个slices,运行频率为250mhz。

[0091]

在面积优化方案下,quartet轻量级加密算法硬件实现装置使用了1907个查找表,715个寄存器(flip-flop),仅占用545个slices,运行频率为201.9mhz。

[0092]

在xilinx7系列fpga上(spartan-7):

[0093]

在面积优化方案下,quartet轻量级加密算法硬件实现装置使用了2057个查找表,715个寄存器(flip-flop)仅占用580个slices,运行频率为144.7mhz。

附图说明

[0094]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍。

[0095]

图1为本发明实施例所公开的一种quartet轻量级加密算法的实现装置示意图;

[0096]

图2为本发明实施例所公开的明文处理模块结构示意图;

[0097]

图3为本发明实施例所公开的状态更新模块结构示意图;

[0098]

图4为本发明实施例所公开的扩散运算单元结构示意图;

[0099]

图5为本发明实施例所公开的循环移位单元一结构示意图;

[0100]

图6为本发明实施例所公开的状态控制单元结构示意图;

[0101]

图7为本发明实施例所公开的轮常数生成模块结构示意图。

具体实施方式

[0102]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。

[0103]

本发明提供了一种quartet轻量级加密算法的实现装置,如图1所示,包括明文处理模块、状态更新模块、状态寄存器组、状态控制单元、轮常数生成模块、密钥流生成模块、多路开关、数据选择器mux1及数据选择器mux2。

[0104]

一、明文处理模块

[0105]

明文处理模块接收用户输入的指示信号flag和明文,输出处理后的64-bit明文给状态控制单元。

[0106]

如图2所示,明文处理模块包括一个二选一的数据选择器mux5和一个七选一的数据选择器mux6,数据选择器mux6具备一个输入端flag,用于接收指示输入的明文是否完整;数据选择器mux5具有一个输入端length(`m),用于接收不完整明文的长度,其输入最大值为7,如length(`m)=1,表示不完整明文的长度为1个字节(8-bit);数据选择器mux5具有一个输出端mi,用于输出64-bit的明文mi;明文处理模块的功能是对用户输入的明文进行处理,如果flag取值为1,表示输入的明文是完整的64-bit,此时数据选择器mux5将直接按照用户输入的明文进行输出;如果flag取值为0,则表示输入的明文是不完整的,需要进行填充,数据选择器mux5将同通过数据选择器mux6选择与不完整明文长度对应的填充完成的序列输出。

[0107]

其基本原理是在剩余明文前补充一位1,然后用多个0将其补充为64-bit的组。如

当剩余1个字节(即8位)时,明文处理模块通过位拼接的形式,在剩余明文前补充一位1,而剩余55位全部用0表示;当剩余2个字节(即16位)时,在剩余明文前补充一位1,剩余的47位全部用0表示,以此类推。因为剩余字节数的情况只有7种(剩余1/2/3/4/5/6/7个字节),因此需使用一个七选一的数据选择器mux6,将所有可能的情况提前计算出以供选择使用。

[0108]

二、状态更新模块

[0109]

状态更新模块包括三个,用于在状态控制单元输出的使能信号的驱动下进行3种不同的扩散运算,为加密算法计算不断更新的内部状态,并将更新后的状态送入状态寄存器组中。

[0110]

如图3所示,每个状态更新模块包括执行ascon线性扩散函数的扩散运算单元和二选一的数据选择器mux4,数据选择器mux4具备使能端记作enable,enable取值为0或者1;当其值为1时,4个64-bit数据通过输入端口si_x0~si_x3被送入扩散运算单元中,1≤i≤3,i代表状态更新模块号;每个64-bit数据均需经过4个ascon线性扩散函数获得运算结果,通过输出端口si_s0~si_s3输出,1≤i≤3,i代表状态更新模块号;当enable取值为0时,状态更新模块的输出等于输入的数据。

[0111]

如图4所示,扩散运算单元由非门、与门、异或门及循环移位单元一、循环移位单元二、循环移位单元三组成,功能是对输入的数据进行扩散运算。而三个循环移位单元的功能是相同的,即均为对输入的数据进行循环移位,区别在于循环移动的位数不同,且循环移动的操作对象不同。循环移位单元一对in2操作,而循环移位单元二和循环移位单元三均对in3操作;循环移位单元一移动位数为n2(见表1),而循环移位单元二和循环移位单元三移动位数为r

i,1ri,2

(见表2~4)。其基本工作原理相同,以循环移位单元一为例,若x<<<2表示将x向左循环移动2位,当x=64

′

h00000001时,对其向左循环移动2位后结果为s=64

′

h00000100。循环移位单元一由固定连接的连线及寄存器组成,而连线关系与循环移动的位数及循环移动方向有关,如图5所示。当循环移动位数为2-bit,循环移动方向为向左时,将x的高2位(对应x[63:62])取出,对应连接到s的低2位(对应s[1:0]),剩余部分(对应x[61:0])对应连接到s[63:2]。同理,当循环移动方向为向左,循环移动位数为i时(0<i<63),将x[63:64-i]取出,连接到s[i-1:0],剩余部分连接到s[63:i]。同理,循环移位单元二和三也是由固定连接的连线及寄存器组成,只不过连线关系由循环右移和参数r

i,1ri,2

(见表2~4)决定。

[0112]

扩散运算单元的具体逻辑如下:

[0113]

χ函数:outi←ꢀ

ini^(~in

i+2

)&in

i+1

;0≤i≤3

[0114]

ρ函数:outi←

{ini[63-ni:32],ini[63:64-ni],ini[31-ni:0],ini[31:32-ni]};0≤i≤3

[0115]

λ函数:outi←

ini^{ini[r

i,1-1:0],ini[63:r

i,1

]}^{ini[r

i,2-1:0],ini[63:r

i,2

]};0≤i≤3;

[0116]

其中,ini代表输入的64比特数据,^表示逐位异或,逻辑值相同则结果为0,不同则结果为1;~表示逐位取反,逻辑值1取反为0,逻辑值0取反为1;&表示逐位相与;ini[:]表示64比特中的某些比特位,{}表示拼接,即将几个不同位宽的信号拼接为一个信号,而最终信号的位宽等于各个信号位宽的和;ni代表ascon线性扩散函数中ρ函数使用的参数值,如表1所示;在算法运行的不同阶段,ni的取值始终是固定的;r

i,1

,r

i,2

代表ascon线性扩散函数中

χ函数使用的参数值,在算法运行的不同阶段,r

i,1

,r

i,2

的取值是可变的。在初始化阶段中,r

i,1

,r

i,2

使用如表2所示的参数;在处理关联数据阶段,r

i,1

,r

i,2

使用如表3所示的参数;在加密阶段,r

i,1

,r

i,2

使用如表2所示的参数;在生成认证标签阶段,r

i,1

,r

i,2

使用如表4所示的参数。因此,状态更新模块也有与之相对应的3种,区别仅在于r

i,1

,r

i,2

的不同取值。

[0117]

表1ρ函数中ni的取值

[0118]

staten0n1n2n3value2023526

[0119]

表2初始化/加密阶段χ函数中r

i,1

,r

i,2

的取值

[0120]

states0s1s2s3variable(r

0,1

,r

0,2

)(r

i,1

,r

1,2

)(r

2,1

,r

2,2

)(r

3,1

,r

3,2

)value(1,6)(10,17)(7,41)(61,39)

[0121]

表3处理关联数据阶段χ函数中r

i,1,ri,2

的取值

[0122]

states0s1s2s3variable(r

0,1

,r

0,2

)(r

i,1

,r

1,2

)(r

2,1

,r

2,2

)(r

3,1

,r

3,2

)value(1,6)(10,17)(7,41)(19,28)

[0123]

表4生成认证标签阶段χ函数中r

i,1

,r

i,2

的取值

[0124]

lanes0s1s2s3variable(r

0,1

,r

0,2

)(r

1,1

,r

1,2

)(r

2,1

,r

2,2

)(r

3,1

,r

3,2

)value(61,39)(10,17)(7,41)(19,28)

[0125]

根据上述规律,所述的状态更新模块将在每个时钟周期产生一组更新后的取值,并将其通过端口si_s0~si_s3输出,以供加密时提取状态生成密钥流。

[0126]

三、状态寄存器组

[0127]

状态寄存器组由4个状态寄存器state0-state3组成,负责存储加密算法运行过程中生成并不断更新的状态,每个时刻4个状态寄存器state0-state3的取值称为该时刻的状态,分别记作x

0-x3,状态更新模块、密钥流生成模块均需获取当前时刻的状态。

[0128]

四、状态控制单元

[0129]

如图6所示,状态控制单元包括一个9比特计数器c

′

,三个比较器,三个使能信号寄存器en1~en3,一个状态指示寄存器mode以及三个数据选择器mux7~mux9,用于指示硬件装置依次进入五个阶段:载入阶段、初始化阶段、处理关联数据阶段、加密数据及密钥流生成阶段、生成认证标签阶段。计数器具备复位端rst,其取值为0或1,当取值为1时为有效状态,计数器清零,否则计数器计数并输出计数值cnt。状态控制单元具备输入端cin0~cin3,用于从状态寄存器组中读取4个64-bit的数据输入cin0~cin3;还具备输入端adi和mi,分别用于读取用户输入的8-bit关联数据adi和64-bit的明文mi;具备输入端k和iv,用于读取用户输入的128-bit初始化密钥key和96-bit初始化向量initialvector;状态控制单元的输出cnt与轮常数生成模块的输入、以及数据选择器mux2的地址端相连,分别为轮常数生成模块提供计数值和为数据选择器mux2提供地址;状态控制单元将读入的128-bit初始化密钥按照64位一组的形式分成两组,即k[127:64]和k[63:0]分别输出给数据选择器mux2的数据输入端。状态控制单元还与数据选择器mux1的地址端及多路开关的地址端相连;三个状

态更新模块的输出端与数据选择器mux1的数据输入端相连,状态控制单元的输出cout0~cout3与多路开关的数据输入端相连,分别决定某个状态更新模块的输出被送入状态寄存器组中以及状态控制单元的输出被送入某个状态更新模块中。

[0130]

计数器用于计算加密算法消耗的周期数,并通过比较器控制改变使能信号寄存器en1~en3和状态指示寄存器mode的值;其中,使能信号寄存器en1~en3取值为0或1,当取值为1时为有效状态,否则为无效状态;状态指示寄存器mode可取8个值,范围为0~7,不同的取值代表对输入数据进行不同的逻辑操作,而三个数据选择器mux7~mux9通过状态指示寄存器mode的值选择对输入的4个64-bit数据cin0~cin3做不同逻辑操作并输出。

[0131]

具体逻辑如下:

[0132]

(1)在载入阶段:

[0133]

载入阶段负责读入初始化密钥key和初始化向量initialvector,并给状态寄存器组赋初值,此时使能信号寄存器en1~en3均取值为0,状态指示寄存器mode取值也为0,cin0~cin3读入的4个64-bit数据均为0,输出cout0~cout3也置为0;

[0134]

(2)在初始化阶段:

[0135]

初始化阶段使能信号寄存器en1取值为1,en2、en3取值为0,状态指示寄存器mode取值为1,此时:

[0136]

cout0=cin0

[0137]

cout1=cin1

[0138]

cout2=cin2

[0139]

cout3=cin3^cr_num

[0140]

其中cr_num为轮常数生成单元根据状态控制单元中的计数器值产生的8-bit轮常数;当计数器计数值到达24时,状态指示寄存器取值为2,使能信号寄存器en1~en3均取值为0,此时:

[0141]

cout0=cin0^k[63:0]

[0142]

cout1=cin1^k[127:64]

[0143]

cout2=cin2

[0144]

cout3=cin3

[0145]

其中,k为载入阶段多轮读入的初始化密钥key;

[0146]

(3)在处理关联数据阶段:

[0147]

处理关联数据阶段状态指示寄存器取值为3,使能信号寄存器en2取值为1,en1、en3取值为0。此时:

[0148]

cout0=cin0

[0149]

cout1=cin1^adi

[0150]

cout2=cin2

[0151]

cout3=cin3

[0152]

其中,adi为用户通过端口adi输入的8-bit关联数据;

[0153]

当关联数据吸收完毕(计数器计数值到达指定值),状态指示寄存器取值为4,使能信号寄存器en2、en3取值为0,en1取值为1。此时:

[0154]

cout0=cin0

[0155]

cout1=cin1

[0156]

cout2=cin2

[0157]

cout3=cin3

[0158]

在12个周期后,状态指示寄存器取值为5,使能信号寄存器en1、en2、en3取值均为0,此时:

[0159]

cout0=cin0

[0160]

cout1=cin1

[0161]

cout2=cin2

[0162]

cout3=cin3^1

′

b1

[0163]

其中,1’b1表示1位二进制数1;

[0164]

(4)在加密及密钥流生成阶段:

[0165]

加密阶段状态指示寄存器取值为6,使能信号寄存器en2、en3取值为0,en1取值为1。此时:

[0166]

cout0=cin0^mi[0167]

cout1=cin1

[0168]

cout2=cin2

[0169]

cout3=cin3

[0170]

其中,mi为通过端口mi接收的来自明文处理模块的64-bit明文;

[0171]

(5)在生成认证标签阶段:

[0172]

生成认证标签阶段状态指示寄存器取值为7,使能信号寄存器en1、en2取值为0,en3取值为1。此时:

[0173]

cout0=cin0

[0174]

cout1=cin1

[0175]

cout2=cin2

[0176]

cout3=cin3

[0177]

五、轮常数生成模块

[0178]

如图7所示,轮常数生成模块由26选1的数据选择器mux3组成,数据选择器mux3具备5-bit地址输入端address和8-bit数据输出端cr_num,可根据地址输入端address的输入选择输出对应地址的内部8-bit常数(这些8-bit常数在算法运行前就已经确定,如表5所示),这些常数即为轮常数,用于初始化阶段中的状态更新。

[0179]

表5轮常数取值

[0180]

地址输入01234567891011cr_numf0e1d2c3b4a5968778695a4b地址输入121314151617181920212223cr_num13260c1932250a152a1d3a2b

[0181]

六、密钥流生成模块

[0182]

密钥流生成模块由异或门、非门和循环移位单元四组成;其中,循环移位单元四的结构与状态更新模块中的循环移位单元一、循环移位单元二、循环移位单元三类似,基本原理也完全相同,即循环移位单元四亦是由固定连接的连线及寄存器组成,区别在于循环移

位单元四的循环移位方向为向右,循环移位的位数为nz=11。假定循环移位单元四的操作对象为64-bit的y,则s`=y>>>11就表示向右循环移位11-bit的结果。按照状态更新模块中循环移位单元的原理,将y的低11位(对应y[10:0])取出,对应连接到s`的高11位(对应s`[63:53]),剩余部分(对应y[63:11])连接到s`[52:0],如此即可获得最终的移位结果。

[0183]

密钥流生成模块每轮将状态x1逐位取反,状态x0循环右移nz比特,二者相与的结果再和状态x2、x3逐位异或,最终生成64-bit的密钥流z

t

用于加密。具体地,密钥流输出函数为:

[0184]zt

←

x2^x3^(~x1)&{x0[n

z-1:0],x0[63:nz]}。

[0185]

密钥流生成模块与状态寄存器组的输出相连,密钥流生成模块根据状态寄存器组的取值与数据选择器mux2的输出异或生成密钥流z

t

。

[0186]

七、多路开关

[0187]

多路开关具备4个64-bit数据输入,1个3-bit地址输入和3个256-bit数据输出;其功能是根据地址输出指定的输入数据,如图1。其具体逻辑如下:

[0188]

当地址输入为0、1、2、4、5、6时,标记为1的256-bit输出等于输入数据,其余两个输出置0;

[0189]

当地址输入为3时,标记为2的256-bit输出等于输入数据,其余两个输出置0;

[0190]

当地址输入为7时,标记为3的256-bit输出等于输入数据,其余两个输出置0。

[0191]

八、数据选择器

[0192]

数据选择器(mux)具备数据输入端和地址输入端,具备数据输出端。不同数据选择器数据输入端的个数不同、每个数据输入端的位宽不同,地址输入端的位宽不同,但其基本逻辑相同。本发明中使用的有二选一的数据选择器、三选一的数据选择器、七选一的数据选择器、26选1的数据选择器。二选一的数据选择器代表数据输入端有2个,三选一的数据选择器代表输入有3个,以此类推。

[0193]

其中,数据选择器mux1是三选一的数据选择器,单个数据输入宽度为256-bit,输出宽度为256-bit,其逻辑为:

[0194]

当地址输入为0时,把通过第一个数据输入端输入的数据输出;

[0195]

当地址输入为1时,把通过第二个数据输入端输入的数据输出;

[0196]

当地址输入为2时,把通过第三个数据输入端输入端数据输出;

[0197]

当地址输入溢出(即超出0~2的范围),把通过第一个数据输入端输入的数据输出;

[0198]

数据选择器mux2是二选一的数据选择器,单个数据输入宽度为64-bit,输出宽度为64-bit,其逻辑为:

[0199]

当地址输入为0时,把通过第一个数据输入端输入的数据输出;

[0200]

当地址输入为1时,把通过第二个数据输入端输入的数据输出;

[0201]

当地址输入溢出(即超出0~1的范围),把通过第一个数据输入端输入的数据输出。

[0202]

一种quartet轻量级加密算法的实现方法,包括如下过程:

[0203]

(1)载入阶段:

[0204]

算法开始前,状态控制单元将三个使能信号寄存器en1~en3全部置为低电平无效

状态,状态指示寄存器mode取值为0,此时三个状态更新模块关闭,位于状态控制单元的输入端k和输入端iv多轮读入初始化密钥和初始化向量,状态寄存器state0~state3根据k和n的部分位进行指定组合并形成初值,载入阶段结束;

[0205]

(2)初始化阶段:

[0206]

状态控制单元通过输入端cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,同时计数器开始计数,使能信号寄存器en1的值为高电平有效,使能信号寄存器en2和en3为低电平无效,状态指示寄存器mode取值为1,则状态控制单元对输入数据进行如下操作:

[0207]

cout0=cin0

[0208]

cout1=cin1

[0209]

cout2=cin2

[0210]

cout3=cin3^cr_num

[0211]

其中,cr_num是轮常数生成模块根据状态控制单元中计数器输出的计数值cnt而产生的初始化每轮需要的轮常数;cout0~cout3为状态控制单元的输出;

[0212]

多路开关根据状态指示寄存器mode的值将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3(取值为0、1、2、4、5、6时将状态控制单元的输出cout0~cout3送入状态更新模块一的输入s1_x0~s1_x3;取值为3时则将状态控制单元的输出cout0~cout3送入状态更新模块二的输入s2_x0~s2_x3;取值为7时则将状态控制单元的输出cout0~cout3送入状态更新模块三的输入s3_x0~s3_x3);状态更新模块一接收到有效使能信号后,通过扩散运算单元的与或非操作及循环移位,获得一次扩散运算的结果;而数据选择器mux1根据状态指示寄存器mode的取值将状态更新模块一的输出s1_s0~s1_s3与状态寄存器state0~state3一一对应相连,进而更新一次状态寄存器组的值(取值为0、1、2、4、5、6时将状态更新模块一的输出s1_s0~s1_s3送入状态寄存器组state0~state3,取值为3则将状态更新模块二的输出s2_s0~s2_s3送入状态寄存器组state0~state3,取值为7则将状态更新模块三的输出s3_s0~s3_s3送入状态寄存器组state0~state3)。

[0213]

当下一次时钟到达时,使能信号寄存器en1仍然有效,使能信号寄存器en2和en3均无效,状态指示寄存器mode的值为1,状态控制单元继续通过端口cin0~cin3从状态寄存器组读入4个64-bit的数据(该值就是上次的运算结果),操作同上;多路开关仍将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3,状态更新模块一重复进行扩散运算及与轮常数异或的计算,数据选择器mux1根据状态指示寄存器mode的取值将状态更新模块一的输出s1_s0~s1_s3送入状态寄存器state0~state3,如此循环直至当计数器计数值到达24时,状态控制单元将使能信号寄存器en1置为低电平,状态指示寄存器mode的值为2,状态控制单元对读入的cin0~cin3进行如下操作:

[0214]

cout0=cin0^k[63:0]

[0215]

cout1=cin1^k[127:64]

[0216]

cout2=cin2

[0217]

cout3=cin3

[0218]

其中,k为载入阶段多轮读入的初始化密钥key;

[0219]

根据状态指示寄存器mode的取值,多路开关仍将状态控制单元的输出cout0~

cout3连接到状态更新模块一的输入s1_x0~s1_x3;由于状态控制单元一已被关闭,所以最终计算结果不会进行扩散运算而是被直接输出;数据选择器mux1根据状态指示寄存器mode的取值将状态更新模块一的输出s1_s0~s1_s3送入状态寄存器state0~state3中,至此初始化阶段结束;

[0220]

(3)处理关联数据阶段:

[0221]

状态控制单元通过端口cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,通过位于状态控制单元的端口adi读入用户输入的8-bit关联数据adi,并将使能信号寄存器en2置为高电平有效,使能信号寄存器en1和en3置为低电平无效,状态指示寄存器mode取值置为3,则状态控制单元对输入数据进行如下操作:

[0222]

cout0=cin0

[0223]

cout1=cin1^adi

[0224]

cout2=cin2

[0225]

cout3=cin3

[0226]

多路开关根据状态指示寄存器mode的值,将状态控制单元的输出cout0~cout3连接到状态更新模块二的输入s2_x0~s2_x3;状态更新模块二接收到有效使能信号后通过扩散运算单元的与或非操作及循环移位,获得一次扩散运算的结果;而数据选择器mux1根据状态指示寄存器mode的取值,将状态更新模块二的输出s2_s0~s2_s3与状态寄存器state0~state3一一对应相连,进而更新一次状态寄存器组的值(该值即为1次扩散运算的结果);如此循环直至当关联数据全部处理完成后,此时计数器计数值到达指定数,状态控制单元将使能信号寄存器en2置为低电平,使能信号寄存器en1置为高电平,此时状态指示寄存器mode的值变为4,状态控制单元通过端口cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,并根据状态指示寄存器mode的取值做如下操作:

[0227]

cout0=cin0

[0228]

cout1=cin1

[0229]

cout2=cin2

[0230]

cout3=cin3

[0231]

多路开关将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3,由于状态更新模块二已被关闭,而状态更新模块一接收到了有效使能信号,因此状态更新模块一开始进行扩散运算,数据选择器mux1根据状态指示寄存器mode的取值将状态更新模块一的输出s1_s0~s1_s3送入状态寄存器state0~state3中,如此循环12个时钟周期;12轮状态更新结束后,状态控制单元将使能信号寄存器en1~en3全部置为低电平无效,状态指示寄存器mode取值为5,此时对获取的4个64-bit的数据cin0~cin3做如下操作:

[0232]

cout0=cin0

[0233]

cout1=cin1

[0234]

cout2=cin2

[0235]

cout3=cin3^1

′

b1

[0236]

其中,1’b1代表1位二进制数1;多路开关仍将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3;由于状态更新模块一已被关闭,因此最终计算结果不会进行扩散运算而是被数据选择器mux1直接送入状态寄存器state0~state3中,至

此,处理关联数据阶段结束;

[0237]

(4)加密数据及密钥流生成阶段:

[0238]

关联数据处理结束后,明文处理模块接收到外部用户输入的高电平flag信号,状态控制单元通过端口mi读入完整的64-bit明文,并将使能信号寄存器en2、en3均置为低电平无效,使能信号寄存器en1置为高电平有效,状态指示寄存器mode取值为6;状态控制单元通过端口cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,并根据状态指示寄存器mode的取值做如下操作:

[0239]

cout0=cin0^mi[0240]

cout1=cin1

[0241]

cout2=cin2

[0242]

cout3=cin3

[0243]

多路开关根据mode的取值将状态控制单元的输出cout0~cout3连接到状态更新模块一的输入s1_x0~s1_x3;状态更新模块一接收到有效使能信号后,进行一次扩散运算;而数据选择器mux1根据多路开关根据mode的取值,将状态更新模块一的输出s2_s0~s2_s3与状态寄存器state0~state3一一对应相连,进而更新一次状态寄存器组的值(该值即为1次扩散运算的结果),此时密钥流生成模块开始工作,从状态寄存器组中取值,并根据其内部逻辑生成密钥流;如此循环直至完整明文全部处理完成,此时计数器计数值到达指定数,flag输入即将变为0;此后,flag输入变为低电平,明文处理模块对不完整明文进行处理,根据不完整明文的长度length(`m),明文处理模块选择对应填充好的64-bit明文输出,由于使能信号寄存器en1仍为高电平,使能信号寄存器en2、en3为低电平,状态指示寄存器mode的值仍为6,因此状态控制单元对读入数据cin0~cin3的操作以及状态更新模块以的工作过程与对完整明文处理时的完全相同;

[0244]

当明文全部处理完毕后,状态控制单元将使能信号寄存器en1、en2置为低电平无效,使能信号寄存器en3置为高电平有效,状态指示寄存器mode取值为7,状态控制单元通过端口cin0~cin3从状态寄存器组中获取4个64-bit的数据cin0~cin3,并根据mode的取值做如下操作:

[0245]

cout0=cin0

[0246]

cout1=cin1

[0247]

cout2=cin2

[0248]

cout3=cin3

[0249]

多路开关根据状态指示寄存器mode的取值将状态控制单元的输出cout0~cout3连接到状态更新模块三的输入s3_x0~s3_x3,状态更新模块一和状态更新模块二关闭,状态更新模块三接收到有效使能信号后进行一次扩散运算,数据选择器mux1根据状态指示寄存器mode的取值,将状态更新模块三的输出s3_s0~s3_s3与状态寄存器state0~state3一一对应相连,进而更新一次状态寄存器组的值,密钥流生成模块继续从状态寄存器组中取值,并根据其内部逻辑生成密钥流,如此循环共需24轮;

[0250]

(5)生成认证标签阶段:

[0251]

当进行至第23轮时,数据选择器mux2将状态控制单元输出的k[63:0](即初始化密钥key的低64位)选择输出,与生成的密钥流逐位异或,生成认证标签tag的低64位;第24轮

时,数据选择器mux2将状态控制单元输出的k[127:64](即初始化密钥key的高64位)选择输出,与生成的密钥流逐位异或,生成认证标签tag的高64位,至此认证标签生成结束。

[0252]

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1