三阶截点测试电路的制作方法

1.本实用新型涉及射频通信技术领域,特别涉及一种三阶截点测试电路。

背景技术:

2.在射频或微波多载波通信系统中,三阶交调截取点ip3(third-orderintercept point)是一个衡量线性度或失真的重要指标。交调失真对模拟微波通信来说,会产生邻近信道的串扰,对数字微波通信来说,会降低系统的频谱利用率,并使误码率变化,因此,在系统设计的时候,会尽量提高三阶交调截取点的值,以提高线性度,减少失真。

3.ip3通常用两个输入音频进行测试,两个输入音频是指两个频率靠得比较近的射频或微波频率信号。专利《一种功率放大器的测试方法、装置及计算机可读存储介质》(公开号cn113267718a)公开了一种三阶互调系数的计算方法,包括步骤:获取测试信号基于待测试功率放大器的输入输出特性函数,其中,所述测试信号包括双音信号;根据所述输入输出特性函数,得到所述测试信号经所述待测试功率放大器后的测试输出信号;对所述测试输出信号进行幅相失真拟合,得到所述待测试功率放大器基于幅相失真作用下的非线性输出信号;根据所述非线性输出信号,得到所述待测试功率放大器的理论三阶互调系数;将所述测试信号输入所述待测试功率放大器,以得到所述待测试功率放大器的实际三阶互调系数;获取所述待测试功率放大器的信号增益;根据所述理论三阶互调系数和所述信号增益,得到所述待测试功率放大器的三阶交调截取点的理论横纵坐标,以及根据所述实际三阶互调系数和所述信号增益,得到所述待测试功率放大器的三阶交调截取点的实际横纵坐标;根据所述三阶交调截取点的理论横纵坐标以及实际横纵坐标,得出所述待测试功率放大器的非线性测试结果。上述公开的内容,侧重于方法的改进,一方面计算出待测试功率放大器的理论三阶互调系数,从而借助该理论三阶互调系数以及待测试功率放大器的信号增益,得出待测试功率放大器的三阶交调截取点的理论横纵坐标,另一方面还将测试信号输入待测试功率放大器,以得出其测试数据,从而得出实际三阶互调系数,以便通过实际三阶互调系数以及信号增益,得出三阶交调截取点的实际横纵坐标,最后通过二者的比较得出测试结果,大大提高了测试的准确度。

4.但是,作为最接近的现有技术,该方案并没有公开将双音信号输入到被测器件的电路,也并没有公开用于三阶交调截取点计算的测试输出信号的产生电路,因此,无法从硬件电路上知晓其实现方案。

技术实现要素:

5.本实用新型针对上述问题,给出了一种三阶截点测试电路,可以快速测试被测器件的三阶截点值。

6.为了实现上述发明目的,本发明提供了以下技术方案:

7.一种三阶截点测试电路,包括第一信号源通路、第二信号源通路、功率合成电路和信号分析通路,

8.所述第一信号源通路用于根据输入的载波信号输出频率为f1的第一路信号;

9.所述第二信号源通路用于根据输入的载波信号输出频率为f2的第二路信号;所述第一路信号和第二路信号是两路幅度相同,输出频率相近的单音信号,并且输出频率f1和f2在被测器件工作频率范围内;

10.所述功率合成电路用于将所述第一路信号和第二路信号合成一路信号,并将合成的一路信号通过输出端口送到被测器件的输入端;

11.所述信号分析通路接收所述被测器件的输出端产生的输出信号,并将所述输出信号转换为用于三阶截点计算的信号。

12.作为本实用新型的优选方案,所述第一信号源通路和所述第二信号源通路的结构相同,包括fpga控制电路、正交数字上变频电路、电调衰减器电路、第一混频电路、第一本振电路、第二混频电路、第二本振电路;

13.所述fpga控制电路用于输出载波生成控制信号到所述正交数字上变频电路;所述正交数字上变频电路根据所述载波生成控制信号输出固定频率的载波信号到所述电调衰减器电路;所述电调衰减器电路用于对所述载波信号进行幅度调理,然后经过滤波衰减后送入所述第一混频电路,与第一本振电路产生的第一本振信号进行混频,得到一个固定的第一中频信号;所述第一中频信号送入第二混频电路,与第二本振电路产生的第二本振信号混频后得到宽带的射频输出信号;所述宽带的射频输出信号经过幅度调理后输出射频信号到所述功率合成电路。

14.作为本实用新型的优选方案,所述电调衰减器电路是由pin二极管、电阻和电容组成的电调衰减器。

15.作为本实用新型的优选方案,得到所述射频信号是所述宽带的射频输出信号经过两级可控数字衰减器调理得到的。

16.作为本实用新型的优选方案,所述信号分析通路包括第一混频电路、第一本振电路、第二混频电路、第二本振电路、ad变换器和fpga数字下变频电路,

17.被测器件的输出信号经过输入调理后,送入第一混频电路,与第一本振电路产生的第一本振信号混频,得到一个固定的第二中频信号;所述第二中频信号经过放大、带通滤波及衰减处理后送到第二混频电路,与第二本振电路产生的第二本振信号混频,得到可以直接进行数字信号处理的第三中频信号,所述第三中频信号经过ad变换器的采样和fpga数字下变频电路的变换后,得到用于三阶截点计算的信号。

18.作为本实用新型的优选方案,本振电路通过锁相环电路来产生本振信号。

19.作为本实用新型的优选方案,所述锁相环电路包括锁相环芯片hmc830、环路滤波器与滤波幅度调理电路,

20.锁相环芯片用于接收参考信号和环路滤波器输出的vtune信号,并且输出cp信号到所述环路滤波器,还输出初始本振信号,所述初始本振信号经过所述滤波幅度调理电路的高通滤波、衰减、放大、低通滤波后,输出本振信号到混频电路。

21.作为本实用新型的优选方案,所述锁相环电路输入端的参考信号来自于 ocxo晶体振荡器,所述ocxo晶体振荡器产生的参考输出信号通过功分器分成两路信号,分别经过放大、衰减和滤波后,送到锁相环电路作为锁相环芯片hmc830的参考信号。

22.作为本实用新型的优选方案,所述环路滤波器为无源环路滤波器。

23.作为本实用新型的优选方案,所述无源环路滤波器包括第一电阻、第二电阻、第三电阻、第一电容、第二电容、第三电容、第四电容,

24.第一电阻与第二电容串联构成第一支路,第一电阻和第一支路并联于第二电阻的第一端和地之间,第三电阻与第二电阻串联,并且第三电容并联于第三电阻的第一端和地之间,第四电容并联于第三电阻的第二端和地之间。

25.与现有技术相比,本发明的有益效果:

26.本实用新型给出了一种截点测试电路,电路包括第一信号源通路、第二信号源通路、功率合成电路和信号分析通路,第一信号源通路和第二信号源通路输出两路幅度相同,输出频率相近的单音信号,并且两个通路的输出频率在被测器件工作频率范围内;功率合成电路用于将两路单音信号合成一路信号,并将合成的一路信号输入到被测器件的输入端;信号分析通路接收被测器件的输出端产生的输出信号,并将输出信号转换为用于三阶截点计算的信号。该测试电路为快速测试被测器件的三阶截点给出了硬件电路支撑。

附图说明:

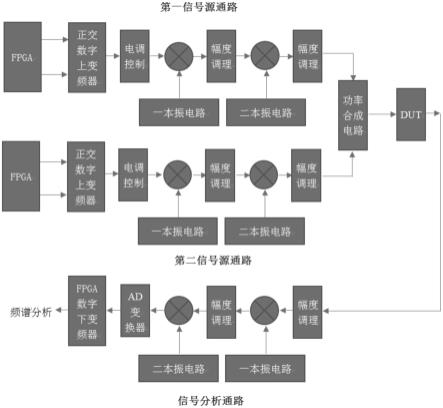

27.图1为实施例1中三阶截点测试电路整体硬件框图;

28.图2为实施例1中第一信号源通路的输出幅度调理电路的原理图;

29.图3为实施例1中第一信号源通路的第一混频和第二混频电路原理图;

30.图4为实施例1中第一信号源通路中第一次混频所用到的第一本振信号产生电路的原理图;

31.图5为实施例1中第一信号源通路中第二次混频所用到的第二本振信号产生电路的原理图;

32.图6为实施例1中第二信号源通路的第一混频和第二混频电路以及功率合成电路的原理图;

33.图7为实施例1中第二信号源通路中第一次混频所用到的第一本振信号产生电路的原理图;

34.图8为实施例1中第二信号源通路中第二次混频所用到的第二本振信号产生电路的原理图;

35.图9为实施例1中信号分析通路的输入幅度调理电路的原理图;

36.图10为实施例1中信号分析通路的第一混频和第二混频电路原理图;

37.图11为实施例1中信号分析通路中第一次混频所用到的第一本振信号产生电路的原理图;

38.图12为实施例1中信号分析通路中第二次混频所用到的第二本振信号产生电路的原理图;

39.图13为实施例1中锁相环电路原理图;

40.图14为实施例1中具体的锁相环电路的参考信号原理图。

具体实施方式

41.下面结合试验例及具体实施方式对本发明作进一步的详细描述。但不应将此理解为本发明上述主题的范围仅限于以下的实施例,凡基于本

技术实现要素:

所实现的技术均属于本

发明的范围。

42.实施例1

43.一种三阶截点测试电路,整体硬件框图如图1所示,包括第一信号源通路、第二信号源通路、功率合成电路和信号分析通路。第一信号源通路包括fpga 控制电路、正交数字上变频电路、第一混频电路、第一本振电路、第二混频电路、第二本振电路;第二信号源通路包括fpga控制电路、正交数字上变频电路、第一混频电路、第一本振电路、第二混频电路、第二本振电路;信号分析通路包括第一混频电路、第一本振电路、第二混频电路、第二本振电路、ad 变换器和fpga数字下变频器电路。

44.三阶截点的测试电路主要功能就是获取测试被测器件三阶截点值的信号。电路中的第一信号源通路部分和第二信号源通路部分产生两路幅度相同、频率相近的单音信号,通过功率合成电路后,输出到被测器件(dut),被测器件 (dut)的输出值再送到本电路中的信号分析通路部分,信号分析通路部分输出用于三阶截点计算的信号,用于三阶截点计算的信号通过频谱分析测量出单音信号的输出功率值和三阶交调的功率值,最后在控制器单元中计算出被测器件(dut)的三阶截点值。

45.1、第一信号源通路

46.由fpga控制正交数字上变频器产生一个固定频率的载波信号,该信号经过一个由pin二极管和电阻电容组成的电调衰减器,对载波信号进行幅度调理,然后经过滤波衰减后送入第一混频电路,与第一本振电路产生的一本振信号混频进行混频,得到一个固定的高中频信号。该中频信号经过放大器放大,带通滤波器滤波及衰减器衰减等信号处理后送入第二混频器,与二本振电路产生的二本振信号混频后可得到宽带的射频输出信号,最后经过两级可控数字衰减器调理得到需要的射频信号作为输出。假设第一路信号频率为f1,幅度为p

in

。

47.第一信号源通路的输出幅度调理电路的原理图如图2所示,输出幅度调理电路是第二次混频后输出信号的调理通路;第一信号源通路的第一混频和第二混频电路原理图如图3所示;第一信号源通路中第一次混频所用到的第一本振信号产生电路的原理图如图4所示;第一信号源通路中第二次混频所用到的第二本振信号产生电路的原理图如图5所示。

48.2、第二信号源通路

49.第二信号源的产生原理同第一信号源近似,只是两路信号的频率不同。通过幅度校准,可以使得两路信号的幅度相同。假设第二路信号频率为f2,幅度为p

in

。

50.第二信号源通路的第一混频和第二混频电路以及功率合成电路的原理图如图6所示;第二信号源通路中第一次混频所用到的第一本振信号产生电路的原理图如图7所示;第二信号源通路中第二次混频所用到的第二本振信号产生电路的原理图如图8所示。

51.3、功率合成输出

52.两个信号源通路产生的两路频率近似、幅度相同的载波信号,通过一个功率合成电路合成成一路信号,通过输出端口送到被测器件(dut)的输入端,被测器件(dut)的输出信号再通过本电路的输入端口进入信号分析通路进行信号分析。功率合成电路的详细原理图如图6所示,图6中将两个信号源通路产生的两路频率近似、幅度相同的载波信号是通过型号为adp-2-1w+的功率合成芯片实现的。

53.4、信号分析通路

54.被测器件(dut)的输出信号通过输入端口,进入信号分析通路,该信号经过输入调理后,送入第一混频电路,与第一本振电路产生的第一本振信号混频,得到一个固定的中频信号;该中频信号经过放大器放大,射频带通滤波器滤波及衰减器衰减等信号处理后送到第二级混频电路,与第二本振电路产生的固定的第二本振信号混频,得到一个可以直接进行数字信号处理的中频信号,该信号经过带通滤波器滤波后,进入中频调理电路进行中频调理,进入中频 ad采样及数字化处理单元进行数字中频变换、滤波和检波,得到其频域信号,完成对输入信号的频谱计算。

55.信号分析通路的输入幅度调理电路的原理图如图9所示,该输入幅度调理电路是将输入到信号分析通路的信号进行幅度调理,是进行第一混频前的幅度调理电路;信号分析通路的第一混频和第二混频电路原理图如图10所示;信号分析通路中第一次混频所用到的第一本振信号产生电路的原理图如图11所示;信号分析通路中第二次混频所用到的第二本振信号产生电路的原理图如图 12所示。

56.通过计算可以得到单音信号的输出功率为p

out

,三阶交调分量的频率为 (2f

1-f2)和(2f

2-f1),由于f1和f2的幅度相同,三阶交调分量的输出相同,为 p

imd3

。三阶截点的计算公式如下所示:

57.iip3=p

in

+1/2imd358.oip3=p

out

+1/2imd3=iip3+g

59.其中

60.imd3=p

out-p

imd3

61.g=p

out-p

in

62.上述公式中,iip3为输入三阶截点;oip3为输出三阶截点;p

in

为单音信号的输入功率电平;p

out

为单音信号的输出功率电平;g为被测件(dut)的小信号增益;imd3为三阶互调失真,等于干扰信号的输出功率电平p

out

减去三阶互调量p

imd3

功率电平的值。

63.由上式可以看出,如果测出单音信号的输入/输出功率和三阶互调分量的电平值,就可求出输入/输出三阶截点的值。

64.5、本振产生电路

65.射频部分一共需要六个本振信号,每个信号源通路和射频分析通路各需要两个本振信号,具体的本振产生电路如图4、5、7、8、11和12所示。这些本振信号都是通过包含锁相环芯片hmc830的锁相环电路来产生,锁相环电路原理图如图13所示。锁相环芯片hmc830与环路滤波器构成的锁相环电路产生一个本振信号,经过高通滤波、衰减、放大、低通滤波后输出一个幅度合适的信号到混频器混频。

66.锁相环电路的参考信号来自于一个ocxo晶体振荡器,晶振产生的参考输出信号通过功分器后分成两路信号,分别经过放大、衰减滤波后,送到锁相环电路作为锁相环芯片hmc830的参考信号,本案中具体的锁相环电路的参考信号原理图如图14所示。

67.以上所述仅为本实用新型的较佳实施例而已,并不用以限制本实用新型,凡在本实用新型的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1