显示装置的制作方法

1.本发明涉及一种显示装置。

背景技术:

2.专利文献1公开了一种通过在具备发光元件的显示装置中进行脉冲型驱动来改善动态图像模糊的方法。现有技术文献专利文献

3.专利文献1:日本国公开特许公报「特开2007-256728」

技术实现要素:

发明要解决的问题

4.如专利文献1所示,在利用具备发光元件的显示装置进行脉冲式驱动的情况下,存在由于高亮度的发光而发光元件的劣化很容易发展这样的问题。解决问题的方案

5.本发明的一方面所涉及的显示装置具备:多条数据信号线,其与数据信号线驱动电路连接;多条扫描信号线,其与扫描信号线驱动电路连接,所述多条扫描信号线以与所述多条数据信号线交叉的方式设置;多个像素电路,与所述多条数据信号线和所述多条扫描信号线的交叉部对应地设置,在各像素电路中,设置有由电流驱动的发光元件、控制所述发光元件的电流的驱动晶体管、切换电路和与所述切换电路连接的第一电容元件和第二电容元件,所述切换电路在1帧期间所包含的第一期间,将所述第一电容元件与所述驱动晶体管的控制端子连接,在所述1帧期间所包含的、接着所述第一期间的第二期间,将所述第二电容元件与所述驱动晶体管的控制端子连接。发明效果

6.根据本发明的一个方式,能够在抑制发光元件的劣化的同时提高显示(特别是动态图像显示)的品质。

附图说明

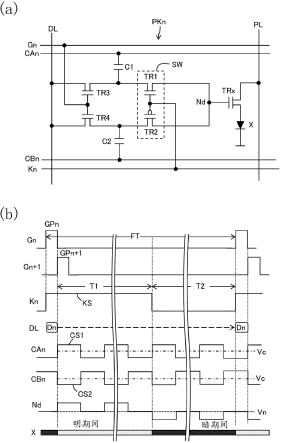

7.图1的(a)是第一实施方式的显示装置的平面示意图,图1的(b)是显示区域的剖视图。图2的(a)是第一实施方式的像素电路图,图2的(b)是像素电路的驱动方法的时序图。图3的(a)、(b)是示出第一实施方式中的像素数据和各期间的亮度的设定例的表,图3的(c)是示出比较例的表。图4是表示第一实施方式的动态图像显示质量的改善的说明图。图5是主干布线与电容信号线的连接关系的电路图。

图6是表示向各电容信号线供给的电容信号和各级的栅极脉冲的流程图。图7是各像素电路的显示例的示意图。图8是表示主干布线与电容信号线的连接关系的另一例的电路图。图9是各像素电路的显示例的示意图。图10的(a)是第二实施方式的像素电路图,图10的(b)是像素电路的驱动方法的时序图。图11的(a)是第三实施方式的像素电路图,图11的(b)是像素电路的驱动方法的时序图。图12是表示第四实施方式的像素电路的电路图。图13是示出图12所示的像素电路的驱动方法的时序图。图14是表示第五实施方式的像素电路的电路图。图15是示出图14所示的像素电路的驱动方法的时序图。图16是表示第五实施方式的像素电路的变形例的电路图。图17是示出图16所示的像素电路的驱动方法的时序图。图18的(a)是表示各实施方式(在高灰度区域中不进行亮度限制的情况)的数据电压_亮度特性的曲线图,图18的(b)是表示数据电压(在高灰度区域中不进行亮度限制的情况)的校正特性的曲线图。图19的(a)是表示各实施方式(在高灰度区域进行亮度限制的情况)的数据电压_亮度特性的曲线图,图19的(b)是表示数据电压(在高灰度区域进行亮度限制的情况)的校正特性的曲线图。

具体实施方式

8.〔第一实施方式〕图1的(a)是第一实施方式的显示装置的平面示意图,图1的(b)是显示区域的剖视图。如图1所示,显示装置2具备显示区域da、数据信号线驱动电路sd、扫描信号线驱动电路gd、切换信号生成电路kc、以及控制数据信号线驱动电路sd、扫描信号线驱动电路gd和切换信号生成电路kc的显示控制电路dcc。

9.在显示区域da中设置有多个像素电路(包括像素电路pkn)、多个数据信号线(包括数据信号线dl)、与多条数据信号线交叉的多条扫描信号线(包括扫描信号线gn)、以及多条切换信号线(包括切换信号线kn)。多条数据信号线与数据信号线驱动电路sd连接,多条扫描信号线与扫描信号线驱动电路gd连接,多条切换信号线与切换信号生成电路kc连接。

10.如图1所示,在显示装置2中,在基板12上按顺序形成有阻挡层3、薄膜晶体管层4、顶部发光(向上层侧发光)型的发光元件层5以及密封层6,在显示区域da分别形成有包括发光元件x的多个像素电路。

11.基板12是玻璃基板或以聚酰亚胺等树脂为主要成分的柔性基材,例如,也可以由2层聚酰亚胺膜及夹在该些之间的无机膜构成基板12。阻挡层(底涂层)3是防止水、氧等异物的侵入的无机绝缘层,例如能够使用氮化硅、氧化硅等构成。

12.如图1所示,薄膜晶体管层4包括:比阻挡层3更上层的半导体层ps;比半导体层ps更上层的栅极绝缘膜16;比栅极绝缘膜16更上层的第一金属层(包括栅电极ge及扫描信号

线gn);比第一金属层更上层的第一层间绝缘膜18;比第一层间绝缘膜18更上层的第二金属层(包括切换信号线kn);比第二金属层更上层的第二层间绝缘膜20;比第二层间绝缘膜20更上层的第三金属层(包括数据信号线dl);以及比第三金属层更上层的平坦化膜21。

13.半导体层ps例如是低温形成的多晶硅(ltps),以包含栅电极ge及半导体层ps的方式构成晶体管tr。关于半导体层ps,可以将晶体管的沟道以外的区域导体化。

14.第一金属层、第二金属层及第三金属层例如由包含铝、钨、钼、钽、铬、钛及铜中的至少一种的金属的单层膜或多层膜构成。

15.栅极绝缘膜16、第一层间绝缘膜18以及第二层间绝缘膜20可以由例如通过cvd法形成的氧化硅(siox)膜、氮化硅(sinx)膜或它们的层叠膜构成。平坦化膜21能够由例如聚酰亚胺、丙烯酸树脂等能够涂布的有机材料构成。

16.发光元件层5包括:比平坦化膜21更上层的第一电极(下部电极)22、覆盖第一电极22的边缘的绝缘性的边缘覆盖膜23、比边缘覆盖膜23更上层的el(电致发光)层24、比el层24更上层的第二电极(上部电极)25。边缘罩23例如通过在涂覆了聚酰亚胺、丙烯酸树脂等有机材料后利用光刻进行图案化而形成。

17.如图1所示,发光元件层5例如形成发射不同颜色的光的多个发光元件x,各发光元件包括岛状的第一电极22、el层24(包括发光层ek)和第二电极25。第二电极25是多个发光元件共用的整体状的共用电极。

18.发光元件x例如可以是包含有机层作为发光层的oled(有机发光二极管),也可以是包含量子点层作为发光层的qled(量子点发光二极管)。

19.el层24例如构成为从下层侧依次层叠空穴注入层、空穴传输层、发光层ek、电子传输层、电子注入层。发光层通过蒸镀法或喷墨法、光刻法,在边缘覆盖膜23的开口(每个子像素)形成岛状。其他层为岛状或整体(共用层)地形成。另外,也可以构成为不形成空穴注入层、空穴输送层、电子输送层、电子注入层中的一个以上的层。

20.第一电极22例如由ito(indium tin oxide)和ag(银)或包含ag的合金的层叠构成,为光反射性电极。第二电极25(阴极)例如由镁银合金等金属薄膜构成,具有透光性。

21.在发光元件x为oled的情况下,通过第一电极22和第二电极25间的驱动电流,空穴和电子在发光层ek内复合,在由此产生的激子迁移到基底状态的过程中发射光。在发光元件x为qled的情况下,通过第一电极22以及第二电极25之间的驱动电流使空穴和电子在发光层ek内复合,由此产生的激子从量子点的导带能级(conduction band)向价带能级(valence band)跃迁的过程中发出光(荧光)。

22.覆盖发光元件层5的密封层6是防止水、氧等异物渗入发光元件层5的层,例如可以由两层无机密封膜26、28和在它们之间形成的有机膜27构成。

23.图2的(a)是第一实施方式的像素电路图,图2的(b)是像素电路的驱动方法的时序图。像素电路pkn包括:发光元件x;驱动晶体管trx;包括n型的第一晶体管tr1和p型的第二晶体管tr2的切换电路sw;第一电容元件c1;第二电容元件c2;n型的第三晶体管tr3;以及n型的第四晶体管tr4。

24.发光元件x的节点经由驱动晶体管trx与high侧的电源线pl(elvdd线)连接,其阴极与low侧的电源线(elvss线)连接。

25.驱动晶体管trx的栅极端子nd经由第一晶体管tr1与第一电容元件c1的一个电极

连接,第一电容元件c1的一个电极经由第三晶体管tr3与数据信号线dl连接,第一电容元件c1的另一个电极与第一电容信号线can连接。

26.驱动晶体管trx的栅极端子nd经由第二晶体管tr2与第二电容元件c2的一个电极连接,第二电容元件c2的一个电极经由第三晶体管tr3与数据信号线dl连接,第二电容元件c2的另一个电极与第二电容信号线cbn连接。

27.第一晶体管tr1以及第二晶体管tr2的栅极端子与切换信号线kn连接,第三晶体管tr3以及第四晶体管tr4的栅极端子与对应于本级的扫描信号线gn连接。切换信号线kn、第一电容信号线can和第二电容信号线cbn与扫描信号线gn平行地延伸。

28.提供给切换信号线kn的切换信号ks在被包含在1帧期间ft中的接着扫描信号线gn的选择期间(栅极脉冲gpn的激活期间)的第一期间t1中为“high”,在被包含在1帧期间ft中的接着第一期间t1的第二期间t2中为“low”。由此,切换电路sw在第一期间t1,第一电容元件c1与驱动晶体管trx的控制端子nd连接,在第二期间t2,第二电容元件c2与驱动晶体管trx的控制端子nd连接。第一期间t1和第二期间t2例如为相同长度,各自比1/60秒短。

29.提供给第一电容信号线can的第一电容信号cs1和提供给第二电容信号线cbn的第二电容信号cs2是第一电平(low)和高于第一电平的第二电平(high)周期性地交替的信号,第一电平和第二电平的中央值为vc。

30.另外,在图2中,在与本级对应的扫描信号线gn的选择期间,第一电容信号cs1为第一电平(low),并且第二电容信号cs2为第二电平(high),因此驱动晶体管trx的栅极端子nd的有效电压在第一期间t1比与像素数据dn对应的值vn高,在第二期间t2比与像素数据dn对应的值vn低。具体而言,将cs1/cs2的振幅的一半(第一或第二电平与vc之差)设为vad,第一期间t1的nd的有效电压为vn+k1

×

vad,第二期间t2的nd的有效电压为vn-k2

×

vad(k1是与第一电容元件c1的电容对应的常数,k2是与第二电容元件c2的电容对应的常数)。

31.此外,为了抑制发光元件x的劣化,优选满足数据信号线dl的信号延迟(充电期间)<第一容量信号cs1以及第二电容信号cs2的周期<发光元件x的信号延迟(电流的上升期间)的关系。

32.因此,像素数据dn为中间灰度时,在第一期间t1流经发光元件x的有效电流比第二期间t2流经发光元件x的有效电流大,第一期间t1中的发光元件x的有效亮度比第二期间t2中的发光元件x的有效亮度高。在第一实施方式中,第一期间为明期间,第二期间为暗期间,发光元件x的第一期间及第二期间的平均亮度相当于与像素数据dn对应的像素电路pkn的亮度。

33.图3的(a)(b)是示出第一实施方式中的像素数据和各期间的亮度的设定例的表,图3的(c)是示出比较例的表。对发光元件x的亮度设置上限的情况(重视元件劣化抑制的情况)能够例如如图3的(a)那样设定。另外,在发光元件x的亮度未设置上限的情况下(重视显示质量的情况),例如可以如图3的(b)那样设定。通过如图3的(a)、(b)那样进行设定,与使1帧期间为相同亮度的比较例(参照图3的(c))相比能够消除动态图像模糊。另外与将1帧期间的一部分设为非点亮的脉冲型的驱动相比,能够抑制发光元件x的劣化。

34.图4是的第一实施方式的动态图像显示质量的改善的说明图。例如,关于向右移动的矩形(50%的亮度)的显示,可知第一实施方式的情况(图4的(b))下的动态图像模糊部比将1帧期间设为同一亮度的现有的情况(图4的(a))下的动态图像模糊部小(接近脉冲驱动

的情况(图4的(c)),动态图像的显示品质得到改善。

35.图5是主干布线与电容信号线的连接关系的电路图。图6是向各电容信号线供给的电容信号和各级的栅极脉冲的流程图。图7是各像素电路的显示例的示意图。

36.在图5中,对于与像素电路pkn(本级)连接的第一电容信号线can和第二电容信号线cbn、与像素电路pkn+1(第一个后一级)连接的第一电容信号线can+1和第二电容信号线cbn+1、与像素电路pkn+2(第二个后一级)连接的第一电容信号线can+2和与第二电容信号线cbn+2、与像素电路pkn+3(第三个后一级)连接的第一电容信号线can+3和第二电容信号线cbn+3,将第一电容信号线cn和第二电容信号线cbn+2连接到第一主干布线m1,将第二电容信号线cbn和第一电容信号线can+2连接到第二主干布线m2,将第一电容信号线can+1和第二电容信号线cbn+3连接到第一主干布线m3上,将第一电容信号线can+3和第二电容信号线cbn+1连接到第四主干布线m4上。

37.如图6所示,以提供给第一主干布线m1的电容信号cs1为基准,提供给第二主干布线m2的电容信号cs2超前180

°

相位(反相位),提供给第三主干布线m3的电容信号超前90

°

相位,提供给第四主干布线m4的电容信号的超前270

°

相位。

38.在栅极脉冲gpn的激活期间,第一电容信号线can的电容信号(第一电容信号cs1)为low,第二电容信号线cbn的电容信号(第二电容信号cs2)为high,在栅极脉冲gpn+1的激活期间,第一电容信号线can+1的电容信号为low,第二电容信号线cbn+1的电容信号为high,在栅极脉冲gpn+2的激活期间,第一电容信号线can+2的电容信号为low,第二电容信号线cbn+2的电容信号为high,在栅极脉冲gpn+3的激活期间,第一电容信号线cn+3的电容信号为low,第二电容信号线cbn+3的电容信号为high。像素电路pkn

·

pkn+1

·

pkn+2

·

pkn+3分别与切换信号线kn

·

kn+1

·

kn+2

·

kn+3连接。

39.这样,如图7所示那样,关于各像素电路(pkn

·

pkn+1

·

pkn+2

·

pkn+3),能够使第一期间t1为明期间,使第二期间t2为暗期间。

40.图8是主干布线与电容信号线的连接关系的另一示例的电路图。图9是各像素电路的显示例的示意图。

41.在图8中,将第一电容信号线can以及第一电容信号线can+2与第一主布线m1连接,将第二电容信号线cbn以及第一电容信号线cbn+2与第二主布线m2连接,将第一电容信号线can+1以及第一电容信号线can+3与第三主干布线m3连接,将第二电容信号线cbn+1以及第二电容信号线cbn+3与第四主干布线m4连接。

42.这样,如图9所示,对于像素电路pkn

·

pkn+1分别能够使第一期间t1为明期间,使第二期间t2为暗期间,对于像素电路pkn+2

·

pkn+3分别能够使第一期间t1为暗期间,使第二期间t2为明期间。

43.在第一实施方式中,优选第一电容信号cs1和第二电容信号cs2的半周期(high)或维持low的期间比发光元件x的电流的上升期间短。这样对发光元件x的劣化抑制是激活的。第一电容信号cs1和第二电容信号cs2的半周期例如为水平扫描期间(1h)的整数倍。

44.在第一实施方式中,帧频率(改写频率)与输入视频信号相同,切换信号ks的频率(例如,t1=t2的倒数)以n为2以上的自然数,为帧频率的n倍(例如,2倍~8倍)。

45.在图2的第一实施方式中,也可以在发光元件x的阴极与驱动晶体管trx的栅极端子nd之间插入恒压二极管,设定发光元件x的亮度上限。

46.〔第二实施方式〕图10的(a)是第二实施方式的像素电路图,图10的(b)是像素电路的驱动方法的时序图。在图10中,也可以将发光元件x的阳极和驱动晶体管trx的源极端子经由发光控制晶体管tre连接,将发光控制晶体管tre的栅极端子与发光控制线en连接。发光控制线en在栅极脉冲gpn聚焦后设为激活(high),在下一栅极脉冲gpn上升前设为非激活(low)。通过这样,能够防止选择期间的发光。

47.〔第三实施方式〕图11的(a)是第三实施方式的像素电路图,图11的(b)是像素电路的驱动方法的时序图。与第一实施方式不同,本实施方式使用具有相同极性的第一晶体管tr1和第二晶体管tr2。在图11中,n型第一晶体管tr1的栅极端子连接到切换信号线kan,n型第二晶体管tr2的栅极端子连接到切换信号线kbn。

48.切换信号线kan在扫描信号线gn的选择期间(栅极脉冲gpn上升的期间)和第一期间t1激活(high),在第一期间t1结束(第二期间t2开始)时非激活(low)。切换信号线kbn在扫描信号线gn的选择期间激活(high),在第一期间t1开始时为非激活(low),在第一期间t1结束(第二期间t2开始)时为激活(high)。

49.以上以n型说明了第一晶体管tr1和第二晶体管tr2,但也可以都是p型。这样,通过采用具有相同极性的晶体管,可以简化晶体管的制造过程。

50.〔第四实施方式〕图12是表示第四实施方式的像素电路的电路图。在图12中,提供第三电容信号线ccn和第四电容信号线cdn。像素电路pkn包括包含发光元件x、驱动晶体管trx、n型第一晶体管tr1、n型第二晶体管tr2、n型第五晶体管tr5、n型第六晶体管tr6的切换电路sw、第一电容元件c1、第二电容元件c2、第三电容元件c3、第四电容元件c4、n型第三晶体管tr3、n型第四晶体管tr4、n型第七晶体管tr7以及n型第八晶体管tr8。在第四实施方式中,作为保持电容的四个第一电容元件c1、第二电容元件c2、第三电容元件c3和第四电容元件c4经由切换电路sw连接到共用驱动晶体管trx的控制端子。

51.驱动晶体管trx的栅极端子nd经由第一晶体管tr1与第一电容元件c1的一个电极连接,第一电容元件c1的一个电极经由第三晶体管tr3与数据信号线dl连接,第一电容元件c1的另一个电极与第一电容信号线can连接。

52.驱动晶体管trx的栅极端子nd经由第二晶体管tr2与第二电容元件c2的一个电极连接,第二电容元件c2的一个电极经由第三晶体管tr3与数据信号线dl连接,第二电容元件c2的另一个电极与第二电容信号线cbn连接。

53.驱动晶体管trx的栅极端子nd经由第五晶体管tr5与第一电容元件c3的一个电极连接,第三电容元件c3的一个电极经由第七晶体管tr7与数据信号线dl连接,第三电容元件c3的另一个电极与第三电容信号线ccn连接。

54.驱动晶体管trx的栅极端子nd经由第六晶体管tr6与第四电容元件c4的一个电极连接,第四电容元件c4的一个电极经由第八晶体管tr8与数据信号线dl连接,第四电容元件c4的另一个电极与第四电容信号线cdn连接。

55.第一晶体管tr1的栅极端子连接到切换信号线kan,第二晶体管tr2的栅极端子连接到切换信号线kbn,而第五晶体管tr5的栅极端子连接到切换信号线kcn,第六晶体管tr6

的栅极端子连接到切换信号线kdn,第三晶体管tr3、第四晶体管tr4、第七晶体管tr7和第八晶体管tr8的栅极端子连接到与本级对应的扫描信号线gn。

56.另外,第一电容信号线can连接到第一主干布线m1,第二电容信号线cbn连接到第二主干布线m2,第三电容信号线ccn连接到第五主干布线m5,第四电容信号线cdn连接到第六主干布线m6。

57.图13是示出图12所示的像素电路的驱动方法的时序图。在图13中,1帧期间ft被划分为第一期间t1至第四期间t4。在与本级对应的扫描信号线gn的选择期间,第一电容信号cs1和第三电容信号cs3为第一电平(low),并且第二电容信号cs2和第四电容信号cs4为第二电平(high)。

58.在第一期间t1,切换信号线kan的电为变为“high”,并且第一电容信号cs1变为“high”。在第二期间t2,切换信号线kbn的电为变为“high”,并且第二电容信号cs2变为“low”。在第三期间t3,切换信号线kcn的电为变为“high”,并且第三电容信号cs3变为“high”。在第四期间t4,切换信号线kdn的电为变为“high”,并且第四电容信号cs4变为“low”。因此,第一期间t1可以是明期间,第二期间t2可以是暗期间,第三期间t3可以是明期间,第四期间t4可以是暗期间,并且可以是四倍速度驱动。

59.〔第五实施方式〕图14是表示第五实施方式的像素电路的电路图。图15是示出图14所示的像素电路的驱动方法的时序图。在图14中,将发光元件x、第一电容元件c1和第二电容元件c2、栅极端子连接到像素电路pkn的前一级(n-1级)扫描信号线gn-1的初始化晶体管tri、栅极端子与本级(n级)的扫描信号线gn连接的补偿晶体管trs、栅极端子与本级(n级)的扫描信号线gn连接的写入控制晶体管trw、控制发光元件x的电流的驱动晶体管trx、栅极端子与发光控制线em(n级)连接的电源供给晶体管trp、栅极端子与发光控制线em(n级)连接的发光控制晶体管tre、栅极端子包括连接至本级(n级)扫描信号线gn的设置晶体管trj。

60.驱动晶体管trx的栅极端子nd经由初始化晶体管tri连接到初始化电源线il。驱动晶体管trx的源极经由写入控制晶体管trw与数据信号线dl连接,并且经由电源供给晶体管trp与high侧电源布线pl连接。驱动晶体管trx的漏极端子经由发光控制晶体管tre连接到发光元件x的阳极,并且经由补偿晶体管trs连接到驱动晶体管trx的栅极端子nd。初始化电源线il和发光元件x的阴极(共同电极)例如被供给low侧的电源电源(elvss)。

61.驱动晶体管trx的栅极端子nd经由第一晶体管tr1连接到第一电容元件c1的一个电极,而第一电容元件c1的另一个电极连接到第一电容信号线can。

62.驱动晶体管trx的栅极端子nd经由第二晶体管tr2连接到第二电容元件c2的一个电极,并且经由设置晶体管trj连接到第二电容元件c2的一个电极。第二电容元件c2的另一个电极连接到第二电容信号线cbn。

63.第一晶体管tr1和第二晶体管tr2的栅极端子连接到切换信号线kn。切换信号线kn、第一电容信号线can和第二电容信号线cbn与扫描信号线gn平行地延伸。

64.如图15所示,提供给切换信号线kn的切换信号ks在1帧期间ft所包含的扫描信号线gn的选择期间(栅极脉冲gpn的激活期间)和1帧期间ft所包含的、扫描信号线gn的选择期间之后的第一期间t1为“high”,在1帧期间ft所包含的、第一期间t1之后的第二期间t2为“low”。由此,切换电路sw在第一期间t1,第一电容元件c1与驱动晶体管trx的控制端子nd连

接,在第二期间t2,第二电容元件c2与驱动晶体管trx的控制端子nd连接。

65.在图15中,在扫描信号线gn的选择期间,第一电容信号cs1为high,并且第二电容信号cs2为low,因此驱动晶体管trx的栅极端子nd的有效值在第一期间t1比与像素数据dn对应的值vn低,在第二期间t2比与像素数据dn对应的值vn高。

66.因此,像素数据dn为中间灰度时,在第一期间t1流经发光元件x的有效电流比第二期间t2流经发光元件x的有效电流大,第一期间t1中的发光元件x的有效亮度比第二期间t2中的发光元件x的有效亮度高。在第一实施方式中,第一期间为明期间,第二期间为暗期间,发光元件x的第一期间及第二期间的平均亮度相当于与像素数据dn对应的像素电路pkn的亮度。

67.图16是表示第五实施方式的像素电路的变形例的电路图。图17是示出图16所示的像素电路的驱动方法的时序图。在图16中,将第一晶体管tr1和第二晶体管tr2设为与像素电路的其它晶体管(trx、trw、trp、trs、tre、tri)相同的p沟道型。

68.与第一晶体管tr1的栅极端子连接的切换信号线kan的电位在扫描信号线gn的选择期间(栅极脉冲gpn上升的期间)和第一期间t1内激活(low),在第一期间t1结束(第二期间t2开始)时成为非激活(high)。与第二晶体管tr2的栅极端子连接的切换信号线kbn的电位在扫描信号线gn的选择期间为激活(low),在第一期间t1开始时为非激活(high),在第一期间t1结束(第二期间t2开始)时成为激活(low)。

69.根据图16的结构,制造工序变得容易,也不需要图14的设置晶体管trj,因此实现像素电路的缩小。

70.〔关于各实施方式〕图18的(a)是表示各实施方式(在高灰度区域中不进行亮度限制的情况)的数据电压_亮度特性的曲线图,图18的(b)是表示数据电压(在高灰度区域中不进行亮度限制的情况)的校正特性的曲线图。图18(a)中,可知在进行时间上的亮度分配的各实施方式中,明期间的特性与暗期间的特性的总和成为视觉辨认特性,与不进行时间上的亮度分配的情况下的比较特性相比,低灰度区域的变化平缓,因此低灰度区域中的电压控制容易,实现显示品质的改善。另外,如图18(b)所示,在各实施方式中,在整个灰度区域,能够进行与不进行时间上的亮度分配的情况(虚线)同样的接近线性的电压控制。

71.图19的(a)是表示各实施方式(在高灰度区域进行亮度限制的情况)的数据电压_亮度特性的曲线图,图19的(b)是表示数据电压(在高灰度区域进行亮度限制的情况)的校正特性的曲线图。图19的(a)中,可知在进行时间上的亮度分配的各实施方式中,明期间的特性与暗期间的特性的总和成为视觉辨认特性,与不进行时间上的亮度分配的情况下的比较特性相比,低灰度区域的变化平缓,因此低灰度区域中的电压控制容易,实现显示品质的改善。此外,在图19的(b)中,由于灰度区域的斜率大于不进行时间亮度分配的情况下(虚线),因此易于在高灰度区域进行电压控制,从而实现显示质量的改善。

72.上述的各实施方式以例示及说明为目的,并非以限定为目的。基于这些例示及说明,本领域技术人员应当明白能够进行多种变形方式。附图标记说明

73.2显示装置4薄膜晶体管层

5发光元件层6密封层12基板16栅极绝缘膜18第一层间绝缘层20第二层间绝缘层21平坦化膜22第一电极23边缘覆盖膜24el层25第二电极x发光元件pkn像素电路trx驱动晶体管tr1第一晶体管tr2第二晶体管tr3第三晶体管tr4第四晶体管c1第一电容元件c2第二电容元件c3第三电容元件c4第四电容元件ft1帧期间t1第一期间t2第二期间can第一电容信号线cbn第二电容信号线ks切换信号kn切换信号线kc切换信号生成电路

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1