差分输入电路与驱动电路的制作方法

1.本发明有关于一种差分输入电路与驱动电路,且特别是有关于一种具有取样与保持功能,可将感测到的电压信号转换为模拟至数字转换器(analog-to-digital converter)的低电压输入之差分输入电路与驱动电路。

背景技术:

2.请参见图1,其是有机发光二极管像素电路的操作方式的示意图。有机发光二极管(organic light-emitting diode,简称为oled)面板包含排列为矩阵(matrix)的oled像素电路,其中位于第m行与第n列的oled像素电路17可表示为pxl

mn

。oled像素电路17经由第m条数据线dl

m

与第m条感测线sl

m

而电连接于源极驱动器,以及经由第n条门极线gl

n

而电连接至门极驱动器。源极驱动器与门极驱动器均从时序控制器接收与像素电路17对应的控制信号。

3.当oled像素电路(pxl

mn

)17被选择用于显示时,晶体管17a导通并传送第n条门极线gl

n

上的门极控制信号,且像素电容c

pxl

经由第m条数据线dl

m

传送的数据信号充电。一旦像素电容c

pxl

的跨压足以导通驱动晶体管17b(例如,薄膜晶体管(thin film transistor,简称为tft)时,将伴随产生驱动oled 17d的像素驱动电流i

drv

。

4.随着时间的经过,oled像素电路17的特性,例如,驱动晶体管17b的临界电压v

th

与oled17d的导通电压(turn on voltage),可能产生偏移或劣化(degrade)。因此,需引进能感测oled及/或tft劣化的机制。

5.当开关17c导通时,可利用oled面板上的感测线sl

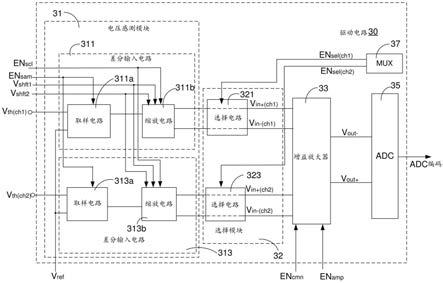

m

,对代表oled及/或tft劣化的感测信号进行感测。oled数据驱动器包含显示数据驱动电路,以及用于处理从感测线sl

m

感测得出的信号的感测电路。感测电路包含模拟至数字转换器,用于将感测信号(属于模拟电压信号)转换为数字感测信息后,再将数字感测信息传送至时序控制器或核心处理器,进而由其对所显示的图像数据进行数据补偿。

6.然而,感测得出的模拟电压信号的范围大于adc的操作电压的范围。因此,亟需能将感测得出的模拟电压信号转换至adc的低电压范围的技术。

技术实现要素:

7.本发明是有关于一种差分输入电路与包含其的驱动电路。差分输入电路将单端形式(single-end)的模拟电压信号转换为增益放大器的差分输入信号对,并能改善信号质量。

8.根据本发明的第一方面,提出一种差分输入电路。差分输入电路将oled面板上,与感测线对应的模拟电压信号转换为,输出至增益放大器的差分输入信号对。差分输入电路包含:取样电路与缩放电路。取样电路接收模拟电压信号与参考电压。取样电路包含:第一取样路径与第二取样路径。第一取样路径根据模拟电压信号与参考电压,选择性对模拟电压信号取样,并在第一感测端点与第一参考端点之间产生第一取样电压。第二取样路径根

据参考电压与模拟电压信号,选择性对模拟电压信号取样,并在第二参考端点与第二感测端点产生第二取样电压。缩放电路包含:第一缩放路径与第二缩放路径。第一缩放路径电连接于第一感测端点与第一参考端点。第一缩放路径接收第一取样电压与第一移位电压,使第一取样电压缩小至第一缩放电压,以及根据第一移位电压与第一缩放电压而产生差分输入信号对中的一个。第二缩放路径电连接于第二感测端点与第二参考端点。第二缩放路径接收第二取样电压与第二移位电压,使第二取样电压缩小至第二缩放电压,以及根据第二移位电压与第二缩放电压而产生差分输入信号对的另一个。其中,第一移位电压与第二移位电压为直流电压,且第一移位电压小于第二移位电压。

9.根据本发明的第二方面,提出一种显示设备的驱动电路。驱动电路包含差分输入电路与增益放大器。差分输入电路将与oled面板上的感测线对应的模拟电压信号转换为差分输入信号对。差分输入电路包含:取样电路与缩放电路。取样电路接收模拟电压信号与参考电压。取样电路包含:第一取样路径与第二取样路径。第一取样路径根据模拟电压信号与参考电压而选择性对模拟电压信号取样,并在第一感测端点与第一参考端点之间产生第一取样电压。第二取样路径根据参考电压与模拟电压信号而选择性对模拟电压信号取样,并于第二参考端点与第二感测端点之间产生第二取样电压。缩放电路包含:第一缩放路径与第二缩放路径。第一缩放路径电连接于第一感测端点与第一参考端点。第一缩放路径接收第一取样电压与第一移位电压,将第一取样电压缩小至第一缩放电压,以及根据第一移位电压与第一缩放电压而产生差分输入信号对中的一个。第二缩放路径电连接于第二感测端点与第二参考端点。第二缩放路径接收第二取样电压与第二移位电压,将第二取样电压缩小至第二缩放电压,以及根据第二移位电压与第二缩放电压而产生差分输入信号对中的另一个。第一移位电压与第二移位电压为直流电压,且第一移位电压小于第二移位电压。增益放大器电连接于差分输入电路。增益放大器包含第一输入端点、第二输入端点、第一输出端点与第二输出端点。增益放大器经由第一输入端点与第二输入端点而接收差分输入信号对,并于第一输出端点与第二输出端点产生差分输出信号对。

10.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下:

附图说明

11.图1,其是oled像素电路的操作方式的示意图。

12.图2,其是与oled显示设备中的像素电路的oled及/或tft劣化信息相关的组件的示意图。

13.图3a,其是根据本发明实施例的驱动电路的示意图。

14.图3b,其是图3a所示的信号的波形变动的示意图。

15.图4,其是根据本发明实施例的差分输入电路的示意图。

16.图5、6,其是根据本发明实施例的差分输入电路,操作在取样阶段与保持阶段(电压缩放阶段)的示意图。

17.图7,其是操作在放大模式的增益放大器的示意图。

18.图8,其是根据本发明的实施例的差分输入电路的实现方式的示意图。

19.图9,其是根据本发明实施例的差分输入电路特性的示意图。

20.图10,其是adc的转换特性的示意图。

具体实施方式

21.请参见图2,其与oled显示设备的像素电路中的oled及/或tft劣化信息相关的组件的示意图。oled显示设备20包含显示面板27、源极驱动器23、时序控制器21与门极驱动器25。时序控制器21与显示面板27均电连接于源极驱动器23与门极驱动器25。

22.显示面板27利用基本显示组件(像素)271显示图像,且各个基本显示组件271包含红色(r)像素电路271a、绿色(g)像素电路271b以及蓝色(b)像素电路271c。

23.源极驱动器23可包含一个或多个驱动电路231、233,且各个驱动电路231、233进一步包含adc 231a、233a、多路复用器(multipexer,简称为mux)231b、233b、增益放大器231c、233c以及多个差分输入电路2311、2313、2315、2331、2333、2335。由于驱动电路231、233内的组件与连接方式相似,此处仅以驱动电路231为例。各个驱动电路231、233可用半导体芯片实现。

24.差分输入电路2311经感测线sl1接收第一通道(ch1)模拟电压信号。差分输入电路2313经感测线sl2接收第二通道(ch2)模拟电压信号v

th(ch2)

。差分输入电路2315经感测线sl3接收第三通道(ch3)模拟电压信号v

th(ch3)

。请留意,图2仅为示意图,且感测线sl1~sl3与像素的行之间并不限定须为一对一的对应关系。根据从感测线sl1~sl3分别接收的模拟电压信号,可取得oled/tft劣化信息。

25.根据本发明的实施例,毋须限定源极驱动器23所包含的驱动电路231、233的数量。如图2所示,驱动电路231、233可包含多路复用器231b、231c,驱动电路231、233可分别设置adc 231a、233a。

26.从感测线sl1~sl3接收模拟电压信号后,差分输入电路2311、2313、2315进行取样,并将模拟电压信号缩小。接着,adc 231a、233a将经过缩放后的模拟电压信号,转换为代表adc编码的数字信号。数字信号将进一步传送至时序控制器21。

27.由于数字信号源自于具有oled像素电路的oled及/或tft劣化信息的模拟电压信号,adc编码可代表oled像素电路的oled及/或tft的劣化状态。

28.根据本发明的实施例,多路复用器231b从时序控制器21接收选择信号en

sel

。基本上,选择信号en

sel

分别对应于差分输入电路2311、2313、2315。藉由选择信号en

sel

,adc 231a轮流产生与差分输入电路2311、2313、2315对应的数字信号。据此,时序控制器21可补偿oled面板的oled及/或tft劣化。

29.请参见图3a,其是根据本发明实施例的驱动电路的示意图。驱动电路30包含电压感测模块31、选择模块32、增益放大器33、adc 35与多路复用器37。根据驱动电路30所支持的通道的数量,电压感测模块31内的差分输入电路311、313的数量可能不同。即,多个差分输入电路311、313以时分多址的方式,产生输出至增益放大器33。

30.为便于说明,假设图3a的驱动电路30支持双通道。因此,电压感测模块31包含两个差分输入电路311、313,且选择模块32包含两个选择电路321、323。差分输入电路311与选择电路321对应于第一通道(ch1),且差分输入电路313与选择电路323对应于第二通道(ch2)。

31.根据本发明的实施例,部分的信号特定于通道,部分的信号则否。参考电压v

ref

、第一移位电压v

shft1

、第二移位电压v

shft2

、取样致能信号en

sam

与缩放致能信号en

scl

为传送至差

分输入电路311、313的信号。另一方面,模拟电压信号v

th(ch1)

、v

th(ch2)

与通道选择信号en

sel(ch1)

、en

sel(ch2)

为通道专用。在下文中,必要时将利用括号表示与特定通道对应的信号。

32.差分输入电路311包含取样电路311a与缩放电路311b。同理,差分输入电路313包含取样电路313a与缩放电路313b。由于差分输入电路313的信号与操作,与差分输入电路311的信号与操作相似。因此,后续附图(图4~8)仅以一个差分输入电路为例。

33.取样电路311a、313a分别电连接于缩放电路311b、313b。取样电路311a、313a均由取样致能信号en

sam

与参考电压v

ref

所控制。缩放电路311b、313b均由缩放致能信号en

scl

、第一移位电压v

shft1

与第二移位电压v

shft2

所控制。

34.取样致能信号en

sam

与缩放致能信号en

scl

为时序控制器(此处未说明)发出的脉冲信号。图3b将简要说明取样致能信号en

sam

与缩放致能信号en

scl

的产生与时序。简言之,取样致能信号en

sam

与缩放致能信号en

scl

交错产生,且取样致能信号en

sam

的脉冲早于缩放致能信号en

scl

的脉冲。

35.缩放电路311b、313b分别电连接于选择电路321、323。选择电路321传送与第一通道(v

in+(ch1)

,v

in-(ch1)

)对应的差分输入信号对至增益放大器33,且选择电路321传送与第二通道(v

in+(ch2)

,v

in-(ch2)

)对应的差分输入信号对至增益放大器33。多路复用器37分别产生并传送两个通道选择信号en

sel(ch1)

、en

sel(ch2)

至选择电路321、323。基本上,通道选择信号en

sel(ch1)

、en

sel(ch2)

用于选择选择电路321、323中的哪一个所产生的输出信号可传送至增益放大器33。

36.增益放大器33可操作在共同模式(common mode)(mcmn)或放大模式(mamp)。时序控制器利用共模(common mode)信号en

cmn

控制增益放大器33操作在共同模式(mcmn),以及利用放大模式信号en

amp

控制增益放大器33操作在放大模式(mamp)。

37.当增益放大器33操作在共同模式(mcmn)时,选择电路321、323均不会将差分输入信号(v

in+(ch1)

,v

in-(ch1)

),(v

in+(ch2)

,v

in-(ch2)

)传送至增益放大器33。

38.当增益放大器33操作在放大模式(mamp)时,选择电路321、323中的一个传送差分输入信号对(v

in+(ch1)

,v

in-(ch1)

)、(v

in+(ch2)

,v

in-(ch2)

)至增益放大器33,增益放大器33产生并传送差分输出信号对(v

out+

,v

out-)至adc 35,且adc35将差分输出信号对(v

out+

,v

out-)转换为数字信号。adc35的输入范围相对小于感测得到的模拟电压信号的范围。adc 35的输入范围与输出范围的实际值并不需要限定。

39.请参见图3b,其是图3a所示的信号的波形变动的示意图。纵轴代表不同的信号,横轴代表时间。此处所示的信号的电压电平仅为举例,并非用于限制实际的应用。

40.第一个波形为取样致能信号en

sam

,第二个波形为缩放致能信号en

scl

。第三个波形与第四个波形为分别被传送至选择电路321、323的通道选择信号(en

sel(ch1)

、en

sel(ch2)

)。第五个波形为共模信号en

cmn

,且第六个波形为放大模式信号en

amp

。

41.取样致能信号en

sam

在时点t1从低电压电平显著地转换至高电压电平,以及在时点t3从高电压电平显著地转换至低电压电平。取样致能信号en

sam

在高电压电平的期间表示为第一期间t1。在第一期间t1,取样电路311a、313a由取样致能信号en

sam

致能。

42.缩放致能信号en

scl

在时点t4自低电压电平显著地变动至高电压电平,以及在时点t5由高电压电平显著地变动至低电压电平。缩放致能信号en

scl

处于高电压电平的期间为第二期间t2。第一期间t1的结束时点等于或早于第二期间t2的开始时点。在第一期间t1与第

二期间t2间可定义短暂的时间差,用于避免信号冲突。

43.在第一期间t1,取样电路311a、313a分别对模拟电压信号v

th(ch1)

、v

th(ch2)

取样。在第二期间t2,缩放电路311b产生差分输入信号对(v

in+(ch1)

,v

in-(ch1)

),且缩放电路313b产生差分输入信号对(v

in+(ch2)

,v

in-(ch2)

)。

44.取样电路311a、313a同时接收取样致能信号en

sam

,且缩放电路311b、313b同时接收缩放致能信号en

scl

。换言之,取样电路311a、313a的操作彼此同步,且缩放电路311b、313b的操作彼此同步。即,差分输入信号对(v

in+(ch1)

,v

in-(ch1)

)与差分输入信号对(v

in+(ch2)

,v

in-(ch2)

)同时产生。

45.与第一通道(ch1)对应的通道选择信号en

sel(ch1)

在时点t6自低电压电平变动至高电压电平,以及在时点t7从高电压电平变动至低电压电平。与第一通道(ch1)对应的通道选择信号en

sel(ch1)

为高电压电平的期间为第三期间t3。第二期间t2的结束时点等于或早于第三期间t3的开始时点。在第二期间t2与第三期间t3之间可定义短暂的时间差,用于避免信号冲突。

46.与第二通道(ch2)对应的通道选择信号en

sel(ch2)

在时点t8从低电压电平变动至高电压电平,以及在时点t9从高电压电平变动至低电压电平。与第二通道(ch2)对应的通道选择信号en

sel(ch2)

处于高电压电平的期间为第四期间t4。第三期间t3的结束时点,等于或早于第四期间t4的开始时点。在第三期间t3与第四期间t4之间可定义短暂的时间差,用于避免信号冲突。

47.在图3b中,假设共模信号en

cmn

在时点t2从低电压电平转换至高电压电平;以及,在时点t5从高电压电平转换至低电压电平。共模信号en

cmn

为高电压电平的期间为第五期间t5。

48.根据本发明的实施例,在选择模块32接收通道选择信号en

sel(ch1)

、en

sel(ch2)

前,增益放大器33可取得共模电压v

cmn

。例如,第五期间t5的开始时点可介于时点t1、t4之间,且期间t5的结束时点可早于或等于时点t6。

49.放大模式信号en

amp

在时点t6由低电压电平变动至高电压电平,以及在时点t10由高电压电平变动至低电压电平。放大模式信号en

amp

为高电压电平的期间为第六期间t6。第五期间t5的结束时点等于或早于第六期间t6的开始时点。在第五期间t5与第六期间t6之间可定义短暂的时间差,用于避免信号冲突。

50.根据图3b所示的波形,差分输入电路311、313将与感测线对应的模拟电压信号,转换为增益放大器33的差分输入信号对(v

in+(ch1)

,v

in-(ch1)

)、(v

in+(ch2)

,v

in-(ch2)

)。接着说明根据本发明实施例的差分输入电路的设计与操作。为便于说明,此处仅以一个差分输入电路为例。

51.请参见图4,其是根据本发明实施例的差分输入电路的示意图。差分输入电路41包含取样电路411与缩放电路413。取样电路411进一步包含第一取样路径411a与第二取样路径411b,且缩放电路413进一步包含第一缩放路径413a与第二缩放路径413b。第一缩放路径413a电连接于第一取样路径411a与选择电路43。第二缩放路径413b电连接于第二取样路径411b与选择电路43。

52.取样电路411接收模拟电压信号v

th

与参考电压v

ref

。第一取样电路411a根据模拟电压信号v

th

与参考电压v

ref

而选择性产生第一取样电压δv

c1

,即,δv

c1

=v

th-v

ref

。第二取样路

径411b根据参考电压v

ref

与模拟电压信号v

th

而选择性产生第二取样电压δv

c2

。

53.第一缩放路径413a接收第一取样电压δv

c1

与第一移位电压v

shft1

,利用第一缩放倍率r

s1

将第一取样电压δv

c1

缩小至第一缩放电压δv

cs1

,并根据第一移位电压v

shft1

与第一缩放电压δv

cs1

产生差分输入信号对中的一个(例如,非反相差分输入信号v

in+

)。即,δv

cs1

=δv

c1

*r

s1

,且v

in+

=v

shft1

+δv

c1

*r

s1

=v

shft1

+δv

cs1

。

54.第二缩放路径413b接收第二取样电压δv

c2

与第二移位电压v

shft1

,利用第二缩放倍率r

s2

将第二取样电压δv

c2

缩小至第二缩放电压δv

cs2

,并根据第二移位电压v

shft2

与第二缩放电压δv

cs2

产生差分输入信号对中的另一个(例如,反相差分输入信号v

in-)。即,δv

cs2

=δv

c2

*r

s2

,且v

in-=v

shft2

+δv

c2

*r

s2

=v

shft2

+δv

cs2

。

55.根据本发明的实施例,第一移位电压v

shft1

与第二移位电压v

shft2

为直流(direct current,简称为dc)电压,且第一移位电压v

shft1

小于第二移位电压v

shft2

(v

shft1

<v

shft2

)。此外,差分输入信号对(v

in+

,v

in-)的范围,小于或等于第一移位电压v

shft1

与第二移位电压v

shft2

之间的差值。即,|v

in+-v

in-|≦|v

shft1-v

shft2

|。根据本发明的实施例,第一移位电压v

shft1

与第二移位电压v

shft2

相对于参考点(reference point)可能具有相同的绝对值与相反的极性。例如,相对于参考点0v,第一移位电压v

shft1

为-0.5v,且第二移位电压v

shft2

为+0.5v;或者,相对于参考点+1.5v,第一移位电压v

shft1

为+1v,且第二移位电压v

shft2

为+2v。

56.选择电路43包含第一选择开关sw

sel1

与第二选择开关sw

sel2

。选择电路43电连接于增益放大器45。当与差分输入电路41对应的通道选择信号en

sel

处于高电压电平时,第一选择开关sw

sel1

与第二选择开关sw

sel2

导通,第一选择开关sw

sel1

将非反相差分输入信号v

in+

传导至增益放大器45,且第二选择开关sw

sel2

将反相差分输入信号v

in-传导至增益放大器45。

57.请参见图5、6,其是根据本发明实施例的差分输入电路,操作在取样阶段与保持阶段(电压缩放阶段)的示意图。图5对应于取样致能信号en

sam

处于高电压电平的情形(例如,图3b的第一期间t1)。图6对应于取样致能信号en

sam

转换至低电压电平,且缩放致能信号en

scl

处于高电压电平的情形(例如,图3b的第二期间t2)。

58.第一取样路径411a与第一缩放路径413a的内部组件,以及第二取样路径411b与第二缩放路径413b的内部组件彼此对称。

59.根据模拟电压信号v

th

、参考电压v

ref

与第一移位电压v

shft1

,以及取样致能信号en

sam

与缩放致能信号en

scl

的控制,第一取样路径411a与第一缩放路径413a共同产生非反相差分输入信号v

in+

。

60.第一取样路径411a包含第一取样开关sw

s1

、第一参考开关sw

ref1

与第一取样电容c

s1

。第一取样开关sw

s1

电连接于第一接收端点n

rv1

与第一感测端点n

sen1

。第一参考开关sw

ref1

电连接于第二接收端点n

rv2

与第一参考端点n

ref1

。第一取样电容c

s1

电连接于第一感测端点n

sen1

与第一参考端点n

ref1

。当取样致能信号en

sam

处于高电压电平时,第一取样开关sw

s1

将模拟电压信号传导至第一感测端点n

sen1

,且第一参考开关sw

ref1

将参考电压v

ref

传导至第一参考端点n

ref1

,进而对第一取样电容c

s1

充电,且在第一感测端点n

sen1

与第一参考端点n

ref1

之间产生第一取样电压δv

c1

。

61.第一缩放路径413a包含第一缩放开关sw

scl1

、第一移位开关sw

shft1

,与第一电荷共享电容c

cs1

。第一缩放开关sw

scl1

电连接于第一感测端点n

sen1

与第一缩放端点n

scl1

。第一移位开关sw

shft1

电连接于第一参考端点n

ref

与第一移位端点n

sft1

。第一电荷共享电容c

cs1

电连接

于第一缩放端点n

scl1

与第一移位端点n

sft1

。

62.当缩放致能信号en

scl

处于高电压电平时,第一缩放开关sw

scl1

将第一感测端点n

sen1

传导至第一缩放端点n

scl1

,且第一移位开关sw

shft1

将第一参考端点n

ref1

传导至第一移位端点n

sft1

。在此同时,第一电荷共享电容c

cs1

经由第一移位端点n

sft1

接收第一移位电压v

shft1

,且先前储存在第一取样电容c

s1

的电荷,将由第一取样电容c

s1

与第一电荷共享电容c

cs1

所共享。

63.第二取样路径411b与第二缩放路径413b根据模拟电压信号v

th

、参考电压v

ref

与第二移位电压v

shft2

,以及取样致能信号en

sam

与缩放致能信号en

scl

的控制,共同产生反相差分输入信号v

in-。由于第二取样路径411b与第二缩放路径413b的实现方式与第一取样路径411a与第一缩放路径413a的实现方式相似,此处不说明其细节。

64.当取样致能信号en

sam

处于高电压电平时,第一取样开关sw

s1

与第一参考开关sw

ref1

均导通。在此同时,第一取样电容c

s1

被充电,且在第一感测端点n

sen1

与第一参考端点n

ref1

之间产生第一取样电压δv

c1

。当缩放致能信号en

scl

处于高电压电平时,在感测阶段累积在第一取样电容c

s1

的电荷将由两个电容(即,第一取样电容c

s1

与第一电荷共享电容c

cs1

)共同共享。连带的,第一缩放端点n

scl1

与第一移位端点n

sft1

之间的电压降低并小于第一取样电压δv

c1

。在第一缩放端点n

scl1

与第一移位端点n

sft1

之间经缩小后的电压,称为第一缩放电压δv

cs1

。

65.同理,当取样致能信号en

sam

处于高电压电平时,第二取样开关sw

s2

与第二参考开关sw

ref2

均导通。在此同时,第二取样电容c

s2

被充电,且在第二参考端点n

ref2

与第二感测端点n

sen2

之间产生第二取样电压δv

c2

。当缩放致能信号en

scl

处于高电压电平时,在感测阶段所累积在第二取样电容c

s2

的电荷,将由两个电容(即,第一取样电容c

s1

与第一电荷共享电容c

cs1

)共同共享。连带的,在第二缩放端点n

scl2

与第二移位端点n

sft2

之间的电压降低,并小于第二取样电压δv

c2

。在第二缩放端点n

scl2

与第二移位端点n

sft2

之间经缩小后的电压,称为第二缩放电压δv

cs2

。

66.根据本发明的实施例,参考电压v

ref

、第一移位电压v

shft1

与第二移位电压v

shft2

为直流电压。第一移位电压v

shft1

小于第二移位电压v

shft2

(v

shft1

<v

shft2

)。第一移位电压v

shft1

与第二移位电压v

shft2

之间的电压差(δv

shft

)可表示为δv

shft

=v

shft2-v

shft1

。差分输入信号对(v

in+(ch1)

,v

in-(ch1)

)、(v

in+(ch2)

,v

in-(ch2)

)的范围,小于或等于第一移位电压v

shft1

与第二移位电压v

shft2

之间的差值(δv

shft

)。

67.如图5所示,增益放大器45可包含输入级电路451、负载级电路453、互接路径(interconnection path)、第一导通路径45a与第二导通路径45b。第一导通路径45a电连接于第一输入端点n

in1

与第一输出端点n

out-,且第二导通路径45b电连接于第二输入端点n

in2

与第二输出端点n

out+

。

68.输入级电路451电连接于选择电路43,并从其接收差分输入信号v

in+

、v

in-。负载级电路453电连接于输入级电路452、第一输出端点n

out-与第二输出端点n

out+

。互接路径包含开关sw

amp5

、sw

amp6

,第一导通路径45a包含开关sw

amp1

、sw

amp2

、sw

amp7

与放大电容c

amp1

,第二导通路径45b包含开关sw

amp3

、sw

amp4

、sw

amp8

与放大电容c

amp2

。

69.当增益放大器45操作在共同模式(mcmn)时,开关sw

amp1

、sw

amp2

、sw

amp3

、sw

amp4

、sw

amp5

、sw

amp6

导通,且开关sw

amp7

、sw

amp8

为断开。因开关sw

amp1

、sw

amp2

导通的缘故,第一导通路径45a接

收共模电压v

cmn

。藉由因开关sw

amp3

、sw

amp4

导通的缘故,第二导通路径45b接收共模电压v

cmn

。

70.当增益放大器45操作在放大模式(mamp)时,第一导通路径45a根据共模电压v

cmn

与差分输入信号对(v

in+

,v

in-)产生反相差分输出信号v

out-,且第二导通路径45b同样据以产生非反相差分输出信号v

out+

。

71.图6对应于增益放大器45处于共同模式(mcmn)的情形(例如,图3b的第五期间t5)。

72.由于第一缩放开关sw

scl1

与第一移位开关sw

shft1

被缩放致能信号en

scl

导通,第一电荷共享电容c

cs1

共享先前储存在第一取样电容c

s1

的电荷。据此,第一取样电压δv

c1

被缩小至第一缩放电压δv

cs1

,且非反相差分输入信号v

in+

在第一缩放端点n

scl1

产生。非反相差分输入信号v

in+

的产生可表示为式(1)。

73.v

in+

=v

shft1

+δv

c1

*r

s1

=v

shft1

+δv

cs1

74.=v

shft1

+δv

c1

*c

s1

/(c

s1

+c

cs1

)

…………………………………

..式(1)

75.由于缩放致能信号en

scl

导通第二缩放开关sw

scl2

与第二移位开关sw

shft2

的缘故,第二电荷共享电容c

cs2

共享储存在第二取样电容c

s2

的电荷。据此,将第二取样电压δv

c2

缩小至第二缩放电压δv

cs2

,以及在第二缩放端点n

scl2

产生反相差分输入信号v

in-。反相差分输入信号v

in-的产生可表示为式(2)。

76.v

in-=v

shft2

+δv

cs2

77.=v

shft2

+δv

c2

*c

s2

/(c

s2

+c

cs2

)

…………………………………

..式(2)

78.第一取样电容c

s1

以其阳极和阴极分别接收模拟电压信号v

th

与参考电压v

ref

。第二取样电容c

s2

以其阴极和阳极分别接收模拟电压信号v

th

与参考电压v

ref

。假设c

s1

=c

s2

,第一取样电压δv

c1

与第二取样电压δv

c1

的大小相等,但第一取样电压δv

c1

与第二取样电压δv

c2

的极性为反向。

79.第一缩放电压δv

cs1

与第一取样电压δv

c1

之间的第一缩放倍率rs1,可根据第一取样电容c

s1

的电容值与第一电荷共享电容c

cs1

的电容值而决定。例如,若c

s1

=c且c

cs1

=2*c,则δv

cs1

=1/3*δvc1。同理,第二缩放电压δv

cs2

与第二取样电压δv

c2

之间的第二缩放倍率r

s2

,可根据第二取样电容c

s2

的电容值与第二电荷共享电容c

cs2

的电容值而决定。

80.根据本发明的实施例,第一取样电容c

s1

的电容值与第二取样电容c

s2

的电容值相等,且第一电荷共享电容c

cs1

的电容值与第二电荷共享电容c

cs2

的电容值相等。因此,第一缩放倍率r

s1

等于第二缩放倍率r

s2

。

81.根据这些等式(c

s1

=c

s2

、c

cs1

=c

cs2

,且δv

c2

=-δv

c1

),式(2)可改写为式(3)。

82.v

in-=v

shft2

+δv

cs2

83.=v

shft2

+δv

c2

*c

s2

/(c

s2

+c

cs2

)

84.=v

shft2-δv

c1

*c

s1

/(c

s1

+c

cs1

)

…………………………………

..式(3)

85.请参见图7,其是操作在放大模式的增益放大器的示意图。图7对应于图3b的第六期间t6。

86.当增益放大器45操作在放大模式(mamp)时,开关sw

amp1

、sw

amp2

、sw

amp3

、sw

amp4

、sw

amp5

、sw

amp6

断开,且开关sw

amp7

、sw

amp8

导通。经由放大电容c

amp1

与开关sw

amp7

,第一导通路径45a将从第一输出端点n

out-反相差分输出信号v

out-反馈至第一差分输入端点n

in1

。经由放大电容c

amp2

与开关sw

amp8

,第二导通路径45b将非反相差分输出信号v

out+

自第二输出端点n

out+

反馈至第二差分输入端点n

in2

。在图7中,第一导通路径45a根据共模电压v

cmn

与差分输入信号(v

in+

,

v

in-)产生反相差分输出信号v

out-,且第二导通路径45b根据共模电压v

cmn

与差分输入信号(v

in+

,v

in-)产生非反相差分输出信号v

out+

。

87.请参见图8,其是根据本发明的实施例的差分输入电路的实现方式的示意图。如图8所示,利用传输门(transmission gates)实现第一取样开关sw

s1

、第二取样开关sw

s2

、第一参考开关sw

ref1

、第二参考开关sw

ref2

、第一选择开关sw

sel1

,以及第二选择开关sw

sel2

;以及利用nmos晶体管实现第一缩放开关sw

scl1

、第二缩放开关sw

scl2

、第一移位开关sw

shft1

,与第二移位开关sw

shft2

。图8所示的实现方式仅为举例,实际应用的实现方式可能不同。

88.请参见图9,其根据本发明实施例的差分输入电路特性的示意图。横轴代表差分输入电路41的输入电压(v

th-v

ref

),且纵轴代表差分输入电路41的差分输出信号。即,增益放大器45的差分输入信号。在图9中,线条l1代表非反相差分输入信号v

in+

,且线条l2代表反相差分输出信号v

in-。

89.请参见图10,其是差分输入电路的输入电压(v

th-v

ref

)转换为adc编码输出的转换特性的示意图。纵轴代表差分输入电路的的输入电压(v

th-v

ref

)。水平轴代表adc编码。在图10中,差分输入电路的输入电压的最大值(v

th-v

ref

)

max

,对应于adc编码的最大值。例如,若adc编码的分辨率(resolution)为10位时,则adc编码的最小值为“0”,且adc编码的最小值为“1023”。在图10中,线条l3代表非反相差分输入信号v

in+

,线条l4代表反相差分输出信号v

in-。

90.假设adc的操作范围为1v(增益放大器的输出之间的电压,即,|v

out+-v

out-|等于1v(|v

out+-v

out-|=1v),增益放大器的增益等于1,为满足v

shft2-v

shft1

=1v的关系,第一移位电压v

shft1

可设计为v

shft1

=-0.5,且第二移位电压v

shft2

可设计为v

shft2

=+0.5v。

91.此外,假设缩小倍率等于1/3,差分输入电路的输入电压(v

th-v

ref

)必须小于或等于3v,以确保缩小电压(v

in+-v

in-)维持小于或等于1v。即,非反相差分输入信号v

in+

与反相差分输入信号v

in-必须满足以下关系:|v

in+-v

in-|≦|v

shft1-v

shft2

|。

92.接着说明模拟电压信号v

th

等于最小值,且模拟电压信号v

th

等于参考电压v

ref

(例如,v

ref

=0v,v

th

=0v)的情形。据此,根据式(2),非反相差分输入信号v

in+

等于第一移位电压v

shft1

(v

in+

=-0.5+0*(1/3)=-0.5v=v

shft1

)。再者,根据式(3),反相差分输入信号v

in-等于第二移位电压v

shft2

(v

in-=+0.5+0*(1/3)=+0.5v=v

shft2

)。

93.接着说明模拟电压信号v

th

等于3v,且参考电压v

ref

等于0v(v

th

=3v且v

ref

=0v)的情形。此时,根据式(2),非反相差分输入信号v

in+

等于第二移位电压v

shft2

(v

in+

=-0.5v+3*(1/3)v=+0.5v)。再者,根据式(3),反相差分输入信号v

in-等于第一移位电压v

shft1

(v

in-=-0.5v+(-3)*(1/3)=-0.5v=v

shft1

)。

94.当差分输入电路41的输入电压(v

th-v

ref

)等于“0”时,模拟电压信号v

th

等于参考电压v

ref

,且第一取样电压δvc1等于“0”。根据式(1)可得出非反相差分输入信号v

in+

。即,v

in+

=v

shft1

+(0)*c

s1

/(c

s1

+c

cs1

)=v

shft1

。同样的,根据式(3),可得出反相差分输入信号v

in-。即,v

in-=v

shft2-(0)*c

s1

/(c

s1

+c

cs1

)=v

shft2

。因此,非反相差分输入信号v

in+

等于第一移位电压v

shft1

,且反相差分输入信号v

in-等于第二移位电压v

shft2

。

95.根据前述说明可以得知图10中线条l3、l4的含义。当差分输入电路41的输入电压(v

th-v

ref

)为最小值(v

th-v

ref

)

min

时,增益放大器45的差分输出(v

out+-v

out-)等于最小值,且其对应于adc编码的最小值(adc编码=0)。另一方面,当差分输入电路的输入电压(v

th-v

ref

)为

最大值(v

th-v

ref

)

max

时,增益放大器45的差分输出(v

out+-v

out-)等于最大值,且其对应于adc编码的最大值(adc编码=1023)。

96.根据本发明的实施例,差分输入电路接收单端形式的模拟电压信号v

th

,并将成对的全差分信号提供给增益放大器。连带的,增益放大器不需要将单端输入转换为差分输出。换言之,由于差分输入电路可提供全差分信号至增益放大器的缘故,驱动电路的信号质量可获得提升。

97.本发明的应用并不限于前述所举例的oled显示面板。因此,若其他的显示设备需要将模拟电压信号缩小时,也可修改并将本发明的实施例应用于其上。

98.综上所述,虽然本发明已以实施例揭示如上,然其并非用以限定本发明。本发明所属技术领域中的技术人员,在不脱离本发明的精神和范围内,当可作各种之更动与润饰。因此,本发明的保护范围当视后附的权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1