显示驱动器、应用于显示驱动器的装置及显示面板驱动方法与流程

1.本揭示内容关于一种驱动显示器、装置及方法,特别是用以根据指令信号驱动显示驱动器。

背景技术:

2.随着显示技术的快速发展,显示装置被广泛地应用于人们的日常生活中,且扮演了重要的角色。举例而言,显示驱动器被应用在电视、计算机、智能型手机等各类电子装置上,用以呈现多种信息。

3.一般言,显示装置中的显示驱动器会提供包含有时脉信号与数据信号的指令信号,使显示面板能显示出不同亮度与色彩的影像,而前述驱动过程将对显示面板的显示品质有着重大影响。

技术实现要素:

4.本揭示内容是关于一种显示面板驱动方法,包含下列步骤:透过显示驱动器接收指令信号;在不同时间点记录指令信号中的多个指令值,其中该些指令值对应于像素电路中的至少一条数据线;判断该些指令值中的正确机率最高的指令值,且产生过滤指令信号,其中过滤指令信号对应于正确机率最高的指令值;以及根据过滤指令信号,驱动像素电路。

5.在一实施例中,该些指令值中的最具代表性的指令值是被判断为正确机率最高的指令值。

6.在一实施例中,该些指令值中的最具代表性的指令值为该些指令值中的重复性最高的指令值。

7.在一实施例中,重复性最高的指令值为出现频率最高的指令值。

8.在一实施例中,该些指令值中的正确机率最高的指令值为该些指令值中的连续出现次数最高的指令值。

9.在一实施例中,连续出现次数最高的指令值包含n个相同的连续值,且n为等于或大于2的正整数。

10.在一实施例中,根据过滤指令信号驱动像素电路的方法包含:根据过滤指令信号,设定像素电路的频宽、电流值或驱动频率。

11.本揭示内容还关于一种应用于显示驱动器的装置,包含取样电路及逻辑电路。取样电路用以透过记录指令信号中的多个指令值,以对指令信号进行取样。指令值对应于像素电路中的至少一条数据线。逻辑电路电性连接于取样电路,且用以接收该些指令值。逻辑电路还用以根据该些指令值产生过滤指令值,且用以根据过滤指令值驱动像素电路。

12.在一实施例中,逻辑电路用以将该些指令值中的出现频率最高的指令值设定为过滤设定值。

13.在一实施例中,逻辑电路还用以透过多个节点,在不同时间点记录该些指令值,且逻辑电路包含多个逻辑门,每个逻辑门电性连接于该些节点的子集合,以分别接收该些指

令集的子集合。

14.在一实施例中,逻辑电路以判断该些指令值是否包含n个相同的连续值,其中n为等于或大于2的正整数,逻辑电路还用以将n个相同的连续值设定为过滤指令值。

15.在一实施例中,逻辑电路包含计数器,计数器用以计算该些指令值是否包含n个相同的连续值。

16.在一实施例中,逻辑电路包含多个逻辑门及多个多工器。逻辑门电性连接于取样电路的输出端,且用以对该些指令值中的当前指令值及下个指令值执行逻辑运算。多工器电性连接于逻辑门的多个输出端以及逻辑电路的输出端。

17.在一实施例中,逻辑电路还包含输出暂存器,输出暂存器电性连接于该些多工器的其中个的输入端及该些多工器的其中另个的输出端之间,以形成回授路径。

18.在一实施例中,逻辑电路包含计数电路及多工器。计数电路用以记录指令信号中的该些指令值,且用以输出计数信号。多工器用以接收指令信号中的该些指令值,且由装置的输出端接收回授信号,其中多工器用以根据计数信号,选择性地输出接收到的指令信号或回授信号。

19.在一实施例中,取样电路包含相互串接的多个暂存器,且逻辑电路还包含逻辑电路。逻辑电路电性连接于该些暂存器中第暂存器的输出端,以及电性连接于该些暂存器中第二暂存器的输出端,且逻辑电路的输出端电性连接于计数电路的输入端。

20.在一实施例中,装置还包含输出暂存器,电性连接于逻辑电路的输出端。

21.在一实施例中,取样电路包含相互串接的多个暂存器,该些暂存器中的前级暂存器用以接收指令信号,且用以传输指令信号至该些暂存器中的次级暂存器。

22.在一实施例中,该些暂存器的每个包含d型正反器。

23.本揭示内容还关于一种显示驱动器,包含转换电路、信号过滤装置及驱动电路。转换电路用以接收至少一个原始信号,且用以从至少一个原始信号中取得指令信号。信号过滤装置电性连接于转换电路。信号过滤装置用以在不同时间点记录指令信号中的多个指令值。该些指令值对应于像素电路中的至少一条数据线,且信号过滤装置还用以判断该些指令值中的正确机率最高的指令值,以产生过滤指令信号。驱动电路电性连接于信号过滤装置,以接收过滤指令信号。驱动电路用以根据过滤指令信号驱动像素电路。

24.在一实施例中,该些指令值中的最具代表性的指令值是被判断为正确机率最高的指令值。

25.在一实施例中,该些指令值中的最具代表性的指令值为该些指令值中的重复性最高的指令值。

26.在一实施例中,重复性最高的指令值为出现频率最高的指令值。

27.在一实施例中,该些指令值中的正确机率最高的指令值为该些指令值中的连续出现次数最高的指令值。

28.在一实施例中,连续出现次数最高的指令值包含n个相同的连续值,且n为等于或大于2的正整数。

附图说明

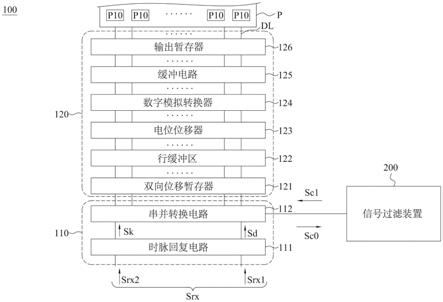

29.图1为根据本揭示内容的部分实施例的显示驱动器的示意图;

30.图2a为根据本揭示内容的部分实施例的信号过滤装置的示意图;

31.图2b为根据本揭示内容的部分实施例的方法的步骤流程图;

32.图3为根据本揭示内容的部分实施例的信号过滤装置的示意图;

33.图4为根据本揭示内容的部分实施例的信号过滤装置的示意图;

34.图5为根据本揭示内容的部分实施例的信号过滤装置的示意图。

35.【符号说明】

36.100:显示驱动器

37.110:转换电路

38.111:驱动电路

39.112:串并转换电路

40.120:驱动电路

41.121:双向位移暂存器

42.122:行缓冲器

43.123:电位位移器

44.124:数字模拟转换器

45.125:缓冲电路

46.126:输出多工器

47.200:信号过滤装置

48.210:取样电路

49.211:暂存器

50.212:暂存器

51.21(n-1):暂存器

52.21n:暂存器

53.220:逻辑电路

54.300:信号过滤装置

55.310:取样电路

56.311:暂存器

57.312:暂存器

58.320:逻辑电路

59.321:第一与非门

60.322:第二与非门

61.323:第三与非门

62.324:第四与非门

63.330:输出暂存器

64.400:信号过滤装置

65.410:取样电路

66.411:暂存器

67.420:逻辑电路

68.421:与门

69.422:或门

70.423:第一多工器

71.424:第二多工器

72.430:输出暂存器

73.500:信号过滤装置

74.510:取样电路

75.511:第一暂存器

76.512:第二暂存器

77.520:逻辑电路

78.521:计数电路

79.522:多工器

80.523:互斥或门

81.530:输出暂存器

82.dl:数据线

83.n31:第一节点

84.n32:第二节点

85.n33:第三节点

86.n41:第一输入端

87.n42:第二输入端

88.n43:输出端

89.n51:输出端

90.srx:原始信号

91.srx1:第一原始信号

92.srx2:第二原始信号

93.sc0:指令信号

94.sc1:过滤指令信号

95.sd:数据信号

96.sk:时脉信号

97.rb:信号

98.p:显示面板

99.p10:像素电路

100.s201-s204:步骤

具体实施方式

101.以下将以附图揭露本发明的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本发明。也就是说,在本发明部分实施方式中,这些实务上的细节是非必要的。此外,为简化附图起见,一些已知惯用的结构与元件在附图中将以简单示意的方式绘示。

102.于本文中,当一元件被称为“连接”或“耦接”时,可指“电性连接”或“电性耦接”。

“

连接”或“耦接”亦可用以表示二或多个元件间相互搭配操作或互动。此外,虽然本文中使用“第一”、“第二”、

…

等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。除非上下文清楚指明,否则该用语并非特别指称或暗示次序或顺位,亦非用以限定本发明。

103.在部分实施例中,显示驱动器接收到的指令将于不同时间被取样,以取得多个指令值。显示驱动器可透过不同的程序,判断出用以控制及驱动显示面板的正确机率最高的指令值。在部分实施例中,“正确机率最高的指令值”可以定义为该些指令值中最具代表性的指令值,例如该些指令值中重复性最高的指令值、出现频率最高的指令值或连续出现次数最高的指令值,故能有效避免信号被干扰,导致显示面板显示出异常画面。

104.请参阅图1所示,为根据本揭示内容的部分实施例的显示驱动器100的示意图。显示驱动器100用以驱动显示面板p。显示面板p包含至少一个像素电路p10。在部分实施例中,显示面板p可以由液晶面板(lcd)来实现,但本揭示内容不以此为限。

105.显示驱动器100包含转换电路110、信号过滤装置200及驱动电路120。显示驱动器100用以接收至少一个原始信号srx,再从原始信号srx中取得指令信号sc0。在过滤掉控制指令sc0中的错误值后,显示驱动器100根据过滤指令信号sc1驱动显示面板p中的像素电路p10。

106.转换电路110自原始信号srx取得指令信号sc0。在部分实施例中,原始信号srx用以驱动像素电路p10以显示出预期的像素亮度。控制指令sc0中的多个指令值对应于像素电路p10中的至少一条数据线dl。意即,控制指令sc0中的指令值可以是任何类型的控制指令,用以透过对应的数据线dl驱动像素电路p10。在部分实施例中,逻辑电路220根据过滤指令信号sc1设定像素电路p10的频宽、电流值、驱动频率中的其中一者。

107.请参阅图2a所示,信号过滤装置200应用于显示驱动器100,且包含取样电路210及逻辑电路220。取样电路210用以透过记录指令信号sc0中的多个指令值,在不同时间点取样指令信号sc0。举例而言,取样电路210依序接收多个指令值,如:“0、0、0、1、0、0”。

108.逻辑电路220电性连接于取样电路210,且用以接收指令值sc0。逻辑电路220还用以根据指令值产生过滤指令信号sc1,且用以提供过滤指令信号sc1以驱动像素电路p10。在部分实施例中,逻辑电路220用以根据指令值,判断出一个正确机率最高的指令值。在部分实施例中,前述“正确机率最高的指令值”可以判断为所有指令值中最具代表性的指令值,例如所有指令值中重复性最高的指令值、或所有指令值中连续出现次数最高的指令值。

109.图2b为根据本揭示内容的部分实施例的应用于显示驱动器100的方法的步骤流程图。如图1~2b所示,在步骤s201中,转换电路110接收原始信号srx,且自原始信号srx取得指令信号sc0。在部分实施例中,转换电路110接收第一原始信号srx1,且自第一原始信号srx1取得数据信号sd。转换电路110接收第二原始信号srx2,且自第二原始信号srx2取得时脉信号sk(即信号中的“clk”)。指令信号sc0可为包含于数据信号sd中(例如数据信号sd中的“cmd”)。转换电路110传送指令信号sc0至信号过滤装置200的取样电路210。

110.在步骤s202中,取样电路210在不同时间点记录指令信号中的多个指令值。指令值对应于像素电路p10的数据线dl。在部分实施例中,数据信号sd中的指令信号sc0包含多个依序发送出的指令值。意即,同一个指令信号sc0中的多个指令值应该要一致,但部分指令值可能会因为噪声或干扰而出错。当取样电路210在不同时间点接收指令信号sc0中的多个

指令值,取样电路210取样或储存指令值,再将取样后或储存的指令值传送至逻辑电路220进行分析。

111.在步骤s203中,逻辑电路220根据多个指令值判断出一个正确机率最高的指令值,且产生过滤指令信号sc1,过滤指令信号sc1对应于该正确机率最高的指令值(即,正确的指令值)。如前所述,该“正确机率最高的指令值”可以由所有指令值中最具代表性的指令值来判断,例如所有指令值中重复性最高的指令值、或者所有指令值连续出现次数最高的指令值。举例而言,指令信号sc0中的多个指令值为“0、0、0、1、0”,其中“0”出现4次、“1”出现1次。因此,“0”即为所有指令值中重复性最高的指令值,且同样是出现频率最高的指令值。另一方面,前述该些指令值中包含连续出现3次的指令值“0”,因此“0”为连续出现次数最高的指令值。

112.在步骤s204中,逻辑电路220传送过滤指令信号sc1至转换电路110。转换电路110传送接收到的过滤指令信号sc1至驱动电路120,以使驱动电路120根据过滤指令信号sc1驱动像素电路p10。在部分实施例中,逻辑电路220根据过滤指令信号sc1设定像素电路p10的频宽、电流值及驱动频率的其中之一。

113.请参阅图2a所示,在一实施例中,取样电路210包含多个暂存器211-21n,该些暂存器211-21n相互串接。多个暂存器211-21n中的前级暂存器根据时脉信号sk及信号rb(如:用来设定多个暂存器211-21n中初始值的信号)用以接收指令信号sc0,且用以传送指令信号sc0至多个暂存器211-21n中的次级暂存器。在部分实施例中,每个暂存器211-21n包含d型正反器。

114.举例而言,指令信号中的多个指令值为“0、0、0、1、0”。暂存器21n先接收及传送第一个“0”至暂存器21(n-1)。暂存器21(n-1)则接收及传送该第一个指令值“0”至次级暂存器。当暂存器211-21n接收到指令信号中的所有指令值后,暂存器211用以记录第一个指令值“0”、暂存器21n用以记录最后一个指令值“0”。逻辑电路220依序地记录指令信号中的所有指令值,且判断出正确机率最高的指令值。

115.图3为根据本揭示内容的部分实施例的信号过滤装置300的示意图。如图3所示,信号过滤装置300包含取样电路310及逻辑电路320。取样电路310透过多个节点n31-n33电性连接于逻辑电路320。逻辑电路320用以透过多个节点在不同时间分别记录多个指令值。换言之,透过第一节点n31在第一时间点记录该些指令值中的第一指令值、透过第二节点n32在第二时间点记录该些指令值中的第二指令值、透过第三节点在第三时间点记录该些指令值中的第三指令值,以使逻辑电路320可以将所有指令值中出现频率最高的指令值设定为指令信号sc1中正确机率最高的指令值。

116.在部分实施例中,取样电路310包含多个暂存器。暂存器311-312相互串接。每一个暂存器311-312用以接收指令信号sc0,且用以传送指令信号sc0至多个暂存器311-312中的次级暂存器。取样电路310的运作图2a中所述的取样电路210相同,故在此不再复述。

117.在部分实施例中,逻辑电路320包含多个逻辑门。该些逻辑门电性连接于节点的子集合(如:每个逻辑门的输入端分别连接两个节点,且每个逻辑门所连接到的节点不完全相同),以分别接收该些指令值的子集合。具体而言,逻辑电路320包含第一与非门321(n与门)、第二与非门322以及第三与非门323。第一与非门321电性连接于第一节点n31,以接收第一指令值,且电性连接于第二节点n32以接收第二指令值。第二与非门322电性连接于第

一节点n31以接收第一指令值,且电性连接于第三节点n33以接收第三指令值。第三与非门323电性连接于第二节点n32以接收第二指令值,且电性连接于第三节点n33以接收第三指令值。

118.在部分实施例中,逻辑电路320还包含第四与非门324。第四与非门324电性连接于第一与非门321、第二与非门322及第三与非门323的多个输出节点。因此,第四与非门324可将所有指令值中出现频率最高的指令值设定为正确机率最高的指令值,即过滤指令信号。换言之,所有指令值中“最具代表性的指令值”的定义为重复性最高的指令值,且“重复性最高的指令值”就是所有指令值中出现频率最高的指令值。

119.举例而言,指令信号中的多个指令值为“0、0、1”,第一节点n31接收第一指令值“0”,第二节点n32接收第二指令值“0”,第三节点n33接收第三指令值“1”。此时,与非门321-323的所有输出节点将会输出“1”,因此第四与非门的324输出端会输出“0”。意即,“0”就是所有指令值中出现频率最高的指令值。在部分实施例中,逻辑电路320传送出现频率最高的指令值至输出暂存器330。逻辑电路320的真值表如下所示:

120.n33n32n31sc100001000010011010010101101111111

121.在前述实施例中,如图3所示,逻辑电路320将出现频率最高的指令值设定为所有指令值中正确机率最高的指令值,但本揭示内容并不以此为限。

122.图4为根据本揭示内容的部分实施例的信号过滤装置400的示意图。信号过滤装置400对应于图1所示的信号过滤装置200。如图4所示,信号过滤装置400包含取样电路410、逻辑电路420及输出暂存器430。取样电路410包含暂存器411,暂存器411用以接收指令信号sc0中的指令值。暂存器411可以由d型正反器实现。逻辑电路420中的第一输入端n41用以指令信号sc0中的接收指令值。逻辑电路420中的第二输入端n42电性连接于取样电路410的输出端。

123.逻辑电路420可判断出指令信号sc0的多个指令值中具有n个相同的连续值的指令值,其中n为等于或大于2的正整数。逻辑电路420设定指令信号sc0中具有n个相同的连续值的指令值为正确机率最高的指令值,即过滤指令信号sc1。

124.在部分实施例中,逻辑电路420包含多个逻辑门及多个多工器。逻辑门用以对该些指令值中的当前指令值及下一个指令值执行逻辑运算。多工器电性连接于逻辑门的多个输出节点及逻辑电路420的输出端。具体而言,逻辑电路420包含一个与门421(and gate)、或门422(or gate)、第一多工器423及第二多工器424。与门421电性连接于取样电路410的输出端n42,且用以对该些指令值中的当前指令值及下一个指令值执行and逻辑运算。或门422电性连接于取样电路410的输出端n42,且用以对该些指令值中的当前指令值及下一个指令

值执行or逻辑运算。

125.举例而言,指令信号sc0中的指令值为“0、1、0

…”

,第一指令值“0”先被暂存器411储存。接着,当第二指令值“1”被输入至信号过滤装置400时,与门421透过输入端n41接收第二指令值“1”,且接收由暂存器411输出的第一指令值“0”。同理,或门422透过输入端n41接收第二指令值“1”,且接收暂存器411输出的第一指令值“0”。

126.第一多工器423的二个输入节点分别电性连接于与门421的输出端及输出暂存器430的输出端sc1。输出暂存器430电性连接于第一多工器423的输入端及第二多工器424的输出端之间,以形成回授路径。意即,第一多工器423的其中一个输入节点接收由逻辑电路420输出的回授信号。第一多工器423的控制节点电性连接于与门421的输出端。

127.第二多工器424的二个输入节点分别电性连接于或门422的输出端及第一多工器423的输出端。第二多工器424的输出端电性连接于逻辑电路420的输出端n43。第二多工器424的控制节点电性连接于或门422的输出端。逻辑电路420用以记录指令信号中当前的指令值的最大的连续出现次数。逻辑电路420的真值表如下所示,其中sc1[n+1]代表过滤指令信号sc1的当前输出值。sc1[n]代表过滤指令信号sc1前一次的输出值:

[0128][0129][0130]

在其他部分实施例中,逻辑电路包含计数器,用以计算及产生前述“n个相同的连续值”。因此,逻辑电路可判断出所有指令值连续出现次数最高的指令值。举例而言,图2a所示的逻辑电路220或图4所示的逻辑电路420可由计数器实现,且逻辑电路的真值表将如上列表格相同。

[0131]

前述n个相同的连续值中的“n”可为一个可调整的临界值(如:2、3、4

…

)。逻辑电路的结构可设计为计数电路,而无须使用n级d型正反器(例如当n为远大于2的数值时)。

[0132]

图5为根据本揭示内容的部分实施例的信号过滤装置400的示意图。信号过滤装置500对应于图1所示的信号过滤装置200。在其他部分实施例中,信号过滤装置500包含取样电路510、逻辑电路520及输出暂存器530。取样电路510包含多个相互串接的暂存器(如:第一暂存器511、第二暂存器512)。逻辑电路520包含计数电路521及多工器522。计数电路521用以记录指令信号的多个指令值,且用以输出计数信号。

[0133]

多工器522用以透过取样电路510接收多个指令值,且自信号过滤装置500的输出端n51接收回授信号。多工器522用以根据计数信号,选择性地输出接收到的指令信号或回

授信号。输出暂存器530电性连接于逻辑电路520的输出端。

[0134]

在部分实施例中,逻辑电路520还包含逻辑门,例如互斥或门523。互斥或门523电性连接于第一暂存器511的输出端及第二暂存器512的输出端。互斥或门523的输出端电性连接于计数电路521的输入端。在一实施例中,取样电路510透过第一暂存器511及第二暂存器512依序接收指令信号sc0的指令值。当指令信号sc0中的二指令值不同时,互斥或门523的输入节点所接收到的信号亦会不同,导致互斥或门523输出致能信号至计数电路521。接着,计数电路521会重新开始计数t。前述“n”为关联于计数电路521的计数数量(number of bits)。因此,所有指令值中连续出现次数最高的指令值将会被输出。

[0135]

请再参阅图1,其显示本揭示内容的部分实施例中,显示驱动器100的细部结构图。附图的结构是用于描述本揭示内容,但并不以此为限。转换电路110包含时脉回复电路111、串并转换电路112。时脉回复电路111接收原始信号srx1、srx2,以从第一原始信号srx1及第二原始信号srx2中取得时脉信号sk及数据信号sd。接着,时脉回复电路111传送时脉信号sk及数据信号sd至串并转换电路112。

[0136]

串并转换电路112用以对数据信号sd进行串并列转换(series to parallel),且用以将数据信号sd的指令信号sc0传送至信号过滤装置200。在部分实施例中,串并转换电路112传送转换后的数据信号sd至信号过滤装置200。

[0137]

信号过滤装置200用以在不同时间点记录指令信号的多组指令值。每一组指令值对应于像素电路p10中的数据线。信号过滤装置200还用以根据每组指令值判断出正确机率最高的指令值,以产生对应于正确机率最高的指令值的过滤指令信号sc1。

[0138]

串并转换电路112可根据过滤后的指令信号sc1重新产生数据信号sd,且传送数据信号sd及时脉信号sk至驱动电路120。

[0139]

驱动电路120电性连接于信号过滤装置200以接收过滤指令信号sc1,且驱动电路120包含双向位移暂存器121、行缓冲器122、电位位移器123、数字模拟转换器124、缓冲电路125及输出多工器126。双向位移暂存器121用以接收数据信号sd及时脉信号sk。

[0140]

数字模拟转换器124接收由行缓冲器122及电位位移器123处理过的数据信号sd,且将数据信号sd将数字格式转换为模拟格式,以能透过缓冲电路125驱动显示面板。输出多工器126可透过不同的数据线dl传送模拟的数据信号sd至不同的像素电路p10。

[0141]

如前所述,显示驱动器100可根据过滤指令信号sc1设置像素电路p10的频宽、电流值及驱动频率的其中之一。在部分实施例中,驱动电路120根据过滤指令信号sc1,透过双向位移暂存器121、电位位移器123或数字模拟转换器124以设定数据信号sd的电流或数值。

[0142]

虽然本揭示内容已以实施方式揭露如上,然其并非用以限定本揭示内容,任何熟悉此技艺者,在不脱离本揭示内容的精神和范围内,当可作各种更动与润饰,因此本揭示内容的保护范围当视所附的权利要求书所界定的范围者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1