液晶显示装置的制作方法

液晶显示装置

[0001]

本申请以日本专利申请第2019-114716(申请日:2019年6月20日)为基础,根据该申请主张优先权。本申请通过参照该申请而包含该申请的全部内容。

技术领域

[0002]

本实用新型涉及液晶显示装置。

背景技术:

[0003]

近年来,被称作存储器内置像素(mip)液晶等的液晶面板开始普及。该液晶面板中,各像素具有存储器,例如在显示静止图像那样的情况下,能够利用在存储器中记录的影像信号来显示图像,从而省电性良好。

[0004]

在搭载液晶面板的显示装置中,有液晶面板和对液晶面板进行控制的控制器例如经由中继基板相连接的情况。此外,例如有中继基板和控制器利用扁平柔性线缆等多个线缆相连接的情况。该情况下,作为显示装置的制造工序之一,需要进行将线缆的一端与中继基板侧的连接器连接并且将线缆的另一端与控制器侧的连接器连接的工序。

[0005]

该情况下,如果由于将线缆与连接器连接的工序中的失误等,在一部分线缆未结线的状态下使液晶面板点亮,则担心液晶面板发生点亮不良而损坏。

[0006]

现有技术文献

[0007]

专利文献

[0008]

专利文献1:日本特开2017-083768号公报

技术实现要素:

[0009]

因此,本实用新型要解决的课题在于,例如提供能够判定将基板间连接的多个线缆的连接状态的液晶显示装置。

[0010]

根据实施方式,液晶显示装置具有液晶面板、控制上述液晶面板的控制器、以及介于上述液晶面板与上述控制器之间而设置的中继基板。上述中继基板和上述控制器被多个线缆相连接。上述中继基板具有供上述多个线缆的一端连接的多个第1连接器。上述控制器具有微型计算机以及多个第2连接器,该多个第2连接器与上述多个第1连接器成一对地设置,供上述多个线缆的另一端连接。上述中继基板和上述控制器具有用于形成测试电路的布线图案,上述测试电路是使从上述微型计算机的输出引脚输出的测试信号向上述微型计算机的输入引脚反馈的电路,在形成上述多个第1连接器和上述多个第2连接器的对的各组中,上述测试电路从上述控制器侧向上述中继基板侧传送上述测试信号、并且从上述中继基板侧向上述控制器侧将上述测试信号送回。上述微型计算机从上述输出引脚输出上述测试信号,基于上述测试信号向上述输入引脚的反馈状况,判定将上述中继基板与上述控制器进行连接的上述多个线缆的连接状态。

附图说明

[0011]

图1是实施方式的显示装置的系统整体图。

[0012]

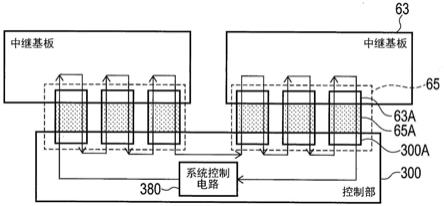

图2是用于说明在实施方式的显示装置中为了实现线缆的连接测试功能而设置于中继基板和控制部的布线图案的图。

[0013]

图3是表示在实施方式的显示装置中为了实现线缆的连接测试功能而设置于中继基板的布线图案的一例的图。

[0014]

图4是实施方式的显示装置中的ffc连接测试的时序图。

[0015]

图5是表示实施方式的显示装置所具备的ffc连接测试功能的处理顺序的流程图。

[0016]

图6是实施方式的显示装置的液晶显示面板的详细图。

[0017]

图7是实施方式的显示装置的锁存电路的框图。

[0018]

图8是表示实施方式的显示装置的锁存电路单元的图。

[0019]

图9是表示实施方式的显示装置的缓冲电路的图。

[0020]

图10是表示实施方式的显示装置的像素电路的图。

[0021]

图11是实施方式的显示装置的极性信号时序图。

[0022]

图12是表示实施方式的显示装置中的极性信号移位寄存器以及存储器电路的图。

[0023]

图13是实施方式的显示装置中的极性信号移位寄存器以及存储器电路的时序图。

[0024]

图14是表示实施方式的显示装置的像素周边的电路的第1例的图。

[0025]

图15是表示实施方式的显示装置的像素电极的配置的第1例的图。

[0026]

图16是表示实施方式的显示装置的像素周边的电路的第2例的图。

[0027]

图17是表示实施方式的显示装置的像素电极的配置的第2例的图。

[0028]

图18是表示用于说明实施方式的显示装置中的通孔的位置的电路的布局的图。

[0029]

图19是图18的电路的第1截面图(a-a)。

[0030]

图20是图18的电路的第2截面图(b-b)。

[0031]

标记说明

[0032]1…

显示装置,10

…

液晶显示面板,63

…

中继基板,63a

…

中继基板侧连接器,65

…

扁平柔性线缆群,65a

…

扁平柔性线缆,300

…

控制部,300a

…

控制部侧连接器,380

…

系统控制电路。

具体实施方式

[0033]

以下,参照附图对实施方式进行说明。

[0034]

另外,所公开的只不过是一例,关于本领域技术人员保持实用新型的主旨而进行的适当变更,容易想到的变更当然包含在本实用新型的范围内。此外,附图为了使说明更明确,与实施方式相比,有示意性表示各部分的宽度、厚度、形状等的情况,但只不过是一例,并不限定本实用新型的解释。在各图中,关于连续地配置的同一要素或类似要素,有时省略标记。此外,在本说明书和各图中,有时对于发挥与就已出现的附图已描述过的构成要素相同或类似的功能的构成要素附加同一参照标记,适当省略重复的详细说明。

[0035]

图1是本实施方式的显示装置1的系统整体图。

[0036]

显示装置1包括液晶显示面板10和对液晶显示面板10进行控制驱动的控制部300。

[0037]

液晶显示面板10具有对图像进行显示的显示区域20a以及将该显示区域20a包围

的边框状的非显示区域(位于显示区域20a周边的区域)20b。在液晶显示面板10所具有的显示区域20a中,多个像素100例如以矩阵状排列。多个像素100的每一个包含开关元件。作为开关元件,采用薄膜晶体管(tft:thin film transistor)。此外,虽然详情后述,但多个像素100的每一个具有采用具备能够存储影像信号(数据信号)的存储器电路的mip(memory in pixel)方式的结构,除了存储器电路以外例如具备反射电极。显示装置1被称作反射型存储器内置显示装置,不需要背灯,静止图像等使用在存储器电路中蓄积的数据来显示,所以已知是省电性良好的显示装置。

[0038]

标记30是扫描信号输出部,经由扫描线而与多个像素100分别包含的开关元件的栅极电极电连接。扫描信号输出部30输出进行将影像信号向像素100写入的控制的扫描信号。标记50是影像信号输出部,经由影像信号线而与多个像素100分别包含的开关元件的源极电极电连接。影像信号输出部50将影像信号以及显示控制信号向显示区域20输出。另外,多个像素100分别包含的开关元件的漏极电极与后述的存储器电路电连接。

[0039]

标记60是柔性电路基板(也称作fpc),将中继基板63与液晶显示面板10连接。中继基板63分为左右2个,将从控制部300经由扁平柔性线缆(ffc)群65发送来的信号、电源电压等向液晶显示面板10供给。即,本实施方式的显示装置1中,设想了将中继基板63和控制部300使用多个ffc和(在中继基板63侧和控制部300一对地设置的)ffc连接器而连接的情况。因而,在本实施方式的显示装置1中,作为制造工序之一,存在将ffc与ffc连接器进行连接的工序。

[0040]

此外,如果由于该将ffc与ffc连接器进行连接的工序中的失误等,在一部分ffc未结线的状态下使液晶显示面板10点亮,则担心液晶显示面板10发生点亮不良而损坏。

[0041]

因此,在本实施方式的显示装置1中,具备对将中继基板63和控制部300进行连接的多个ffc的连接状态进行判定的机制,抑制了由于ffc的连接异常引起的液晶显示面板10的损坏的风险。

[0042]

参照图2至图5,说明本实施方式的显示装置1所具备的、对将中继基板63与控制部300进行连接的多个ffc的连接状态进行判定的机制(ffc连接测试功能)。另外,这里,作为连接状态的判定对象,例示将中继基板63与控制部300连接的多个ffc,但该机制不限于此,能够通常地适用于例如将基板间连接的多个线缆。

[0043]

图2是用于说明为了实现ffc连接测试功能而设置于中继基板63和控制部300的布线图案的图。另外,图2所示的系统控制电路380的主要功能后述,系统控制电路380在这里设想为是能够将脉冲波形输入输出的mcu(micro control unit)。

[0044]

如图2所示,在中继基板63,设有供多个ffc65a的一端连接的多个连接器63a。另一方面,在控制部300,与中继基板63侧的多个连接器63a成一对地,设置有供多个ffc65a的另一端连接的多个连接器300a。

[0045]

此外,在中继基板63侧,关于多个连接器63a,分别设有将开头引脚(在ffc65a内以列状配置的多个信号线之中的位于一端的信号线所连接的引脚)和最终引脚(在ffc65a内以列状配置的多个信号线之中的位于另一端的信号线所连接的引脚)连接的布线图案。另一方面,在控制部300侧,设有:(1)将控制部300的输出引脚与多个连接器300a之中的位于开头的连接器300a的开头引脚进行连接的布线图案,(2)将多个连接器300a之中的依次连续的2个连接器300a的最终引脚和开头引脚进行连接的布线图案,(3)将多个连接器300a之

中的位于最后的连接器300a的最终引脚、与控制部300的输入引脚进行连接的布线图案。

[0046]

通过在中继基板63侧和控制部300侧设置这样的布线图案,如果将多个ffc65a连接于中继基板63侧的多个连接器63a和控制部300侧的多个连接器300a则形成测试电路,该测试电路是使从控制部300输出的脉冲波形向控制部300反馈的电路,在形成中继基板63侧的多个连接器63a与控制部300侧的多个连接器300a的对的各组中,该测试电路从控制部300侧向中继基板63侧传送脉冲波形,并且从中继基板63侧向控制部300侧送回脉冲波形。即,形成所谓的一笔书写(日语:一筆書

き

)状的电路。

[0047]

另外,图2中,可以想象,设于中继基板63侧的将连接器63a的开头引脚和最终引脚进行连接的布线图案从开头引脚侧向最终引脚侧跨中间引脚而配置,但该布线图案优选的是,例如如图3所示,将中间引脚绕过而配置。

[0048]

此外,在形成中继基板63侧的多个连接器63a和控制部300侧的多个连接器300a的对的各组中,从控制部300侧向中继基板63侧传送脉冲波形的信号线、从中继基板63侧向控制部300侧送回脉冲波形的信号线虽然不需要必须使用在ffc65a内以列状配置的多个信号线之中的两端的信号线,但是ffc65a的未结线状态在大部分情况下产生在位于端部的信号线中,因此优选使用ffc65a的两端的信号线。

[0049]

接着,参照图4以及图5,说明本实施方式的显示装置1所具备的、通过如以上那样形成的测试电路对多个ffc65a的连接状态进行判定的ffc连接测试功能。

[0050]

图4是ffc连接测试的时序图。

[0051]

系统控制电路380首先将任意脉冲波形作为测试信号从输出引脚输出。接着,系统控制电路380参照将被期待在特定定时(n[例如100]μs后)由测试电路反馈的任意脉冲波形进行输入的输入引脚的逻辑。并且,系统控制电路380将从输出引脚输出的任意脉冲波形的电压电平的逻辑与所参照的输入引脚的逻辑进行比较,调查它们的一致或不一致。在它们的逻辑一致的情况下,系统控制电路380判定为多个ffc65a全部是被正常连接的状态。另一方面,在它们的逻辑不一致的情况下,系统控制电路380判定为多个ffc65a中的至少一个是未结线的状态。

[0052]

系统控制电路380将该ffc连接测试反复执行例如4次。系统控制电路380如果输出引脚和输入引脚的逻辑在4次中全部一致,则判定为ffc连接没有问题,只要有1次不一致,则判定为ffc连接异常。在判定为ffc连接异常的情况下,系统控制电路380使显示装置1转移到关闭模式,将显示装置1紧急关闭。

[0053]

伴随向关闭模式的转移,系统控制电路380在执行了液晶显示面板10的电源断开处理后,向不接受来自外部的命令的状态转变。此外,在关闭模式下,在将显示装置1紧急关闭的情况下,使设置在例如控制部300的壳体周壁等处的led(light emitting diode)点亮。通过该led的点亮,报告ffc的连接异常。

[0054]

图5是表示ffc连接测试功能的处理顺序的流程图。

[0055]

在显示装置1起动时,在成为执行ffc连接测试的设定的情况下(步骤s1:是),系统控制电路380在执行起动处理之前执行ffc连接测试(步骤s2)。更具体而言,将以下步骤反复执行规定次数(步骤s2_1~s2_4),即:将任意脉冲波形作为测试信号从输出引脚输出,参照将被期待在特定定时(nμs后)由测试电路反馈来的任意脉冲波形进行输入的输入引脚的逻辑,调查它们的一致或不一致。

[0056]

系统控制电路380在通过ffc连接测试判定为ffc连接没有问题的情况下(步骤s3:是),执行起动处理(步骤s4)。另一方面,在判定为ffc连接有异常的情况下(步骤s3:否),系统控制电路380使显示装置1转移到关闭模式(步骤s5),将显示装置1紧急关闭(步骤s6)。

[0057]

此外,在没有成为执行ffc连接测试的设定的情况下(步骤s1:否),系统控制电路380不执行ffc连接测试,执行起动处理(步骤s4)。

[0058]

这样,在本实施方式的显示装置1中,具备对将中继基板63和控制部300连接的多个ffc的连接状态进行判定的机制,从而抑制由于fcc的连接异常引起的液晶显示面板10的损坏的风险。即,实现提供例如能够对将基板间连接的多个线缆的连接状态进行判定的液晶显示装置。

[0059]

返回图1,继续说明显示装置1的各部。

[0060]

控制部300进行处理以使从外部装置400发送来的信号适合于液晶显示面板10,将影像信号以及定时信号向液晶显示面板供给。

[0061]

控制部300具有影像信号控制电路310、传送信号接收电路360、电源电压电路370、系统控制电路380,影像信号控制电路310具有定时生成电路320、影像信号处理电路330、存储电路340、接口电路350。

[0062]

从外部装置400,经由线缆67提供电源电压、影像信号、控制信号。线缆67利用连接器410而与外部装置400连接,利用连接器390而与控制部300连接。

[0063]

从外部装置400发送来的通常的影像信号,与由红绿蓝3色的副像素构成的像素相对应,将每个颜色的灰度用6比特以上的数字数据表示。相对于此,在作为反射型存储器内置显示装置的本实施方式的显示装置1中,副像素是3色以上的n色,表现灰度的比特数是6比特以下的m比特。

[0064]

因而,控制部300根据从外部发送来的通常的影像信号、电源电压、控制信号,加工形成与作为反射型存储器内置显示装置的本实施方式的显示装置1对应的影像信号、电源电压、控制信号并向液晶显示面板10供给。

[0065]

在本说明书中,以副像素为4色且表现灰度的比特数是3比特的情况进行说明,但不限于4色3比特的情况。

[0066]

影像信号控制电路310将从外部发送来的影像信号转换为与反射型存储器内置显示装置对应的影像信号,并且形成显示所需要的定时信号并向液晶显示面板10供给。

[0067]

传送信号接收电路360接收从外部发送的、依照在短距离高速传送中使用的lvds等标准的影像信号。

[0068]

电源电压电路370根据从外部发送的例如直流12v的电源电压,生成反射型存储器内置显示装置所需要的电压。

[0069]

系统控制电路380对传送信号接收电路360进行控制而从外部接收影像信号,对影像信号控制电路310进行控制而将传送信号接收电路360接收到的影像信号进行转换,对电源电压电路370进行控制而生成并供给反射型存储器内置显示装置所需要的电压,经由连接器390而与外部装置400进行控制信号的输入输出。

[0070]

作为系统控制电路380的特征,除了上述那样的通常的控制部300的控制以外,还将显示所需要的定时信号(详细后述)向液晶显示面板10供给。系统控制电路380例如能够使用mcu(micro control unit),除了cpu和保存有程序的存储器以外还具有输入输出部。

系统控制电路380能够利用输入输出部,将显示所需要的定时信号向液晶显示面板10供给。

[0071]

本实施方式的显示装置1,如上述那样是像素100具有反射电极和存储器电路的反射型存储器内置显示装置,具有影像信号控制电路310使用来自将显示所需要的信号输出的控制器的信号的驱动模式(以下也称作控制器模式)、和使用在存储器电路中记录的信号的驱动模式(以下也称作存储器模式)。

[0072]

在控制器模式中,控制部300利用接口电路350进行来自系统控制电路380的控制信号的输入输出,在存储电路340中保存控制信号、影像信号,利用影像信号处理电路330将影像信号进行转换以与反射型存储器内置显示装置对应,利用定时生成电路320形成显示所需要的定时信号。

[0073]

进而,控制部300分为液晶显示面板10的左侧和右侧地供给影像信号、电源电压、控制信号。中继基板63被分为液晶显示面板10的左侧用和右侧用的2个,从中继基板63向液晶显示面板10,从各中继基板63连接有5个柔性电路基板60。经由柔性电路基板60将显示所需要的信号向液晶显示面板10供给。

[0074]

在存储器模式下,控制部300将影像信号处理电路330等的动作停止,从系统控制电路380将存储器模式所需要的定时信号向液晶显示面板10输出。

[0075]

图6是液晶显示面板10的框图。如上述那样,在显示区域20中像素100以矩阵状配置,但为了避免附图复杂,仅记载了1个像素100。

[0076]

多个像素100在由第1方向x以及第2方向y规定的x-y平面中以矩阵状排列。例如,在液晶显示面板10的分辨率是1920

×

1080的情况下,在第1方向x上排列配置1920个像素100,在第2方向y上排列配置1080个像素100。

[0077]

像素100是构成彩色图像的最小单位。像素100具备多个副像素110。图2中,例示了像素100具备在第1方向x以及第2方向y上各排列2个而配置的4个副像素110的情况。

[0078]

多个扫描线35以在第2方向y上排列配置的方式与扫描信号输出部30连接。扫描信号输出部30在非显示区域20b中形成有2个,2个扫描信号输出部30夹着显示区域20a对置配置。该情况下,一方的扫描信号输出电路30与奇数行的扫描线35连接,另一方的扫描信号输出电路30与偶数行的扫描线35连接。即,多个扫描线35交替地与2个扫描信号输出部30连接。

[0079]

在显示区域20的左右形成有扫描信号输出部30,扫描信号输出部30具有扫描移位寄存器200和缓冲电路250。

[0080]

按照从扫描移位寄存器200输出的定时信号,从缓冲电路250向扫描线35输出扫描信号。扫描信号在图中从上向下或从下向上依次被向扫描线35输出。

[0081]

在扫描信号输出部30,连接有与在第2方向y上配置的副像素110的数量相同数量的扫描线35。如上述那样,这里,设想了像素100具备在第1方向x以及第2方向y上各排列2个而配置的4个副像素110的情况,所以在第2方向y上配置的副像素110的数量是2,在如上述那样液晶显示面板10的分辨率是1920

×

1080的情况下,在液晶显示面板10中与扫描信号输出部30连接的扫描线35的数量为2

×

1080=2160。

[0082]

另外,设于副像素110的开关元件由极性相互反转的2个信号来控制,详情后述。因此,实际上,图2所示的扫描线35的每一个由用于输出这2个信号的2条信号线构成。这2条信号线都在第1方向x上延伸且在第2方向y上排列配置。

[0083]

多个影像信号线25以在与第2方向y交叉的第1方向x上排列配置的方式与影像信号输出部50连接。影像信号输出部50形成在非显示区域20b的图中下部。

[0084]

影像信号输出部50具有影像信号输出电路600、极性信号输出电路630、极性信号移位寄存器650、电平移位器(level shifter)660、防静电损坏电路670。

[0085]

影像信号输出电路600将影像信号向影像信号线25输出。极性信号输出电路630将极性信号向极性信号线45输出。极性信号移位寄存器650将表示极性信号输出电路630输出极性信号的定时的定时信号输出。电平移位器660将影像信号转换为影像信号输出电路600能够驱动的电压、电流。防静电损坏电路670是设于输入端子680的用于防止静电损坏的保护电路。

[0086]

影像信号输出部50连接有与在第1方向x上配置的副像素110的数量、以及每个颜色的表现灰度的比特数相对应的数量的影像信号线25。这里,由于设想了像素100具备在第1方向x以及第2方向y上各排列2个而配置的4个副像素110的情况,所以在1个像素100中在第1方向x上配置的副像素110的数量是2。此外,这里,由于设想了每个颜色的表现灰度的比特数是3比特的情况,所以对于1个副像素110,需要的影像信号线25的数量是3。即,对于在1个像素100中在第1方向x上相邻配置的2个副像素110,需要的影像信号线25的数量为2

×

3=6。

[0087]

由此,如上述那样,在液晶显示面板10的分辨率是1920

×

1080的情况下,在液晶显示面板10中与影像信号输出部50连接的影像信号线25的数量为6

×

1920=11520。

[0088]

另外,在1个像素100中,在第2方向y上相邻的副像素110中,影像信号线25被共用。

[0089]

图6所示的液晶显示面板10的情况下,使向11520条影像信号线25输出的影像信号为串行数据,向影像信号输出电路600传送,影像信号输出电路600将从影像信号控制电路310发送来的串行数据进行锁存并向影像信号线25输出。

[0090]

液晶显示面板10中,按每8像素列而具有锁存电路的单元,按48条(8像素

×

2副像素行

×

3比特)影像信号线25的每一条,将影像信号从影像信号控制电路310串行地输送。

[0091]

图6的影像信号输出电路600,24个锁存电路单元形成1个块610,具有10个块610。因而,影像信号输出电路600是48条

×

24单元

×

10块,具有11520个输出。

[0092]

极性信号输出电路630输出极性信号。极性信号是为了防止液晶组成物被施加直流电压而引起的劣化的信号,以一定周期相对于基准电压将极性反转了的电压作为极性信号被向像素100供给。

[0093]

极性信号移位寄存器650向极性信号输出电路630输出定时信号,以将极性信号不是一次输出而是依次输出。

[0094]

标记203是生成扫描信号输出部30用的定时信号的扫描定时信号生成部。标记663是扫描定时信号生成部用的电平移位器,标记673是扫描定时信号生成部用的防静电损坏电路,标记675是扫描信号输出部30用的防静电损坏电路。

[0095]

如上述那样,影像信号输出电路600具有多个块610,各块610具有多个锁存电路单元620(参照图7)。另外,本说明书中,以块610是10个且锁存电路单元620是24个的情况进行说明,但这些数量能够根据影像信号线25的数量等任意地选择。

[0096]

图7表示块610,具有24个锁存电路单元620。各锁存电路单元620向48条影像信号线25输出影像信号。关于输入,由于影像信号以串行数据从影像信号控制电路310发送来,

所以输入线613是1条。

[0097]

图8表示锁存电路单元620,输入线613向串联连接有49个锁存电路641的移位寄存器电路640输入。输入到第49个锁存电路641中的影像信号,在同步于由传送时钟线643供给的传送时钟而被依次传送,48个影像信号被锁存电路641保持的时刻,根据由第1读入(load)信号线645供给的第1读入信号,从移位寄存器电路640同时地被向第1级锁存电路629传送。

[0098]

从影像信号控制电路310继续传送影像信号,在48个影像信号再次被锁存电路641保持的时刻,根据由第1读入(load)信号线645供给的第1读入信号,从移位寄存器电路640同时地被向第1级锁存电路629传送。

[0099]

另外,在第2次从移位寄存器电路640向第1级锁存电路629传送影像信号之前,最初传送的48个影像信号根据由第2读入(load)信号线647供给的第2读入信号,从第1级锁存电路629被向第2级锁存电路627传送。

[0100]

在第1级锁存电路629和第2级锁存电路627中准备了影像信号后,由写入信号线649供给写入信号,开关电路625成为导通状态,向缓冲电路621传送影像信号,通过缓冲电路621将影像信号向影像信号线25写入。

[0101]

在通常的显示装置中,向影像信号线写入的影像信号是具有与所显示的灰度对应的电压的所谓模拟信号,但向影像信号线25写入的影像信号是具有2值的电压的所谓数字信号。其中,向影像信号线25写入的2值的电压的一方是在像素100中能够将液晶分子驱动的电压或者与能够将液晶分子驱动的电压相近的电压。

[0102]

即,为了将液晶分子驱动,使用10v左右的电压,向像素100供给的影像信号被像素100内的存储器电路所保持,但由于在像素100内没有设置电平移位器的余量,所以向像素100供给的电压使用能够将液晶分子驱动的电压或者与能够将液晶分子驱动的电压相近的电压。

[0103]

缓冲电路621如图9所示,具有电平移位器电路622和输出反相器电路623,利用电平移位器电路622将从第2级锁存电路627发送来的影像信号升压为能够将输出反相器电路623驱动的电压。标记vsh是缓冲电路621的高电压侧的电源电压线,vss是低电压侧的电源电压线。

[0104]

输出反相器电路623包括以能够将液晶分子驱动的电压作为电源电压而具有的多个反相器电路。构成输出反相器电路623的晶体管是能够将影像信号线25的负载充分驱动那样的大尺寸,例如沟道宽度是300μm以上,构成锁存电路单元620的电源电压是5v系的晶体管的70倍以上。

[0105]

因此,开关电路635成为导通状态的瞬间的输出反相器电路623中流通的贯通电压非常大,成为电源电压电路370的负担。

[0106]

影像信号输出电路600通过使开关电路635成为导通状态的定时错开而分散电源电压电路370的负担。具体而言,锁存电路单元620是24单元

×

10块的240单元,但将液晶显示面板10左右分为2个,经由中继基板63供给2系统的电源电压,使左右的120单元的锁存电路单元620的输出的定时错开。

[0107]

影像信号控制电路310制作按每个锁存电路单元620错开了定时的写入信号并向写入信号线649输出。

[0108]

接着,极性信号输出电路630也同样地,具有使电源电压电路370的负荷突出增大的问题。极性信号通过使用极性信号移位寄存器650,使输出的定时错开。

[0109]

另外,液晶显示面板10由于与上述的存储器模式对应,以能够在内部输出极性信号的方式,内置了极性信号输出电路630和极性信号移位寄存器650。

[0110]

从极性信号移位寄存器650,将定时信号依次向极性信号输出电路630供给,从极性信号输出电路630,依次隔开一定间隔而输出极性信号。极性信号移位寄存器650例如以240级形成,从240个极性信号输出电路630输出极性信号。

[0111]

在从设于液晶显示面板10的全部的极性信号输出电路630将极性信号一齐输出的情况下,与上述的影像信号输出电路600的情况同样地,有对电源电压电路370作用较大负荷的问题。因此,极性信号移位寄存器650通过以使各极性信号输出电路630的极性信号的输出定时错开的方式输出定时信号,使作用于电源电压电路370的负荷分散、减轻。作为具体结构,例如,将极性信号移位寄存器650以与极性信号输出电路630数量相同的级数形成,向与各级对应的极性信号输出电路630依次输出定时信号,从而使极性信号输出电路630的极性信号的输出定时错开。

[0112]

图10表示像素电路。标记120是像素驱动开关电路,130是像素存储器电路,140是写入开关电路。

[0113]

标记37和39是写入控制信号线,45是极性信号线,47是基准电压线,55是共通信号线,57和59是存储器电源线。

[0114]

像素存储器电路130将反相器(inverter)电路133和135串联连接而形成,反相器电路135的输出经由写入开关电路140的传输门145而与反相器电路133的输入连接。

[0115]

上述构造的像素存储器电路130将输入的数字数据(逻辑值“1”或“0”的2值)以1比特量来记录。因而,从影像信号线25供给数字数据。通过写入控制信号线37和39,传输门143成为导通状态的情况下,数字数据向像素存储器电路130输入,传输门143成为非导通状态,传输门145成为导通状态的情况下,数字数据被记录于像素存储器电路130。

[0116]

在像素存储器电路130的反相器电路133的输出是“0”(由存储器电源线50向像素存储器电路130供给的低电压)的情况下,像素驱动开关电路120的传输门129成为导通状态,经由极性信号线45供给的极性信号被向像素电极150供给。在反相器电路133的输出是“1”(由存储器电源线50向像素存储器电路130供给的高电压)的情况下传输门127成为导通状态,经由基准电压线47供给的基准信号被向像素电极150供给。

[0117]

与像素电极150对置而形成有共通电极155,在像素电极150与共通电极155之间配置液晶组成物。根据像素电极150与共通电极155的电位差,液晶分子的取向方向变化而进行显示。

[0118]

例如,使像素电极150与共通电极155之间产生电位差,沿像素电极150与共通电极155之间的电力线使液晶分子取向,不使从液晶组成物中通过的光的偏光方向变化,使夹着液晶组成物的2个偏光元件的偏光方向交差的情况下,显示成为黑(透射光量小)。此外,不使像素电极150与共通电极155之间产生电位差,液晶分子扭转取向,从液晶组成物中通过的光的偏光方向以90度旋转了的情况下,显示成为白(透射光量大)。

[0119]

本实施方式中,设像素电极150与共通电极155之间的电位差为5v左右,为了防止向液晶素组成物持续施加直流电压,以一定周期使向像素电极150施加的电压的极性反转。

[0120]

作为一例,设向共通电极155施加的电压为5v,向像素电极150施加的极性信号能够设为0v和10v。该情况下,为了使像素驱动开关电路120的传输门127和129成为导通状态,关于像素存储器电路130的电源电压,利用存储器电源线57供给约10v的电压,利用存储器电源线59供给约0v的电压。

[0121]

此外,从影像信号线25供给的数字数据的高电压为约10v,低电压为约0v。

[0122]

因而,上述的输出反相器电路623的电源电压也是,vsh为约10v,vss为约0v。

[0123]

显示装置1是反射型存储器内置显示装置,具有将从影像信号线25供给的数字数据的供给停止而利用在像素存储器电路130中记录的数据进行显示的显示模式,该情况下,图1所示的控制部300停止向影像信号线25的数字数据的输出,维持极性信号的输出。

[0124]

另外,控制部300不是仅停止向影像信号线25的输出,还停止向影像信号线25输出的数字数据的生成。本实用新型的反射型存储器内置显示装置,如上述那样具有4色的副像素110,如后述那样各副像素110将3比特的数据用面积灰度(area coverage modulation;日语:面積階調)显示。通常的显示装置中具有3色的副像素,灰度的各色利用从6比特到24比特的程度的数字数据来显示,因此控制部300将3比特以上的数字数据转换为3比特的数字数据,并且从3色的数据生成4色的数据。

[0125]

因而,在将数字数据的供给停止的情况下,控制部300停止影像信号控制电路310。但是,影像信号控制电路310具有定时生成电路320,如果将影像信号控制电路310停止则极性信号的输出也停止。

[0126]

为了极性信号的输出,由于如果继续维持影像信号控制电路310的动作则无法降低耗电,因此在控制部300中利用系统控制电路380输出对极性信号进行控制的信号。

[0127]

系统控制电路380由具有输出电路的mcu(微控制单元)构成,对输出电路进行控制,输出对极性信号输出电路630、极性信号移位寄存器650进行控制的信号。

[0128]

图11表示在存储器模式下系统控制电路380输出的、对极性信号移位寄存器650进行控制的信号、以及极性信号输出电路630的输出。在控制器模式下,对极性信号移位寄存器650进行控制的信号由影像信号控制电路310输出。

[0129]

标记stp是开始信号,ckp是时钟信号,pol是极性信号。对应于开始信号stp的输出开始,输出极性信号pol。极性信号移位寄存器650对应于时钟信号ckp,输出对极性信号输出电路630进行控制的定时信号。

[0130]

标记pola1是第1个极性信号输出电路630的输出,例如表示图2中最左侧的极性信号输出电路630的输出。极性信号移位寄存器650依次输出第2个、第3个极性信号输出电路630的定时信号,直到第240个极性信号输出电路630的定时信号为止。

[0131]

开始信号stp的输出间隔能够任意设定,在将时钟信号ckp输出了240次后,例如隔开8秒间隔来输出。任意的极性信号输出电路630的输出polan将按照接收到来自极性信号移位寄存器650的定时信号的时刻的极性信号pol的值的输出进行维持,通过在8秒后接收的来自极性信号移位寄存器650的定时信号,切换为按照该时刻的极性信号pol的值的输出。

[0132]

因而,极性信号输出电路630的输出不是仅通过来自极性信号移位寄存器650的定时信号进行切换,需要到接下来的定时信号为止将输出维持。

[0133]

图12表示将极性信号输出电路630的输出利用来自极性信号移位寄存器650的定

时信号进行切换、到接下来的定时信号为止将输出维持的电路,图13表示图12所示的电路的时序图。

[0134]

在图12中,标记651表示由多级的寄存器电路构成的极性信号移位寄存器650的第n级的寄存器电路。in是来自前级的输入信号,out表示第n级的寄存器电路651的输出。690是存储器电路,向反相器电路699输入极性信号pol的值,并将输出polan’输出。

[0135]

反相器电路699和693在开关元件695为导通状态下形成存储器电路。输出out为低电压的情况下反相器电路653输出高电压,开关元件695成为导通状态,反相器电路699和693将输出维持。

[0136]

如果寄存器电路651的输出out成为高电压,则开关元件695成为非导通状态,开关元件697成为导通状态,从而极性信号pol的值向反相器电路699输入。然后,如果输出out成为低电压,则极性信号pol成为非导通状态,开关元件695成为导通状态,反相器电路699和693将极性信号pol的值维持。

[0137]

图14表示像素周边的电路的框图。图14中,表示了以2行2列排列的4个副像素。

[0138]

夹着写入开关电路140,写入控制信号线37和39在图中上下配置。另外,图6中,将写入控制信号线37和39归纳为1条而作为扫描线35来表示。

[0139]

在像素存储器电路130的上下也形成有存储器电源线57和59。因而,存储器电源线57和59被从图6所示的显示区域20的左右供给。

[0140]

影像信号线25以2条在每个图中沿上下方向延伸,副像素每隔2列而形成。

[0141]

极性信号线45和基准电压线47在显示区域20的上下方向上延伸,极性信号和基准电压被从图中下侧供给。极性信号线45和基准电压线47为了强化电压供给能力而与影像信号线25相比较粗地形成。

[0142]

标记820表示将像素驱动开关电路120和像素电极150连接的通孔的位置。

[0143]

经由影像信号线25供给的影像信号,经由通过写入控制信号线37和39而成为导通状态的写入开关电路140而被记录于像素存储器电路130。像素存储器电路130通过存储器电源线57和59而被供给电源电压,通过像素存储器电路130的输出而控制像素驱动开关电路120的通断。

[0144]

像素驱动开关电路120按照像素存储器电路130的输出,将通过极性信号线45或基准电压线47供给的电压向像素电极150施加。

[0145]

接着,在图15中表示像素电极150的配置。图中,纵向排列有2个像素。一个像素以与4色的滤色器对应的方式形成有副像素的像素电极150。各色的副像素形成为,像素电极150的面积的大小为1:2:4,利用面积灰度来显示3比特的数字数据。

[0146]

标记150r1、150r2、150r3是与红色的滤色器对应的像素电极,像素电极150r1被写入3比特的红色的数据的(从下位开始数)第1比特的值。同样,像素电极150r2被写入红色的数据的第2比特的值,像素电极150r3被写入红色的数据的第3比特的值。

[0147]

接着,像素电极150b1被写入蓝色的数据的第1比特的值,像素电极150b2被写入蓝色的数据的第2比特的值,像素电极150b3被写入蓝色的数据的第3比特的值。

[0148]

标记150yg1、150yg2、150yg3和150bg1、150bg2、150bg3是被写入绿色的数据的值的像素电极,像素电极150yg1~3和像素电极150bg1~3对应于使相同的绿色波段的光但不同波长的光透射的滤色器。

[0149]

图中,尽管像素电极150的大小不同,通孔820配置在与像素电极150重叠的位置。例如,相对于像素电极150b1,像素电极150b2的面积为2倍,像素电极150b2从通孔820的位置一度向下方延伸,与将自身驱动的像素存储器电路130重叠地形成后,朝向与将像素电极150b1驱动的像素存储器电路130重叠的位置(图中左侧)延伸而形成。

[0150]

进而,相对于像素电极150b1,像素电极150b3的面积为4倍,像素电极150b3从通孔820的位置一度向下方延伸,与将自身驱动的像素存储器电路130以及写入开关电路140重叠地形成后,从将(图中下侧的)相邻的像素的像素电极150bg3驱动的写入开关电路140-2,与将像素电极150bg1驱动的写入开关电路140-2重叠地(向图中左侧)延伸而形成。

[0151]

在图16中表示将存储器电源线57和59沿着极性信号线45和基准电压线47在图中沿上下方向延伸配置的结构。

[0152]

在图14所示的结构中,存储器电源线57和59与影像信号线25交叉,在与影像信号线25之间形成了耦合电容。因此,如果影像信号线25的电压以例如高电压侧10v、定电压侧0v为振幅,则产生存储器电源线57和59的电位变动的问题。

[0153]

如果存储器电源线57和59的电位变动,则使像素驱动开关电路120通断的电压变动,例如,传输门127和129同时成为导通状态,极性信号线45和基准电压线47短路而引起显示不良的情况可能发生。

[0154]

因此,以存储器电源线57和59不与影像信号线25交叉的方式,采用图14所示的将存储器电源线57和59在图中沿上下方向延伸配置的结构。

[0155]

将存储器电源线57和59在图中沿上下方向延伸配置的情况下,能够与构成影像信号线25的导电层同层(相同材料)地形成存储器电源线57和59。图14所示的将存储器电源线57和59与影像信号线25交叉形成的结构的情况下,将存储器电源线57和59用与写入控制信号线37和39同层的导电层形成。写入控制信号线37和39基于工艺上的理由而由比较高电阻的mow等高熔点金属及其合金形成,相对于此影像信号线25由铝等低电阻的金属及其合金形成,所以通过将存储器电源线57和59用比写入控制信号线37和39低电阻的导电层形成从而实现电源供给能力的强化。

[0156]

此外,能够将存储器电源线57和59从按每块形成的输入端子680直线性地且短距离地配置,从而也强化了电源供给能力。

[0157]

在图17中,表示将存储器电源线57和59沿着极性信号线45和基准电压线47排列4条而配置的情况的反射电极的位置。图中横向地追加2条布线,各电路的横向的宽度变窄。由于能够形成各电路的横宽变窄,从而产生如下问题,即:形成将像素驱动开关电路120和像素电极150连接的通孔820的位置接近像素电极150的端部。

[0158]

例如,将被写入绿色的数据的第1比特的值的像素电极150b1、和像素驱动开关电路120连接的通孔820接近像素电极150b1的端部。因此,产生使通孔820的位置移动的需要。

[0159]

在图18中,表示用于说明通孔820的位置的电路的布局。图中左上表示对应于像素电极150yg1的像素驱动开关电路120和像素存储器电路130的布局,右上表示对应于像素电极150bg1的像素驱动开关电路120和像素存储器电路130的布局,左下表示对应于像素电极150r1的像素驱动开关电路120和像素存储器电路130的布局,右下表示对应于像素电极150b1的像素驱动开关电路120和像素存储器电路130的布局。

[0160]

像素存储器电路130由反相器电路133和135构成,反相器电路133和135共通地将

半导体层1310形成为环状,反相器电路133的输出与反相器电路135的输入连接,反相器电路133的栅极电极1320与传输门127和129的一方的栅极电极1220连接,反相器电路133的输出和反相器电路135的输入与传输门127和129的另一方的栅极电极1225连接。

[0161]

像素驱动开关电路120也将半导体层1210形成为环状,但在与像素电极150yg1和像素电极150r1对应的像素驱动开关电路120中,通孔820a形成在半导体层1210的环的孔的位置,以使得不与半导体层1210重叠。相对于此,在与像素电极150bg1和像素电极150b1对应的像素驱动开关电路120中,通孔820b从半导体层1210的环的中央,向像素电极150yg1和像素电极150r1侧移动,通孔820b形成在与半导体层1210重叠的位置。

[0162]

通孔820b一直移动到与半导体层1210重叠的位置,从而能够使像素电极150bg1与像素电极150b1的连接的位置具有裕度。

[0163]

在图19中表示图18a-a线的截面图。像素电极150将由铝等形成的反射电极1510和反射电极1510覆盖,由用ito等形成的透明电极1520形成。

[0164]

标记1240是用玻璃、树脂等形成的基板,在基板1240之上形成用sio、sin形成的基底膜1250,在基底膜1250之上以环状形成半导体层1210。在半导体层1210之上形成绝缘膜1260,在绝缘膜1260之上形成像素驱动开关电路120的栅极电极1220和1225。

[0165]

在栅极电极1220和1225之上形成有绝缘膜1270,在绝缘膜1270之上形成有中继电极1230。在绝缘膜1270和1260中形成通孔1235,将中继电极1230和栅极电极1220以及1225连接。

[0166]

在中继电极1230之上形成绝缘膜1280,在绝缘膜1280中形成通孔820a,将中继电极1230和反射电极1510连接。

[0167]

在图19所示的a-a截面中,通孔820a形成在环状的半导体层1210的中间附近,而在图20所示的b-b截面中,通孔820b以与环状的半导体层1210的一方重叠的方式,形成在从中央偏向一方的半导体层1210的位置。

[0168]

如以上说明,根据本实施方式,在中继基板63侧和控制部300设置用于判定多个ffc的连接状态的布线图案,从而抑制由fcc的连接异常引起的液晶显示面板10的损坏的风险。即,根据本实施方式,能够提供能够判定例如将基板间连接的多个线缆的连接状态的液晶显示装置。

[0169]

作为本实用新型的实施方式,基于上述的显示装置,本领域技术人员适当进行设计变更而实施得到的全部显示装置只要包含本实用新型的主旨则属于本实用新型的范围。

[0170]

在本实用新型的思想范畴中,关于本领域技术人员能够想到各种变更例及修正例的方式、这些变更例及修正例,也属于本实用新型的范围。

[0171]

例如,对上述各实施方式,本领域技术人员适当进行构成要素的追加、消除或设计变更而得到的形态、或者进行工序的追加、省略或条件变更而得到的形态,只要具备本实用新型的精神,就包含在本实用新型的范围中。

[0172]

此外,关于由在本实施方式中描述的形态所带来的其他作用效果,从本说明书记载得到明确的、或者本领域技术人员适当想到的形态当然是由本实用新型带来的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1