显示装置的制作方法

1.本技术涉及有源矩阵型显示装置。

背景技术:

2.使用有机发光二极管(下文称为oled)元件等作为发光元件的显示装置是已知的。在显示装置中,对应于来自垂直扫描电路的扫描线(栅极线)和来自水平扫描电路的数据线(信号线)的交点处的像素,设置包括发光元件、晶体管等的像素电路。当具有取决于像素的灰度等级的电位的数据信号施加到像素电路中的晶体管的栅极时,晶体管向发光元件供应取决于栅极和源极之间的电压的电流,并且发光元件发射具有取决于灰度等级的辉度的光。

3.例如,在专利文献1中,与像素11r中的保持电容器cs的端子33b相比,与像素11b相邻的像素11r中的晶体管tdr和tws被布置成远离像素11b。与像素11g中的保持电容器cs的端子33c相比,与像素11b相邻的像素11g中的晶体管tdr和tws被布置成远离像素11b。描述了入射在相邻像素11b和11g中的晶体管tdr和tws上的从像素11b漏出的光l的量减少,以利用这种布置减少这些晶体管的长期可靠性的劣化。

4.引用列表

5.专利文献

6.专利文献1:日本专利申请公开号2010-217326

技术实现要素:

7.本发明要解决的问题

8.在常规的像素电路中,在自身像素的阳极与自身像素的栅极之间存在寄生电容器,以及在相邻像素的阳极与自身像素的栅极之间存在寄生电容器。因此,阳极的电位波动经由这些寄生电容器对自身像素的栅极施加影响,使得栅极电位波动并且发生辉度偏差。此外,寄生电容器导致在加色混合时辉度的降低或者导致颜色偏差。专利文献1不能解决寄生电容器的影响的问题。

9.因此,本技术的目的是提供能够抑制寄生电容器的影响的显示装置。

10.问题的解决方案

11.本技术提供了一种显示装置,该显示装置具有多条扫描线、多条数据线、以及其中像素由扫描线和数据线指定的像素单元,该显示装置包括:

12.发光元件,设置在像素单元的每个像素电路中;以及

13.驱动晶体管,向发光元件提供驱动信号;

14.其中,显示装置具有拉开发光元件的阳极与驱动晶体管的控制端子之间的距离的布局。

附图说明

15.图1是包括可以应用本技术的有源矩阵型驱动电路的有机el显示装置的框图。

16.图2是示出本技术的实施方式的示意性配置的框图。

17.图3是示出了可以应用本技术的像素电路的配置实例的连接图。

18.图4是示出了传统像素电路的布局的示意图。

19.图5为示出图4的部分横截面的示意图。

20.图6是用于说明传统像素电路的操作的时序图。

21.图7是用于描述由传统像素电路形成的寄生电容器的示意图。

22.图8是用于描述传统像素电路的问题的曲线图。

23.图9是示出本技术的第一实施方式的布局的示意图。

24.图10是示出图9的部分横截面的示意图。

25.图11是用于说明第一实施方式的操作的时序图。

26.图12是示出第一实施方式的变形例的布局的示意图。

27.图13是示出本技术的第二实施方式的布局的示意图。

28.图14是示出图13的部分横截面的示意图。

29.图15是示出本技术的第二实施方式的布局的示意图。

30.图16是示出第二实施方式的变形例的布局的示意图。

31.图17是用于描述本技术的第三实施方式的布局的示意图。

32.图18是本技术的第三实施方式的布局的示意图。

具体实施方式

33.以下描述的实施方式是本技术的优选具体实例,并且给出了各种技术上的优选限制。然而,本技术的范围不限于这些实施方式,除非在以下描述中存在具体限制本技术的描述。此外,在以下描述中,相同的名称和参考标号表示相同或相似的组成元件,并且将适当地省略多余的描述。

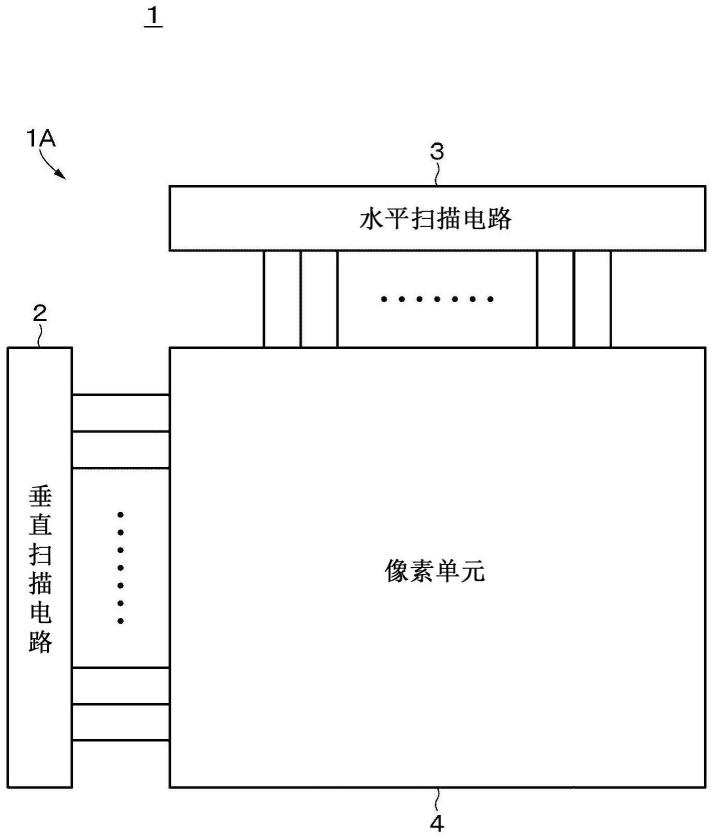

34.本技术可应用于包括图1中所示的有源矩阵型驱动电路的有机el显示装置1(电光装置)。显示装置1包括显示面板1a和控制显示面板1a的操作的控制电路。

35.显示装置1被提供有与数据同步信号同步的数字图像数据。图像数据是定义例如要在显示面板1a上显示的图像的像素的8位灰度等级的数据。此外,同步信号是包括垂直同步信号、水平同步信号和点时钟信号的信号。控制电路基于同步信号生成各种控制信号并且将控制信号供应至显示面板1a。此外,控制电路包括电压生成电路。电压生成电路向显示面板1a提供各种电位。此外,控制电路基于图像数据生成模拟图像信号。

36.如图1所示,在显示面板1a中,垂直扫描电路(扫描线驱动电路)2、水平扫描电路(数据线驱动电路)3和像素单元4形成在半导体基板上,例如,硅基板。来自垂直扫描电路2的多条扫描线相对于像素单元4在水平方向上延伸,并且来自水平扫描电路3的多条数据线在垂直方向上延伸。相对于在垂直方向上延伸的数据线和在水平方向上延伸的扫描线,像素电路以矩阵形式连接。

37.如图2所示,在像素单元4中,相对于矩阵形式的像素电路阵列,沿着行方向(像素行中的像素的排列方向),为每个像素行布线三条扫描线(第一扫描线5、第二扫描线6以及

第三扫描线7)。此外,相对于矩阵形式的像素电路阵列,数据线8沿着列方向(像素列中的像素的排列方向)为每个像素列布线。注意,像素单元4设有与红(r)、蓝(b)、绿(g)所示的三原色的像素对应的像素电路(称为子像素)。这三个像素表达彩色图像的一个点。注意,表达一个单位(一个点)的像素的组合不限于此,并且可以通过添加用于改善辉度的白色(w)像素来配置,或者可以通过添加用于扩大颜色再现范围的互补像素来配置。即,本技术可应用于一个单元包括n个子像素的情况。

38.第一扫描线5中的每一者、第二扫描线6中的每一者以及第三扫描线7中的每一者各自与垂直扫描电路2的对应行的输出端连接。每条数据线8与水平扫描电路3的对应列的输出端连接。

39.垂直扫描电路2包括移位寄存器电路等。当根据灰度等级将数据信号写入像素单元4的每个像素电路时,垂直扫描电路2将写入扫描信号ws顺次供应至第一扫描线5中的每一个,以逐行顺次扫描(行顺次扫描)像素单元4的每个像素电路。此外,垂直扫描电路2将第一控制信号ds提供至每个第二扫描线6以控制像素电路的发光/不发光(消光)。此外,垂直扫描电路2将第二控制信号az提供至每个第三扫描线7以执行控制以使像素电路在非发光时期不发光。注意,垂直扫描电路2可以不通过线顺序扫描而是通过寻址方法来执行扫描。

40.水平扫描电路3根据上述灰度级将数据信号的信号电位(信号电压vdata)和校正电位(基准电压vofs)作为写入电压选择性地写入每条数据线8中。即,信号电压vdata是取决于灰度等级(辉度)的电压。当执行阈值校正操作时,使用基准电压vofs。

41.从水平扫描电路3输出的数据信号以垂直扫描电路2通过扫描而选择的像素行为单位,经由每条数据线8写入像素单元4的每个像素电路。即,水平扫描电路3采用逐行(逐行,line by line)写入数据信号的行顺序写入驱动模式。

42.图3示出了一个子像素的像素电路的实例。像素电路与第一扫描线5、第二扫描线6和来自垂直扫描电路2的第三扫描线7以及来自水平扫描电路3的数据线8连接。像素电路包括四个晶体管(驱动晶体管drvtr、第一晶体管wstr、第二晶体管dstr以及第三晶体管aztr)、保持电容器cs、辅助电容器csub以及oled。这里,注意p沟道晶体管用作四个晶体管。即,像素电路包括pch4tr2c。可以使用n沟道晶体管。

43.驱动晶体管drvtr具有经由晶体管dstr与供电线11连接的源极,以及与oled的阳极连接以控制流向oled的电流的漏极。高电位电源(vccp)被提供给供电线11。oled的阴极与电源线12连接作为公共电极,并且被设置为低电位电源(vcath)。

44.在晶体管wstr(第一晶体管)中,栅极与第一扫描线5连接,源极和漏极中的一个(例如,源极wss)与数据线8连接,并且另一个(例如,漏极wsd)与驱动晶体管drvtr的栅极(drvg)连接。晶体管wstr根据写入扫描信号ws将数据线电位(灰度电位)写入到驱动晶体管drvtr的栅极(drvg)中。

45.在晶体管dstr(第二晶体管)中,栅极与第二扫描线6连接,源极和漏极中的一个与供电线11连接,并且另一个与驱动晶体管drvtr的源极连接,以控制对驱动晶体管drvtr的电力供应。

46.在晶体管aztr(第三晶体管)中,栅极与第三扫描线7连接,源极和漏极中的一个与驱动晶体管drvtr的漏极和oled的阳极连接,并且另一个与电源vss的电源线13连接。

47.保持电容器cs连接在驱动晶体管drvtr的栅极和源极之间并且保持驱动晶体管

drvtr的栅极-源极电压vgs。辅助电容器csub连接在驱动晶体管drvtr的源极与固定电源vccp之间,并且通过与保持电容器cs电容耦合来执行抑制驱动晶体管drvtr的源极电压的波动和执行驱动晶体管drvtr的阈值校正的功能。

48.在具有上述配置的有机el显示装置1中,每个像素电路中的oled的发光辉度由驱动晶体管drvtr控制的电流控制。因此,当驱动晶体管drvtr的阈值电压vth在每个像素电路中变化时,发光辉度对于每个像素变化,并且画面的一致性受损。因此,在有机el显示装置1中,根据行顺序扫描执行上述阈值校正,以便减少由驱动晶体管drvtr的阈值电压vth的变化引起的发光辉度的变化。

49.在描述本技术之前,将描述常规技术的问题。在图4中示出了上述像素电路中的四个晶体管dstr、wstr、drvtr和aztr的布局,并且在图5中示出了沿着图4中的点划线表示的线的截面图(层)。注意,图示布局和横截面的附图是示意性的。此外,在图4和布局的其他附图中,在增加到形成dstr、wstr、drvtr和aztr的区域的参考标号中省略tr。

50.在布局图中,阱抽头用于提供vccp。晶体管ws包括半导体层21、源电极wss、漏电极wsd、栅极绝缘膜21i以及栅电极21g。此外,示出了oled的阳极21a的横截面。晶体管ws的漏极wsd与驱动晶体管drvtr的栅极(drvg)电连接,并且oled的阳极与驱动晶体管drvtr的漏极(drvd)电连接(参见图3)。

51.图6示出了上述像素电路的驱动时序图。晶体管dstr、aztr和wstr导通,同时ds、az和ws处于低电平,并且晶体管dstr、aztr和wstr截止,同时ds、az和ws处于高电平。在写入周期中,因为az和ws处于低电平,所以晶体管aztr和wstr导通,取决于期望辉度的电压被写入驱动晶体管drvtr的栅极,并且确定流到oled的电流。驱动晶体管drvtr的源极和栅极之间的电压逐渐增加。接下来,在发光周期中,晶体管wstr和aztr截止,ds被设置为低电平,晶体管dstr导通,取决于驱动晶体管drvtr的栅极电压的电流流向oled,并且oled发光。

52.如图7所示,在自身像素的驱动晶体管drv的漏极和自身像素的第一晶体管wstr的漏极被设置为彼此靠近的情况下,在其间生成寄生电容器cp。当oled的阳极的电位改变时,与oled的阳极电连接的驱动晶体管drvtr的漏极的电位也改变。当驱动晶体管的漏极的电位改变时,晶体管wstr的漏极的电位也由于寄生电容器cp而改变。

53.当晶体管wstr的漏极的电位改变时,与晶体管wstr的漏极电连接的驱动晶体管drvtr的栅极的电位也改变。当oled的阳极的电位以这种方式改变时,驱动晶体管drvtr的栅极的电位由于驱动晶体管drvtr的漏极与晶体管wstr的漏极之间的寄生电容器cp而改变。

54.此外,在相邻像素(另一个像素)的驱动晶体管drv的漏极和自身像素的第一晶体管wstr的漏极被设置为彼此靠近的情况下,在其间生成寄生电容器cp'。当另一个像素的oled的阳极的电位改变时,与oled的阳极电连接的另一个像素的驱动晶体管drvtr的漏极的电位也改变。当另一个像素的驱动晶体管的漏极的电位改变时,由于寄生电容器cp',自身像素的晶体管wstr的漏极的电位也改变。

55.当晶体管wstr的漏极的电位改变时,与晶体管wstr的漏极电连接的自身像素的驱动晶体管drvtr的栅极的电位也改变。当另一个像素的oled的阳极的电位以这种方式改变时,驱动晶体管drvtr的栅极的电位由于驱动晶体管drvtr的漏极与晶体管wstr的漏极之间的寄生电容器cp'而改变。

56.如上所述,由于寄生电容器cp和cp'引起的oled阳极的电位波动产生自身像素的驱动晶体管drvtr的栅极电位,并且发生辉度偏差。随着辉度变高,这种现象显著地出现,因为阳极的波动量变大。即,随着辉度变得更高,寄生电容器cp和cp'产生与根据期望辉度的理想驱动栅极电压(由虚线表示)的更大差异的可能性,并且获得偏离理想伽玛曲线的伽玛曲线,如图8中的虚线所示。

57.在传统像素电路中,由于阳极在发光时的电压波动,通过寄生电容器cp和cp'使栅极电压高于理想驱动晶体管drvtr的栅极电压。在包括p沟道晶体管的像素电路中,随着栅极电压变高,栅极-源极电压降低,并且辉度变得低于期望辉度。阳极的电压波动随着辉度变高而变大,并且与理想伽玛曲线的偏差量随着辉度变高而变大。

58.本技术的第一实施方式解决了这种问题。在第一实施例中,阱的触点(阱抽头)被布置在驱动晶体管drvtr的栅极与发光元件oled的阳极之间。图9示出了第一实施方式的布局,并且图10示出了沿图9中由单点划线表示的线的截面图。

59.如图9和图10所示,在相邻像素之间,阱抽头21w位于自身像素的阳极与自身像素的驱动晶体管drvtr的栅极(drvg,wsd)之间以及相邻像素的阳极与自身像素的驱动晶体管drvtr的栅极(drvg,wsd)之间,并且因此,由于屏蔽效应,可以抑制如现有技术中那样形成寄生电容器cp和cp'。因此,可以抑制自身像素的阳极和相邻像素的阳极的电压波动对晶体管wstr的漏极wsd(驱动晶体管drvtr的栅极drvg)的影响。

60.因此,如图11所示,当写入周期转换到dstr导通的发光周期时,第一实施方式可以抑制驱动晶体管drvtr的栅极变得高于理想电压。因此,可以抑制灰度-辉度特性(伽玛曲线)与理想特性的偏差。

61.注意,如图12所示,阱抽头不限于被配置为提供vccp的阱抽头,而可以是被配置为提供接地或负电位的阱抽头。

62.接下来,将描述本技术的第二实施方式。第二实施方式具有这样的布局,其中控制写入驱动晶体管drvtr的栅极和oled的阳极的时序的晶体管wstr的信号节点(不与驱动晶体管drvtr的栅极连接的节点,例如,晶体管ws的源极ws)在某个像素电路中彼此接近。利用这样的第二实施方式,可以减小驱动晶体管drvtr的栅极与阳极之间的寄生电容器并抑制伽马偏差。图13示出了第二实施方式的布局,并且图14示出了沿着图13中由单点划线表示的线的截面图。

63.如图13和图14所示,采用这样的布局,其中晶体管wstr的漏极wsd和源极wss的位置被上下反转,wstr的源极(信号节点)wss和oled的阳极电极21a彼此接近,并且此外,wstr的漏极wsd(驱动晶体管drvtr的栅极drvg)远离阳极电极21a。

64.从示出自身像素和相邻像素的布局的图15可以看出,在第二实施方式中,可以使自身像素的晶体管wstr的漏极wsd(栅极drvg)与自身像素的阳极之间的距离以及自身像素的晶体管wstr的漏极wsd(栅极drvg)与相邻像素的阳极之间的距离大于现有技术中的那些距离。因此,可以抑制在自身像素的阳极与自身像素的驱动晶体管drvtr的栅极之间的寄生电容器cp,以及在相邻像素的阳极与自身像素的驱动晶体管drvtr的栅极之间的寄生电容器cp'。因此,可以抑制自身像素的阳极和相邻像素的阳极的电压波动对晶体管wstr的漏极wsd(驱动晶体管drvtr的栅极drvg)的影响。

65.图16示出了第二实施方式的第一变形例。自身像素的布局与图13和图15中的布局

相似。另一方面,在相邻像素的布局中,晶体管wstr的位置相对于驱动晶体管drvtr左右反转。以这种方式,可以使晶体管wstr的漏极wsd(栅极drvg)与相邻像素的阳极之间的距离比图15中示出的布局中的更大,并且可以进一步抑制寄生电容器cp'。

66.接下来,将描述本技术的第三实施方式。在像素单元具有与红(r)、蓝(b)和绿(g)三原色的像素对应的像素电路(子像素)的配置的情况下,两种颜色中的一种颜色的像素电路的布局左右反转。结果,可以抑制相邻像素的阳极波动对两种颜色的影响,并且可以抑制伽马偏差。

67.如参考图7所描述的,当oled发光时,阳极的电位波动经由相邻像素的阳极与自身像素的驱动晶体管drvtr的栅极之间的寄生电容器cp'对自身像素的栅极的驱动晶体管drvtr施加影响,使得栅极电压波动并且发生辉度偏差。随着辉度变高,该现象显著出现,因为阳极电位的波动量变大。随着辉度变得更高,存在产生取决于期望辉度的与理想栅极电压的更大差异的问题,从而导致灰度-辉度特性(γ)偏差。

68.为了抑制该辉度偏差,如图17所示,第三实施方式具有其中晶体管wstr的位置相对于用于每个子像素的驱动晶体管drvtr左右反转的布局。左右反转意味着多个子像素沿着第一方向布置,子像素之一的晶体管wstr存在于驱动晶体管drvtr的右侧,并且另一子像素的晶体管wstr存在于驱动晶体管drvtr的左侧。图17示出了在三个rgb子像素被设置为一个像素的情况下的两个像素(r1、b1、g1、r2、b2、g2)的布局。

69.从该布局中可以看出,可以使从相邻像素的阳极到自身像素的驱动晶体管drvtr的栅极drvg的距离更大,并且可以减小寄生电容器。另一方面,在子像素阵列的单元数量是奇数的情况下,对于相同颜色的子像素之间(r1和r2之间、b1和b2之间、g1和g2之间)的每个像素,左右位置切换,因此,寄生电容器的影响在相同颜色的子像素之间改变,并且出现可能在显示图像中产生条纹(竖直条纹)的可能性。

70.为了解决这种问题,第三实施方式的另一实例具有以下布局:三个子像素rgb中的一种颜色的子像素相对于其他两种颜色的子像素左右反转,使得还可抑制条纹(竖直条纹)的产生。左右反转的颜色是具有高可见性的颜色(例如,绿色g)。具体地,与图17中的布局相比,通过采用将具有高可见性的两种颜色(绿色和蓝色)中的一种颜色的子像素左右反转的布局,可减轻寄生电容器的影响,并且可抑制条纹的产生。图18示出了第三实施方式的另一实例的布局。图18示出了在三个rgb子像素被设置为一个像素的情况下的两个像素(r1、b1、g1、r2、b2、g2)的布局。

71.子像素r1、r2、b1和b2具有其中晶体管wstr位于阳极的左侧的布局,而子像素g1和g2具有其中晶体管wstr位于阳极的右侧的布局。如上所述,采用其中g(绿色)子像素的晶体管wstr的位置从其他r(红色)和b(蓝色)子像素的晶体管wstr的位置左右反转(左右切换)的布局。

72.以这种方式,因为子像素b1的晶体管wstr的沟道存在于子像素g1的晶体管wstr的漏极wsd(驱动晶体管drvtr的栅极drvg)与相邻子像素b1的阳极之间,所以可以减小寄生电容器。此外,因为子像素g1的晶体管wstr的沟道存在于子像素b1的晶体管wstr的漏极wsd(驱动晶体管drvtr的栅极drvg)与相邻子像素g1的阳极之间,所以可以减小寄生电容器。此外,由于晶体管ws的左和右位置在绿色、蓝色和红色的各个颜色的子像素中不改变,因此可以抑制寄生电容器的影响的改变和显示图像中条纹的产生。注意,第三实施方式不限于其

中三种颜色的子像素被设置为一个像素的配置,并且可应用于一个像素由四个或更多个子像素配置的情况。

73.接下来,将描述应用了根据实施方式等电光装置或应用实例的电子装置。电光装置适合于像素尺寸小并且执行高清晰显示的应用。因此,作为电子设备,电光设备可被应用于显示设备,诸如头戴式显示器、智能眼镜、智能电话、或数码相机的电子取景器。

74.虽然以上具体描述了本技术的实施方式,但是本技术不限于上述实施方式,并且可以基于本技术的技术构思进行各种修改。例如,如下所述的各种修改是可能的。另外,能够适当地组合后述的变形例的任意选择的一个以上的方式。此外,在不背离本技术的主旨的情况下,上述实施方式的配置、方法、步骤、形状、材料、数值等可彼此组合。

75.例如,像素电路可具有图3中所示的配置之外的配置。如果像素电路包括驱动晶体管、第一晶体管wstr、发光元件以及保持(写入)电容器就足够了。例如,诸如显示装置的垂直方向上的扫描线的数量的数值是实例,并且可以是另一数量的扫描线。此外,像素电路不一定包括p沟道晶体管,而是可以包括n沟道晶体管。

76.应注意,本技术还可具有以下配置。

77.(1)

78.一种显示装置,包括多条扫描线、多条数据线和像素单元,所述像素单元中由所述扫描线和所述数据线指定像素,

79.所述显示装置包括:

80.发光元件,设置在所述像素单元的每个像素电路中;以及

81.驱动晶体管,向所述发光元件提供驱动信号;

82.其中,显示装置具有在发光元件的阳极与驱动晶体管的控制端子之间具有大距离的布局。

83.(2)

84.根据(1)所述的显示装置,

85.其中,发光元件的阳极与驱动晶体管的源极连接,发光元件的阴极与预定的电源连接;

86.提供具有与信号线连接的第一端子和与驱动晶体管的控制端子连接的第二端子的第一晶体管;以及

87.通过第一晶体管将信号写入驱动晶体管并且基于该信号驱动发光元件。

88.(3)

89.根据(2)所述的显示装置,具有其中具有恒定电位的部分形成在第一晶体管的第二端子与阳极之间的布局。

90.(4)

91.根据(2)所述的显示装置,具有其中第一晶体管的第二端子与阳极之间的第二距离大于第一晶体管的第一端子与阳极之间的第一距离的布局。

92.(5)

93.根据(4)所述的显示装置,其中,根据第一晶体管的第一端子和第二端子的位置与阳极的位置之间的关系形成布局。

94.(6)

95.根据(5)所述的显示装置,其中,所述第一晶体管的位置相对于所述阳极的延伸方向上下或左右反转。

96.(7)

97.根据(2)所述的显示装置,

98.其中,像素电路的一个单元具有n个子像素;以及

99.所述n个子像素中的一个子像素的第一晶体管的位置与其他(n-1)个子像素的第一晶体管的位置不同。

100.(8)

101.根据(2)所述的显示装置,

102.其中,像素电路的一个单元具有n个子像素;以及

103.第一晶体管从1到(n-1)个子像素的位置被反转。

104.(9)

105.根据(8)所述的显示装置,其中,n个子像素中的一个特定子像素的第一晶体管的位置被反转。

106.(10)

107.根据(9)所述的显示装置,其中,所述一个特定子像素是绿色子像素。

108.附图标记列表

109.1有机el显示装置

110.2垂直扫描电路

111.3水平扫描电路

112.4像素单元

113.8数据线

114.drvtr驱动晶体管

115.oled作为发光元件的有机el

116.drvg驱动晶体管的栅极

117.wsd晶体管ws的漏极

118.wss晶体管ws的源极。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1