显示面板、像素电路、发光驱动器、行驱动电路及方法与流程

1.本技术涉及显示技术领域,尤其涉及一种显示面板、像素电路、发光驱动器、行驱动电路及方法。

背景技术:

2.随着显示技术的发展,越来越多的电子设备应运而生,如平板电脑、手机、电子阅读器、遥控器、个人数字助理、车载设备、电视机等已经成为人们日常惯用的显示工具。

3.微型发光二极管(micro light-emitting diode,micro led)因其体积小、耗电量小、产品寿命长等优点有望成为下一代主流显示技术。

4.现有的电子设备主要包括显示面板,显示面板包括多个亚像素单元,每个亚像素单元中包括micro led和像素电路。其中,像素电路用于为对应的亚像素单元中的micro led提供驱动电流,以使得micro led发光,进而实现显示。

5.研究发现,显示面板在显示过程中一帧画面主要包括驱动阶段和发光阶段,现有的显示面板在显示过程中驱动阶段所占时间较长,使得显示面板的发光阶段在一帧中所占时间较少,导致无法发挥出micro led的高亮度优势且对增大对灰阶精确控制的难度。

技术实现要素:

6.本技术实施例提供一种显示面板、像素电路、发光驱动器、行驱动电路及方法,用于解决显示面板的发光阶段在一帧中所占时间较少的问题。

7.为达到上述目的,本实施例采用如下技术方案:

8.第一方面,提供一种显示面板,包括多个像素电路;像素电路包括数据写入子电路;数据写入子电路与栅极扫描信号端、数据信号端、斜波扫描信号端以及第一节点相耦接,用于在栅极扫描信号端的控制下,将数据信号端的信号和斜波扫描信号端的信号择一传输至第一节点;其中,与同一栅极扫描信号端相耦接的像素电路位于同一行,位于不同行的像素电路与不同斜波扫描信号端相耦接。

9.本技术提供的显示面板,通过改变显示面板的内部结构,将斜波扫描信号端设置为多个,位于不同行的像素电路与不同斜波扫描信号端相耦接,使得显示面板中的斜波扫描信号端接收的斜波信号也类似于栅极扫描信号端的栅极信号,变成移位式斜波信号。可以很大程度的延长显示面板中发光元件的发光时长。通过延长发光元件的发光时长,可以有效提升显示面板的显示亮度,从而使得本示例提供的显示面板可以适用于各种屏幕尺寸的电子设备,解决了以micro led作为发光元件的显示面板无法应用于户外屏幕、电视等大尺寸屏幕的问题。此外,通过延长发光元件的发光时长,使得显示面板的可控灰阶数变多(发光时长短,有些灰阶控制实现不了),从而使得显示面板具有更高的色彩饱和度。其次,由于每行发光元件的发光时长不受其他行像素电路的影响,也就是说,每行发光元件的发光时长不受显示面板的像素分辨率的影响。因此,可以根据需要提高显示面板的像素分辨率。另外,本示例中斜波扫描信号端只需向一行像素电路提供斜波信号,与示例一中的斜波

扫描信号端需向整个面板中的像素电路提供斜波信号相比,明显可以降低斜波信号的负载,可有效解决斜波信号负载过大带来的显示问题。

10.可选的,像素电路还包括控制子电路;控制子电路与栅极扫描信号端、控制信号端、第一电压端、第二电压端以及第一节点相耦接,用于在栅极扫描信号端、控制信号端和第一节点的控制下,将第一电压端的信号和第二电压端的信号择一输出。一种新的像素电路结构,可以实现显示面板中的多行像素电路逐行接收移位式斜波信号。

11.可选的,显示面板还包括多个发光元件;像素电路还包括驱动子电路;驱动子电路与发光元件、第一电压端、第一信号端以及控制子电路相耦接,用于在控制子电路和第一信号端的控制下,根据第一电压端的信号生成驱动信号,驱动发光元件发光。

12.可选的,显示面板还包括发光驱动电路,发光驱动电路包括多个发光驱动器,发光驱动器用于输出斜波信号;发光驱动器的第一输出端与斜波扫描信号端相耦接。发光驱动器可以和移位寄存器同步形成,无需增加显示面板的工艺步骤和工艺成本,但是可以节省ddic内部的斜波信号产生模块,可以节省ddic的成本。

13.可选的,发光驱动器包括输出控制子电路、第一输出子电路以及存储子电路;输出控制子电路与第一输入端、第二输入端、第一时钟信号端、第三电压端以及第二节点相耦接,用于在第一输入端的控制下将第一时钟信号端的信号传输至第二节点,在第二输入端的控制下将第三电压端的信号传输至第二节点;第一输出子电路与第二节点、第二输入端、第四电压端、第五电压端、第二信号端以及第一输出端相耦接,用于在第二节点的控制下,将第四电压端的信号传输至第一输出端,在第二输入端和第二信号端的控制下将第五电压端的信号传输至第一输出端;存储子电路与第六电压端和第一输出端相耦接,用于根据第六电压端的信号和第一输出端的信号,存储第一输出端的信号。

14.可选的,显示面板还包括栅极驱动电路,栅极驱动电路包括多级级联的移位寄存器;移位寄存器用于输出栅极信号,移位寄存器的第二输出端与栅极扫描信号端相耦接。

15.可选的,移位寄存器包括上拉节点、下拉节点以及第二输出子电路;第二输出子电路与上拉节点、下拉节点、第一时钟信号端、第三电压端以及第二输出端相耦接,用于在上拉节点的控制下将第一时钟信号端的信号传输至第二输出端,在下拉节点的控制下将第三电压端的信号传输至第二输出端。

16.可选的,移位寄存器还包括第一输入子电路、第二输入子电路、第一下拉控制子电路、第二下拉控制子电路以及漏电保护子电路;第一输入子电路与第二时钟信号端、第三输入端以及上拉节点相耦接,用于在第二时钟信号端的控制下,将第三输入端的信号传输至上拉节点;第二输入子电路与第四输入端、第三电压端以及上拉节点相耦接,用于在第四输入端的控制下,将第三电压端的信号传输至上拉节点;第一下拉控制子电路与第二时钟信号端和下拉节点相耦接,用于在第二时钟信号端的控制下,将第二时钟信号端的信号传输至下拉节点;第二下拉控制子电路与上拉节点、第三电压端以及下拉节点相耦接,用于在上拉节点的控制下,将第三电压端的信号传输至下拉节点;漏电保护子电路与第一输入子电路、第一时钟信号端以及第二输出端相耦接,用于降低上拉节点的漏电流。

17.可选的,第一级移位寄存器的第三输入端与起始信号端相耦接;除第一级移位寄存器外,其他级移位寄存器的第三输入端与上一级移位寄存器的第二输出端相耦接;除最后一级移位寄存器外,其他级移位寄存器的第四输入端与下一级移位寄存器的第二输出端

相耦接;最后一级移位寄存器的第四输入端与起始信号端相连接或者复位信号端相耦接。

18.可选的,上拉节点与发光驱动器的第一输入端相耦接,下拉节点与发光驱动器的第二输入端相耦接。本示例中通过将移位寄存器的上拉节点与发光驱动器的第一输入端相耦接,将移位寄存器的下拉节点与发光驱动器的第二输入端相耦接。即,斜波信号产生电路中的部分电路(向第一输入端和第二输入端提供信号的那部分电路)与移位寄存器中的部分电路共用。这样可以很大程度的简化斜波信号产生电路的结构,减少斜波信号产生电路对非显示区的占用率,有利于电子设备窄边框的实现。

19.可选的,数据写入子电路包括第一晶体管和第一电容;第一晶体管的栅极与栅极扫描信号端相耦接,第一晶体管的第一极与数据信号端相耦接,第一晶体管的第二极与第一节点相耦接;第一电容的一端与第一节点相耦接,第一电容的另一端与斜波扫描信号端相耦接。

20.可选的,控制子电路包括第二晶体管、第三晶体管以及第四晶体管;第二晶体管的栅极与栅极扫描信号端相耦接,第二晶体管的第一极与第二电压端相耦接,第二晶体管的第二极与第三节点相耦接;第三晶体管的栅极与第一节点相耦接,第三晶体管的第一极与第一电压端相耦接,第三晶体管的第二极与第三节点相耦接;第四晶体管的栅极与控制信号端相耦接,第四晶体管的第一极与第三节点相耦接,第四晶体管的第二极与驱动子电路相耦接。

21.可选的,驱动子电路包括第五晶体管和第六晶体管;第五晶体管的栅极与控制子电路相耦接,第五晶体管的第一极与发光元件相耦接,第五晶体管的第二极与第六晶体管的第一极相耦接;第六晶体管的栅极与第一信号端相耦接,第六晶体管的第二极与第一电压端相耦接。

22.可选的,第五晶体管和第六晶体管均为n型晶体管,第二电压端相对第一电压端为高电平电源信号端。

23.可选的,第五晶体管和第六晶体管均为p型晶体管,第一电压端相对第二电压端为高电平电源信号端。

24.可选的,输出控制子电路包括第七晶体管和第八晶体管;第七晶体管的栅极与第一输入端相耦接,第七晶体管的第一极与第一时钟信号端相耦接,第七晶体管的第二极与第二节点相耦接;第八晶体管的栅极与第二输入端相耦接,第八晶体管的第一极与第三电压端相耦接,第八晶体管的第二极与第二节点相耦接。

25.可选的,第一输出子电路包括第九晶体管、第十晶体管以及第十一晶体管;第九晶体管的栅极与第二节点相耦接,第九晶体管的第一极与第四电压端相耦接,第九晶体管的第二极与第一输出端相耦接;第十晶体管的栅极与第二信号端相耦接,第十晶体管的第一极与第五电压端相耦接,第十晶体管的第二极与第十一晶体管的第一极相耦接;第十一晶体管的栅极与第二输入端相耦接,第十一晶体管的第二极与第二输出端相耦接。

26.可选的,存储子电路包括第二电容;第二电容的一端与第六电压端相耦接,第二电容的另一端与第一输出端相耦接。

27.可选的,第一输入子电路包括第十二晶体管和第十三晶体管;第十二晶体管的栅极与第二时钟信号端相耦接,第十二晶体管的第一极与第三输入端相耦接,第十二晶体管的第二极与第十三晶体管的第一极相耦接;第十三晶体管的栅极与第二时钟信号端相耦

接,第十三晶体管的第二极与上拉节点相耦接。

28.可选的,第二输入子电路包括第十四晶体管和第十五晶体管;第十四晶体管的栅极与第四输入端相耦接,第十四晶体管的第一极与第三电压端相耦接,第十四晶体管的第二极与第十五晶体管的第一极相耦接;第十五晶体管的栅极与第四输入端相耦接,第十五晶体管的第二极与上拉节点相耦接。

29.可选的,第一下拉控制子电路包括第十六晶体管;第十六晶体管的栅极与第二时钟信号端相耦接,第十六晶体管的第一极与第二时钟信号端相耦接,第十六晶体管的第二极与下拉节点相耦接。

30.可选的,第二下拉控制子电路包括第十七晶体管和第十八晶体管;第十七晶体管的栅极与第三电压端相耦接,第十七晶体管的第一极与第三电压端相耦接,第十七晶体管的第二极与第十八晶体管的第一极相耦接;第十八晶体管的栅极与上拉节点相耦接,第十八晶体管的第二极与下拉节点相耦接。

31.可选的,漏电保护子电路包括第十九晶体管;第十九晶体管的栅极与第二输出端相耦接,第十九晶体管的第一极与第一时钟信号端相耦接,第十九晶体管的第二极与第十三晶体管的第一极相耦接。

32.可选的,第二输出子电路包括第二十晶体管、第二十一晶体管以及第三电容;第二十晶体管的栅极与上拉节点相耦接,第二十晶体管的第一极与第一时钟信号端相耦接,第二十晶体管的第二极与第二输出端相耦接;第二十一晶体管的栅极与下拉节点相耦接,第二十一晶体管的第一极与第三电压端相耦接,第二十一晶体管的第二极与第二输出端相耦接;第三电容的一端与上拉节点相耦接,第三电容的另一端与第二输出端相耦接。

33.可选的,显示面板还包括显示驱动集成电路,显示驱动集成电路与栅极扫描信号端和斜波扫描信号端相耦接,用于向栅极扫描信号端提供栅极信号,向斜波扫描信号端提供斜波信号。

34.第二方面,提供一种显示面板的驱动方法,显示面板包括多个像素电路;像素电路包括数据写入子电路;数据写入子电路与栅极扫描信号端、数据信号端、斜波扫描信号端以及第一节点相耦接;与同一栅极扫描信号端相耦接的像素电路位于同一行,位于不同行的像素电路与不同斜波扫描信号端相耦接;显示面板的驱动方法,包括:向显示面板中的栅极扫描信号端分时传输有效脉冲;像素电路中的数据写入子电路在栅极扫描信号端的有效脉冲的控制下,将数据信号端的信号传输至第一节点;在向栅极扫描信号端传输有效脉冲后,向栅极扫描信号端传输非有效脉冲,并向与接收截止信号的数据写入子电路相耦接的斜波扫描信号端传输斜波信号;数据写入子电路在栅极扫描信号端的非有效脉冲的控制下,将斜波扫描信号端的斜波信号传输至第一节点。

35.第二方面提供的显示面板的驱动方法的有益效果与第一方面提供的显示面板的有益效果相同,此处不再赘述。

36.可选的,显示面板还包括栅极驱动电路,栅极驱动电路包括多级级联的移位寄存器,移位寄存器用于输出栅极信号;显示面板的驱动方法,还包括:栅极驱动电路中的移位寄存器向栅极扫描信号端传输有效脉冲和非有效脉冲。

37.可选的,显示面板还包括发光驱动电路,发光驱动电路包括多个发光驱动器,发光驱动器用于输出斜波信号;显示面板的驱动方法,还包括:发光驱动器向斜波扫描信号端传

输斜波信号。

38.可选的,显示面板还包括显示驱动集成电路;显示面板的驱动方法,还包括:显示驱动集成电路向斜波扫描信号端传输斜波信号。

39.第三方面,提供一种像素电路,包括:数据写入子电路、控制子电路以及驱动子电路;数据写入子电路与栅极扫描信号端、数据信号端、斜波扫描信号端以及第一节点相耦接,用于在栅极扫描信号端的控制下,将数据信号端的信号和斜波扫描信号端的信号择一传输至第一节点;控制子电路与栅极扫描信号端、控制信号端、第一电压端、第二电压端以及第一节点相耦接,用于在栅极扫描信号端、控制信号端和第一节点的控制下,将第一电压端的信号和第二电压端的信号择一输出;驱动子电路与发光元件、第一电压端、第一信号端以及控制子电路相耦接,用于在控制子电路和第一信号端的控制下,根据第一电压端的信号生成驱动信号,驱动发光元件发光。

40.可选的,数据写入子电路包括第一晶体管和第一电容;第一晶体管的栅极与栅极扫描信号端相耦接,第一晶体管的第一极与数据信号端相耦接,第一晶体管的第二极与第一节点相耦接;第一电容的一端与第一节点相耦接,第一电容的另一端与斜波扫描信号端相耦接。

41.可选的,控制子电路包括第二晶体管、第三晶体管以及第四晶体管;第二晶体管的栅极与栅极扫描信号端相耦接,第二晶体管的第一极与第二电压端相耦接,第二晶体管的第二极与第三节点相耦接;第三晶体管的栅极与第一节点相耦接,第三晶体管的第一极与第一电压端相耦接,第三晶体管的第二极与第三节点相耦接;第四晶体管的栅极与控制信号端相耦接,第四晶体管的第一极与第三节点相耦接,第四晶体管的第二极与驱动子电路相耦接。

42.可选的,驱动子电路包括第五晶体管和第六晶体管;第五晶体管的栅极与控制子电路相耦接,第五晶体管的第一极与发光元件相耦接,第五晶体管的第二极与第六晶体管的第一极相耦接;第六晶体管的栅极与第一信号端相耦接,第六晶体管的第二极与第一电压端相耦接。

43.第四方面,提供一种像素电路的驱动方法,像素电路包括数据写入子电路、控制子电路以及驱动子电路;数据写入子电路与栅极扫描信号端、数据信号端、斜波扫描信号端以及第一节点相耦接;控制子电路与栅极扫描信号端、控制信号端、第一电压端、第二电压端以及第一节点相耦接;驱动子电路与发光元件、第一电压端、第一信号端以及控制子电路相耦接;像素电路的驱动方法,包括:数据写入子电路在栅极扫描信号端的控制下,将数据信号端的信号和斜波扫描信号端的信号择一传输至第一节点;控制子电路在栅极扫描信号端、控制信号端和第一节点的控制下,将第一电压端的信号和第二电压端的信号择一输出;驱动子电路在控制子电路和第一信号端的控制下,根据第一电压端的信号生成驱动信号,驱动发光元件发光。

44.第五方面,提供一种发光驱动器,包括:输出控制子电路、第一输出子电路以及存储子电路;输出控制子电路与第一输入端、第二输入端、第一时钟信号端、第三电压端以及第二节点相耦接,用于在第一输入端的控制下将第一时钟信号端的信号传输至第二节点,在第二输入端的控制下将第三电压端的信号传输至第二节点;第一输出子电路与第二节点、第二输入端、第四电压端、第五电压端、第二信号端以及第一输出端相耦接,用于在第二

节点的控制下,将第四电压端的信号传输至第一输出端,在第二输入端和第二信号端的控制下将第五电压端的信号传输至第一输出端;存储子电路与第六电压端和第一输出端相耦接,用于根据第六电压端的信号和第一输出端的信号,存储第一输出端的信号。

45.可选的,输出控制子电路包括第七晶体管和第八晶体管;第七晶体管的栅极与第一输入端相耦接,第七晶体管的第一极与第一时钟信号端相耦接,第七晶体管的第二极与第二节点相耦接;第八晶体管的栅极与第二输入端相耦接,第八晶体管的第一极与第三电压端相耦接,第八晶体管的第二极与第二节点相耦接。

46.可选的,第一输出子电路包括第九晶体管、第十晶体管以及第十一晶体管;第九晶体管的栅极与第二节点相耦接,第九晶体管的第一极与第四电压端相耦接,第九晶体管的第二极与第一输出端相耦接;第十晶体管的栅极与第二信号端相耦接,第十晶体管的第一极与第五电压端相耦接,第十晶体管的第二极与第十一晶体管的第一极相耦接;第十一晶体管的栅极与第二输入端相耦接,第十一晶体管的第二极与第二输出端相耦接。

47.可选的,存储子电路包括第二电容;第二电容的一端与第六电压端相耦接,第二电容的另一端与第一输出端相耦接。

48.第六方面,提供一种发光驱动器的驱动方法,发光驱动器包括输出控制子电路、第一输出子电路以及存储子电路;输出控制子电路与第一输入端、第二输入端、第一时钟信号端、第三电压端以及第二节点相耦接;第一输出子电路与第二节点、第二输入端、第四电压端、第五电压端、第二信号端以及第一输出端相耦接;存储子电路与第六电压端和第一输出端相耦接;发光驱动器的驱动方法,包括:输出控制子电路在第一输入端的控制下将第一时钟信号端的信号传输至第二节点,在第二输入端的控制下将第三电压端的信号传输至第二节点;

49.第一输出子电路在第二节点的控制下,将第四电压端的信号传输至第一输出端,在第二输入端和第二信号端的控制下将第五电压端的信号传输至第一输出端;存储子电路根据第六电压端的信号和第一输出端的信号,存储第一输出端的信号。

50.第七方面,提供一种行驱动电路,包括:多个第五方面的发光驱动器。

51.可选的,行驱动电路还包括多个级联的移位寄存器;移位寄存器包括上拉节点、下拉节点以及第二输出子电路;第二输出子电路与上拉节点、下拉节点、第一时钟信号端、第三电压端以及第二输出端相耦接;第二输出子电路在上拉节点的控制下将第一时钟信号端的信号传输至第二输出端,在下拉节点的控制下将第三电压端的信号传输至第二输出端;发光驱动器的第一输入端与上拉节点相耦接,发光驱动器的第二输入端与下拉节点相耦接。

52.通过将移位寄存器的上拉节点与发光驱动器的第一输入端相耦接,将移位寄存器的下拉节点与发光驱动器的第二输入端相耦接。即,斜波信号产生电路中的部分电路(向第一输入端和第二输入端提供信号的那部分电路)与移位寄存器中的部分电路共用。这样可以很大程度的简化斜波信号产生电路的结构,减少斜波信号产生电路对非显示区的占用率,有利于电子设备窄边框的实现。

53.第八方面,提供一种行驱动电路的驱动方法,行驱动电路包括多个发光驱动器和多个级联的移位寄存器;发光驱动器包括输出控制子电路、第一输出子电路以及存储子电路;输出控制子电路与第一输入端、第二输入端、第一时钟信号端、第三电压端以及第二节

点相耦接;第一输出子电路与第二节点、第二输入端、第四电压端、第五电压端、第二信号端以及第一输出端相耦接;存储子电路与第六电压端和第一输出端相耦接;移位寄存器包括上拉节点、下拉节点以及第二输出子电路;第二输出子电路与上拉节点、下拉节点、第一时钟信号端、第三电压端以及第二输出端相耦接;第一输入端与上拉节点相耦接,第二输入端与下拉节点相耦接;行驱动电路的驱动方法,包括:上拉节点接收有效脉冲,第二输出子电路在上拉节点的控制下将第一时钟信号端的信号传输至第二输出端,输出控制子电路在上拉节点的控制下将第一时钟信号端的信号传输至第二节点;第一输出子电路在第二节点的控制下,将第四电压端的信号传输至第一输出端;存储子电路根据第六电压端的信号和第一输出端的信号,存储第一输出端的信号;下拉节点接收有效脉冲,第二输出子电路在下拉节点的控制下将第三电压端的信号传输至第二输出端,输出控制子电路在下拉节点的控制下将第三电压端的信号传输至第二节点;第一输出子电路在第二输入端和第二信号端的控制下将第五电压端的信号传输至第一输出端;存储子电路根据第六电压端的信号和第一输出端的信号,存储第一输出端的信号。

54.第九方面,提供一种电子设备,包括壳体和第一方面任一项的显示面板,显示面板放置在壳体内。

55.第九方面提供的电子设备包括第一方面提供的显示面板,其有益效果与第一方面的显示面板的有益效果相同,此处不再赘述。

附图说明

56.图1为本技术实施例提供的一种电子设备的框架示意图;

57.图2a为本技术实施例提供的一种显示面板的俯视示意图;

58.图2b为本技术实施例提供的一种像素电路的结构示意图;

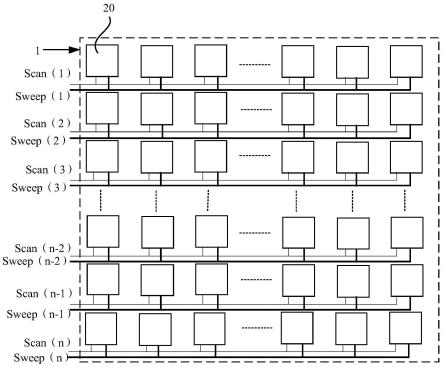

59.图2c为本技术实施例提供的一种显示面板的像素电路与斜波扫描信号端的连接关系示意图;

60.图2d为本技术实施例提供的一种图2c所示的显示面板的驱动时序图;

61.图3a为本技术实施例提供的另一种显示面板的俯视示意图;

62.图3b为本技术实施例提供的另一种显示面板的像素电路与斜波扫描信号端的连接关系示意图;

63.图4为本技术实施例提供的另一种像素电路的结构示意图;

64.图5a为本技术实施例提供的一种位于两行的两个像素电路的示意图;

65.图5b为图5a所示的两行像素电路的驱动时序图;

66.图5c-图5e为本技术实施例提供的图5a所示的两行像素电路的驱动过程示意图;

67.图6a为本技术实施例提供的另一种位于两行的两个像素电路的示意图;

68.图6b为图6a所示的两行像素电路的驱动时序图;

69.图7a为本技术实施例提供的一种发光驱动器的结构示意图;

70.图7b为图7a所示的发光驱动器的驱动过程示意图;

71.图7c为本技术实施例提供的一种图7a所示的发光驱动器的详细结构示意图;

72.图7d和图7e为本技术实施例提供的一种图7c所示的发光驱动器的驱动过程示意图;

reality,ar)终端设备、无人机等。家居式电子产品如为智能门锁、电视、遥控器、冰箱、充电家用小型电器(例如豆浆机、扫地机器人)等。车载式电子产品如为车载导航仪、车载dvd等。金融终端产品如为atm机、自助办理业务的终端等。

94.本技术实施例对上述电子设备的具体形式不做特殊限制,以下为了方便说明,是以电子设备为手机为例进行的说明。

95.如图1所示,上述电子设备01主要包括:前壳10、显示面板20、中框30以及后壳(也可以称为电池盖)40。

96.显示面板20具有能够看到显示画面的出光侧和与出光侧相对设置的背面。

97.前壳10位于显示面板20的出光侧,用于保护显示面板20。前壳10例如可以是前壳玻璃(cover glass,cg),该前壳玻璃可以具有一定的韧性。

98.中框30位于显示面板20和后壳40之间。中框30远离显示面板20的表面用于安装电池、主板、摄像头(camera)、天线等内部元件。

99.后壳40安装于中框30上,后壳40能够对上述电子设备01的内部元件进行保护。

100.随着显示技术的不断发展,有机发光二极管(organic light-emitting diode,oled)面板以其可柔性、厚度薄、功耗低等优点而受到广泛的应用。但是,oled面板目前存在一些无法满足需求的缺陷,如显示寿命低,烧屏问题一直无法解决、亮度低,无法应用在高亮度需求的领域(如户外显示)等。

101.在本技术的一些实施例中,上述显示面板10可以为oled显示面板。

102.而微型发光二极管(micro light-emitting diode,micro led)面板或者称为uled面板,因为其具有高亮度、高寿命、低功耗等优点,而受到广泛的关注。

103.在本技术的一些实施例中,上述显示面板10可以为micro led显示面板。

104.示例一

105.在本技术的一种可能的实施例中,关于显示面板10,如图2a所示,显示面板10包括有效显示区(active area,aa)1和位于该有效显示区1周边的非显示区2。

106.上述有效显示区1包括多个亚像素单元(sub pixel)20。为了方便说明,本技术中上述多个亚像素单元20是以矩阵形式排列为例进行的说明。此时,沿水平方向x排列成一排的亚像素单元20称为同一行亚像素单元,沿竖直方向y排列成一排的亚像素单元20称为同一列亚像素单元。水平方向x例如为显示面板10中栅线(gate line,gl)的延伸方向,竖直方向y例如为显示面板10中数据线(data line,dl)的延伸方向。

107.上述非显示区2包括栅极驱动电路40、多路开关(multiplexer,mux)、显示驱动集成电路(display driver integrated circuits,ddic)以及柔性电路板(flexible printed circuit,fpc)。

108.栅极驱动电路40主要为有效显示区1中的亚像素单元20的栅极扫描信号端scan提供逐行扫描的栅极信号,mux用于将有效显示区1中与亚像素单元20的数据信号端data相耦接的数据线与ddic电连接,实现亚像素单元20通过数据线接收ddic传输的数据信号。ddic用于接收电子设备中驱动系统端传输的信号并将信号按照特定的时序控制输送至显示面板10。fpc用于连接驱动系统与ddic。

109.关于亚像素单元20的结构,如图2b所示,以一个亚像素单元20为例,亚像素单元20包括像素电路21和发光元件22,像素电路21用于为对应的亚像素单元20中的发光元件22提

供驱动电流,以使得发光元件22发光,进而实现显示面板10显示。

110.示例的,像素电路21包括晶体管m1、晶体管m2、晶体管m3以及电容c。以像素电路21包括的晶体管为n型晶体管为例,对像素电路21中晶体管的连接关系进行示意说明。

111.晶体管m1的栅极扫描信号端scan相耦接,晶体管m1的第一极与数据信号端data相耦接,晶体管m1的第二极与节点o相耦接。

112.电容c的一端与斜波扫描信号端sweep相耦接,电容c的另一端与节点o相耦接。

113.晶体管m2的栅极与节点o相耦接,晶体管m2的第一极与发光元件22的阴极相耦接,晶体管m2的第二极与晶体管m3的第一极相耦接。

114.晶体管m3的栅极与第一信号端vba相耦接,晶体管m3的第二极与低电平电源信号端vss相耦接。

115.发光元件22的阳极与高电平电源信号端vss相耦接。

116.如图2c所示,位于同一行的亚像素单元20(实则为亚像素单元20中的像素电路21)与同一栅极扫描信号端scan相耦接,显示面板10中的所有亚像素单元20(实则为亚像素单元20中的像素电路21)与同一斜波扫描信号端sweep相耦接。

117.也就是说,显示面板10的有效显示区1包括多个亚像素单元20,每个亚像素单元20包括一个像素电路21。在像素电路21中,主要通过栅极扫描信号端scan和斜波扫描信号端sweep来控制电路的工作。栅极扫描信号端scan接收栅极驱动电路30的输出信号,栅极扫描信号端scan接收到的信号的特点:是后一行栅极扫描信号端scan接收到的信号的扫描信号脉冲,相比前一行栅极扫描信号端scan接收到的信号扫描信号脉冲时间上相差一个脉冲宽度,主要用来负责控制像素电路21中晶体管m1逐行导通,使得数据信号端data的数据信号可以逐行写入。斜波扫描信号端sweep主要由ddic提供,用来控制晶体管m2的打开与关闭。为了节省ddic的空间,所有亚像素单元20的斜波扫描信号端sweep会先进行短接,然后统一由ddic输出一个斜波信号供给各个亚像素单元20,即各亚像素单元20的斜波信号共用。

118.micro led由于其存在发光亮度随着电流的变化而变化,不同的电流驱动下容易存在色偏问题。因此,在本技术实施例中,采用脉冲宽度调制(pulsewidthmodulation,pwm)驱动技术,维持micro led发光电流不变,以改善色偏问题。

119.示例的,如图2d所示,像素电路20的驱动在一帧(frame)内主要包括驱动阶段p1和发光阶段p2。

120.在驱动阶段p1内,栅极扫描信号端scan的信号起主导作用,其工作原理为:

121.当第一栅极扫描信号端scan(1)的脉冲有效(高电平信号highvoltage)时,第一行的所有亚像素单元20中的晶体管m1打开,数据信号端data负责向节点o输送电压,完成第一行亚像素单元20的数据信号写入。

122.当第二栅极扫描信号端scan(2)的脉冲信号有效时,第一栅极扫描信号端scan(1)的脉冲无效(低电平信号low voltage)。因此第一行的亚像素单元20中晶体管m1关闭,节点o由于悬空(floating)电位可以维持住原先写入的数据信号。而此时第二行的亚像素单元20中晶体管m1打开,数据信号端data此时负责对第二行的亚像素单元20进行数据信号写入。

123.以此类推,数据信号端data通过当第n栅极扫描信号端scan(n)的脉冲信号有效时,第1栅极扫描信号端scan(1)~第n-1栅极扫描信号端scan(n-1)的脉冲信号无效,第n行

的亚像素单元20中晶体管m1打开,数据信号端data此时负责对第n行的亚像素单元20进行数据信号写入。

124.在该驱动阶段p1,通过控制第一信号端vba的写入电压,始终保证晶体管m3在该阶段处于关闭状态,即该阶段发光元件22不发光。

125.在发光阶段p2内,斜波扫描信号端sweep的信号起主导作用,其工作原理为:

126.第一信号端vba在整个发光阶段p2内接收有效脉冲(高电平信号),使得此时晶体管m3打开,发光元件22开始发光。

127.当斜波扫描信号端sweep的电压缓慢降低时,通过电容c的耦合,节点o的电压也开始缓慢降低,直至小于晶体管m2的导通电压,将晶体管m2关闭,发光元件22才进入不发光状态。

128.在上述结构中,由于斜波扫描信号端sweep对于每个亚像素单元20都是共用,因此每个亚像素单元20的发光时间段必须在相同的时间段内。即,在整帧的像素驱动中,驱动阶段p1主要是逐行对每行亚像素单元20进行数据写入,该阶段不发光。发光阶段p2主要对所有亚像素单元20同时控制发光,发光时间的长度依赖于驱动阶段p1写入的数据信号。

129.然而,这样一来,如图2d所示,在所有行亚像素单元20的栅极扫描信号端scan依次接收完有效脉冲信号后,所有行亚像素单元20的发光元件22才同时进入发光阶段p2,开始发光。发光阶段p2(发光元件22的发光时长)在一帧中的占比(发光阶段p2时长/一帧时长)受驱动阶段p1的影响较大,而在上述结构中,驱动阶段p1在一帧中的占比较大,发光阶段p2占比较小,发光元件22的发光时长较小,无法发挥出发光元件22的高亮度优势。因此,只能通过减少亚像素单元20的行数,来减少驱动阶段p1在一帧中的占比,从而增加发光元件22的发光时长,导致显示面板10只适用于较小尺寸和较小的分辨率的电子设备上。

130.另外,发光元件22的发光时长越短,每个灰阶对应的时间长度也就越短,要在较短时间内对灰阶进行精确控制的难度较大,导致显示效果较差。

131.再者,所有的亚像素单元20与同一斜波扫描信号端sweep相耦接,斜波扫描信号端sweep对应的负载很大,对斜波信号的驱动能力要求较高,导致对ddic的要求较高,成本较大。

132.示例二

133.示例二与示例一的不同之处在于,斜波扫描信号端sweep的数量和信号来源不同。

134.在本技术的另一种可能的实施例中,如图3a所示,显示面板10包括有效显示区1和位于该有效显示区1周边的非显示区2。

135.如图3b所示,上述有效显示区1包括多个亚像素单元20,位于同一行的亚像素单元20与同一斜波扫描信号端sweep相耦接,位于不同行的亚像素单元20与不同斜波扫描信号端sweep相耦接。其中,与同一栅极扫描信号端scan相耦接的亚像素单元20位于同一行。例如,沿水平方向x排列成一排的亚像素单元20称为同一行亚像素单元20。

136.上述非显示区2包括发光驱动电路30、栅极驱动电路40、多路开关(multiplexer,mux)、显示驱动集成电路(display driver integrated circuits,ddic)以及柔性电路板(flexible printed circuit,fpc)。

137.发光驱动电路30主要为有效显示区1中的亚像素单元20的斜波扫描信号端sweep提供逐行扫描的斜波信号,栅极驱动电路40主要为有效显示区1中的亚像素单元20的栅极

扫描信号端scan提供逐行扫描的栅极信号,mux用于将有效显示区1中与亚像素单元20的数据信号端data相耦接的数据线(data line,dl)与ddic电连接,实现亚像素单元20通过数据线接收ddic传输的数据信号。ddic用于接收电子设备中驱动系统端传输的信号并将信号按照特定的时序控制输送至显示面板10。fpc用于连接驱动系统与ddic。

138.关于显示面板10中亚像素单元20的结构,如图4所示,亚像素单元20包括像素电路21和发光元件22,像素电路21用于为对应的亚像素单元20中的发光元件22提供驱动电流,以使得发光元件22发光,进而实现显示面板10显示。

139.其中,像素电路21的结构可以与示例一中相同。

140.或者,本技术实施例还提供一种像素电路21,用于驱动发光元件22发光。

141.如图4所示,像素电路21包括数据写入子电路211、控制子电路212以及驱动子电路213。

142.数据写入子电路211与栅极扫描信号端scan、数据信号端data、斜波扫描信号端sweep以及第一节点a相耦接,用于在栅极扫描信号端scan的控制下,将数据信号端data的信号和斜波扫描信号端sweep的信号择一传输至第一节点a。

143.控制子电路212与栅极扫描信号端scan、控制信号端ctr、第一电压端v1、第二电压端v2以及第一节点a相耦接,用于在栅极扫描信号端scan、控制信号端ctr和第一节点a的控制下,将第一电压端v1的信号和第二电压端v2的信号择一输出。

144.其中,在一些实施例中,位于同一行的像素电路21与同一控制信号端ctr相耦接,以减少端口,简化线路布局。

145.驱动子电路213与发光元件22、第一电压端v1、第一信号端vba以及控制子电路212相耦接,用于在控制子电路212和第一信号端vba的控制下,根据第一电压端v1的信号生成驱动信号,驱动发光元件22发光。

146.其中,在一些实施例中,多个像素电路21与同一第一信号端vba相耦接。或者,显示面板中的所有像素电路21与同一第一信号端vba相耦接。这样一来,可以减少端口,简化线路布局。

147.在像素电路21驱动的过程中,数据写入子电路211在栅极扫描信号端scan的控制下,将数据信号端data的信号和斜波扫描信号端sweep的信号择一传输至第一节点a。控制子电路212在栅极扫描信号端scan、控制信号端ctr和第一节点a的控制下,将第一电压端v1的信号和第二电压端v2的信号择一输出。驱动子电路213在控制子电路212和第一信号端vba的控制下,根据第一电压端v1的信号生成驱动信号,驱动发光元件22发光。

148.示例的,数据写入子电路211在栅极扫描信号端scan的有效脉冲的控制下,将数据信号端data的信号传输至第一节点a。控制子电路212在栅极扫描信号端scan的有效脉冲、控制信号端ctr的有效脉冲和第一节点a的非有效脉冲的控制下,将第二电压端v2的信号传输至驱动子电路213。驱动子电路213在控制子电路212的有效脉冲和第一信号端vba的有效脉冲的控制下,与发光元件22导通,根据第一电压端v1的信号和第二电压端v2的信号生成驱动信号,驱动发光元件22发光。

149.数据写入子电路211在栅极扫描信号端scan的非有效脉冲的控制下,将斜波扫描信号端sweep的信号输至第一节点a。第一节点a的斜波信号从非有效脉冲逐渐变为有效脉冲。第一节点a的斜波信号变为有效脉冲后,控制子电路212在栅极扫描信号端scan的非有

效脉冲、控制信号端ctr的有效脉冲和第一节点a的有效脉冲的控制下,将第一电压端v1的信号传输至驱动子电路213。驱动子电路213在控制子电路212的非有效脉冲的控制下,与发光元件22断开,发光元件22停止发光。

150.关于像素电路21的详细结构,示例的,如图5a所示,数据写入子电路211包括第一晶体管t1和第一电容c1。

151.第一晶体管t1的栅极与栅极扫描信号端scan相耦接,第一晶体管t1的第一极与数据信号端data相耦接,第一晶体管t1的第二极与第一节点a相耦接。

152.第一电容c1的一端与第一节点a相耦接,第一电容c1的另一端与斜波扫描信号端sweep相耦接。

153.控制子电路212包括第二晶体管t2、第三晶体管t3以及第四晶体管t4。

154.第二晶体管t2的栅极与栅极扫描信号端scan相耦接,第二晶体管t2的第一极与第二电压端v2相耦接,第二晶体管t2的第二极与第三节点b相耦接。

155.第三晶体管t3的栅极与第一节点a相耦接,第三晶体管t3的第一极与第一电压端v1相耦接,第三晶体管t3的第二极与第三节点b相耦接。

156.第四晶体管t4的栅极与控制信号端ctr相耦接,第四晶体管t4的第一极与第三节点b相耦接,第四晶体管t4的第二极与驱动子电路213相耦接。

157.驱动子电路213包括第五晶体管t5和第六晶体管t6。

158.第五晶体管t5的栅极与控制子电路212相耦接,第五晶体管t5的第一极与发光元件22相耦接,第五晶体管t5的第二极与第六晶体管t6的第一极相耦接。

159.第六晶体管t6的栅极与第一信号端vba相耦接,第六晶体管t6的第二极与第一电压端v1相耦接。

160.需要说明的是,上述像素电路21中的晶体管可以为n型晶体管,也可以为p型晶体管。可以为增强型晶体管,也可以为耗尽型晶体管。上述晶体管的第一极可以为源极,第二极可以为漏极,或者上述晶体管的第一极可以为漏极,第二极为源极,本发明对此不作限定。

161.在一种可能的实施例中,如图5a所示,上述像素电路21中的第一晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5以及第六晶体管t6均为n型晶体管,第二电压端v2相对第一电压端v1为高电平电源信号端,像素电路21中驱动子电路213与发光元件22的阴极相耦接。示例的,第一电压端v1为低电平电源信号端vss,第二电压端v2为高电平电源信号端vdd。

162.如图5b所示,像素电路21的驱动过程包括:

163.驱动阶段p1:

164.第n栅极扫描信号端scan(n)接收高电平信号,第n控制信号端ctr(n)接收低电平信号,第n斜波扫描信号端sweep(n)接收固定电平(例如参考电压ref)。如图5c所示,此时,第一晶体管t1和第二晶体管t2在第n栅极扫描信号端scan(n)的高电平信号的控制下导通,数据信号端data的数据信号经第一晶体管t1传输至第一节点a,控制第三晶体管t3截止。第二电压端v2的高电平电源信号经第二晶体管t2传输至第三节点b。第四晶体管t4在第n控制信号端ctr(n)的低电平信号的控制下截止,第五晶体管t5截止。第一信号端vba接收高电平信号,即使第六晶体管t6在第一信号端vba的高电平信号的控制下导通,发光元件22中也没

有驱动电流流过。

165.也就是说,如图5c所示,在驱动阶段p1,第n行亚像素单元20中的像素电路21,第一晶体管t1、第二晶体管t2以及第六晶体管t6导通,第三晶体管t3、第四晶体管t4以及第五晶体管t5截止。在第n行亚像素单元20的驱动阶段p1,第n+1行亚像素单元20中的像素电路21,第六晶体管t6'导通,第一晶体管t1'、第二晶体管t2'、第三晶体管t3'、第四晶体管t4'以及第五晶体管t5'截止。

166.发光阶段p2:

167.第n栅极扫描信号端scan(n)接收低电平信号,第n控制信号端ctr(n)接收高电平信号,第n斜波扫描信号端sweep(n)接收呈上升趋势的斜波信号。如图5d所示,第一晶体管t1和第二晶体管t2在第n栅极扫描信号端scan(n)的低电平信号的控制下截止。第一节点a保持数据电压端的信号,第三晶体管t3在第一节点a的控制下截止。第三节点b因处于悬空状态而依旧保持高电平,第四晶体管t4在第n控制信号端ctr(n)的高电平信号的控制下导通,第三节点b的高电平信号传输至第五晶体管t5的栅极,控制第五晶体管t5导通。第一信号端vba接收高电平信号,第六晶体管t6在第一信号端vba的高电平信号的控制下导通,发光元件22中产生驱动电流i,驱动发光元件22发光。

168.也就是说,如图5d所示,在发光阶段p2,第n行亚像素单元20中的像素电路21,第一晶体管t1、第二晶体管t2、第三晶体管t3截止,第四晶体管t4、第五晶体管t5以及第六晶体管t6导通。

169.在第n栅极扫描信号端scan(n)接收低电平信号的同时,第n+1栅极扫描信号端scan(n+1)接收高电平信号,处于驱动阶段p1。

170.也就是说,如图5d所示,在第n行亚像素单元20的发光阶段p2,第n+1行亚像素单元20中的像素电路21,第一晶体管t1'、第二晶体管t2'以及第六晶体管t6'导通,第三晶体管t3'、第四晶体管t4'以及第五晶体管t5'截止。

171.在发光元件22发光期间,第一节点a通过第一电容c1受到第n斜波扫描信号端sweep(n)的斜波信号的耦合,使得第一节点a的电压逐渐增加,直至第一节点a的电压与第一电压端v1的电压的差值(vgs)大于第三晶体管t3的阈值电压(vth)时,如图5e所示,第一节点a控制第三晶体管t3导通,第一电压端v1的低电平电源信号传输至第三节点b。第三节点b的低电平信号经第四晶体管t4传输至第五晶体管t5的栅极,控制第五晶体管t5截止,发光元件22停止发光。

172.也就是说,第一节点a的电压与第一电压端v1的电压的差值(vgs)大于第三晶体管t3的阈值电压(vth)时,如图5e所示,第n行亚像素单元20中的像素电路21,第三晶体管t3、第四晶体管t4以及第六晶体管t6导通,第一晶体管t1、第二晶体管t2以及第五晶体管t5截止。而此时,第n+1行亚像素单元20中的像素电路21,已经处于发光阶段p2,第一晶体管t1'、第二晶体管t2'以及第三晶体管t3'截止,第四晶体管t4'、第五晶体管t5'以及第六晶体管t6'导通。

173.通过上述描述可知,在第n行亚像素单元20处于发光阶段p2时,第n+1行亚像素单元20已经进入驱动阶段p1。第n行亚像素单元20的发光阶段p2的时长,不受其他行亚像素单元20的驱动阶段p1的时长所影响。

174.在另一种可能的实施例中,如图6a所示,上述像素电路21中的第一晶体管t1、第二

晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5以及第六晶体管t6均为p型晶体管,第一电压端v1相对第二电压端v2为高电平电源信号端,像素电路21中驱动子电路213与发光元件22的阳极相耦接。示例的,第一电压端v1为高电平电源信号端vdd,第二电压端v2为低电平电源信号端vss。

175.如图6b所示,像素电路21的驱动过程包括:

176.驱动阶段p1:

177.第n栅极扫描信号端scan(n)接收低电平信号,第n控制信号端ctr(n)接收高电平信号,第n斜波扫描信号端sweep(n)接收固定电平(例如ref)。此时,第一晶体管t1和第二晶体管t2在第n栅极扫描信号端scan(n)的低电平信号的控制下导通,数据信号端data的数据信号经第一晶体管t1传输至第一节点a,控制第三晶体管t3截止。第二电压端v2的低电平电源信号经第二晶体管t2传输至第三节点b。第四晶体管t4在第n控制信号端ctr(n)的高电平信号的控制下截止,第五晶体管t5截止。第一信号端vba接收低电平信号,即使第六晶体管t6在第一信号端vba的低电平信号的控制下导通,发光元件22中也没有驱动电流流过。

178.也就是说,在驱动阶段p1,第n行亚像素单元20中的像素电路21,第一晶体管t1、第二晶体管t2以及第六晶体管t6导通,第三晶体管t3、第四晶体管t4以及第五晶体管t5截止。在第n行亚像素单元20的驱动阶段p1,第n+1行亚像素单元20中的像素电路21,第六晶体管t6'导通,第一晶体管t1'、第二晶体管t2'、第三晶体管t3'、第四晶体管t4'以及第五晶体管t5'截止。

179.发光阶段p2:

180.第n栅极扫描信号端scan(n)接收高电平信号,第n控制信号端ctr(n)接收低电平信号,第n斜波扫描信号端sweep(n)接收呈下降趋势的斜波信号。第一晶体管t1和第二晶体管t2在第n栅极扫描信号端scan(n)的高电平信号的控制下截止。第一节点a保持数据电压端的信号,第三晶体管t3在第一节点a的控制下截止。第三节点b因处于悬空状态而依旧保持低电平,第四晶体管t4在第n控制信号端ctr(n)的低电平信号的控制下导通,第三节点b的低电平信号传输至第五晶体管t5的栅极,控制第五晶体管t5导通。第一信号端vba接收低电平信号,第六晶体管t6在第一信号端vba的低电平信号的控制下导通,发光元件22中产生驱动电流i,驱动发光元件22发光。

181.也就是说,在发光阶段p2,第n行亚像素单元20中的像素电路21,第一晶体管t1、第二晶体管t2、第三晶体管t3截止,第四晶体管t4、第五晶体管t5以及第六晶体管t6导通。

182.在第n栅极扫描信号端scan(n)接收低电平信号的同时,第n+1栅极扫描信号端scan(n+1)接收高电平信号,处于驱动阶段p1。

183.也就是说,在第n行亚像素单元20的发光阶段p2,第n+1行亚像素单元20中的像素电路21,第一晶体管t1'、第二晶体管t2'以及第六晶体管t6'导通,第三晶体管t3'、第四晶体管t4'以及第五晶体管t5'截止。

184.在发光元件22发光期间,第一节点a通过第一电容c1受到第n斜波扫描信号端sweep(n)的斜波信号的耦合,使得第一节点a的电压逐渐降低,直至第一节点a的电压与第一电压端v1的电压的差值(vgs)小于第三晶体管t3的阈值电压(vth)时,第一节点a控制第三晶体管t3导通,第一电压端v1的高电平电源信号传输至第三节点b。第三节点b的高电平信号经第四晶体管t4传输至第五晶体管t5的栅极,控制第五晶体管t5截止,发光元件22停

止发光。

185.也就是说,第一节点a的电压与第一电压端v1的电压的差值(vgs)小于第三晶体管t3的阈值电压(vth)时,第n行亚像素单元20中的像素电路21,第三晶体管t3、第四晶体管t4以及第六晶体管t6导通,第一晶体管t1、第二晶体管t2以及第五晶体管t5截止。而此时,第n+1行亚像素单元20中的像素电路21,已经处于发光阶段p2,第一晶体管t1'、第二晶体管t2'以及第三晶体管t3'截止,第四晶体管t4'、第五晶体管t5'以及第六晶体管t6'导通。

186.通过上述描述可知,在第n行亚像素单元20处于发光阶段p2时,第n+1行亚像素单元20已经进入驱动阶段p1。第n行亚像素单元20的发光阶段p2的时长,不受其他行亚像素单元20的驱动阶段p1的时长所影响。

187.基于此,本示例中提供的像素电路21,某一行亚像素单元20中的像素电路21是否进入发光阶段,与接收到的栅极扫描信号端scan和斜波扫描信号端sweep的信号有关,不受其它行亚像素单元20中的像素电路21的影响,无需等到所有行亚像素单元20中的像素电路21均执行完驱动阶段p1再进入发光阶段p2。因此,像素电路21可提供较长时间的驱动电流i,以驱动发光元件22长时间发光,大大提升了发光元件22的发光时长。

188.关于向上述像素电路21的斜波扫描信号端sweep提供逐行扫描的斜波信号的方式,本技术实施例还提供一种发光驱动电路30,用于向像素电路21的斜波扫描信号端sweep提供逐行扫描的斜波信号。

189.关于发光驱动电路30的结构,在一些实施例中,发光驱动电路30包括多个发光驱动器,发光驱动器用于输出斜波扫描信号。

190.其中,发光驱动电路30中的发光驱动器的第一输出端out1与斜波扫描信号端sweep相耦接,发光驱动器用于向斜波扫描信号端sweep提供斜波信号。

191.关于发光驱动器的结构,在一些实施例中,如图7a所示,发光驱动器31包括输出控制子电路311、第一输出子电路312以及存储子电路313。

192.输出控制子电路311与第一输入端in1、第二输入端in2、第一时钟信号端clk1、第三电压端v3以及第二节点d相耦接,用于在第一输入端in1的控制下将第一时钟信号端clk1的信号传输至第二节点d,在第二输入端in2的控制下将第三电压端v3的信号传输至第二节点d。

193.第一输出子电路312与第二节点d、第二输入端in2、第四电压端v4、第五电压端v5、第二信号端vre以及第一输出端out1相耦接,用于在第二节点d的控制下,将第四电压端v4的信号传输至第一输出端out1,在第二输入端in2和第二信号端vre的控制下将第五电压端v5的信号传输至第一输出端out1。

194.存储子电路313与第六电压端v6和第一输出端out1相耦接,用于根据第六电压端v6的信号和第一输出端out1的信号,存储第一输出端out1的信号。在发光驱动器31驱动过程中,输出控制子电路311在第一输入端in1的控制下将第一时钟信号端clk1的信号传输至第二节点d,在第二输入端in2的控制下将第三电压端v3的信号传输至第二节点d。第一输出子电路312在第二节点d的控制下,将第四电压端v4的信号传输至第一输出端out1,在第二输入端和第二信号端vre的控制下将第五电压端v5的信号传输至第一输出端out1。存储子电路313根据第六电压端v6的信号和第一输出端out1的信号,存储第一输出端out1的信号。

195.在一种可能的实施例中,如图7a所示,第四电压端v4为低电平信号端,例如为接地

端gnd或者低电平电源信号端vss。第五电压端v5为高电平信号端,例如为高电平电源信号端vdd。第三电压端v3和第六电压端v6为低电平信号端,例如为接地端gnd或者低电平电源信号端vss,第三电压端v3和第六电压端v6可以相耦接。

196.结合如图7b所示的时序图,示例的,输出控制子电路311在第一输入端in1的有效脉冲的控制下将第一时钟信号端clk1的时钟信号传输至第二节点d,第一输出子电路312在第二节点d的有效脉冲的控制下,将第四电压端v4的低电平信号传输至第一输出端out1。第六电压端v6的信号为低电平信号,存储子电路313存储第一输出端out1的低电平信号,相当于第四电压端v4的低电平信号对存储子电路313进行放电。

197.输出控制子电路311在第二输入端in2的有效脉冲的控制下将第三电压端v3的低电平信号传输至第二节点d,第一输出子电路312在第二输入端in2的有效脉冲和第二信号端vre的有效脉冲的控制下将第五电压端v5的高电平信号传输至第一输出端out1。第六电压端v6的信号为低电平信号,存储子电路313存储第一输出端out1的高电平信号,相当于第五电压端v5的高电平信号对存储子电路313进行充电。在充电过程中,第一输出端out1的信号逐渐上升,发光驱动器31输出呈上升趋势的斜波信号。关于发光驱动器31的结构,示例的,如图7c所示,输出控制子电路311包括第七晶体管t7和第八晶体管t8。

198.第七晶体管t7的栅极与第一输入端in1相耦接,第七晶体管t7的第一极与第一时钟信号端clk1相耦接,第七晶体管t7的第二极与第二节点d相耦接。

199.第八晶体管t8的栅极与第二输入端in2相耦接,第八晶体管t8的第一极与第三电压端v3相耦接,第八晶体管t8的第二极与第二节点d相耦接。

200.第一输出子电路312包括第九晶体管t9、第十晶体管t10以及第十一晶体管t11。

201.第九晶体管t9的栅极与第二节点d相耦接,第九晶体管t9的第一极与第四电压端v4相耦接,第九晶体管t9的第二极与第一输出端out1相耦接。

202.第十晶体管t10的栅极与第二信号端vre相耦接,第十晶体管t10的第一极与第五电压端v5相耦接,第十晶体管t10的第二极与第十一晶体管t11的第一极相耦接。

203.第十一晶体管t11的栅极与第二输入端in2相耦接,第十一晶体管t11的第二极与第二输出端out2相耦接。

204.存储子电路313包括第二电容c2。第二电容c2的一端与第六电压端v6相耦接,第二电容c2的另一端与第一输出端out1相耦接。

205.结合图7b所示的时序图,如图7c所示的发光驱动器31的驱动方法包括:

206.阶段一:

207.如图7b所示,第一输入端in1接收高电平信号,第二输入端in2接收低电平信号。如图7d所示,第七晶体管t7在第一输入端in1高电平信号的控制下导通,第一时钟信号端clk1的时钟信号经第七晶体管t7传输至第二节点d。第九晶体管t9在第二节点d高电平信号的控制下将导通,第四电压端v4的低电平信号经第九晶体管t9传输至第一输出端out1,第二电容c2存储第四电压端v4的低电平信号,相当于第二电容c2对第四电压端v4进行放电。第八晶体管t8和第十一晶体管t11在第二输入端in2低电平信号的控制下截止,虽然第十晶体管t10在第二信号端vre的低电平信号(小于vth+vdd的电位,vth为第十晶体管t10的阈值电压)的控制下导通,但第十一晶体管t11截止,第五电压端v5的高电平信号无法传输至第一输出端out1。因此,第一输出端out1的电位维持在第四电压端v4的低电平电位(例如gnd)。

208.也就是说,在阶段一,第七晶体管t7、第九晶体管t9以及第十晶体管t10导通,第八晶体管t8和第十一晶体管t11截止,第一输出端out1输出第四电压端v4的低电平信号。

209.阶段二:

210.如图7b所示,第一输入端in1接收低电平信号时,第二输入端in2接收高电平信号。如图7e所示,第七晶体管t7在第一输入端in1低电平信号的控制下截止,第八晶体管t8和第十一晶体管t11在第二输入端in2低电平信号的控制下导通。第三电压端v3的低电平信号经第八晶体管t8传输至第二节点d,第九晶体管t9在第二节点d低电平信号的控制下截止。第十晶体管t10在第二信号端vre的低电平信号(小于vth+vdd的电位,vth为第十晶体管t10的阈值电压)的控制下导通,第五电压端v5的高电平信号经第十晶体管t10和第十一晶体管t11传输至第一输出端out1。第二电容c2存储第五电压端v5的高电平信号,相当于第五电压端v5对第二电容c2进行充电,充电过程中第一输出端out1的电位逐渐增加,输出呈上升趋势的斜波信号。

211.也就是说,阶段二中,第七晶体管t7和第九晶体管t9截止,第八晶体管t8、第十晶体管t10以及第十一晶体管导通,第一输出端out1输出呈上升趋势的斜波信号。

212.其中,上述发光驱动器31的驱动方法是以第八晶体管t8、第九晶体管t9、第十一晶体管t11为n型晶体管,第十晶体管t10为p型晶体管为例进行示意说明的,但本技术实施例不对此进行限定。

213.需要说明的是,受第二信号端vre控制的第十晶体管t10为p型晶体管,通过控制第二信号端vre的电位,使得第十晶体管t10的栅极(g)、源极(s)和漏极(d)电压满足vds<vgs-vth(vth为第十晶体管t10的阈值电压),此时第十晶体管t10工作在饱和区域,即第十晶体管t10的电流可以不受其漏极的电位变化而变化,为常开晶体管。

214.另外,可以向第二信号端vre提供一个固定的电位,使得第二电容c2以一个恒定的电流进行充电,即第一输出端out1输出的斜波信号各段只有一个斜率。也可以通过调整第二信号端vre的电位来调整第二电容c2的充电速度,进而改变斜波信号斜波的斜率。

215.在另一种可能的实施例中,如图8a所示,第四电压端v4为高电平信号端,例如为高电平电源信号端vdd。第五电压端v5为低电平信号端,例如为接地端gnd或者低电平电源信号端vss。第三电压端v3和第六电压端v6为低电平信号端,例如为接地端gnd或者低电平电源信号端vss,第三电压端v3和第六电压端v6可以相耦接。

216.结合如图8b所示的时序图,示例的,输出控制子电路311在第一输入端in1的有效脉冲的控制下将第一时钟信号端clk1的时钟信号传输至第二节点d,第一输出子电路312在第二节点d的有效脉冲的控制下,将第四电压端v4的高电平信号传输至第一输出端out1。第六电压端v6的信号为低电平信号,存储子电路313存储第一输出端out1的高电平信号,相当于第四电压端v4的高电平信号对存储子电路313进行充电。

217.输出控制子电路311在第二输入端in2的有效脉冲的控制下将第三电压端v3的低电平信号传输至第二节点d,第一输出子电路312在第二输入端in2的有效脉冲和第二信号端vre的有效脉冲的控制下将第五电压端v5的低电平信号传输至第一输出端out1。第六电压端v6的信号为低电平信号,存储子电路313存储第一输出端out1的低电平信号,相当于第五电压端v5的低电平信号对存储子电路313进行放电。在放电过程中,第一输出端out1的信号逐渐下降,发光驱动器31输出呈下降趋势的斜波信号。

218.关于发光驱动器31的详细结构,示例的,如图8c所示,输出控制子电路311包括第七晶体管t7和第八晶体管t8。第一输出子电路312包括第九晶体管t9、第十晶体管t10以及第十一晶体管t11。存储子电路313包括第二电容c2。各晶体管和电容与各端口之间的连接关系与图7c所示的发光驱动器31中的连接关系相同,可参考相关描述,此处不再赘述。

219.结合图8b所示的时序图,如图8c所示的发光驱动器31的驱动方法包括:

220.阶段一:

221.如图8b所示,第一输入端in1接收高电平信号,第二输入端in2接收低电平信号。如图8d所示,第七晶体管t7在第一输入端in1高电平信号的控制下导通,第一时钟信号端clk1的时钟信号经第七晶体管t7传输至第二节点d。第九晶体管t9在第二节点d高电平信号的控制下将导通,第四电压端v4的高电平信号经第九晶体管t9传输至第一输出端out1,第二电容c2存储第四电压端v4的高电平信号,相当于对第二电容c2进行充电。第八晶体管t8和第十一晶体管t11在第二输入端in2低电平信号的控制下截止,虽然第十晶体管t10在第二信号端vre的高电平信号(大于vth的电位,vth为第十晶体管t10的阈值电压)的控制下导通,但第十一晶体管t11截止,第五电压端v5的低电平信号无法传输至第一输出端out1。因此,第一输出端out1的电位维持在第四电压端v4的高电平电位(例如vdd)。

222.也就是说,阶段一中,第七晶体管t7、第九晶体管t9以及第十晶体管t10导通,第八晶体管t8和第十一晶体管t11截止。

223.阶段二:

224.如图8b所示,第一输入端in1接收低电平信号时,第二输入端in2接收高电平信号。如图8e所示,第七晶体管t7在第一输入端in1低电平信号的控制下截止,第八晶体管t8和第十一晶体管t11在第二输入端in2低电平信号的控制下导通。第三电压端v3的低电平信号经第八晶体管t8传输至第二节点d,第九晶体管t9在第二节点d低电平信号的控制下截止。第十晶体管t10在第二信号端vre的高电平信号(大于vth的电位,vth为第十晶体管t10的阈值电压)的控制下导通,第五电压端v5的低电平信号经第十晶体管t10和第十一晶体管t11传输至第一输出端out1。第二电容c2存储第五电压端v5的低电平信号,相当于对第二电容c2进行放电,放电过程中第一输出端out1的电位逐渐降低,输出呈下降趋势的斜波信号。

225.也就是说,阶段二中,第七晶体管t7和第九晶体管t9截止,第八晶体管t8、第十晶体管t10以及第十一晶体管导通。

226.其中,上述发光驱动器31的驱动方法是以第八晶体管t8、第九晶体管t9、第十晶体管t10以及第十一晶体管t11为n型晶体管为例进行示意说明的,但本技术实施例不对此进行限定。

227.需要说明的是,受第二信号端vre控制的第十晶体管t10为n型晶体管,通过控制第二信号端vre的电位,使得第十晶体管t10的栅极(g)、源极(s)和漏极(d)电压满足vds》vgs-vth(vth为第十晶体管t10的阈值电压),此时第十晶体管t10工作在饱和区域,即第十晶体管t10的电流可以不受其漏极的电位变化而变化,为常开晶体管。

228.另外,可以向第二信号端vre提供一个固定的电位,使得第二电容c2以一个恒定的电流进行放电,即第一输出端out1输出的斜波信号各段只有一个斜率。也可以通过调整第二信号端vre的电位来调整第二电容c2的放电速度,进而改变斜波信号斜波的斜率。

229.其中,第一输入端in1的信号和第二输入端in2的信号例如可以由上述显示面板10

中的ddic提供,或者由位于非显示区2的其他电路提供。

230.关于向上述像素电路21的栅极扫描信号端scan提供逐行扫描的栅极信号的方式,在一些实施例中,例如可以通过栅极驱动电路40向上述像素电路21提供逐行扫描的栅极信号。

231.本技术实施例不对栅极驱动电路40的结构进行限定,相关技术中用于向像素电路21的栅极扫描信号端scan提供栅极信号的栅极驱动电路40均适用于本技术。

232.示例的,栅极驱动电路40包括多级级联的移位寄存器(shift register,sr);移位寄存器用于输出栅极信号,移位寄存器的第二输出端out2与栅极扫描信号端scan相耦接,移位寄存器用于向栅极扫描信号端scan提供栅极信号。

233.关于移位寄存器的结构,如图9a所示,移位寄存器sr包括第一输入子电路41、第二输入子电路42、第一下拉控制子电路43、第二下拉控制子电路44、漏电保护子电路45、上拉节点q、下拉节点qb以及第二输出子电路46。

234.第一输入子电路41与第二时钟信号端clk2、第三输入端in3以及上拉节点q相耦接,用于在第二时钟信号端clk2的控制下,将第三输入端in3的信号传输至上拉节点q。

235.第二输入子电路42与第四输入端in4、第三电压端v3以及上拉节点q相耦接,用于在第四输入端in4的控制下,将第三电压端v3的信号传输至上拉节点q。

236.第一下拉控制子电路43与第二时钟信号端clk2和下拉节点qb相耦接,用于在第二时钟信号端clk2的控制下,将第二时钟信号端clk2的信号的信号传输至下拉节点qb。

237.第二下拉控制子电路44与第三电压端v3、上拉节点q以及下拉节点qb相耦接,用于在上拉节点q的控制下,将第三电压端v3的信号传输至下拉节点qb。

238.漏电保护子电路45与第一输入子电路41、第一时钟信号端clk1以及第二输出端out2相耦接,用于降低上拉节点q的漏电流。

239.第二输出子电路46与上拉节点q、下拉节点qb、第一时钟信号端clk1、第三电压端v3以及第二输出端out2相耦接,用于在上拉节点q的控制下将第一时钟信号端clk1的信号传输至第二输出端out2,在下拉节点qb的控制下将第三电压端v3的信号传输至第二输出端out2。

240.关于移位寄存器sr中各子电路的结构,示例的,如图9a所示,第一输入子电路41包括第十二晶体管t12和第十三晶体管t13。

241.第十二晶体管t12的栅极与第二时钟信号端clk2相耦接,第十二晶体管t12的第一极与第三输入端in3相耦接,第十二晶体管t12的第二极与第十三晶体管t13的第一极相耦接。

242.第十三晶体管t13的栅极与第二时钟信号端clk2相耦接,第十三晶体管t13的第二极与上拉节点q相耦接。

243.第二输入子电路42包括第十四晶体管t14和第十五晶体管t15。

244.第十四晶体管t14的栅极与第四输入端in4相耦接,第十四晶体管t14的第一极与第三电压端v3相耦接,第十四晶体管t14的第二极与第十五晶体管t15的第一极相耦接。

245.第十五晶体管t15的栅极与第四输入端in4相耦接,第十五晶体管t15的第二极与上拉节点q相耦接。

246.第一下拉控制子电路43包括第十六晶体管t16。

247.第十六晶体管t16的栅极与第二时钟信号端clk2相耦接,第十六晶体管t16的第一极与第二时钟信号端clk2相耦接,第十六晶体管t16的第二极与下拉节点qb相耦接。

248.第二下拉控制子电路44包括第十七晶体管t17和第十八晶体管t18。

249.第十七晶体管t17的栅极与第三电压端v3相耦接,第十七晶体管t17的第一极与第三电压端v3相耦接,第十七晶体管t17的第二极与第十八晶体管t18的第一极相耦接。

250.第十八晶体管t18的栅极与上拉节点q相耦接,第十八晶体管t18的第二极与下拉节点qb相耦接。

251.漏电保护子电路45包括第十九晶体管t19。

252.第十九晶体管t19的栅极与第二输出端out2相耦接,第十九晶体管t19的第一极与第一时钟信号端clk1相耦接,第十九晶体管t19的第二极与第十三晶体管t13的第一极相耦接。

253.第二输出子电路46包括第二十晶体管t20、第二十一晶体管t21以及第三电容c3。

254.第二十晶体管t20的栅极与上拉节点q相耦接,第二十晶体管t20的第一极与第一时钟信号端clk1相耦接,第二十晶体管t20的第二极与第二输出端out2相耦接。

255.第二十一晶体管t21的栅极与下拉节点qb相耦接,第二十一晶体管t21的第一极与第三电压端v3相耦接,第二十一晶体管t21的第二极与第二输出端out2相耦接。

256.第三电容c3的一端与上拉节点q相耦接,第三电容c3的另一端与第二输出端out2相耦接。

257.需要说明的是,上述晶体管可以为n型晶体管,也可以为p型晶体管;可以为增强型晶体管,也可以为耗尽型晶体管;上述晶体管的第一极可以为源极,第二极可以为漏极,或者上述晶体管的第一极可以为漏极,第二极为源极,本发明对此不作限定。

258.以下,以上述晶体管均为n型晶体管为例,结合图9b所示的信号时序图对图9a所示的移位寄存器sr在不同的阶段的通断情况进行详细的举例说明。其中,本发明实施例中是以第三电压端v3恒定输出低电平为例进行的说明。

259.阶段一:

260.第二时钟信号端clk2接收高电平信号、第三输入端in3接收高电平信号、第一时钟信号端clk1接收低电平信号、第四输入端in4接收低电平信号。第十二晶体管t12和第十三晶体管t13在第二时钟信号端clk2的高电平信号的控制下导通,第三输入端in3的高电平信号经第十二晶体管t12和第十三晶体管t13传输至上拉节点q,上拉节点q为高电平信号。第二十晶体管t20在上拉节点q高电平信号的控制下导通,第一时钟信号端clk1的低电平信号经第二十晶体管t20传输至第二输出端out2。第三电容c3存储上拉节点q的高电平信号。第十四晶体管t14和第十五晶体管t15在第四输入端in4低电平信号的控制下截止。第十六晶体管t16在第二时钟信号端clk2的高电平信号的控制下导通,第二时钟信号端clk2的高电平信号经第十六晶体管t16传输至下拉节点qb。第十七晶体管t17和第十八晶体管t18在上拉节点q的高电平信号的控制下导通,第三电压端v3的低电平信号经第十七晶体管t17和第十八晶体管t18传输至下拉节点qb。通过调整第十六晶体管t16、第十七晶体管t17和第十八晶体管t18的宽长比等参数,使得第十七晶体管t17和第十八晶体管t18的驱动能力大于第十六晶体管t16的驱动能力,从而使得下拉节点qb的电位为第三电压端v3的低电平电位。第二十一晶体管t21在下拉节点qb低电平信号的控制下截止。第十九晶体管t19在第二输出端

out2的低电平信号的控制下截止。

261.也就是说,在阶段一,第十二晶体管t12、第十三晶体管t13、第十六晶体管t16、第十七晶体管t17、第十八晶体管t18以及第二十晶体管t20导通,第十四晶体管t14、第十五晶体管t15、第十九晶体管t19以及第二十一晶体管t21截止。第二输出端out2输出低电平信号。

262.阶段二:

263.第一时钟信号端clk1接收高电平信号、第二时钟信号端clk2接收低电平信号、第三输入端in3接收低电平信号、第四输入端in4接收低电平信号,第十二晶体管t12、第十三晶体管t13、第十六晶体管t16在第二时钟信号端clk2的低电平信号的控制下截止。第十四晶体管t14和第十五晶体管t15在第四输入端in4的低电平信号的控制下截止。第三电容c3对上拉节点q进行充电,使得上拉节点q保持高电平信号。第十七晶体管t17和第十八晶体管t18在上拉节点q高电平信号的控制下导通,第三电压端v3的低电平信号经第十七晶体管t17和第十八晶体管t18传输至下拉节点qb。第二十一晶体管t21在下拉节点qb低电平信号的控制下截止。第二十晶体管t20在上拉节点q高电平信号的控制下导通,第一时钟信号端clk1的高电平信号经第二十晶体管t20传输至第二输出端out2。此外,在第三电容c3的自举(bootstrapping)作用下,上拉节点q的电位进一步升高(第三电容c3与第二输出端out2连接的一端的电位由0跳变为1,在第三电容c3对上拉节点q进行充电时,上拉节点q的电位在1的基础上再向高电位跳变1,跳变为2),以维持第二十晶体管t20处于导通状态,使得第一时钟信号端clk1的高电平能够作为栅极信号输出至与第二输出端out2相耦接的栅极扫描信号端scan上。第十九晶体管t19在第二输出端out2的高电平信号的控制下导通,将第一时钟信号端clk1的高电平信号传输至第十三晶体管t13的第一极,以降低第十三晶体管t13的第一极与第二极的电压差,从而降低第十三晶体管t13上的漏电流。

264.也就是说,在阶段二,第十七晶体管t17、第十八晶体管t18、第十九晶体管t19以及第二十晶体管t20导通,第十二晶体管t12、第十三晶体管t13、第十四晶体管t14、第十五晶体管t15、第十六晶体管t16以及第二十一晶体管t21截止。第二输出端out2输出高电平信号。

265.阶段三:

266.第二时钟信号端clk2接收高电平信号、第四输入端in4接收高电平信号、第三输入端in3接收低电平信号、第一时钟信号端clk1接收低电平信号,第十四晶体管t14和第十五晶体管t15在第四输入端in4的高电平信号的控制下导通,第三电压端v3的信号经第十四晶体管t14和第十五晶体管t15传输至上拉节点q,上拉节点q为低电平信号。第十二晶体管t12和第十三晶体管t13在第二时钟信号端clk2的高电平信号的控制下导通,第三输入端in3的低电平信号经第十二晶体管t12和第十三晶体管t13传输至上拉节点q,上拉节点q为低电平信号。第二十晶体管t20在上拉节点q低电平信号的控制下截止。第十七晶体管t17和第十八晶体管t18在上拉节点q低电平信号的控制下截止。第十六晶体管t16在第二时钟信号端clk2的高电平信号的控制下导通。第二时钟信号端clk2的高电平信号经第十六晶体管t16传输至下拉节点qb,控制下拉节点qb为高电位。第二十一晶体管t21在上拉节点q高电平信号的控制下导通,第三电压端v3的低电平信号经第二十一晶体管t21传输至第二输出端out2,第二输出端out2输出低电平信号。第十九晶体管t19在第二输出端out2低电平信号的

控制下截止。

267.也就是说,在阶段三,第十二晶体管t12、第十三晶体管t13、第十四晶体管t14、第十五晶体管t15、第十六晶体管t16以及第二十一晶体管t21导通,第十七晶体管t17、第十八晶体管t18、第十九晶体管t19以及第二十晶体管t20截止。第二输出端out2输出低电平信号。

268.需要说明的是,第一,上述实施例中晶体管的通、断过程是以所有晶体管为n型晶体管为例进行说明的,当所有晶体管均为p型时,需要对图9b中各个控制信号进行翻转,而移位寄存器中各个电路的晶体管的通断过程同上,此处不再赘述。

269.第二,上述移位寄存器sr的工作过程,是以上述多个移位寄存器级sr联构成的栅极驱动电路40采用正向扫描的方式为例进行的说明。

270.实现上述移位寄存器级sr联的方式,示例的,如图9c所示,第一级移位寄存器sr(1)的第三输入端in3与起始信号端stv相耦接。

271.除第一级移位寄存器sr(1)外,其他级移位寄存器sr(m)的第三输入端in3与上一级移位寄存器sr(m-1)的第二输出端out2相耦接。

272.除最后一级移位寄存器sr(n)外,其他级移位寄存器sr(m)的第四输入端in4与下一级移位寄存器sr(m+1)的第二输出端out2相耦接。

273.最后一级移位寄存器sr(n)的第四输入端in4与起始信号端stv相耦接。

274.其中,奇数级移位寄存器sr的第一时钟信号端clk1与偶数级移位寄存器sr的第二时钟信号端clk2相耦接,接收同一时钟信号。奇数级移位寄存器sr的第二时钟信号端clk2与偶数级移位寄存器sr的第一时钟信号端clk1相耦接,接收同一时钟信号。

275.这样一来,当起始信号端stv的起始信号输入第一级移位寄存器单元sr(1)的第三输入端in3时,最后一级移位寄存器单元sr(n)的第四信号输入端可以将起始信号端stv的起始信号作为第四信号输入端的信号对最后一级移位寄存器单元sr(n)的第二输出端out2进行复位。

276.或者,最后一级移位寄存器sr(n)的第四输入端in4与复位信号端相耦接。

277.这样一来,当起始信号端stv接收的为高电平信号时,起始信号端stv的信号为有效信号,启动第一级移位寄存器sr(1)。当起始信号端stv接收的为低电平信号时,起始信号端stv的信号为非有效信号。

278.第一级移位寄存器sr(1)向与该第一级移位寄存器sr(1)的第二输出端out2相耦接的栅极扫描信号端scan提供栅极信号。同时,该第一级移位寄存器sr(1)还向第二级移位寄存器sr(2)的第三输入端in3提供起始信号,以使得第二级移位寄存器sr(2)启动。

279.接下来,第二级移位寄存器sr(2)向与该第二级移位寄存器sr(2)的第二输出端out2相耦接的栅极扫描信号端scan提供栅极信号。同时,该第二级移位寄存器sr(2)还向第三级移位寄存器sr(3)的第三输入端in3提供起始信号,以使得第三级移位寄存器sr(3)启动。

280.重复上述过程,通过上述多个级联的移位寄存器sr,可以对显示面板中的多个亚像素单元20进行逐行扫描。

281.基于上述显示面板的结构,显示面板在驱动过程包括:

282.栅极驱动电路40中的移位寄存器向显示面板中的栅极扫描信号端scan分时传输

有效脉冲,像素电路21中的数据写入子电路211在栅极扫描信号端scan的有效脉冲的控制下,将数据信号端data的信号传输至第一节点a。控制子电路212在栅极扫描信号端scan的有效脉冲、控制信号端ctr的有效脉冲和第一节点a的非有效脉冲的控制下,将第二电压端v2的信号传输至驱动子电路213。驱动子电路213在控制子电路212的有效脉冲和第一信号端vba的的有效脉冲的控制下,与发光元件22导通,根据第一电压端v1的信号和第二电压端v2的信号生成驱动信号,驱动发光元件22发光。

283.移位寄存器在向栅极扫描信号端scan传输有效脉冲后,向栅极扫描信号端scan传输非有效脉冲信号。发光驱动电路30中的发光驱动器31向与接收非有效脉冲的数据写入子电路211相耦接的斜波扫描信号端sweep传输斜波信号。数据写入子电路211在栅极扫描信号端scan的非有效脉冲的控制下,将斜波扫描信号端sweep的斜波信号传输至第一节点a。第一节点a的斜波信号从非有效脉冲逐渐变为有效脉冲。第一节点a的斜波信号变为有效脉冲后,控制子电路212在栅极扫描信号端scan的非有效脉冲、控制信号端ctr的有效脉冲和第一节点a的有效脉冲的控制下,将第一电压端v1的信号传输至驱动子电路213。驱动子电路213在控制子电路212的非有效脉冲的控制下,与发光元件22断开,发光元件22停止发光。

284.其中,可以理解的是,在显示面板中的像素电路21为图5a所示的像素电路21(斜波扫描信号端sweep接收呈上升趋势的斜波信号)的情况下,用于向像素电路21提供斜波信号的发光驱动器31例如可以为图7a所示的发光驱动器31(输出呈上升趋势的斜波信号)。

285.在显示面板中的像素电路21为图6a所示的像素电路21(斜波扫描信号端sweep接收呈下降趋势的斜波信号)的情况下,用于向像素电路21提供斜波信号的发光驱动器31例如可以为图8a所示的发光驱动器31(输出呈下降趋势的斜波信号)。

286.本示例提供的显示面板,在示例一提供的显示面板驱动架构的基础上,将斜波扫描信号端sweep设置为多个,位于不同行的像素电路21与不同斜波扫描信号端sweep相耦接,使得显示面板中的斜波扫描信号端sweep接收的斜波信号也类似于栅极扫描信号端scan的栅极信号,变成移位式斜波信号。所谓的移位式斜波,是指每一行像素的斜波信号彼此相互独立不干扰,并且下一行的斜波信号脉冲开始时间相比上一行的斜波信号脉冲开始时间往后推移一个驱动阶段p1。即,如图10所示,对于第n行像素电路21来说,栅极扫描信号端scan的栅极信号在驱动阶段p1的有效脉冲输入结束后,第n行像素电路21就开始进入发光阶段p2,斜波扫描信号端sweep就开始输入斜波信号。与此同时,第n+1行像素电路21开始进入驱动阶段p1。

287.也就是说,与同一行像素电路21相耦接的栅极扫描信号端scan和斜波扫描信号端sweep二者的有效脉冲信号不存在交叠。与不同行像素电路21相耦接的栅极扫描信号端scan和斜波扫描信号端sweep二者的有效脉冲信号可以存在交叠。与相邻两行像素电路21相耦接的斜波扫描信号端sweep之间的斜波信号扫描开始时间相差一个驱动阶段p1的时间,任意相邻两行的斜波信号的扫描开始时间向后推移的时间可以相等。其中,任意相邻两行的斜波信号的扫描开始时间向后推移的时间可以是一个栅极信号的有效脉冲宽度,也可以是多个栅极信号的有效脉冲宽度,本技术实施例对此不作限定,图10仅为一种示意。

288.示例的,以第一行像素电路21为例,当第一栅极扫描信号端scan(1)输入有效脉冲时,数据信号端data的数据信号开始对第一行像素电路21进行数据写入。当第一栅极扫描信号端scan(1)扫描完毕后,立即进入发光阶段p2,第一斜波扫描信号端sweep(1)开始扫

描,因为第一斜波扫描信号端sweep(1)是用来控制发光元件22发光的,所以此时发光元件22已经开始发光,发光元件22发光时间的长短取决于数据信号端data数据信号的电压大小。在一帧的时间内,每一行像素电路21驱动阶段p1所需的时间为对应行的栅极信号有效脉冲宽度,其余时间都可以用来作为发光元件22发光的时间,因此发光元件22的发光时间可以有效提升。以显示面板的分辨率为1920*1080(rgb)为例,在一帧16.68ms的时间内,假设每一行栅极信号的有效脉冲宽度为5us,若采用示例一的方案,则发光元件22发光时间最大的占比为(16680-5*1920)/16680=42.5%。若采用本示例的方案,则发光时间最大的占比为(16680-5)/16680》99%,其发光时间可以提升2倍以上。

289.基于此,本示例中通过改变显示面板的内部结构,可以很大程度的延长显示面板中发光元件22的发光时长。通过延长发光元件22的发光时长,可以有效提升显示面板的显示亮度,从而使得本示例提供的显示面板可以适用于各种屏幕尺寸的电子设备,解决了以micro led作为发光元件22的显示面板无法应用于户外屏幕、电视等大尺寸屏幕的问题。此外,通过延长发光元件22的发光时长,使得显示面板的可控灰阶数变多(发光时长短,有些灰阶控制实现不了),从而使得显示面板具有更高的色彩饱和度。其次,由于每行发光元件22的发光时长不受其他行像素电路21的影响,也就是说,每行发光元件22的发光时长不受显示面板的像素分辨率(pixel per inch,ppi)的影响。因此,可以根据需要提高显示面板的像素分辨率。再者,发光驱动器31可以和移位寄存器同步形成,因此,本示例提供的显示面板无需增加显示面板的工艺步骤和工艺成本,但是可以节省ddic内部的斜波信号产生模块,可以节省ddic的成本。另外,本示例中斜波扫描信号端sweep只需向一行像素电路21提供斜波信号,与示例一中的斜波扫描信号端sweep需向整个面板中的像素电路21提供斜波信号相比,明显可以降低斜波信号的负载,可有效解决斜波信号负载过大带来的显示问题。

290.示例三

291.示例三与示例二的不同之处在于,发光驱动电路30的第一输入端in1的信号和第二输入端in2的信号不再由上述显示面板中的ddic提供,而是由移位寄存器中的上拉节点q和下拉节点qb提供。

292.如图11所示,移位寄存器的上拉节点q与发光驱动器31的第一输入端in1相耦接,移位寄存器的下拉节点qb与发光驱动器31的第二输入端in2相耦接。

293.基于此,本技术实施例还提供一种行驱动电路,行驱动电路包括多个示例二中的发光驱动器31。发光驱动器31的结构可以参考示例二中关于发光驱动器31的描述,此处不再赘述。在这种情况下,行驱动电路可以理解为示例二中的发光驱动电路。

294.在一些实施例中,如图11所示,行驱动电路还包括多个级联的移位寄存器,移位寄存器包括上拉节点q和下拉节点qb,发光驱动器31的第一输入端in1与上拉节点q相耦接,发光驱动器31的第二输入端in2与下拉节点qb相耦接。

295.其中,移位寄存器中的上拉节点q和下拉节点qb是用于控制移位寄存器第二输出子电路46向第二输出端out2是否输出栅极信号的有效脉冲的节点。

296.基于此,结合示例二中图7a和图8a所示的发光驱动器31,行驱动电路的驱动方法,包括:

297.上拉节点q接收有效脉冲,第二输出子电路46在上拉节点q的控制下将第一时钟信号端clk1的信号传输至第二输出端out2,输出控制子电路311在上拉节点q的控制下将第一

时钟信号端clk1的信号传输至第二节点d。第一输出子电路312在第二节点d的控制下,将第四电压端v4的信号传输至第一输出端out1。存储子电路313根据第六电压端v6的信号和第一输出端out1的信号,存储第一输出端out1的信号。

298.下拉节点qb接收有效脉冲,第二输出子电路46在下拉节点qb的控制下将第三电压端v3的信号传输至第二输出端out2,输出控制子电路311在下拉节点qb的控制下将第三电压端v3的信号传输至第二节点d。第一输出子电路312在第二输入端in2和第二信号端vre的控制下将第五电压端v5的信号传输至第一输出端out1。存储子电路313根据第六电压端v6的信号和第一输出端out1的信号,存储第一输出端out1的信号。

299.其中,在一些实施例中,如图12a所示,发光驱动器31的结构可以与示例二中图7a所示的发光驱动器31的结构相同,可以参考示例二中关于图7a所示的发光驱动器31的相关描述,此处不再赘述。

300.如图12b所示,移位寄存器的结构可以与示例二中移位寄存器的结构相同,可以参考示例二中关于移位寄存器的相关描述,此处不再赘述。

301.如图12c所示,行驱动电路的驱动方法,包括:

302.阶段一:

303.第二时钟信号端clk2接收高电平信号、第三输入端in3接收高电平信号、第一时钟信号端clk1接收低电平信号、第四输入端in4接收低电平信号。第十二晶体管t12和第十三晶体管t13在第二时钟信号端clk2的高电平信号的控制下导通,第三输入端in3的高电平信号经第十二晶体管t12和第十三晶体管t13传输至上拉节点q,上拉节点q为高电平信号。第二十晶体管t20在上拉节点q高电平信号的控制下导通,第一时钟信号端clk1的低电平信号经第二十晶体管t20传输至第二输出端out2。第三电容c3存储上拉节点q的高电平信号。第十四晶体管t14和第十五晶体管t15在第四输入端in4低电平信号的控制下截止。第十六晶体管t16在第二时钟信号端clk2的高电平信号的控制下导通,第二时钟信号端clk2的高电平信号经第十六晶体管t16传输至下拉节点qb。第十七晶体管t17和第十八晶体管t18在上拉节点q的高电平信号的控制下导通,第三电压端v3的低电平信号经第十七晶体管t17和第十八晶体管t18传输至下拉节点qb。通过调整第十六晶体管t16、第十七晶体管t17和第十八晶体管t18的宽长比等参数,使得第十七晶体管t17和第十八晶体管t18的驱动能力大于第十六晶体管t16的驱动能力,从而使得下拉节点qb的电位为第三电压端v3的低电平电位。第二十一晶体管t21在下拉节点qb低电平信号的控制下截止。第十九晶体管t19在第二输出端out2的低电平信号的控制下截止。

304.在第二输出端out2输出低电平的同时,第七晶体管t7在上拉节点q为高电平信号的控制下导通,第一时钟信号端clk1的低电平非时钟信号经第七晶体管t7传输至第二节点d。第九晶体管t9在第二节点d低电平信号的控制下截止,第八晶体管t8和第十一晶体管t11在下拉节点qb低电平信号的控制下截止,虽然第十晶体管t10在第二信号端vre的低电平信号的控制下导通,但第十一晶体管t11截止,第五电压端v5的高电平信号无法传输至第一输出端out1。因此,第一输出端out1悬空(floating),维持之前的电位。

305.也就是说,在阶段一,第七晶体管t7、第十晶体管t10、第十二晶体管t12、第十三晶体管t13、第十六晶体管t16、第十七晶体管t17、第十八晶体管t18以及第二十晶体管t20导通,第八晶体管t8、第九晶体管t9、第十一晶体管t11、第十四晶体管t14、第十五晶体管t15、

第十九晶体管t19以及第二十一晶体管t21截止。第一输出端out1悬空,第二输出端out2输出低电平信号。

306.阶段二:

307.第一时钟信号端clk1接收高电平信号、第二时钟信号端clk2接收低电平信号、第三输入端in3接收低电平信号、第四输入端in4接收低电平信号,第十二晶体管t12、第十三晶体管t13、第十六晶体管t16在第二时钟信号端clk2的低电平信号的控制下截止。第十四晶体管t14和第十五晶体管t15在第四输入端in4的低电平信号的控制下截止。第三电容c3对上拉节点q进行充电,使得上拉节点q保持高电平信号。第十七晶体管t17和第十八晶体管t18在上拉节点q高电平信号的控制下导通,第三电压端v3的低电平信号经第十七晶体管t17和第十八晶体管t18传输至下拉节点qb。第二十一晶体管t21在下拉节点qb低电平信号的控制下截止。第二十晶体管t20在上拉节点q高电平信号的控制下导通,第一时钟信号端clk1的高电平信号经第二十晶体管t20传输至第二输出端out2。此外,在第三电容c3的自举作用下,上拉节点q的电位进一步升高,以维持第二十晶体管t20处于导通状态,使得第一时钟信号端clk1的高电平能够作为栅极信号输出至与第二输出端out2相耦接的栅极扫描信号端scan上。第十九晶体管t19在第二输出端out2的高电平信号的控制下导通。

308.在第二输出端out2输出高电平的同时(像素电路21进入驱动阶段p1),第七晶体管t7在上拉节点q高电平信号的控制下导通,第一时钟信号端clk1的时钟信号经第七晶体管t7传输至第二节点d。第九晶体管t9在第二节点d高电平信号的控制下将导通,第四电压端v4的低电平信号经第九晶体管t9传输至第一输出端out1,第二电容c2存储第四电压端v4的低电平信号,相当于第二电容c2对第四电压端v4进行放电。第八晶体管t8和第十一晶体管t11在下拉节点qb低电平信号的控制下截止,虽然第十晶体管t10在第二信号端vre的低电平信号的控制下导通,但第十一晶体管t11截止,第五电压端v5的高电平信号无法传输至第一输出端out1。因此,第一输出端out1的电位维持在第四电压端v4的低电平电位。

309.也就是说,在阶段二,第七晶体管t7、第九晶体管t9、第十晶体管t10、第十二晶体管t12、第十三晶体管t13、第十六晶体管t16、第十七晶体管t17、第十八晶体管t18以及第二十晶体管t20导通,第八晶体管t8、第十一晶体管t11、第十四晶体管t14、第十五晶体管t15、第十九晶体管t19以及第二十一晶体管t21截止。第一输出端out1输出低电平信号,第二输出端out2输出高电平信号。

310.阶段三:

311.第二时钟信号端clk2接收高电平信号、第四输入端in4接收高电平信号、第三输入端in3接收低电平信号、第一时钟信号端clk1接收低电平信号,第十四晶体管t14和第十五晶体管t15在第四输入端in4的高电平信号的控制下导通,第三电压端v3的信号经第十四晶体管t14和第十五晶体管t15传输至上拉节点q,上拉节点q为低电平信号。第十二晶体管t12和第十三晶体管t13在第二时钟信号端clk2的高电平信号的控制下导通,第三输入端in3的低电平信号经第十二晶体管t12和第十三晶体管t13传输至上拉节点q,上拉节点q为低电平信号。第二十晶体管t20在上拉节点q低电平信号的控制下截止。第十七晶体管t17和第十八晶体管t18在上拉节点q低电平信号的控制下截止。第十六晶体管t16在第二时钟信号端clk2的高电平信号的控制下导通。第二时钟信号端clk2的高电平信号经第十六晶体管t16传输至下拉节点qb,控制下拉节点qb为高电位。第二十一晶体管t21在上拉节点q高电平信

号的控制下导通,第三电压端v3的低电平信号经第二十一晶体管t21传输至第二输出端out2,第二输出端out2输出低电平信号。第十九晶体管t19在第二输出端out2低电平信号的控制下截止。

312.在第二输出端out2输出低电平信号的同时(像素电路21进入发光阶段p2),第七晶体管t7在上拉节点q低电平信号的控制下截止,第八晶体管t8和第十一晶体管t11在下拉节点qb高电平信号的控制下导通。第三电压端v3的低电平信号经第八晶体管t8传输至第二节点d,第九晶体管t9在第二节点d低电平信号的控制下截止。第十晶体管t10在第二信号端vre的低电平信号的控制下导通,第五电压端v5的高电平信号经第十晶体管t10和第十一晶体管t11传输至第一输出端out1。第二电容c2存储第五电压端v5的高电平信号,相当于第五电压端v5对第二电容c2进行充电,充电过程中第一输出端out1的电位逐渐增加,输出呈上升趋势的斜波信号。

313.也就是说,在阶段三,第八晶体管t8、第十晶体管t10、第十一晶体管t11、第十二晶体管t12、第十三晶体管t13、第十四晶体管t14、第十五晶体管t15、第十六晶体管t16以及第二十一晶体管t21导通,第七晶体管t7、第九晶体管t9、第十七晶体管t17、第十八晶体管t18、第十九晶体管t19以及第二十晶体管t20截止。第一输出端out1输出呈上升趋势的斜波信号,第二输出端out2输出低电平信号。

314.其中,可以向第二信号端vre提供一个固定的电位,使得第十晶体管t10的源漏压差(vgs)为固定值,从而使得第二电容c2以一个恒定的电流进行充电,即第一输出端out1输出的斜波信号各段只有一个斜率。也可以通过调整第二信号端vre的电位来调整第二电容c2的充电速度,进而改变斜波信号斜波的斜率。

315.在另一些实施例中,图13a所示,发光驱动器31的结构可以与示例二中图8a所示的发光驱动器31的结构相同,可以参考示例二中关于图8a所示的发光驱动器31的相关描述,此处不再赘述。

316.如图13b所示,移位寄存器的结构可以与示例二中移位寄存器的结构相同,可以参考示例二中关于移位寄存器的相关描述,此处不再赘述。

317.行驱动电路的驱动过程的时序图如图13c所示,在驱动过程中,

318.阶段一:

319.第二时钟信号端clk2接收高电平信号、第三输入端in3接收高电平信号、第一时钟信号端clk1接收低电平信号、第四输入端in4接收低电平信号。上拉节点q为高电平信号,下拉节点qb为低电平信号。

320.第七晶体管t7、第十晶体管t10、第十二晶体管t12、第十三晶体管t13、第十六晶体管t16、第十七晶体管t17、第十八晶体管t18以及第二十晶体管t20导通,第八晶体管t8、第九晶体管t9、第十一晶体管t11、第十四晶体管t14、第十五晶体管t15、第十九晶体管t19以及第二十一晶体管t21截止。第一输出端out1悬空,第二输出端out2输出低电平信号。

321.阶段二:

322.第一时钟信号端clk1接收高电平信号、第二时钟信号端clk2接收低电平信号、第三输入端in3接收低电平信号、第四输入端in4接收低电平信号。上拉节点q为高电平信号,下拉节点qb为低电平信号。

323.第七晶体管t7、第九晶体管t9、第十晶体管t10、第十二晶体管t12、第十三晶体管

t13、第十六晶体管t16、第十七晶体管t17、第十八晶体管t18以及第二十晶体管t20导通,第八晶体管t8、第十一晶体管t11、第十四晶体管t14、第十五晶体管t15、第十九晶体管t19以及第二十一晶体管t21截止。第一输出端out1输出低电平信号,第二输出端out2输出高电平信号。

324.阶段三:

325.第二时钟信号端clk2接收高电平信号、第四输入端in4接收高电平信号、第三输入端in3接收低电平信号、第一时钟信号端clk1接收低电平信号。上拉节点q为低电平信号,下拉节点qb为高电平信号。

326.第八晶体管t8、第十晶体管t10、第十一晶体管t11、第十二晶体管t12、第十三晶体管t13、第十四晶体管t14、第十五晶体管t15、第十六晶体管t16以及第二十一晶体管t21导通,第七晶体管t7、第九晶体管t9、第十七晶体管t17、第十八晶体管t18、第十九晶体管t19以及第二十晶体管t20截止。第一输出端out1输出呈下降趋势的斜波信号,第二输出端out2输出低电平信号。

327.其中,可以向第二信号端vre提供一个固定的电位,使得第十晶体管t10的源漏压差(vgs)为固定值,从而使得第二电容c2以一个恒定的电流进行放电,即第一输出端out1输出的斜波信号各段只有一个斜率。也可以通过调整第二信号端vre的电位来调整第二电容c2的充电速度,进而改变斜波信号斜波的斜率。

328.另外,由于上拉节点q和下拉节点qb是移位寄存器的内部信号节点,且上拉节点q和下拉节点qb在栅极驱动电路40中的每一级移位寄存器中是属于逐行移位的脉冲信号,因此,各个发光驱动器31产生的斜波信号也具有逐行移位的特征,实现了将斜波信号由示例一中的整个显示面板共用,改为每一行像素电路21各自独立使用斜波信号,以提升发光元件22的发光时间。

329.本示例中通过将移位寄存器的上拉节点q与发光驱动器31的第一输入端in1相耦接,将移位寄存器的下拉节点qb与发光驱动器31的第二输入端in2相耦接,即,斜波信号产生电路中的部分电路(向第一输入端in1和第二输入端in2提供信号的那部分电路)与移位寄存器中的部分电路共用。这样可以很大程度的简化斜波信号产生电路的结构,减少斜波信号产生电路对非显示区2的占用率,有利于电子设备窄边框的实现。

330.示例四

331.示例四与示例二和示例三的不同之处在于,斜波扫描信号端sweep的信号是由ddic提供的,不是由发光驱动电路30提供的。

332.即,显示面板10包括有效显示区1和位于该有效显示区1周边的非显示区2。上述有效显示区1包括多个亚像素单元20,位于同一行的亚像素单元20与同一斜波扫描信号端sweep相耦接,位于不同行的亚像素单元20与不同斜波扫描信号端sweep相耦接。其中,与同一栅极扫描信号端scan相耦接的亚像素单元20位于同一行。

333.上述非显示区2包括栅极驱动电路40、mux、ddic以及柔性电路板fpc。

334.栅极驱动电路40主要为有效显示区1中的亚像素单元20的栅极扫描信号端scan提供逐行扫描的栅极信号,mux用于将有效显示区1中与亚像素单元20的数据信号端data相耦接的数据线与ddic电连接,实现亚像素单元20通过数据线接收ddic传输的数据信号。ddic用于接收电子设备中驱动系统端传输的信号并将信号按照特定的时序控制输送至显示面

板10,驱动系统端传输的信号包括斜波扫描信号端的斜波信号。fpc用于连接驱动系统与ddic。

335.以上,仅为本技术的具体实施方式,但申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1