电致发光显示装置的制作方法

电致发光显示装置

1.本技术要求于2020年12月28日提交的韩国专利申请第10-2020-0184551号的权益,该韩国专利申请通过引用并入本文,如同在此完全阐述一样。

技术领域

2.本公开内容涉及电致发光显示装置。

背景技术:

3.电致发光显示装置根据发光层的材料分为无机发光显示装置和有机发光显示装置。电致发光显示装置的每个像素包括自发射发光元件,并通过根据取决于视频数据的灰度的数据电压来控制发光元件的发光量来调节亮度。

4.随着驱动时间的流逝,可能产生像素之间的驱动特性差异。这样的驱动特性差异导致亮度不均匀,从而使图片质量劣化。尽管进行了补偿电致发光显示装置中的像素之间的驱动特性差异的各种尝试,但是由于低的感测精度,在确保亮度均匀性方面存在限制。

技术实现要素:

5.因此,本公开内容涉及一种电致发光显示装置,其基本上消除了由于相关技术的限制和缺点而引起的一个或更多个问题。

6.本公开内容的目的是提供一种用于提高感测精度的电致发光显示装置。

7.为了实现这些以及其他目的和优点,并根据本发明的目的,如本文所实施和广泛描述的,电致发光显示装置包括:像素,所述像素包括驱动元件,所述驱动元件具有连接至数据线的栅电极和连接至读出线的源电极;感测电路,所述感测电路被配置成在感测操作期间感测根据流过驱动元件的像素电流而变化的读出线的电压;以及升压电路,所述升压电路连接在数据线与读出线之间并且被配置成在感测操作期间根据读出线中的变化的电压来改变数据线的电压。

8.在另一实施方式中,电致发光显示装置,包括像素,像素包括驱动元件,驱动元件具有连接至数据线的栅电极和连接至读出线的源电极;感测电路,感测电路被配置成在感测操作期间感测根据流过驱动元件的像素电流而变化的读出线的电压;以及升压电容器,升压电容器电耦接在数据线与读出线之间,升压电容器被配置成在感测操作期间将读出线的变化的电压耦接至数据线。

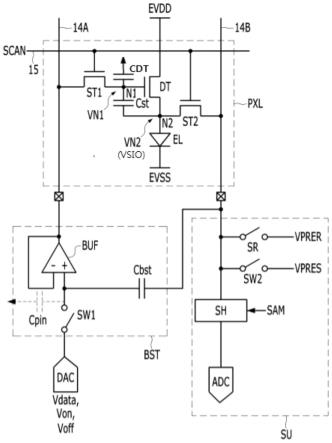

附图说明

9.附图被包括以提供对本发明的进一步理解,并且被并入本技术中并构成本技术的一部分,附图示出了本发明的实施方式并且与说明书一起用于说明本发明的原理。在附图中:

10.图1是示出根据本公开内容的实施方式的电致发光显示装置的框图;

11.图2是示出共享读出线的一个单位像素的连接的示例的图;

12.图3是示出像素阵列和源极驱动ic的配置的示例的图;

13.图4是示出根据本公开内容的实施方式的像素电路、感测电路和升压电路的配置的示例的图;

14.图5是用于驱动图4所示的电路的波形图;

15.图6是用于描述根据升压电路的存在和不存在的操作和效果的差异的图;

16.图7a是与图5的编程时段对应的等效电路图;

17.图7b是与图5的感测时段对应的等效电路图;

18.图7c是与图5的采样时段对应的等效电路图;

19.图8是示出升压电路中包括的升压电容器形成在显示面板中的示例的图;

20.图9是示出升压电路中包括的升压电容器形成在控制印刷电路板上的示例的图;

21.图10是示出根据本公开内容的另一实施方式的像素电路、感测电路和升压电路的配置的示例的图;

22.图11是用于驱动图10所示的电路的波形图;

23.图12是示出与一个单位像素对应的四个升压电路共享一个单个升压电容器的图;以及

24.图13是示出了被配置成具有可控的总电容值的升压电容器单元的图。

具体实施方式

25.参考以下结合附图详细描述的实施方式,本公开内容的优点和特征以及实现本公开内容的优点和特征的方式将变得明显。然而,本公开内容不限于下文所公开的实施方式,并且可以以许多不同的形式实现。相反,提供这些示例性实施方式以使得本公开内容透彻和完整,并且这些示例性实施方式将向本领域技术人员充分传达范围。因此,本公开内容的范围应由权利要求限定。

26.为了描述本公开内容的各种实施方式而在附图中示出的形状、尺寸、比例、角度、数字等仅通过示例的方式给出,因此,本公开内容不限于附图中的图示。在整个说明书中,相同或极其相似的元件由相同的附图标记表示。此外,在本公开内容的描述中,当相关已知技术的详细描述可能使本公开内容的主题相当不清楚时,将省略对相关已知技术的详细描述。在本说明书中,当使用术语“包含”、“包括”等时,除非使用术语“仅”,否则可以添加其他元件。除非上下文另有明确指示,否则以单数形式描述的元件旨在包括复数个元件。

27.在对包括在本公开内容的各种实施方式中的组成元件的解释中,即使没有对其进行明确的描述,组成元件也被解释为包括误差范围。

28.在本公开内容的各种实施方式的描述中,当描述位置关系时,例如,当使用“在

……

上”、“在

……

上方”、“在

……

下方”、“在

……

旁边”等描述两个部件之间的位置关系时,除非使用术语“直接地”或“紧密地”,否则两个部件之间可以安置有一个或更多个其他部件。

29.尽管诸如“第一”和“第二”的术语可以用于描述各种元件,但这些术语仅用于将相同或相似的元件彼此区分开。因此,在本说明书中,除非另有提及,否则在本公开内容的技术范围内,由“第一”修饰的元件可以与由“第二”修饰的元件相同。

30.在本公开内容中,在显示面板的基板上形成的像素电路可以实现为n型金属氧化

物半导体场效应晶体管(mosfet)结构的薄膜晶体管(tft)或p型mosfet结构的tft。tft是包括栅极、源极和漏极的三电极元件。源极是向晶体管提供载流子的电极。载流子在tft中从源极流动。漏极是通过其将载流子释放到外部的电极。也就是说,在mosfet中载流子从源极流向漏极。在n型tft(nmos)的情况下,载流子是电子,因此源极电压低于漏极电压,使得电子可以从源极流向漏极。由于在n型tft中电子从源极流向漏极,所以电流从漏极流向源极。相反,在p型tft(pmos)的情况下,载流子是空穴,因此源极电压高于漏极电压,使得空穴可以从源极流向漏极。由于在p型tft中空穴从源极流向漏极,所以电流从源极流向漏极。应注意,mosfet的源极和漏极不是固定的。例如,mosfet的源极和漏极可以根据所施加的电压而改变。

31.在本公开内容中,tft的半导体层可以由氧化物、非晶硅和多晶硅中的至少一种形成。

32.在下文中,将参照附图详细描述本公开内容的实施方式。在下面的描述中,当包含在本文中的已知功能和配置的详细描述可能使本发明的主题模糊时,将省略其详细描述。

33.图1是示出根据本公开内容的实施方式的电致发光显示装置的框图,图2是示出共享读出线的一个单位像素的连接的示例的图,并且图3是示出像素阵列和源极驱动ic的配置的示例的图。

34.参照图1至图3,根据本公开内容的实施方式的电致发光显示装置包括显示面板10、定时控制器11、数据驱动器12、栅极驱动器13、存储器16、补偿电路20和发电电路30。

35.在显示面板10中以与多条栅极线15交叉的方式布置多条数据线14a和多条读出线14b,并且像素pxl在交叉处以矩阵布置以形成像素阵列。

36.连接至不同数据线14a的两个或更多个像素pxl可以共享相同的读出线14b和相同的栅极线15。例如,如图2所示,用于表示红色的像素r、用于表示白色的像素w、用于表示绿色的像素g和用于表示蓝色的像素b(它们在水平方向上相邻并且连接至同一栅极线15)可以共同连接至单个读出线14b。根据该读出线共享结构,简化了像素阵列结构,因此易于确保显示面板的开口率和处理余量。在读出线共享结构中,多条数据线14a可以布置在相邻读出线14b之间。

37.如图2所示,像素r、像素w、像素g和像素b可以构成单个单位像素。在单位像素中,可以根据灰度率(或发光率)组合红色、白色、绿色和蓝色以表示各种颜色。单位像素可以由像素r、像素g和像素b组成。在这种情况下,在水平方向上相邻并且连接至同一栅极线15的像素r、像素g和像素b可以共同连接至单个读出线14b。

38.每个像素pxl从发电电路30接收高水平像素电压evdd和低水平像素电压evss。本公开内容中的像素pxl可以具有如下电路配置:该电路配置适合于感测根据经过的驱动时间和/或诸如面板温度的环境条件的驱动元件的电子迁移率特性的变化。

39.定时控制器11可以根据预定控制序列执行用于感测操作的感测模式和用于显示操作的显示模式。在此,感测操作是用于感测驱动元件的电子迁移率的变化并根据该变化更新补偿值的操作,并且显示操作是用于在显示面板10中写入校正视频数据cdata以再现显示图像的操作,在校正视频数据cdata中已经反映了补偿值。根据定时控制器11的控制,可以在显示操作期间的垂直消隐时段内执行感测操作。在用于显示的数据电压被写入像素pxl的垂直有效时段之间设置垂直消隐时段。在垂直消隐时段,用于显示的数据电压不写入

像素pxl。在垂直消隐时段,用于感测的数据电压被写入感测像素pxl。

40.可以以像素行l1至ln为单位执行感测操作。例如,可以按照像素行对包括在像素阵列中的第一颜色的所有像素顺序地或非顺序地执行感测操作,然后按照像素行对第二颜色的所有像素顺序地或非顺序地执行感测操作。然后,可以以相同的方式对第三颜色和第四颜色的像素执行感测操作。在此,像素行l1至ln中的每一行不表示物理信号线,而是表示在水平方向上相邻的一组像素pxl。

41.可以仅对一个像素行中包括的不同颜色的一些像素执行感测操作,并且可以省略对其余像素的感测操作。在这种情况下,可以通过插值逻辑计算其余像素的补偿值。插值逻辑可以基于相同颜色的感测像素的补偿值来计算相同颜色的非感测像素的补偿值。如此,可以减少感测更新周期,以使补偿性能最大化,以应对电子迁移率的实时变化。

42.定时控制器11可以基于从主机系统输入的诸如垂直同步信号vsync、水平同步信号hsync、点时钟信号dclk和数据使能信号de的定时信号来生成用于控制数据驱动器12的操作定时的数据定时控制信号ddc和用于控制栅极驱动器13的操作定时的栅极定时控制信号gdc。定时控制器11可以与用于感测操作的定时控制信号ddc和gdc不同地生成用于显示操作的定时控制信号ddc和gdc。

43.栅极定时控制信号gdc包括栅极起始脉冲信号和栅极移位时钟信号。栅极起始脉冲信号被施加至生成第一输出的栅极级以控制栅极级。栅极移位时钟信号是被输入至栅极级以移位栅极起始脉冲信号的时钟信号。

44.数据定时控制信号ddc包括源极起始脉冲信号、源极采样时钟信号和源极输出使能信号。源极起始脉冲信号控制数据驱动器12的数据采样起始定时。源极采样时钟信号基于上升沿或下降沿控制数据采样定时。源极输出使能信号控制数据驱动器12的输出定时。

45.定时控制器11可以包括补偿电路20,但本公开内容不限于此。补偿电路20可以包括在单独的补偿集成电路中。

46.在感测操作期间,补偿电路20从感测电路su接收关于驱动元件的电子迁移率的感测结果数据sdata。补偿电路20基于感测结果数据sdata计算用于对由于驱动元件的劣化(即,电子迁移率变化)而引起的亮度偏差进行补偿的补偿值,并将该补偿值存储在存储器16中。每当执行感测操作时,可以更新在存储器16中存储的补偿值。存储器16可以实现为闪存,但本公开内容不限于此。

47.补偿电路20可以基于从存储器16读取的补偿值校正输入视频数据data,并在显示操作期间将校正视频数据cdata提供给数据驱动器12。可以根据校正视频数据cdata对由于驱动元件中的电子迁移率特性差异引起的亮度偏差进行补偿。

48.数据驱动器12包括至少一个源极驱动器集成电路(sdic)。源极驱动器ic sdic可以包括连接至每条数据线14a的数模转换器(dac)、连接至每条读出线14b的感测电路su、在时间上划分多个感测电路su的输出的多路复用器mux、以及连接至多路复用器mux以将感测电路su的模拟输出转换为感测结果数据sdata的模数转换器(adc)。

49.在显示操作期间,dac根据从定时控制器11提供的数据定时控制信号ddc将校正图像数据cdata转换为用于显示的数据电压并将用于显示的数据电压提供给数据线14a。在感测操作期间,源极驱动器ic sdic的dac可以根据从定时控制器11提供的数据定时控制信号ddc生成用于感测的数据电压并将用于感测的数据电压提供给数据线14a。

50.用于感测的数据电压可以包括用于使驱动元件导通的导通水平数据电压(图4中的von)和用于使驱动元件截止的截止水平数据电压(图4中的voff)。导通水平数据电压被施加至共享读出线14b的像素中的感测像素,而截止水平数据电压被施加至共享读出线14b的像素中的非感测像素。导通水平数据电压是在感测操作期间被施加至感测像素中包括的驱动元件的栅电极以使驱动元件导通的电压(即,生成像素电流的电压),并且截止水平数据电压是在感测操作期间被施加至非感测像素中包括的驱动元件的栅电极以使驱动元件截止的电压(即,阻断像素电流的电压)。考虑到各个颜色的驱动元件/发光元件的不同驱动特性,可以针对红色像素r、绿色像素g、蓝色像素b和白色像素w将导通水平数据电压设置为不同的水平,但本公开内容不限于此。

51.导通水平数据电压被施加至单位像素中的感测像素,而截止水平数据电压被施加至与单位像素中的感测像素共享读出线14b的非感测像素。例如,如果在图2中像素r被感测而像素w、g和b未被感测,则导通水平数据电压可以被施加至像素r的驱动元件,而截止水平数据电压可以被施加至像素w、g和b的驱动元件。

52.每个感测电路su可以连接至每条读出线14b,并通过多路复用器mux选择性地连接至adc。每个感测电路su被实现为电压感测类型,使得其可以在感测操作期间感测根据流过感测像素的驱动元件的像素电流而变化的读出线14b的电压。感测电路su在显示操作期间将从发电电路30接收的用于显示的参考电压vprer施加至像素pxl,并且在感测操作期间将从发电电路30接收的用于感测的参考电压vpres施加至像素pxl。

53.adc可以将从每个感测电路su输出的模拟感测电压转换为数字感测结果数据sdata,并将数字感测结果数据输出至补偿电路20。

54.在感测操作期间,栅极驱动器13可以基于栅极控制信号gdc生成用于感测的栅极信号,然后将用于感测的栅极信号提供给连接至感测像素的栅极线15。用于感测的栅极信号是与用于感测的数据电压同步的用于感测的扫描信号。根据用于感测的栅极信号和用于感测的数据电压,可以顺序地或非顺序地驱动像素行l1至ln以用于感测。

55.在显示操作期间,栅极驱动器13可以基于栅极控制信号gdc生成用于显示的栅极信号,然后将用于显示的栅极信号顺序地提供给栅极线15。用于显示的栅极信号是与用于显示的数据电压同步的用于显示的扫描信号。根据用于显示的栅极信号和用于显示的数据电压,可以顺序地或非顺序地驱动像素行l1至ln以用于显示。

56.发电电路30生成高水平像素电压evdd、低水平像素电压evss、用于显示的参考电压vprer和用于感测的参考电压vpres,以提供给每个像素pxl。发电电路30可以生成栅极驱动器13的操作所需的栅极导通电压和栅极截止电压,并将栅极导通电压和栅极截止电压提供给栅极驱动器13。用于感测或显示的栅极信号在栅极导通电压(即,导通水平)与栅极截止电压(即,截止水平)之间摆动。发电电路30可以生成dac的操作所需的高水平驱动电压,并将高水平驱动电压提供给数据驱动器12。

57.根据本公开内容的实施方式的上述电致发光显示装置通过感测操作对包括在每个像素中的驱动元件的电子迁移率的变化进行补偿。电致发光显示装置在感测操作期间感测根据像素电流而变化的读出线14b的电压,并且基于通过计算获得的读出线14b的电压变化梯度来检测感测像素中的电子迁移率变化。

58.像素电流与驱动元件的电子迁移率成比例。驱动元件的电子迁移率可以根据驱动

时间、温度等而变化。当包括在第一像素中的第一驱动元件的电子迁移率与包括在第二像素中的第二驱动元件的电子迁移率不同时,与相同的栅极-源极电压对应的第一驱动元件的第一像素电流和第二驱动元件的第二像素电流在感测操作期间彼此不同。该像素电流差表现为在相同时间在对应的读出线14b中充载的电压之间的差,因此可以计算读出线14b每单位时间的电压变化梯度。由于读出线14b的电压充电速率随着驱动元件的电子迁移率增加而增加,因此读出线14b的电压变化梯度与电子迁移率成比例。

59.为了准确地感测驱动元件的电子迁移率的变化,需要在感测操作期间将驱动元件的栅极-源极电压(即,用于感测的数据电压与用于感测的参考电压之间的差)保持为特定水平。也就是说,每个感测像素需要操作为恒定电流源。然而,驱动元件的栅极-源极电压可能由于驱动元件周围的寄生电容而损耗。这样的损耗导致感测失真。

60.根据本公开内容的实施方式的电致发光显示装置包括如图3所示的升压电路bst,以抑制上述损耗。尽管在图3中升压电路bst仅连接至读出线14b,但是仅示意性地示出了升压电路bst的一部分连接。升压电路bst可以连接在数据线14a与读出线14b之间。升压电路bst通过包括升压电容器(图4中的cbst)在感测操作期间通过读出线14b中的电压变化来改变数据线14a的电压以将驱动元件的栅极-源极电压保持为设定水平。根据本公开内容的电致发光显示装置可以通过包括升压电路bst来使与驱动元件的电子迁移率相关的感测性能和补偿性能最大化。

61.图4是示出根据本公开内容的实施方式的像素电路、感测电路和升压电路的配置的示例的图,图5是用于驱动图4所示的电路的波形图,并且图6是用于描述根据是否存在升压电路在操作和效果上的差异的图。

62.参照图4,根据本公开内容的实施方式的电致发光显示装置包括:像素pxl,像素pxl包括驱动元件dt,驱动元件dt在感测操作期间具有连接至数据线14a的栅电极和连接至读出线14b的源电极;感测电路su,其被配置成在感测操作期间感测根据流过驱动元件的像素电流而变化的读出线的电压;以及升压电路bst,其连接在数据线14a与读出线14b之间,并且在感测操作期间通过读出线14b中的电压变化来改变数据线14a的电压。根据本公开内容的实施方式的电致发光显示装置还包括输出数据电压(vdata、von或voff)的dac。

63.参照图4,除驱动元件dt之外,像素pxl还可以包括发光元件el、存储电容器cst、第一开关晶体管st1和第二开关晶体管st2。驱动元件dt可以实现为驱动晶体管。尽管在本实施方式中驱动晶体管dt和开关晶体管st1和st2可以实现为n型薄膜晶体管(tft),但本公开内容不限于此,并且它们可以实现为p型tft。此外,构成像素的tft的半导体层可以包括非晶硅、多晶硅或氧化物。

64.驱动晶体管dt包括连接至第一节点n1的栅电极、连接至第二节点n2的源电极和连接至高水平像素电压evdd的输入端子的漏电极。驱动晶体管dt根据栅极-源极电压生成像素电流。像素电流可以被生成为与栅极-源极电压的平方成比例的量值。驱动晶体管dt的电子迁移率可以根据像素中的劣化偏差、温度等而变化。因此,可以在感测操作期间通过感测根据像素电流的读出线14b的电压来检测包括在像素中的驱动晶体管dt的驱动特性的变化。

65.当第二节点n2的电压根据像素电流达到工作点水平时,发光元件el被导通,以在显示操作期间根据像素电流发光。发光元件el包括连接至第二节点n2的阳极、连接至低水

平像素电压evss的输入端子的阴极、以及插入在阳极与阴极之间的有机或无机化合物层。有机或无机化合物层包括空穴注入层(hil)、空穴传输层(htl)、发光层(eml)、电子传输层(etl)和电子注入层(eil)。当施加至阳极的第二节点n2的电压与施加至阴极的低水平像素电压evss相比增加到高于工作点水平时,发光元件el被导通。当发光元件el被导通时,已经通过空穴传输层(htl)的空穴和已经通过电子传输层(etl)的电子移动到发光层(eml)以形成激子,因此发光层(eml)发光。

66.同时,为了提高感测的感测度(或感测的精度),在发光元件el截止的状态下执行感测操作。换言之,在第二节点n2的电压低于发光元件el的工作点水平的范围内执行感测操作。为此,可以将被施加至第二节点n2的用于感测的参考电压vpres设置为充分低于工作点水平和用于显示的参考电压vprer。

67.存储电容器cst连接在第一节点n1与第二节点n2之间。存储电容器cst存储驱动晶体管dt的栅极-源极电压,但是由于寄生电容,存储电容器cst难以保持栅极-源极电压而不发生泄漏。

68.第一开关晶体管st1根据栅极信号scan将数据线14a连接至第一节点n1。第一开关晶体管st1包括连接至栅极线15的栅电极、连接至数据线14a的第一电极(源极和漏极中的一个)和连接至第一节点n1的第二电极(源极和漏极中的另一个)。

69.第二开关晶体管st2根据栅极信号scan将第二节点n2连接至读出线14b。第二开关晶体管st2包括连接至栅极线15的栅电极、连接至读出线14b的第一电极和连接至第二节点n2的第二电极。

70.第一开关晶体管st1和第二开关晶体管st2的栅电极连接至同一栅极线15,因此简化了像素和栅极驱动器的结构。当在显示操作期间根据用于显示的栅极信号scan使第一开关晶体管st1和第二开关晶体管st2导通时,根据显示操作条件对驱动晶体管dt的第一栅极-源极电压(vdata-vprer)进行编程。当在感测操作期间根据用于感测的栅极信号scan使第一开关晶体管st1和第二开关晶体管st2导通时,根据感测操作条件对驱动晶体管dt的第二栅极-源极电压(von-vpres)进行编程。在感测操作期间,第一开关晶体管st1和第二开关晶体管st2根据图5所示的用于感测的栅极信号scan保持导通状态。

71.参照图4,dac在显示操作期间输出用于显示的数据电压vdata,并在感测操作期间输出用于感测的数据电压von或voff。

72.参照图4,感测电路su包括:开关sr,其接通/断开用于显示的参考电压vprer的输入端子与读出线14b之间的电流;开关sw2,其接通/断开用于感测的参考电压vpres的输入端子与读出线14b之间的电流、以及根据采样信号sam进行操作的采样电路sh。

73.在显示操作期间,开关sr响应于用于显示的栅极信号scan而接通。用于显示的参考电压vprer通过读出线14b和第二开关st2施加至第二节点n2。

74.如图5所示,在垂直消隐时段vb中执行感测操作。在图5中,va表示执行显示操作的垂直有效时段。垂直消隐时段vb中的感测操作可以在时间上分为编程时段

①

、感测时段

②

和采样时段

③

。在编程时段

①

中,开关sw2在用于感测的栅极信号scan的导通时段中被接通。用于感测的参考电压vpres通过读出线14b和第二开关晶体管st2在感测时段

②

中施加至第二节点n2。在对应于采样时段

③

的用于感测的栅极信号scan的导通时段中,开关sw2断开并且采样信号sam接通。

75.采样电路sh响应于采样信号sam对读出线14b的电压进行采样。

76.参照图4和图5,在感测操作期间,由驱动晶体管dt的栅极-源极电压(即,第一节点电压vn1)与第二节点电压vn2之间的差(von-vpres)确定像素电流。升压电路bst可以在编程时段

①

中将从dac输出的用于感测的数据电压von发送到数据线14a,在感测时段

②

和采样时段

③

中使数据线14a浮置并且将读出线14b耦接至浮置数据线14a以通过读出线14b中的电压变化来改变数据线14a的电压。由于开关晶体管st1和st2在感测时段

②

内保持导通状态。由于开关晶体管st1和st2在感测时段

②

内保持导通状态,因此,在感测时段

②

中,第二节点电压vn2和读出线14b的电压相等地改变,并且第一节点电压vn1和数据线14a的电压相等地改变。换言之,如图6的部分(b)所示,由于第一节点电压vn1根据升压电路bst通过根据像素电流的第二节点电压vn2的变化而改变,因此驱动晶体管dt的栅极-源极电压(von-vpres)和像素电流可以保持恒定。

77.图6的部分(a)示出了当不存在升压电路bst时栅极-源极电压损耗

△

vgs。如下面的数学公式1所示,栅极-源极电压损耗

△

vgs由耦接至驱动晶体管dt的栅电极的寄生电容cdt引起。在数学公式1中,cst是存储电容器cst的电容,并且

△

vsio是由于寄生电容cdt引起的第二节点电压vn2的损耗。因为寄生电容cdt是根据面板设计规范确定的,所以无法人为控制寄生电容cdt。尽管可以考虑增加存储电容器cst的电容cst以使得栅极-源极电压损耗

△

vgs减小的方法,但是存储电容器cst的电容cst的增加导致显示面板的开口率减小,因此难以采用该方法。

78.[数学公式1]

[0079][0080]

如图6的部分(b)所示,可以通过升压电路bst使栅极-源极电压损耗

△

vgs最小化。可以由下面的数学公式2表示升压电路bst存在时栅极-源极电压损耗

△

vgs。在数学公式2中,cbst是升压电容器cbst的电容,并且cpin是出现在如图4所示的电压缓冲器buf的(+)输入端子处的等效寄生电容。

[0081]

[数学公式2]

[0082][0083]

从数学公式2可以清楚地确定,栅极-源极电压损耗

△

vgs可以随着cbst的增加而最小化。可以人为控制升压电容器cbst的电容cbst。由于升压电容器cbst的电容cbst与显示面板的开口率无关,因此升压电容器cbst的电容cbst的控制许可范围比存储电容器cst的电容cst的控制许可范围宽。

[0084]

返回参照图5,感测电路su的开关sw2在感测时段

②

也保持断开状态,因此此时读出线14b也浮置。因此,在感测时段

②

,读出线14b中的电压变化可以通过升压电路bst有效地反映在数据线14a的电位中。

[0085]

升压电路bst可以包括电压缓冲器buf、升压电容器cbst和开关sw1。

[0086]

电压缓冲器buf连接至数据线14a。电压缓冲器buf的(-)输入端子和输出端子彼此连接。升压电容器cbst的一个电极连接至读出线14b,并且其另一个电极连接至电压缓冲器

buf的(+)输入端子。开关sw1连接在电压缓冲器buf的(+)输入端子与dac之间。开关sw1仅在编程时段

①

中导通。数据线14a根据在感测时段

②

和采样时段

③

中保持断开状态的开关sw1而浮置。

[0087]

图7a是与图5的编程时段

①

对应的等效电路图,图7b是与图5的感测时段

②

对应的等效电路图,并且图7c是与图5的采样时段

③

对应的等效电路图。

[0088]

按照编程时段

①

、感测时段

②

和采样时段

③

的顺序执行感测操作。在感测操作期间,第一开关晶体管st1和第二开关晶体管st2根据处于导通水平的用于感测的栅极信号scan保持导通状态。

[0089]

参照图7a,开关sw1和开关sw2在编程时段

①

中接通。用于感测的导通水平数据电压von通过开关sw1、电压缓冲器buf、数据线14a和第一开关晶体管st1施加至像素的第一节点n1。此外,用于感测的参考电压vpres通过开关sw2、读出线14b和第二开关晶体管st2施加至像素的第二节点n2。因此,用于感测操作的驱动晶体管dt的栅极-源极电压vn1-vn2被设置。

[0090]

参照图7b,开关sw1和开关sw2在感测时段

②

中断开,因此数据线14a和读出线14b浮置。在此,与栅极-源极电压vn1-vn2对应的像素电流ip流过驱动晶体管dt。第二节点的电压vn2和读出线14b的电压根据像素电流ip从用于感测的参考电压vpres增加。读出线14b的电压增加通过升压电容cbst和电压缓冲器buf反映在数据线14a的电位中,并且数据线14a的电压也从用于感测的数据电压von增加。根据通过升压电容器cbst的耦合效应,数据线14a的电压增加梯度变得与读出线14b的电压增加梯度相同。

[0091]

参照图7c,采样信号sam在采样时段

③

中导通。采样电路sh根据采样信号sam对读出线14b的电压进行采样。

[0092]

图8是示出升压电路中包括的升压电容器形成在显示面板中的示例的图,并且图9是示出升压电路中包括的升压电容器形成在控制印刷电路板上的示例的图。

[0093]

参照图8,电压缓冲器buf和开关sw1可以位于源极驱动器集成电路sdic中,并且升压电容器cbst可以位于源极驱动器集成电路sdic外部的显示面板10中。因此,可以减小源极驱动器集成电路sdic的尺寸并且可以简化其配置。在显示面板10中,升压电容器cbst可以形成在像素pxl外部的区域中,例如在显示面板10的非显示区域中。因此,可以防止像素pxl的开口率由于升压电容器cbst而减小的副作用。

[0094]

参照图9,电压缓冲器buf和开关sw1可以位于源极驱动器集成电路sdic中,并且升压电容器cbst可以位于源极驱动器集成电路sdic外部的控制印刷电路板cpcb上。因此,可以减小源极驱动器集成电路sdic的尺寸并且可以简化其配置。定时控制器等可以安装在控制印刷电路板cpcb上。控制印刷电路板cpcb通过柔性印刷电路膜等电连接至源极驱动器集成电路sdic。

[0095]

图10是示出根据本公开内容的另一实施方式的像素电路、感测电路和升压电路的配置的示例的图,并且图11是用于驱动图10所示的电路的波形图。

[0096]

在图10和图11的实施方式中,除升压电路bst之外的部件与图4和图5的实施方式中的部件基本相同。因此,将省略对相同部件的描述。

[0097]

参照图10和图11,除了电压缓冲器buf、升压电容器cbst和开关sw1之外,升压电路bst还可以包括开关sw3和开关sw4。

[0098]

电压缓冲器buf、升压电容器cbst和开关sw1与参照图4和图5所描述的那些基本相同。

[0099]

开关sw3连接在升压电容器cbst的另一个电极与电压缓冲器buf的(+)输入端子之间。开关sw4连接在升压电容器cbst的另一个电极与数据线14a之间。

[0100]

开关sw3在编程时段

①

中保持断开状态,而在感测时段

②

和采样时段

③

中保持接通状态。此外,开关sw4仅在编程时段

①

中保持接通状态,而在感测时段

②

和采样时段

③

中保持断开状态。

[0101]

由于开关sw3在编程时段

①

中断开,因此用于感测的数据电压von可以更快地充载在数据线14b中。以此方式,图10和图11的实施方式在dac的充电能力低时有效。在感测时段

②

和采样时段

③

中,升压电容器cbst的另一个电极通过开关sw3和电压缓冲器buf连接至数据线14b。

[0102]

图12是示出与一个单位像素对应的四个升压电路共享一个单升压电容器的图。

[0103]

参照图12,与像素r、w、g和b对应的四个升压电路可以共享单个升压电容器cbst。在这种情况下,升压电路中包括的电压缓冲器buf可以通过mux开关smr、smw、smg和smb选择性地连接至升压电容器cbst。通过mux开关连接至升压电容器cbst的电压缓冲器对应于感测像素,而其他电压缓冲器对应于非感测像素。图12示出了多个升压电路共享单个升压电容器的示例。本公开内容的技术精神可以概括如下。

[0104]

像素可以包括连接至第一数据线和读出线的第一像素以及连接至第二数据线和读出线的第二像素。在这种情况下,升压电路可以包括连接至第一数据线的第一电压缓冲器buf、连接至第二数据线的第二电压缓冲器buf、具有连接至读出线的一个电极以及选择性地连接至第一电压缓冲器和第二电压缓冲器的另一个电极的升压电容器cbst、连接在升压电容器的另一个电极与第一电压缓冲器之间的第一mux开关、以及连接在升压电容器的另一个电极与第二电压缓冲器之间的第二mux开关。

[0105]

图13是示出了被配置成具有可控的总电容值的升压电容器单元的图。

[0106]

参照图13,升压电路可以包括:连接至数据线的电压缓冲器buf;连接在读出线14b与电压缓冲器buf之间并且具有根据控制信号ctr控制的总电容值的升压电容器电路;以及开关sw1,开关sw1连接在电压缓冲器buf与dac之间,在编程时段中接通,而在感测时段和采样时段中断开。

[0107]

升压电容器电路可以包括连接在读出线14b与电压缓冲器buf之间的多个升压电容器单元psc。每个升压电容器单元psc包括串联连接的升压电容器cbst和控制开关swx。由于根据控制信号ctr来确定要接通的控制开关的数目,因此可以如参考数学公式2所描述的那样人为地控制cbst。

[0108]

对于本领域技术人员明显的是,在不脱离本发明的精神或范围的情况下,可以对本发明进行各种修改和变化。因此,本发明旨在涵盖本发明的修改和变化,只要它们落入所附权利要求及其等同物的范围内。

[0109]

本公开内容具有以下优点。

[0110]

根据本公开内容的实施方式的电致发光显示装置包括用于在感测操作期间耦合数据线14a和读出线14b的升压电路bst。升压电路bst包括升压电容器cbst,并且在感测操作期间通过读出线14b中的电压变化来改变数据线14a的电压,以将驱动元件的栅极-源极

电压保持为设定水平。因此,本公开内容可以使与驱动元件的电子迁移率相关的感测性能和补偿性能最大化。

[0111]

通过本公开内容可以获得的效果不限于上述效果,并且本公开内容所属领域的技术人员可以根据以下描述明显地理解各种其他效果。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1