显示装置和包括其的多屏幕显示装置的制作方法

显示装置和包括其的多屏幕显示装置

1.相关申请的交叉引用

2.本技术主张于2020年12月31日递交的韩国专利申请第10-2020-0189730 号的权益,特此通过引用将其并入本文中,如同在本文全部阐述

技术领域

3.本公开涉及一种显示装置和包括该显示装置的多屏幕显示装置。

背景技术:

4.显示装置搭载于电视机(tv)、显示器、笔记本电脑、智能手机、平板个人电脑(pc)、电子平板、可穿戴设备、手表电话、便携式信息设备、导航设备、车辆控制等家用电器或电子设备中显示装置,用作显示图像的屏幕。

5.显示设备包括显示面板,该显示面板包括多个像素,每个像素包括连接到数据线和栅极线的薄膜晶体管(tft),向数据线提供数据电压的数据驱动电路,以及栅极驱动电路它向栅极线提供栅极信号。

6.近来,为了简化配置,在制造每个像素的tft的过程中,栅极驱动电路被嵌入到显示面板的非显示区域中,具有gip结构的显示设备正在被使用电路元件,降低制造成本,减小边框宽度。

7.具有gip结构的栅极驱动电路包括用于向多条栅极线提供栅极信号的多个级。所述级基于通过多条栅极移位时钟线和设置在显示面板中的栅极起始信号线提供的信号而独立地操作。

8.包括具有gip结构的栅极驱动电路的显示面板由于设置在非显示区域中的栅极驱动电路而包括边框区域。相关技术的显示装置需要边框或用于覆盖显示面板的边框区域的机构。

9.近来,通过将显示设备布置为格子型来实现大屏幕的多屏幕显示设备已经商业化。

10.然而,在相关技术的多屏幕显示设备中,由于边框区域或多个发光显示设备中的每一个的边框,在相邻的发光显示设备之间形成诸如接缝的边界部分。当在多屏发光显示装置的整个屏幕上显示一个图像时,边界部分可能会导致图像断开(或不连续)的感觉,因此,观看图像的观看者的沉浸感可能被减少。

技术实现要素:

11.因此,本公开旨在提供一种显示设备和包括该显示设备的多屏显示设备,其基本上消除了由于相关技术的限制和缺点造成的一个或多个问题。

12.本公开的实施方式旨在提供一种具有零边框宽度的显示装置和包括该显示装置的多屏显示装置。

13.本公开的实施方式旨在提供一种显示装置,其具有零边框宽度和最小化或减小的

像素驱动线的线电容偏差,以及包括该显示装置的多屏显示装置。

14.本公开的实施方式旨在提供一种显示装置和包括该显示装置的多屏显示装置,其最小化或减少由像素感测线之间的线电容偏差引起的感测数据的偏差。

15.本公开的另外的优点和特征将部分地在随后的描述中阐述并且部分地对于本领域普通技术人员在检查以下内容后将变得显而易见,或者可以从本公开的实践中获悉。

16.本公开的特征和其他优点可以通过书面描述及其权利要求以及附图中特别指出的结构来实现和获得。

17.为了实现这些和其他优点并根据本公开的目的,如本文所体现和广泛描述的,一种显示装置,包括:显示区域,所述显示区域被配置成包括在基板上方沿着第一方向和与所述第一方向相交的第二方向布置的多个像素;设置在所述显示区域处且耦连至所述多个像素的多个栅极线、多个数据线、和多个基准电压线;和栅极驱动电路,所述栅极驱动电路被配置成包括多个级电路单元,所述多个级电路单元设置在所述显示区域处且耦连至所述多个栅极线中的每一者,其中所述多个级电路单元包括:沿着所述第一方向分开地设置在所述多个像素之间的多个分支电路;设置在网络线形成部处的分支网络,所述网络线形成部限定(例如,定位)在沿着所述第一方向设置的所述多个像素中的每一者的一侧处,所述分支网络包括多个控制节点线和选择性地耦连至所述多个分支电路的多个网络线;和附加图案部,所述附加图案部设置在所述网络线形成部处以交叠设置在所述多个像素中的一些各自处的基准电压线。

18.在本公开的另一实施方式中,一种多屏幕显示装置包括:沿着第一方向和与所述第一方向相交的第二方向中的至少一个方向设置的多个显示装置,所述多个显示装置各自可包括显示装置,并且所述显示装置可包括:显示区域,所述显示区域被配置成包括在基板上方沿着第一方向和与所述第一方向相交的第二方向布置的多个像素;设置在所述显示区域处且耦连至所述多个像素的多个栅极线、多个数据线、和多个基准电压线;和栅极驱动电路,所述栅极驱动电路被配置成包括多个级电路单元,所述多个级电路单元设置在所述显示区域处且耦连至所述多个栅极线中的每一者,其中所述多个级电路单元包括:沿着所述第一方向分开地设置在所述多个像素之间的多个分支电路;设置在网络线形成部处的分支网络,所述网络线形成部限定(例如,定位)在沿着所述第一方向设置的所述多个像素中的每一者的一侧处,所述分支网络包括多个控制节点线和选择性地耦连至所述多个分支电路的多个网络线;和附加图案部,所述附加图案部设置在所述网络线信息部处以交叠设置在所述多个像素中的一些各自处的基准电压线。

19.本公开的一些实施方式可以提供一种具有归零边框宽度的显示装置和包括该显示装置的多屏显示装置。

20.本公开的一些实施方式可以提供一种显示装置,其中像素驱动线的线电容偏差被最小化或减小,以及包括该显示装置的多屏显示装置。

21.本公开的一些实施方式可以提供一种显示装置和包括该显示装置的多屏显示装置,其最小化或减少由基于像素的像素感测线之间的线电容偏差引起的基于子像素的感测数据的偏差。

22.本公开的一些实施方式可以提供一种显示设备和包括该显示设备的多屏显示设备,其在整个屏幕上显示一个图像时,没有间断感地显示图像。

23.应当理解,本公开的前述一般描述和以下详细描述都是示例和解释性的,并且旨在提供对所要求保护的本公开的进一步解释。

附图说明

24.随附的附图被包括以提供本公开的进一步理解,且被并入并组成本技术的一部分,随附的附图图解本公开的实施方式并与该描述一起用以解释本公开的原理。

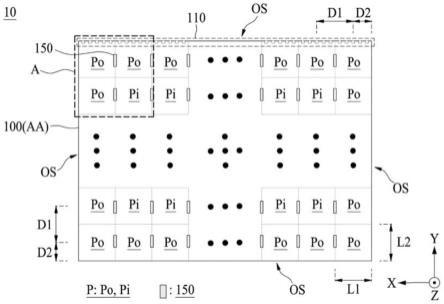

25.图1是图示根据本公开实施方式的显示装置的平面图。

26.图2a是图示图1中所示的根据本公开实施方式的一个像素的图示。

27.图2b是图示图1中所示的根据本公开另一实施方式的一个像素的图示。

28.图2c是图示图1中所示的根据本公开另一实施方式的一个像素的图示。

29.图3是图1中所示的区域“a”的放大视图。

30.图4是图示图1和图3中所示的一个像素的等效电路图。

31.图5是图示图1和图3中所示的栅极驱动电路的图示。

32.图6是图示根据本公开实施方式的显示装置的后表面的图示。

33.图7是图示根据本公开另一实施方式的显示装置的后表面的图示。

34.图8是图示图5中所示的第i级电路单元的电路图。

35.图9是图示图8中所示的节点控制电路、第一逆变器电路、第二逆变器电路、和第一感测控制电路的电路图。

36.图10是图示图8中所示的去噪电路、输出缓冲电路、和第二感测控制电路的电路图。

37.图11是图示图5、图8至图10中所示的分支网络和附加图案的图示。

38.图12a是沿着图11中所示的直线i-i’获取的截面图。

39.图12b是沿着图11中所示的直线ii-ii’获取的截面图。

40.图12c是沿着图11中所示的直线iii-iii’获取的截面图。

41.图13是图示图5、图8至图10中所示的根据另一实施方式的分支网络和附加图案的图示。

42.图14是图示图5、图8至图10中所示的根据另一实施方式的分支网络和附加图案的图示。

43.图15是图示图5、图8至图10中所示的根据另一实施方式的分支网络和附加图案的图示。

44.图16是图示根据本公开实施方式的多屏幕显示装置的图示。

45.图17是沿着图16中所示的直线iv-iv’获取的截面图。

具体实施方式

46.现在将详细参考本公开内容的实施方式,其示例可被图解于随附的附图中。在下述描述中,当确定有关本文件的已知功能或配置的详细描述不必要地模糊了发明理念的主旨时,将省略其详细描述。所描述的处理步骤和/或操作的进程是示例;然而,步骤和/或操作的顺序并不限于本文所阐述的顺序,可按本领域中所已知的进行改变,但必须以特定顺序发生的步骤和/或操作除外。在全文中类似的参考数字指定类似的元件。仅出于书写本说

明书的便利而选择了下述解释中使用的各个元件的名称,并且它们可因此与实际产品中使用的那些不同。

47.本公开内容的优点和特征、以及其实现方法将通过参照随附的附图描述的下式实施方式而清楚。然而,本公开内容可以不同形式体现,并且不应被解读为受限于本文中阐述的实施方式。相反,提供这些实施方式使得本公开内容将是彻底且完整的,并将本公开内容的范围传递给本领域技术人员。

48.用于描述本公开内容实施方式的附图中公开的形状、尺寸、比例、角度、和数量仅为示例,并因此,本公开内容的实施方式不限于图示的细节。在全文中类似的参考数字指类似的元件。在下述描述中,当确定相关的已知功能或配置的详细描述不必要地遮蔽本公开内容的重点时,将省略其详细描述。在使用了本说明书中描述的“包括”、“具有”、和“包含”的情况下,可添加有另一部件,除非使用了“仅~”。单数形式的术语可包括复数形式,除非另有说明。

49.在解释元件时,尽管没有明确的描述,但该元件也被解释为包括误差范围。

50.在描述位置关系中,例如,当两个部件之间的位置关系被描述为“上”、“上方”、“下”、“靠近”时,一个或多个其他部件可设置在这两个部件之间,除非使用了更多的限制性术语,诸如“仅”或“直接”。

51.在描述时间关系中,例如,当时间顺序被描述为,例如,“之后”、“随后”、“接下来”、和“之前”时,可包括不连续的情形,除非使用了更多的限制性术语,诸如“仅”、“立即”、或“直接”。

52.要理解的是,尽管术语“第一”、“第二”等可用于本文中以描述各种元件,但这些元件不应当受这些术语所限。这些术语仅用于将一个元件与其他区分。例如,第一元件可被称为第二元件,并且,类似地,第二元件可被称为第一元件,在不脱离本公开内容范围的情况下。

53.在描述本公开内容的元件中,可使用诸如第一、第二、a、b、(a)、(b) 等之类的术语。这些术语仅用于将相应的元件与其他元件区分,并且这些相应的元件在其本质、顺序、优先级方面不受这些术语所限。要理解的是,当一个元件或层被称为在另一元件或层“上”或“耦接”至另一元件或层时,其可直接在该其他元件或层上或直接耦接至该其他元件或层,或者可存在中间元件或层。此外,应当理解的是,当一个元件设置在另一元件上或下时,这可表示这些元件设置成彼此直接接触的情形,但也可表示这些元件在没有彼此直接接触的情况下进行设置的情形。

54.术语“至少一个”应当被理解为包括相关的列出的元件中的一者或多者的任一和所有组合。例如,“第一元件、第二元件、和第三元件中的至少一者”的含义表示从第一元件、第二元件、和第三元件中的两者或更多者提出的所有元件的组合以及第一元件、第二元件、或第三元件。

55.如本文中所用的术语“围绕”包括至少部分围绕以及完全围绕相关元件中的一者或多者。类似地,如本文中所用的术语“覆盖”包括至少部分覆盖以及完全覆盖相关元件中的一者或多者。

56.本公开内容的各种实施方式的特征可部分或全部地彼此耦连或组合,并且可如本领域技术人员可充分理解的一样彼此各种互相操作并在技术上驱动。本公开内容的实施方

式可彼此独立地实施,或者可以共同依赖的关系一起实施。

57.在下文中,将参照随附的附图详细描述本内容的实施方式。在将参考数字添加给各附图的元件中,尽管在其他附图中示出了相同的元件,但类似的参考数字可指类似的元件。此外,出于描述的便利,随附的附图中所示的每个元件的比例尺不同于真实的比例尺,并因此,并未受限于附图中所示的比例尺。

58.图1是图解根据本公开内容实施方式的显示装置的平面图。

59.参照图1,根据本公开实施方式的显示装置(或显示面板)10可以包括第一基板100,第一基板100包括显示区域aa、第一基板100的显示区域aa 中的多个像素p、第一基板100焊盘部件110和显示区域aa内的栅极驱动电路150。第一基板100可以被称为第一基板、基底基板或像素阵列基板。例如,第一基板100可以是玻璃基板,或者可以是可弯曲或柔性的薄玻璃基板或塑料基板。第一基板100的显示区域aa可以是显示图像的区域并且可以被称为有源部分、有源区域、显示部分或显示部分。显示区aa的尺寸可以与第一基板100(或显示装置或显示面板)相同或基本相同。例如,显示区域aa 的尺寸可以与第一基板100的第一表面的总尺寸相同。因此,显示区域aa可以实施(或设置)在第一基板的整个前表面上。参照图100,因此,第一基板 100可以不包括沿着第一表面的周缘部分(或边缘部分)设置以包围所有显示区域aa的不透明非显示区域。因此,显示设备的整个前表面可以实现显示区域aa。

60.显示区aa的端部(或最外部分)可与第一基板100的外表面os重叠或实质上对准。例如,相对于显示装置的厚度方向z,侧表面显示区aa的(或端线)可以基本上对准从第一基板100的外表面os垂直延伸的垂直延长线。显示区aa的侧表面可以不被单独的机构包围并且可能只与环境空气相邻。例如,显示区域aa的所有侧表面可以被提供为直接接触空气而不被单独的机构包围的结构。因此,与显示区域aa的端部对应的第一基板100的外表面os可以仅被空气(或邻接的环境空气)包围,因此,根据本公开的实施方式的显示装置可以具有空气边框结构或非边框结构(或归零边框),其中显示区域aa 的端部(或侧表面)被空气包围而不是不透明的非显示区域。

61.多个像素p可排列(或设置)于第一基板100的显示区aa以沿第一方向x 与第二方向y具有第一间隔d1。例如,第一方向x可横穿(或与第二方向y 重叠或交叉)。第一方向x可以是第一基板100或显示装置的宽度方向、水平方向或第一长度方向(例如,宽度方向的长度方向)。

62.多个像素p中的每一个可以实现在第一基板100的显示区域aa上限定 (例如,定位)的多个像素区域上。多个像素p中的每一个可以具有平行于第一长度l1的第一长度l1。方向x和平行于第二方向y的第二长度l2。第一长度l1可以与第二长度l2或第一间隔d1相同。第一长度l1和第二长度l2 可以与第一间隔d1相同。因此,多个像素(或像素区域)p可以全部具有相同的尺寸。

63.在制造工艺的误差范围内,沿第一方向x和第二方向y彼此相邻的两个像素p可以具有相同的第一间隔d1。第一间隔d1可为相邻的两个像素p之间的间距(或像素间距)。例如,像素p的第一长度l1或第二长度l2可称为像素间距。例如,第一间隔d1可以是两个相邻像素p的中心部分之间的距离(或长度)。例如,第一间隔(或像素间距)d1可以是两个相邻像素p的中心部分之间的最短距离(或最短长度)。

64.根据实施方式的多个像素p中的每一个可以包括电路层,该电路层包括在第一基

板100的像素区域中实现的像素电路,以及设置在电路层处并耦合到像素电路的发光器件层。像素电路响应于从设置在像素区域中的像素驱动线提供的数据信号和扫描信号,输出与数据信号对应的数据电流。发光器件层可以包括通过从像素电路提供的数据电流发光的发光层。下面将描述像素驱动线、像素电路和发光器件层。

65.多个像素p可以被划分(或分类)为最外像素po和内像素(或内像素) pi。

66.最外面的像素po可以是多个像素p中最靠近第一基板100的外表面os 设置的像素。

67.每个最外面的像素po的中心部分与第一基板100的外表面os之间的第二间隔d2可以是第一间隔d1的一半或更小。例如,第二间隔d2可以是最外像素po的中心部分与第一基板100的外表面os之间的距离(或长度)。例如,第二间隔d2可以是最短距离(或最外像素po的中心部分与第一基板 100的外表面os之间的最短长度)。

68.当第二间距d2大于第一间距d1的一半时,第一基板100的尺寸可以比显示区域aa大第一间距d1的一半与第二间距d2之间的差面积,因此,最外像素po的端部与第一基板100的外表面os之间的区域可以被配置为围绕所有显示区域aa的非显示区域。例如,当第二间隔d2大于第一间隔d1的一半时,第一基板100可能必须包括基于围绕所有显示区域aa的非显示区域的边框区域。另一方面,当第二间距d2等于或小于第一间距d1的一半时,每个最外面的像素po的端部可以与第一基板100的外表面os对齐(或设置),或者端部可以与第一基板100的外表面os对齐(或设置)显示区域aa的一部分可以与第一基板100的外表面os对齐(或设置),因此,显示区域aa 可以实施(或设置)在第一基板100的整个前表面上。

69.内部像素pi可以是除了多个像素p中的最外面的像素po之外的像素,或者可以是被多个像素p中的最外面的像素po围绕的像素。内部像素(或第二像素)pi可以被实现为具有与最外面的像素(或第一像素)po不同的配置或结构。

70.第一焊盘部110可以是第一焊盘部或前焊盘部。第一焊盘部110可以包括多个第一焊盘以从驱动电路部接收数据信号、栅极控制信号、像素驱动功率、参考电压和像素公共电压等。

71.第一焊盘部110可以被包括在平行于第一方向x设置在第一基板100的第一表面的第一周缘部分处的最外侧像素po内。即,设置在第一衬底100的第一表面的第一周缘部分处的最外侧像素po内第一基板100可以包括多个第一焊盘中的至少一个。因此,多个第一焊盘可以设置或包括在显示区域aa内,因此,基于第一焊盘部件110的非显示区域(或边框区域)可以不形成或者可以不在第一焊盘上。基板100。因此,最外面的像素(或第一像素)po可以包括第一焊盘部件110,并且因此,可以被实现为具有与内部像素(或第二像素) pi不同的配置或结构,不包括没有第一焊盘部110。

72.例如,当第一焊盘部110没有设置在最外面的像素po内并且设置在最外面的像素po和第一基板100的外表面os之间时,第一基板100可以包括非显示区域(或(非显示部分)对应于设置第一焊盘部件110的区域,并且由于非显示区域,最外面的像素po和第一基板100的外表面os之间的第二间隔d2可以大于第一间隔d1的一半,可以不将所有的第一基板100实现为显示区域aa,并且可能需要用于覆盖非显示区域的单独的边框(或单独的结构)。另一方面,根据本公开的实施方式的第一焊盘部件110可以设置在最外面的像素po和第一基板100的外表面os之间以被包括在最外面的像素po内,因此,非-基于第一焊盘部件110的

显示区域(或边框区域)可以不形成或者可以不在最外面的像素po和第一基板100的外表面os之间。

73.根据实施方式的第一焊盘部110可以包括多个像素驱动电源焊盘、多个数据焊盘、多个参考电压焊盘和多个像素公共电压焊盘,但是本公开的实施方式不限于到那里。

74.栅极驱动电路150可以设置在显示区aa中以向设置在第一基板100上的像素p提供扫描信号(或栅极信号)。栅极驱动电路150可以同时向设置的像素 p提供扫描信号在平行于第一方向x的水平线上。例如,栅极驱动电路150 可以通过至少一条栅极线向布置在一条水平线上的像素p提供至少一个扫描信号。

75.根据实施方式的栅极驱动电路150可以用包括多个级电路单元的移位寄存器来实现。即,根据本公开实施方式的显示装置可以包括移位寄存器,其设置在第一基板100的显示区域aa中以向像素p提供扫描信号。

76.多个级中的每一个可以包括在第一方向x上在第一基板100的每条水平线中彼此间隔开布置的多个分支电路。多个分支电路中的每一个可以包括至少一个薄膜晶体管(tft)(或支路tft)可以设置在第一方向x的一条水平线上的一个或多个像素p(或像素区域)的两个相邻像素之间。多个级电路单元中的每一个可以产生一个基于通过在显示区域aa中的多个像素p之间彼此隔开布置的栅极控制线提供的栅极控制信号,通过驱动多个分支电路来提供扫描信号,并且可以将扫描信号提供给排列成一排的像素p。对应的水平线。

77.图2a是图示图1中所示的根据本公开实施方式的一个像素的图示,图2b 是图示图1中所示的根据本公开另一实施方式的一个像素的图示,图2c是图示图1中所示的根据本公开另一实施方式的一个像素的图示。

78.图2a是图示图1中所示的根据本公开实施方式的一个像素的图示,图2b 是图示图1中所示的根据本公开另一实施方式的一个像素的图示,图2c是图示图1中所示的根据本公开另一实施方式的一个像素的图示。

79.参照图1和图2a,根据本公开内容实施方式的一个像素(或单元像素)p 可包括第一至第四子像素sp1至sp4。

80.第一子像素sp1可设置在像素区域pa的第一子像素区域中,第二子像素 sp2可设置在像素区域pa的第二子像素区域中,第三子像素sp3可设置在像素区域pa的第三子像素区域中,并且第四子像素sp4可设置像素区域pa的第四子像素区域中。

81.根据实施方式的第一至第四子像素sp1至sp4可以2

×

2形式或四方 (quad)结构设置。第一至第四子像素sp1至sp4可各自包括多个发光区域 ea1至ea4和多个电路区域ca1至ca4。例如,发光区域ea1至ea4可被称为开口区域、开口部、或发光部。

82.第一至第四子像素sp1至sp4各自的发光区域ea1至ea4可具有均匀的四方结构以具有尺寸相同(或面积相同)的正方形状。根据实施方式,具有均匀四方结构的发光区域ea1至ea4各自可设置成接近相应子像素区域内的像素p的中心部cp以具有小于像素p的四个相等划分区域中的每一个的尺寸,或者可设置成集中在像素p的中心部cp处。根据另一实施方式,具有均匀四方结构的发光区域ea1至ea4各自可设置在相应子像素区域的中心部cp处以具有小于像素p的四个相等划分区域中的每一个的尺寸。

83.参照图1和图2b,根据另一实施方式的第一至第四子像素sp1至sp4各自可具有尺寸不同的非均匀的四方结构。例如,第一至第四子像素sp1至sp4 各自的发光区域ea1至ea4

各自可具有尺寸不同的非均匀的四方结构。

84.具有非均匀的四方结构的第一至第四子像素sp1至sp4各自的尺寸可基于分辨率、发光效率、或图像质量进行设定。根据另一实施方式,当发光区域 ea1至ea4具有非均匀的四方结构时,在第一至第四子像素sp1至sp4的发光区域ea1至ea4之中,第四子像素sp4的发光区域ea4可具有最小的尺寸,而第三子像素sp3的发光区域ea3可具有最大的尺寸。例如,具有非均匀的四方结构的第一至第四子像素sp1至sp4各自的发光区域ea1至ea4各自可设置成集中在像素p的中心部cp周围(或附近)。

85.参照图1和图2c,根据另一实施方式的第一至第四子像素sp1至sp4各自可具有1

×

4形式或均匀的条带结构。例如,第一至第四子像素sp1至sp4 的发光区域ea1至ea4可具有1

×

4形式或均匀的条带结构。

86.具有均匀条带结构的第一至第四子像素sp1至sp4的发光区域ea1至 ea4可各自具有包括平行于第一方向x的短边和平行于第二方向y的长边的矩形形状。

87.根据实施方式,具有均匀条带结构的发光区域ea1至ea4各自可设置成接近相应子像素区域内的像素p的中心部cp以具有小于像素p的四个相等划分区域中的每一个的尺寸,或者可设置成集中在像素p的中心部。

88.根据另一实施方式,具有均匀条带结构的发光区域ea1至ea4各自可设置在相应子像素区域的中心部cp处以具有小于像素p的四个相等划分区域中的每一个的尺寸。

89.根据另一实施方式,具有均匀条带结构的发光区域ea1至ea4各自可设置在整个相应子像素区域处以具有与像素p的四个相等划分区域中的每一个相同的尺寸。

90.或者,第一至第四子像素sp1至sp4各自的发光区域ea1至ea4各自可具有尺寸不同的非均匀的条带结构。根据实施方式,当发光区域ea1至ea4 具有非均匀的条带结构时,在第一至第四子像素sp1至sp4的发光区域ea1 至ea4之中,第四子像素sp4的发光区域ea4可具有最小的尺寸,而第三子像素sp3的发光区域ea3可具有最大的尺寸,但本公开内容的实施方式不限于此。

91.参照图2a和图2b,第一至第四子像素sp1至sp4各自的电路区域ca1 至ca4可设置在发光区域ea1至ea4的相应发光区域周围(或附近)。电路区域ca1至ca4各自可包括像素电路和像素驱动线以使第一至第四子像素 sp1至sp4的相应子像素发光。例如,电路区域ca1至ca4可被称为非发光区域、非开口区域、非发光部、非开口部、或周缘部。

92.或者,为了随着像素p的分辨率变得更高而增加对应发光区域ea1至ea4 尺寸的子像素sp1至sp4的孔径比或者降低像素节距d1,第一至第四子像素 sp1至sp4的发光区域ea1至ea4可延伸至电路区域ca1至ca4以与电路区域ca1至ca4中的一些或全部重叠。例如,由于第一至第四子像素sp1至 sp4的发光区域ea1至ea4具有顶部发光结构,因而发光区域ea1至ea4 各自可布置成与相应的电路区域ca1至ca4重叠。在这种情况下,发光区域 ea1至ea4各自可具有大于或等于相应电路区域ca1至ca4的尺寸。

93.在图2a至图2c中,第一子像素sp1可被实现成发出第一颜色的光,第二子像素sp2可被实现成发出第二颜色的光,第三子像素sp3可被实现成发出第三颜色的光,第四子像素sp4可被实现成发出第四颜色的光。例如,第一至第四颜色各自可不同。作为实施方式,第一颜色可以是红色,第二颜色可以是蓝色,第三颜色可以是白色,第四颜色可以是绿色。作为另一实施方式,第一至第四颜色中的一些可相同。例如,第一颜色可以是红色,第二颜色可

以是第一绿色,第三颜色可以是第二绿色,第四颜色可以是蓝色。

94.可选地,可省略被实现成从具有均匀条带结构或非均匀条带结构的第一至第四子像素sp1至sp4发出白色光的白色子像素。

95.图3是图1中所示的区域“a”的放大视图,图4是图解图1和图3中所示的一个子像素的等效电路图。

96.参照图1、图3、和图4,根据本公开内容实施方式的第一基板100可包括像素驱动功率线dl、gl、pl、cvl、rl、和gcl、多个像素p、公共电极ce、多个公共电极连接部cecp和第一焊盘部件110。

97.像素驱动功率线dl、gl、pl、cvl、rl、和gcl可包括多个数据线 dl、多个栅极线gl、多个像素驱动功率线pl、多个像素公共电压线cvl、多个基准电压线rl、和栅极控制线gcl。

98.在图中,在提供参考编号或字母之后在括号中提供另一个参考编号或字母的情况下,这意味着括号中的数字和/或字母是项目的一般类别或组以及第一个数字在它之前是组内该项目的具体示例。例如,图3中pg1(pg)的指示表明第一焊盘组pg1是宽焊盘组pg内的特定项。类似地,在图5中,符号150m(150) 表示电路1501、1502、...1511、1512中的每一个是驱动电路150的广泛组中的驱动电路。相似的含义适用于图中的相似符号,并且这些被提供作为示例以说明含义。

99.以某种类似的方式,特定图形下方的图例提供了一个通用组,后跟一个冒号,然后是该组中的项目列表,如图所示。例如,图1下方的符号p:po、pi表示p是像素的一般组,po和pi是该像素组p中的特定项。此外,在图3下方,符号dl:dlo和dle和gl:glo和gle表示这些中的每一个分别是数据线dl和栅极线gl的通用组内的特定项目。

100.多个数据线dl可在第二方向y上延伸得很长,并且可沿着第一方向x 设置成彼此间隔开第一基板100的显示区域aa中的预定或选定间隔。例如,在多个数据线dl中,奇数的数据线dlo可设置在沿着第二方向y布置在第一基板100处的多个像素区域pa各自的第一周缘部处,而偶数的数据线dle 可设置在沿着第二方向y布置在第一基板100处的多个像素区域pa各自的第二周缘部处,但本公开内容的实施方式不限于此。

101.多个栅极线gl可在第一方向x上延伸得很长,并且可沿着第二方向y 设置成彼此间隔开第一基板100的显示区域aa中的预定或选定间隔。例如,多个栅极线gl中奇数的栅极线glo可设置在沿着第一方向x布置在第一基板100处的多个像素区域pa各自的第三周缘部处。多个栅极线gl中偶数的栅极线gle可设置在沿着第一方向x布置在第一基板100处的多个像素区域 pa各自的第四周缘部处,但本公开内容的实施方式不限于此。

102.多个像素驱动功率线pl可在第二方向y上延伸得很长,并且可沿着第一方向x设置成彼此间隔开第一基板100的显示区域aa中的预定或选定间隔。例如,在多个像素驱动功率线pl中,奇数的像素驱动功率线pl可相对于第一方向x设置在奇数的显示区域pa的第一周缘部处,而偶数的像素驱动功率线pl可相对于第一方向x设置在偶数的像素区域pa的第二周缘部处,但本公开内容的实施方式不限于此。

103.多个像素驱动功率线pl中的两个相邻像素驱动功率线pl可耦连至在第二方向y上布置的每个子像素pa中设置的多个功率共享线psl。例如,多个像素驱动功率线pl可通过多个功率共享线psl电连接至彼此,并因此,可具有梯状结构或网栅结构。多个像素驱动功率线pl可具有梯状结构或网栅结构,并因此,可防止、降低或最小化)由多个像素驱动功率线

pl各自的线电阻导致的像素驱动功率的电压降(ir降)。相应地,根据本公开内容实施方式的显示装置可防止、降低、或最小化由供应至布置在显示区域aa处的每个像素 p的像素驱动功率的偏差导致的图像质量退化。

104.多个功率共享线psl各自可从平行于第一方向x的相邻像素驱动功率线 pl分支,并且可设置在每个像素区域pa的中间区域中,但本公开内容的实施方式不限于此。

105.多个像素公共电压线cvl可在第二方向y上延伸得很长,并且可沿着第一方向x设置成彼此间隔开第一基板100的显示区域aa中的预定或选定间隔。例如,多个像素公共电压线cvl各自可相对于第一方向x设置在偶数的像素区域pa的第一周缘部处。

106.多个基准电压线rl可在第二方向y上延伸得很长,并且可在第一方向x 上设置成彼此间隔开第一基板100的显示区域aa中的预定或选定间隔。多个基准电压线rl各自可设置于在第二方向y上布置的每个像素区域pa的中心区域中。

107.多个基准电压线rl各自可由每个像素区域pa中的第一方向x上的两个相邻子像素((sp1,sp2)(sp3,sp4))共享。为此,多个基准电压线rl 各自可包括基准分支线rdl。基准分支线rdl可分支(突出)至每个像素区域pa中的第一方向x上的两个相邻子像素((sp1,sp2)(sp3,sp4)),并且可电耦连至该两个相邻子像素((sp1,sp2)(sp3,sp4))。

108.多个栅极控制线gcl可在第二方向y上延伸得很长,并且可在第一方向 x上设置成彼此间隔开第一基板100的显示区域aa中的预定或选定间隔。例如,多个栅极控制线gcl各自可相对于第一方向x设置在多个像素区域pa 之间处或者两个相邻像素区域pa之间的边界区域处。

109.多个像素p各自可包括至少三个子像素。例如,多个像素p各自可包括第一至第四子像素sp1至sp4。

110.第一至第四子像素sp1至sp4各自可包括像素电路pc和发光器件层。

111.根据实施方式的像素电路pc可设置在像素区域pa的电路区域中,并且可耦连至与之相邻的栅极线glo或gle、与之相邻的数据线dlo或dle、和像素驱动功率线pl。例如,设置在第一子像素sp1中的像素电路pc可耦连至奇数的数据线dlo和奇数的栅极线glo,设置在第二子像素sp2中的像素电路pc可耦连至偶数的数据线dle和技术的栅极线glo,设置在第三子像素 sp3中的像素电路pc可耦连至奇数的数据线dlo和偶数的栅极线gle,设置在第四子像素sp4中的像素电路pc可耦连至偶数的数据线dle和偶数的栅极线gle。

112.第一至第四子像素sp1至sp4各自的像素电路pc可响应于从相应栅极线 glo或gle供应的扫描信号采样从相应数据线dlo或dle供应的数据信号,并且可基于采样的数据信号控制从像素驱动功率线pl流动至发光器件层的电流。

113.根据实施方式的像素电路pc可包括第一开关薄膜晶体管tsw1、第二开关薄膜晶体管tsw2、驱动薄膜晶体管tdr、和存储电容器cst,但本公开内容的实施方式不限于此。在下述描述中,薄膜晶体管可被称为tft。

114.第一开关twt tsw1可包括耦连至相应栅极线gl(glo或gle)的栅极、耦连至相应数据线dl(dlo或dle)的第一源极/漏极、和耦连至驱动tft tdr 的栅极节点n1的第二源极/漏极。第一开关tft tsw1可由通过相应栅极线gl (glo或gle)供应的扫描信号开启,并且可将通过相应数据线dl(dlo或 dle)供应的数据信号传输至驱动tft tdr的栅极n1。

115.第二开关twt tsw2可包括耦连至相应栅极线gl(glo或gle)的栅极、耦连至驱动

tft tdr的源极节点n2的第一源极/漏极、和耦连至相应基准电压线rl的第二源极/漏极。第二开关tft tsw2可由通过相应栅极线gl(glo 或gle)供应的扫描信号开启,并且可将通过相应基准线rl供应的基准电压传输至驱动tft tdr的源极节点n2。例如,第二开关tft tsw2可与第一开关 tft tsw1同时开启。

116.存储电容器cst可形成在驱动tft tdr的栅极节点n1和源极节点n2之间。根据实施方式的存储电容器cst可包括耦连至驱动tft tdr的栅极节点n1的第一电容器、耦连至驱动tft tdr的源极节点n2的第二电容器、和形成在第一电容器电极和第二电容器电极之间的重叠区域中的介电层。存储电容器cst 可用驱动tft tdr的栅极节点n1和源极节点n2之间的压差进行充电,然后可基于其充电的电压开启或关闭驱动tft tdr。

117.驱动tft tdr可包括共同耦连至第一开关tft tsw1的第二源极/漏极和存储电容器cst的第一电容器电极的栅极(或栅极节点n1)、共同耦连至第二开关tft tsw2的第一源极/漏极、存储电容器cst的第二电容器电极、发光器件层的像素电极pe的第一源极/漏极(或源极节点n2)、和耦连至相应像素驱动功率线pl的第二源极/漏极(或漏极节点)。驱动tft tdr可基于存储电容器cst的电压而开启,并且可控制从像素驱动功率线pl流动至发光器件层的电流量。

118.根据另一实施方式的第一至第四子像素sp1至sp4中的每一个的像素电路pc可以通过半导体制造工艺实现为像素驱动芯片,设置在相应像素区域pa 的电路区域ca中,并连接至栅极与其相邻的线glo或gle,与其相邻的数据线dlo或dle,以及像素驱动电源线pl。例如,像素驱动芯片可以是微芯片或最小单位对应的芯片组,可以是具有两个或多个晶体管和一个或多个电容器的精细尺寸的半导体封装器件。像素驱动芯片可以响应于通过相应的栅极线 glo或gle提供的扫描信号对通过相应的数据线dlo或dle提供的数据信号进行采样,并且可以控制从像素驱动电源线pl流向发光器件层的电流基于采样的数据信号。

119.发光器件层可以设置在像素区pa的发射区ea中并且电耦合到像素电路 pc。

120.根据本公开实施方式的发光器件层可以包括电耦合到像素电路pc的像素电极pe、电耦合到像素公共电压线cvl的公共电极ce、以及插入在两者之间的自发光器件ed。像素电极pe和公共电极ce。

121.像素电极pe可以被称为自发光器件ed的阳极电极、反射电极、下电极、阳极或第一电极。

122.像素电极pe可以与多个子像素sp中的每一个的发射区ea交叠。像素电极pe可以被图案化为岛状并且设置在每个子像素sp中,并且可以电耦合到相应像素电路pc的驱动tft tdr的第一源/漏电极。像素电极pe的一侧可以延伸到驱动tft tdr的第一源/漏电极上并且可以通过设置在驱动tft tdr上方的平坦化层处的接触孔电耦合到驱动tft tdr的第一源/漏电极。tft tdr。

123.像素电极pe可以包括功函数低且反射效率好的金属材料。例如,像素电极pe可以形成为izo/moti/ito或者ito/moti/ito的三层结构,或者可以形成为ito/cu/moti/ito的四层结构,或者可以形成ito/ag/ito/moti/ito的五层结构。

124.自发光器件ed可以设置在像素电极pe之上并且可以直接接触像素电极 pe。自发光器件ed可以是公共层或公共器件层,其共同形成在多个子像素 sp中的每一个中以便不被子像素sp单元区分。自发光器件ed可以对在像素电极pe和公共电极ce之间流动的电流起

反应以发射白光或蓝光。根据实施方式的自发光器件ed可以包括有机发光器件或无机发光器件,或者可以包括有机发光器件(或无机发光器件)和量子点状发光装置。例如:根据另一实施方式的自发光器件ed可以包括有机发光层或无机发光层,或者可以包括有机发光层(或无机发光层)的堆叠或组合结构以及量子点发光层。

125.根据实施方式的有机发光器件可以包括两个或更多个用于发射白光的发光材料层(或发光部分)。例如,有机发光器件可以包括第一发光材料层和第二发光材料层,用于基于第一光和第二光的组合发射白光。这里,第一发光材料层可以包括蓝色发光材料、绿色发光材料、红色发光材料、黄色发光材料和黄绿色发光材料中的至少一种。第二发光材料层可以包括蓝色发光材料、绿色发光材料、红色发光材料、黄色发光材料和黄绿色发光材料中的至少一种,用于发射第二光,与第一束光结合产生白光。

126.根据实施方式的有机发光器件还可以包括一个或多个用于提高发射效率和/或寿命的功能层。例如,功能层可以设置在发光材料层的上方和/或下方。

127.根据实施方式的无机发光器件可以包括半导体发光二极管、微型发光二极管或量子点发光二极管。例如,当发光器件ed为无机发光器件时,发光器件 ed可以具有1μm或100μm的尺度,但本公开的实施方式不限于此。

128.公共电极ce可以设置在第一基板100的显示区域aa上方并且可以电耦合到多个像素p中的每一个的自发光器件ed。例如,公共电极ce可以设置在剩余的除了第一基板100的第一焊盘部分110之外,第一基板100的显示区域aa。例如,公共电极ce可以设置在除了第一基板100的周缘部分之外的第一基板100的剩余显示区域aa上方。

129.公共电极ce可以被称为自发光器件ed的阴极电极、透明电极、上电极、阴极或第二电极。公共电极ce可以形成在自发射器件ed之上并且可以直接接触自发射器件ed或者可以电且直接地接触自发射器件ed。公共电极ce 可以包括透射从自发光器件ed发射的光的透明导电材料。根据本公开实施方式的公共电极ce可以形成为单层结构或多层结构,其包括石墨烯和功函数较高的透明导电材料中的至少一种材料。例如,公共电极ce可以包括诸如ito 或izo的金属氧化物,或者可以包括诸如zno:al或sno2:sb的氧化物和金属的组合。

130.多个公共电极连接部cecp各自可设置在分别与多个像素公共电压线 cvl重叠的多个像素p之间,并且可将公共电极ce电耦连至多个像素公共电压线cvl中的每一者。相对于第二方向y,根据本公开内容实施方式的多个公共电极连接部cecp各自可电耦连至多个像素p之间的部分处(或多个像素 p之间的边界处)的多个像素公共电压线cvl中的每一者,并且可电偶联至公共电极ce的一部分,并因此,可将公共电极ce电偶联至多个像素公共电压线cvl中的每一者。例如,公共电极ce可通过对应底切结构的侧触结构而耦连至多个公共电极连接部cecp中的每一者。

131.多个公共电极连接部cecp各自可设置在多个像素p之间的部分以将公共电极ce电耦连至多个像素公共电压线cvl中的每一者,并因此,可防止、降低、或最小化由公共电极ce的表面电阻导致的像素公共电压的电压降(ir 降)。相应地,根据本公开内容实施方式的显示装置可防止、降低、或最小化由供应至布置在显示区域aa中的每个像素p的像素公共电压的偏差导致的图像质量退化。

132.根据本公开内容的实施方式,多个公共电极连接部cecp各自可与具有至少两层结构的像素电极pe一起形成以便电连接至多个像素公共电压线cvl 中的每一者。多个公共电

极连接部cecp各自可通过具有“(”状截面结构或“〈”状截面结构的侧触结构而耦连至公共电极ce。例如,当多个公共电极连接部cecp各自由第一和第二金属层形成时,多个公共电极连接部cecp各自可包括对应底切结构的侧触结构或者通过第一金属层和第二金属层之间的蚀刻速度差而在第一金属层的侧面上形成的锥形结构。例如,当多个公共电极连接部cecp各自由第一至第三金属层形成时,多个公共电极连接部cecp各自可包括对应底切结构的侧触结构或者通过第一和第二金属层之间的蚀刻速度差而在第一金属层和/或第二金属层的侧面处形成的锥形结构。

133.第一焊盘部件110可设置在平行于第一方向x的基板100的第一表面的第一周缘部处。第一焊盘部件110可设置在第一基板100的第一周缘部处设置的每个最外像素区域pao的第三周缘部处。相对于第二方向y,第一焊盘部件110的端部可与每个最外像素区域pao的端部重叠或对齐。因此,第一焊盘部件110可被包括(或设置)在设置于第一基板100的第一周缘部处的每个最外像素区域pao中,并因此,基于第一焊盘部件110的非显示区域(或边框区域)可并未形成或者可未在第一基板100中。

134.第一焊盘部件110可包括在第一基板100的第一周缘部处沿着第一方向x 设置成彼此平行的多个第一焊盘。多个第一焊盘可被分(或分类)为第一数据焊盘dp、第一栅极焊盘gp、第一像素驱动功率焊盘ppp、第一基准电压焊盘 rvp、和第一像素公共电压焊盘cvp。

135.第一数据焊盘dp各自可单独地(或一对一关系)耦连至设置在第一基板 100处的多个数据线dlo和dle各自的一侧。

136.第一栅焊盘gp各自可单独地(或一对一关系)耦连至设置在第一基板100 处的每个栅极控制线gcl的一侧。根据实施方式的第一栅极焊盘gp可被分 (或分类)为第一起始信号焊盘、多个第一移位时钟焊盘、多个第一进位时钟焊盘、至少一个第一栅极驱动功率焊盘、和至少一个第一栅极公共功率焊盘。

137.第一像素驱动电压焊盘ppp各自可单独地(或一对一关系)耦连至设置在第一基板100处的多个像素驱动功率线pl各自的一侧端。第一基准电压焊盘rvp各自可单独地(或一对一关系)耦连至设置在第一基板100处的多个基准电压线rl各自的一侧端。第一素公共电压焊盘cvp各自可单独地(或一对一关系)耦连至设置在基板100处的多个像素公共电压线cvl各自的一侧端。

138.根据实施方式的第一焊盘部件110可包括多个焊盘组pg,其沿着第一方向x以第一像素驱动功率焊盘ppp、第一数据焊盘dp、第一基准电压焊盘 rvp、第一数据焊盘dp、第一栅极焊盘gp、第一像素公共电压焊盘cvp、第一数据焊盘dp、第一基准电压焊盘rvp、第一数据焊盘dp、和第一像素驱动功率焊盘ppp的顺序进行布置。多个焊盘组pg各自可耦连至沿着第一方向x设置的两个相邻像素p。例如,多个焊盘组pg可包括第一焊盘组pg1 和第二焊盘组pg2,第一焊盘组pg1包括沿着第一方向x连续设置在奇数的像素区域pa中的第一像素驱动功率焊盘ppp、第一数据焊盘dp、第一基准电压焊盘rvp、第一数据焊盘dp、和第一栅极焊盘gp,第二焊盘组pg2包括沿着第一方向x设置在偶数的像素区域pa中的第一像素公共电压焊盘 cvp、第一数据焊盘dp、第一基准电压焊盘rvp、第一数据焊盘dp、和第一像素驱动功率焊盘ppp。

139.根据本公开内容实施方式的第一基板100可进一步包括多个次级电压线 svl和多个次级线连接部slcp。例如,次级电压线可被称为额外电压线或辅助电压线、或类似者。

140.多个次级电压线svl各自可沿着第二方向y延伸得很长,并且可设置成与多个像素公共电压线cvl的相应像素公共电压线cvl相邻。多个次级电压线svl各自可在没有电耦连至像素公共电压焊盘cvp的情况下电耦连至相邻像素公共电压线cvl,并且可通过相邻像素公共电压线cvl供应由像素公共电压。为此,根据本公开内容实施方式的第一基板100可进一步包括将像素公共电压线cvl和次级电压线svl彼此电偶联的多个线连接图案lcp。

141.多个线连接图案lcp各自可设置在第一基板100处,使得线连接图案lcp 和彼此相邻的像素公共电压线cvl和次级电压线svl交叠,并且可通过使用跳线结构而将像素公共电压线cvl和次级电压线svl彼此电偶联。例如,多个线连接图案lcp各自的一侧可通过形成在次级电压线svl上方的绝缘层处的第一线接触孔而电偶联至次级电压线svl的一部分,并且多个线连接图案 lcp各自的另一侧可通过在像素公共电压线cvl上方的绝缘层处形成的第二线接触孔而电偶联至像素公共电压线cvl的一部分。

142.多个次级线连接部slcp各自可在与多个次级电压线svl各自重叠的多个像素p处将公共电极ce与多个次级电压线svl电偶联。相对于第二方向y,根据实施方式的多个次级线连接部slcp各自可在多个像素p之间的部分或多个像素p之间的边界区域处电耦连至多个次级电压线svl中的每一者,并且可电偶联至公共电极ce的一部分,并因此,可将公共电极ce电偶联至多个次级电压线svl中的每一者。因此,公共电极ce可通过次级线连接部slcp 而额外地耦连至多个次级电压线svl中的每一者。相应地,根据本公开内容实施方式的显示装置可防止、降低、或最小化由供应至布置在显示区域aa中的每个像素p的像素公共电压的偏差导致的图像质量退化。此外,在根据本公开内容实施方式的显示装置中,尽管并未额外地设置(或形成)耦连至多个次级电压线svl中的每一者的像素公共电压焊盘cvp,但像素公共电压可通过像素公共电压线cvl和多个线连接部lcp中的每一者供应至多个次级电压线svl中的每一者。

143.根据本公开内容实施方式的第一基板100可进一步包括坝部、封装层、波长转换层107、和功能膜108。

144.坝部可以沿着第一基板100的外围部设置。坝部可以在第一基板100的外围部处以闭环形状(或闭环线形状)实施。坝部可以是包括在最外面的像素 po中,或者可以设置在最外面的像素po的外围部分。

145.封装层可以被实现为围绕发光器件层。根据实施例的封装层可以包括设置在发光器件层和坝部上方的第一无机封装层(或第一封装层)、设置在第一无机封装层上方的第二无机封装层(或第三封装层)包封层,以及设置在第一无机包封层和第二无机包封层之间的有机包封层(或第二包封层),该有机包封层设置在被坝部围绕的发光器件层上。

146.坝部可以限定或限制覆盖发光器件层的前表面(或顶面)的有机封装层的布置区域(或封装区域)。坝部可以阻挡或防止有机封装层的扩散或溢出。

147.波长转换层可以转换从每个像素区pa的发射区ea入射到其上的光的波长。例如,波长转换层可以将从发射区ea入射到其上的白光(或蓝光)转换为对应于子像素的色光或者可以仅透射对应于子像素的色光。例如,波长转换层107可以包括波长转换构件和滤色器层中的至少一种。

148.根据实施例的波长转换层可以包括多个波长转换构件和外涂层(或保护层)。

149.根据实施例的多个波长转换构件可以设置在封装层之上,封装层设置在多个子像

素区中的每一个的发射区ea处。例如,多个波长转换构件中的每一个可以被实现为具有与每个子像素区域的发射区域ea相同或更宽的尺寸。

150.可以实施外涂层以覆盖波长转换构件并在波长转换构件上方提供平坦表面。例如,外涂层可以设置为覆盖波长转换构件和未设置波长转换构件的封装层。根据实施例的外涂层可以包括有机材料。或者,保护层还可以包括用于吸附水和/或氧气的吸气材料。

151.可选地,根据另一实施例的波长转换层可以包括设置在波长转换构件和封装层之间的量子点构件。量子点构件可以被配置为通过重新发射从发光器件层入射的白光或蓝光来重新发射设置在子像素中的有色光。

152.或者,波长转换层可以变为具有片状的波长转换片并且可以设置在封装层上方。在这种情况下,波长转换片(或量子点片)可以包括设置在一对膜之间的波长转换构件。例如,波长转换片的波长转换部件可以包括量子点部件,该量子点部件被配置为通过重新发射从发光器件层入射的白光或蓝光来重新发射设置在子像素中的有色光。

153.功能膜可以设置在波长转换层上方。例如,功能膜可以通过透明粘合构件耦合到波长转换层上方。根据实施例的功能膜可以包括抗反射层(或抗反射膜)、阻挡层(或阻挡膜)、触摸感应层和光路控制层(或光路控制膜)。

154.抗反射层可以包括防止被布置在第一基板100处的tft和/或像素驱动线反射的外部光传播到外部的圆偏振层(或圆偏振膜)。

155.阻挡层可以包括透水率低的材料(例如,聚合物材料),并且可以主要防止水或氧气的渗透。

156.触摸感应层可以包括基于互电容法或自电容法的触摸电极层,并且可以通过触摸电极层输出与用户的触摸相对应的触摸数据。

157.光路控制层可以包括交替堆叠高折射层和低折射层的堆叠结构,并且可以改变从每个像素p入射的光的路径以最小化或减少基于视角的色偏。

158.图5是图解图1和图3中所示的栅极驱动电路的图示。

159.参照图1、图3、和图5,根据本公开内容另一实施方式的栅极驱动电路 150可被实现(或嵌入)在第一基板100的显示区域aa内。栅极驱动电路150 可基于通过第一焊盘部件110和栅极控制线gcl供应的栅极控制信号而生成扫描信号,并顺序地将该扫描信号供应至多个栅极线gl。

160.栅极控制线gcl可包括起始信号线、多个移位时钟线、至少一个栅极驱动电压线、和至少一个栅极公共电压线。栅极控制线gcl可在第二方向y上延伸得很长,并且可沿着第一方向x设置成彼此间隔开第一基板100的显示区域aa中的预定或选定间隔。例如栅极控制线gcl可沿着第一方向设置在至少一个或多个像素p之间。

161.根据本公开内容实施方式的栅极驱动电路150可用包括多个级电路部 1501至150m的移位寄存器来实现,其中m是2或更大的整数。

162.多个级电路部1501至150m各自可单独地沿着第一方向x设置在第一基板100的第一表面的每个水平线中,并且可沿着第二方向y独立地彼此耦连。多个级电路部1501至150m各自可响应于通过第一焊盘部件110和栅极控制线gcl供应的栅极控制信号以预定或选定顺序生成扫描信号,并可将该扫描信号供应至相应的栅极线gl。

163.根据实施方式的多个级电路部1501至150m各自可包括多个分支电路 1511至151n

和分支网络153。

164.多个分支电路1511至151n可通过分支网络153选择性地耦连至栅极控制线gcl的导线,并且可通过分支网络153彼此电偶联。多个分支电路1511 至151n各自可基于通过栅极控制线gcl和分支网络153的电压供应的栅极控制信号生成扫描信号,并且可将该扫描信号供应至相应的栅极线gl。

165.多个分支电路1511至151n各自可包括配置级电路部1501至150m中一个级电路部的至少一个tft(或分支tft)。多个分支电路1511至151n中的任一个分支电路可包括耦连至栅极线gl的上拉(pull-up)tft。多个分支电路1511至151n中的另一个分支电路可包括耦连至栅极线gl的下拉 (pull-down)tft。

166.根据本公开内容实施方式的多个分支电路1511至151n各自可设置在基板 100的每个水平线中的两个相邻像素p之间的电路区域处或至少两个相邻像素 p之间的电路区域处,但本公开内容的实施方式不限于此。例如,多个分支电路1511至151n各自可根据配置级电路部1501至150m中的每一者的tft的数量和设置在一个水平线中的像素p的数量而设置在至少一个或多个相邻像素p之间的电路区域(或边界区域)处。

167.分支网络153可设置在第一基板100的每个水平线处,并且可将多个分支电路1511至151n彼此电偶联。根据本公开内容实施方式的分支网络153可包括多个控制节点线和多个网络线。

168.多个控制节点线可设置在第一基板100的每个水平线处,并且可在一个水平线中选择性地耦连至多个分支电路1511至151n。例如,多个控制节点线可设置在第一基板100的每个水平线处布置的像素中的上周缘区域(或下边缘区域)处。

169.多个网络线可选择性地耦连至设置在第一基板100处的栅极控制线gcl,并且可选择性地耦连至多个分支电路1511至151n。例如,多个网络线可将从栅极控制线gcl供应的栅极控制信号传输至相应的分支电路1511至151n,并且可在多个分支电路1511至151n之间传输信号。

170.如上所述,根据本公开内容的实施方式,由于栅极驱动电路150设置在基板100的显示区域aa内,因而最外像素区域pao的中心部和第一基板100 的外表面os之间的第二间隔d2可小于或等于相邻像素区域pa之间的第一间隔(或像素节距)d1的一半。例如,当栅极驱动电路150未设置在第一基板100的显示区域aa中而是设置在第一基板100的周缘部处时,第二间隔 d2可无法小于或等于第一间隔d1的一半。相应地,在根据本公开内容实施方式的发光显示装置中,栅极驱动电路150可设置在第一基板100的显示区域 aa中,并因此,第二间隔d2可被实现成小于或等于第一间隔d1的一半。

171.图6是图解根据本公开内容实施方式的显示装置的后表面的图示。

172.参照图1、图3、和图6,根据本公开内容实施方式的显示装置可进一步包括设置在基板100的后表面(或背表面)100b处的第二焊盘部210。

173.第二焊盘部210可设置在与设置在第一基板100的前表面100a处的第一焊盘部件110重叠的基板100的后表面100b的ab一个周缘部(或第一后周缘部)处。

174.第二焊盘部件210可包括沿着第一方向x以特定间隔布置从而分别与第一焊盘部件110的焊盘重叠的多个第二焊盘(或选路(rounting)焊盘)。

175.多个第二焊盘可被分(分类)为与第一像素驱动功率焊盘ppp中的每一者重叠的第

二像素驱动功率焊盘、与第第一数据焊盘dp中的每一者重叠的第二数据焊盘、与第一基准电压焊盘rvp中的每一者重叠的第二基准电压焊盘、与第一栅极焊盘gp中的每一者重叠的第二栅极焊盘、和与第一像素公共电压焊盘cvp中的每一者重叠的第二像素公共电压焊盘。

176.根据本公开内容实施方式的显示装置可进一步包括设置在第一基板100 的后表面100b上方的至少一个第三焊盘部件230和链接线部件250。

177.至少一个第三焊盘部件230(或输入焊盘部件)可设置在第一基板100的后表面100b处。例如,至少一个第三焊盘部件230可设置在与第一基板100 的后表面100b的第一周缘部相邻的中间部处。根据实施方式的至少一个第三焊盘部件230可包括以特定间隔彼此间隔开的多个第三焊盘(或输入焊盘)。例如,至少一个第三焊盘部件230可包括第三像素驱动功率焊盘、第三数据焊盘、第三基准电压焊盘、第三栅极焊盘、和第三像素公共电压焊盘。

178.链接线部件250可包括设置在第二焊盘部件210和至少一个第三焊盘部件 230之间的多个链接线。

179.根据本公开内容实施方式的链接线部件250可包括单独(或一对一关系) 将第二像素驱动功率焊盘耦连至第三像素驱动功率焊盘的多个像素驱动功率链接线、单独(或一对一关系)将第二数据焊盘耦连至第三数据焊盘多个数据链接线、单独(或一对一关系)将第二基准电压焊盘耦连至第三基准电压焊盘的多个基准电压链接线、单独(或一对一关系)将第二栅极焊盘耦连至第三栅极焊盘的多个栅极链接线、和单独(或一对一关系)将第二像素公共电压焊盘耦连至第三像素公共电压焊盘的多个像素公共电压链接线。

180.多个像素公共电压链接线各自可包括第一公共链接线251和第二公共链接线253。第一公共链接线251可设置在第二焊盘部件210和至少一个第三焊盘部件230之间,并且可共同地耦连至多个第二像素公共电压焊盘。第二公共链接线253可共同地耦连至多个第三像素公共电压焊盘,并且可电耦连至第一公共链接线251。第二公共链接线253可设置在于第一公共链接线251不同的层上,并且可通过过孔电耦连至第一公共链接线251。第二公共链接线253的尺寸可在从第三焊盘部件230至第一基板100的周缘部的方向上逐步增加以便降低(或最小化)像素公共电压的电压降。

181.根据本公开内容实施方式的显示装置可进一步包括设置在第一基板100 的外表面os处的选路部400。

182.选路部400可设置成围绕第一基板100的第一焊盘部件110、外表面os、和第二焊盘部件210。

183.根据实施方式的选路部400可包括多个选路(routing)线410。多个选路线410各自可沿着第一方向x以特定间隔进行设置,可形成为围绕第一基板 100的第一焊盘部件110、外表面os、和第二焊盘部件210,并且可以一对一关系电耦连至第一焊盘部件110和第二焊盘部件210中的每一者。根据实施方式,多个选路线410各自可通过使用导电胶的打印工艺来形成。作为另一实施方式,多个选路线410各自可通过将导电胶图案转移至由柔性材料制成的转移焊盘并将转移至转移焊盘的导电胶图案转移至选路部400的转移工艺来形成。例如,导电胶可以是ag胶,但本公开内容的实施方式不限于此。

184.多个选路线410各自可以一对一关系电耦连至第一焊盘部件110的第一焊盘和第二焊盘部件210的第二焊盘中的每一者。

185.根据实施方式的多个选路线410可被分(分类)为多个像素功率选路线 411、多个

数据选路线413、多个基准电压选路线415、多个栅极选路线417、和多个像素公共电压选路线419。

186.多个像素功率选路线411可形成为围绕第一焊盘部件110、外表面os、和第二焊盘部件210,并且可以一对一关系电耦连至第一焊盘部件110的多个第一像素驱动功率焊盘和第二焊盘部件210的多个第二像素驱动功率焊盘。

187.多个数据选路线413可形成为围绕第一焊盘部件110、外表面os、和第二焊盘部件210,并且可以一对一关系电耦连至第一焊盘部件110的多个第一数据焊盘和第二焊盘部件210的多个第二数据焊盘。

188.多个基准电压选路线415可形成为围绕第一焊盘部件110、外表面os、和第二焊盘部件210,并且可以一对一关系电耦连至第一焊盘部件110的多个第一基准电压焊盘和第二焊盘部件210的多个第二基准电压焊盘。

189.多个数据选路线417可形成为围绕第一焊盘部件110、外表面os、和第二焊盘部件210,并且可以一对一关系电耦连至第一焊盘部件110的多个第一栅极焊盘和第二焊盘部件210的多个第二像栅焊盘。

190.多个像素公共电压选路线419可形成为围绕第一焊盘部件110、外表面 os、和第二焊盘部件210,并且可以一对一关系电耦连至第一焊盘部件110 的多个第一像素公共电压焊盘cvp和第二焊盘部件210的多个第二像像素公共电压焊盘。

191.根据本公开内容实施方式的显示装置或选路部400可进一步包括边缘涂层。

192.边缘涂层可被实现成覆盖多个选路部400。根据实施方式的边缘涂层可被实现成覆盖第一基板100的第一周缘部和第一外表面os的全部以及多个选路线410。边缘涂层可防止包括金属材料的多个选路线410各自的腐蚀或者多个选路线410之间的电短路。此外,边缘涂层可防止、降低、或最小化由多个选路线410和第一焊盘部件110的第一焊盘导致的外部光的反射。根据实施方式的边缘涂层可包括含黑色油墨的阻光材料。例如,边缘涂层可以是边缘保护层或边缘绝缘层。

193.根据本公开内容实施方式的显示装置可进一步包括驱动电路部件500。

194.驱动电路部件500可基于从显示驱动系统供应的数字视频数据和时序同步信号驱动(或使之发光)设置在第一基板100上的像素p以允许显示区域 aa显示对应图像数据的图像。驱动电路部件500可耦连至设置在第一基板100 的后表面100b处的至少一个第三焊盘部件230,并且可将用于驱动(或使之发光)设置在第一基板100处的像素p的数据信号、栅极控制信号、和驱动功率输出至至少一个第三焊盘部件230。

195.根据实施方式的驱动电路部件500可包括柔性电路膜510、驱动集成电路 (ic)530、印刷电路板(pcb)550、时序控制器570、和电源电路590。

196.柔性电路膜510可耦连至设置在第一基板100的后表面100b处的至少一个第三焊盘部件230。

197.驱动ic 530可安置在柔性电路膜510上。驱动ic 530可接收从时序控制器570提供的子像素数据和数据控制信号,并基于数据控制信号将子像素数据转换为模拟数据信号已将该模拟数据信号供应至相应数据线dl。数据信号可通过柔性电路膜510而被供应至至少一个第三焊盘部件230中的相应第三数据焊盘。

198.驱动ic 530可通过设置在第一基板100处的多个基准电压线rl(或像素传感线)传

感设置在子像素sp中的驱动tft的特征值、针对每个子像素生成对应传感值的传感原始数据、并针对每个子像素将该传感原始数据提供至时序控制器570。

199.pcb 550可耦连至柔性电路膜510的另一侧周缘部。pcb 550可在驱动电路部件500的元件之间转移信号和功率。

200.时序控制器570可安装在pcb 550上,并且可通过设置在pcb 550上的用户连接器接收从显示驱动系统提供的数字视频数据和时序同步信号。或者,时序控制器570可未安装在pcb 550上,并且可被实现在显示驱动系统中或者可安装在pcb 550和显示驱动系统之间的单独控制板上。

201.时序控制器570可基于时序同步信号对齐数字视频数据以生成匹配设置在显示区域aa中的像素布置结构,并且可将生成的像素数据提供至驱动ic530。

202.时序控制器570可基于时序同步信号生成数据控制信号和栅极控制信号中的每一者、基于数据控制信号控制驱动ic 530的驱动时序、和基于栅极控制信号控制栅极驱动电路150的驱动时序。例如,时序同步信号可包括垂直同步信号、水平同步信号、数据使能信号、和主时钟(或点时钟)。

203.根据本公开内容实施方式的数据控制信号可包括源极起始脉冲、源极位移时钟、和源极输出信号、或类似者。数据控制信号可通过柔性电路膜510而被供应至驱动ic 530。

204.根据实施方式的栅极控制信号可包括起始信号(或栅极起始信号)、多个位移时钟、正向驱动信号、和反向驱动信号。在这种情况下,多个位移时钟可包括其相位顺序发生位移的多个扫描时钟和其相位顺序发生位移的多个进位时钟。此外,根据实施方式的栅极控制信号可进一步包括用于传感设置在子像素sp中的驱动tft的特征值的外部传感线选择型号、外部传感重置信号、和外部传感控制信号。栅极控制信号可通过柔性电路膜510、至少一个第三焊盘部件230、链接线部件250、第二焊盘部件210、选路部400、第一焊盘部件 110、和栅极控制线gcl而被供应至栅极驱动电路150。

205.时序控制器570可在预定的外部传感周期期间基于外部传感模式而驱动驱动ic 530和栅极驱动电路150中的每一者、基于从驱动ic 530提供的传感原始数据生成每个子像素的补偿数据以补偿每个子像素的驱动tft的特性变化、并基于生成的每个子像素的补偿数据调制每个子像素的像素数据。例如,时序控制器570可在对应垂直同步信号的空白周期(或垂直空白周期)的每个外部传感周期基于外部传感模式驱动驱动ic 530和栅极驱动电路150中的每一者。例如,可在通电显示装置的过程、断电显示装置的过程、被长时间驱动之后断电显示装置的过程、和实时或周期性设定的帧的空白周期中执行外部传感模式。

206.根据实施方式的时序控制器570可基于外部传感模式而将从驱动ic 530 提供的每个子像素的传感原始数据存储在存储电路中。此外,在显示模式中,时序控制器570可基于存储电路中存储的传感原始数据而校正待被供应至每个子像素的像素数据,并且可将经校正的像素数据提供至驱动ic 530。在此,传感每个子像素的原始数据可包括关于设置在相应子像素中的驱动tft和自发光器件中的每一者的顺序变化信息。因此,在外部传感模式中,时序控制器 570可传感设置在每个子像素中的驱动tft的特征值(例如,阈值电压或迁移率),并基于此可校正待被供应至每个子像素的像素数据,由此最小化或防止由多个子像素的驱动tft的特征值偏差导致的图像质量退化。显示装置的外部传感模式可以是对本领域技术人员已知的技术,并因此,省略了其详细描述。例如,根据本公开内容实施方式的显

示装置可基于韩国专利公开第 10-2016-0093179号、第10-2017-0054654号、或第10-2018-0002099号中公开的传感模式传感设置在每个子像素p中的驱动tft的特征值。

207.电源电路590可安装在pcb 550上,并且可通过使用从外部供应的输入电源来生成在像素p上显示图像所需的各种源电压以将生成的源电压提供至相应的电路。例如,电源电路590可生成并输出驱动时序控制器570和驱动ic530中的每一者所需的逻辑源电压、提供至驱动ic 530的多个基准伽马电压、和驱动栅极驱动电路150所需的至少一个栅极驱动电源和至少一个栅极公共电源。此外,电源电路590可生成并输出像素驱动电源和像素公共电压,但本公开内容的实施方式不限于此。例如,驱动ic 530可基于多个基准伽马电压生成并输出像素驱动电源和像素公共电压。

208.图7是图解根据本公开内容另一实施方式的显示装置的后透视图,图解了在图1至图6中所示的显示装置中额外设置配线基板的实施方式。

209.参照图7,根据本公开内容另一实施方式的显示装置可包括第一基板100、第二基板200、耦连元件300、和选路部400。

210.第一基板100可被称为显示基板、像素阵列基板、上基板、前基板、和基础基板。第一基板100可以是玻璃基板,或者可以是薄玻璃基板或塑料基板,其是可弯曲的或者柔性的。

211.第一基板100可与图1至图6中所示的发光显示装置的第一基板100实质上相同,并因此,类似的参考数字指类似的元件,并且可省略它们重复的描述。

212.第二基板200可被称为配线基板、线基板、链接基板、下基板、后基板、或链接玻璃。第二基板200可以是玻璃基板,或者可以是薄玻璃基板或塑料基板,其是可弯曲的或者柔性的。例如,第二基板200可包括与第一基板100 相同的材料。第二基板200的尺寸可与第一基板100相同或实质上相同,但本公开内容的实施方式不限于此,第二基板200可具有小于第一基板100的尺寸。例如,第二基板200可被配置成具有与第一基板100相同的尺寸以便保持或确保第一基板100的硬度。

213.第二基板200可包括第二焊盘部件210、至少一个第三焊盘部件230、和链接线部250。除了第二焊盘部件210、至少一个第三焊盘部件230、和链接线部250设置在第二基板200的后表面(或背表面)200b处之外,第二焊盘部件210、至少一个第三焊盘部件230、和链接线部250各自可与图6中所示的第二焊盘部件210、至少一个第三焊盘部件230、和链接线部250各自实质上相同,并因此,类似的参考数字指类似的元件,并且可省略它们重复的描述。

214.第二基板200可通过使用耦连元件300耦连(连接)至第一基板100的第二表面100b。耦连元件300可插置在第一基板100和第二基板200之间。因此,第一基板100和第二基板200可通过耦连元件300彼此相对的结合。

215.选路部400可被称为侧选路部、侧配线部、印刷配线部、或印刷线部。根据实施方式的选路部400可包括设置在第一基板100的外表面os之中第一外表面(或一个表面)os1a和第二基板200的外表面os之中的第一外表面(或一个表面)os1b中的每一者处的多个选路线410。除了多个选路线410设置成围绕第一焊盘部件110和第一基板100的第一外表面os1a以及第二焊盘部 210和第二基板200的第一外表面os1b之外,选路部400可与图6中所示的选路部400实质上相同,并因此,类似的参考数字指类似的元件,并且可省略它们重复的描述。

216.根据本公开内容另一实施方式的显示装置可进一步包括驱动电路部件 500。

217.电路部件500可包括柔性电路膜510、驱动集成电路(ic)530、印刷电路板(pcb)550、时序控制器570、和电源电路590。除了柔性电路膜510耦连至设置在第二基板200的后表面200b处的第三焊盘部件230之外,具有这种配置的驱动电路部件500可与图6中所示的驱动电路部件500实质上相同,并因此,类似的参考数字指类似的元件,并且可省略它们重复的描述。

218.图8是图解图5中说明的第i级电路单元的电路图。

219.参照图3至图5和图8,根据本公开的一个实施方案的第i级电路单元150i 可以响应从布置在基板(或第一基板)100上的栅极控制线gcl提供的栅极控制信号,输出两个扫描信号ssi和ssi+1以及一个仅为信号csi。

220.根据一个实施方式的栅极控制信号可以包括启动信号vst,多个移位时钟,包括多个扫描时钟sclk和多个进位时钟cclk,第一至第三栅极驱动功率 gvdd1、gvdd2和gvdd3,以及第一至第三栅极公共功率gvss1、gvss2和 gvss3。在这种情况下,栅极控制线gcl可以包括一个启动信号线,多个扫描时钟线,多个进位时钟线,第一至第三栅极驱动电源线,以及第一至第三次级栅极公共电源线。

221.根据一个实施方式的栅极控信号可以包括第一到第j个进位时钟和第一到第j个扫描时钟。例如,j可以是4,但是本公开的实施方式不限于此,并且可以是6,8或10或更多的偶数。

222.当栅极控制信号包括第一到第四进位时钟时,第一进位时钟可以应用于第 4k-3级(其中k为自然数)级电路单元,第二进位时钟可以应用于第4k-2级电路单元电路单元,第三进位时钟可以应用于第4k-1级电路单元,第四进位时钟可以应用于第4k级电路单元。当栅极控制信号包括第一至第四扫描时钟时,第一和第二扫描时钟可以被施加到奇数级电路单元,并且第三和第四扫描时钟可以被施加到偶数级电路单元。

223.此外,根据实施方式的栅极控制信号还可以包括正向驱动信号fws和反向驱动信号bws。在这种情况下,栅极控制线gcl还可以包括正向驱动信号线和反向驱动信号线。

224.根据实施方式的栅极控制信号还可包括用于外部感测模式的外部感测线选择信号slss、外部感测复位信号srst和外部感测控制信号scs。在这种情况下,栅极控制线gcl还可以包括外部感测选择信号线、外部感测复位信号线和外部感测控制信号线。

225.根据本公开实施方式的第i级电路单元150i可以包括分支网络153、节点控制电路ncc、第一反相电路ic1、第二反相电路ic2、节点复位电路nrc 和输出缓冲电路obc

226.分支网络153可用于在节点控制电路ncc、第一反相电路ic1、第二反相电路ic2、节点复位电路nrc和输出缓冲电路obc之间形成电路连接,并选择性地连接到栅极控制线gcl的线。

227.分支网络153可以选择性地耦合到栅极控制线gcl的线。根据实施方式的分支网络153可以包括第一至第三控制节点线q、qbo和qbe以及网络线 nl。

228.第一至第三控制节点线q、qbo和qbe中的每一个可以设置在布置在第一基板100的第i条水平线上的每个像素区域的上边缘区域(或下边缘区域)。第一至第三控制节点线q、qbo和qbe可以与第一方向x或栅极线gl平行布置。例如,第一至第三控制节点线q、qbo和qbe中的每一条可以设置为与栅极线gl相邻。

229.网络线nl可以选择性地耦合到栅极控制线gcl的线并且可以选择性地耦合到第一至第三控制节点线q、qbo和qbe。此外,网络线nl可以选择性地耦合在配置级电路单元150i的电路之间。

230.节点控制电路ncc可以被实现为控制第一至第三控制节点线q、qbo和 qbe中的每一个的电压。

231.根据实施方式的节点控制电路ncc可以通过网络线nl耦合到第一到第三控制节点线q、qbo和qbe中的每一个,并且可以被实现为控制第一到第三控制节点中的每一个的电压线q、qbo和qbe响应于通过网络线nl提供的起始信号vst、复位信号vrst和第一栅极驱动电源gvdd1。作为一个实施方式,起始信号vst可以是从第i-2级电路单元150i-2输出的第i-2进位信号 csi-2。复位信号vrst可以是从第i+2级电路单元150i+2输出的第i+2进位信号csi+2。

232.根据另一实施方式,节点控制电路ncc可以通过网络线nl耦合到第一到第三控制节点线q、qbo和qbe中的每一个,并且可以控制第一到第三控制节点线q中的每一个的电压、qbo和qbe响应于通过网络线nl提供的启动信号vst、复位信号vrst、正向驱动信号fws、反向驱动信号bws和第一栅极驱动电源gvdd1。作为一个实施方式,当正向驱动信号fws具有高电压电平(或高电位电压电平)时,反向驱动信号bws可具有低电压电平(或低电位电压电平),当正向驱动信号fws具有低电压电平(或低电位电压电平),反向驱动信号bws可具有高电压电平(或高电位电压电平)。例如,当正向驱动信号fws具有高电压电平时,栅极驱动电路150可以基于正向扫描驱动提供从第一条栅极线到最后一条栅极线的扫描信号,并且当反向驱动信号bws具有在高电压电平时,栅极驱动电路150可以基于反向扫描驱动将扫描信号从最后一条栅极线提供到第一条栅极线。在此,高电压电平可称为第一电压电平、高电位电压电平、栅极导通电压电平或晶体管导通电压电平,而低电压电平可称为第二电压。电平、低电位电压电平、栅极关断电压电平或晶体管关断电压电平。

233.第一逆变器电路ic1可以基于通过网络线nl提供的第一控制节点线q的电压来控制或放电第二控制节点线qbo的电压。根据实施方式的第一反相器电路ic1可以通过以下方式耦合到第二栅极驱动电源gvdd2、第一控制节点线q、第二控制节点线qbo、第一栅极公共电源gvss1和第二栅极公共电源 gvss2网络线nl。响应于第二栅极公共电源gvss2和第一控制节点线q的电压,第一反相电路ic1可以向第二控制节点线qbo提供第一栅极公共电源 gvss1以对第二控制节点线的电压进行放电qbo。

234.第二逆变器电路ic2可以基于通过网络线nl提供的第一控制节点线q的电压来控制或放电第三控制节点线qbe的电压。根据实施方式的第二反相器电路ic2可以通过以下方式耦合到第三栅极驱动电源gvdd3、第一控制节点线q、第三控制节点线qbe、第一栅极公共电源gvss1和第二栅极公共电源 gvss2。网络线nl。响应于第三栅极公共电源gvss3和第一控制节点线q的电压,第二反相电路ic2可以向第三控制节点线qbe提供第一栅极公共电源 gvss1以对第三控制节点线的电压进行放电qbe。第二栅极驱动电源gvdd2 和第三栅极驱动电源gvdd3之间可以具有反相(或彼此相反)的电压电平。例如,当第二栅极驱动电源gvdd2具有高电压电平时,第三栅极驱动电源 gvdd3可以具有低电压电平,而当第二栅极驱动电源gvdd2具有低电压电平时,第三栅极驱动电源gvdd3可以具有具有高电压电平。

235.第二栅极公共电源gvss2和第一栅极公共电源gvss1可以具有相同的电压电平或

不同的电压电平。

236.节点复位电路nrc可以维持第二控制节点线qbo和第三控制节点线qbe 中的每一个的电压电平,而第一控制节点线q的电压具有高电压电平。

237.根据实施方式的节点复位电路nrc可以响应于通过网络线nl提供的起始信号vst和复位信号vrst同时复位第二控制节点线qbo的电压和第三控制节点线qbe的电压。作为一个实施方式,节点复位电路nrc可以响应于起始信号vst和复位信号vrst向第二控制节点线qbo和第三控制节点线qbe提供第一栅极公共电源gvss1,从而可以保持第二控制节点线qbo和第三控制节点线qbe处于第一栅极公共电源gvss1的电压电平。

238.根据另一实施方式,节点重置电路nrc可响应于起始信号vst、重置信号vrst、正向驱动信号fws以及通过网络线nl提供的反向驱动信号bws 同时重置第二控制节点线qbo的电压和第三控制节点线qbe的电压。作为一个实施方式,节点复位电路nrc可以响应于起始信号vst、复位信号vrst、正向驱动信号fws、向第二控制节点线qbo和第三控制节点线qbe提供第一栅极公共电源gvss1、以及反向驱动信号bws,因此可以将第二控制节点线 qbo和第三控制节点线qbe中的每一个保持在第一栅极公共电源gvss1的电压电平。

239.输出缓冲电路obc可以被实现为响应于第一至第三控制节点线中的每一条的电压,依次输出具有栅极导通电压电平的两个扫描信号或依次输出具有栅极截止电压电平的两个扫描信号。q、qbo和qbe基于通过网络线nl提供的进位时钟cclk、扫描时钟sclk、第一栅极公共电源gvss1和第三栅极公共电源gvss3。

240.输出缓冲电路obc可以被实现为响应于第一至第三控制节点线中的每一条的电压,依次输出具有栅极导通电压电平的两个扫描信号或依次输出具有栅极截止电压电平的两个扫描信号。q、qbo和qbe基于通过网络线nl提供的进位时钟cclk、扫描时钟sclk、第一栅极公共电源gvss1和第三栅极公共电源gvss3。

241.当第一控制节点线q的电压具有高电压电平并且第二和第三控制节点线 qbo和qbe中的每一条的电压具有低电压电平时,根据实施方式的输出缓冲电路obc可以输出每一条第i个进位信号csi对应进位时钟cclk,第i个扫描信号ssi对应奇数扫描时钟sclko,第i+1个扫描信号ssi+1对应偶数扫描时钟sclke。作为一个实施方式,第i个进位信号csi可以作为起始信号vst 提供给第i+2级电路单元,第i个扫描信号ssi可以提供给奇数栅极线glo(或第i栅极线gli),并且第i+1扫描信号ssi+1可以提供给偶数栅极线gle(或第i+1栅极线gli+1)。

242.当第一和第三控制节点线q和qbe中的每一个的电压具有低电压电平并且第二控制节点线qbo的电压具有高电压电平时,根据实施方式的输出缓冲电路obc可以输出每一个第i个扫描信号ssi和第i+1个扫描信号ssi+1各自具有对应于第三栅极公共电源gvss3的电压电平的栅极截止电压电平,并且可以输出具有栅极截止电压电平的第i个进位信号csi对应于第一栅极公共电源gvss1的电压电平。

243.当第一和第二控制节点线q和qbo中的每一个的电压具有低电压电平并且第三控制节点线qbe的电压具有高电压电平时,根据实施方式的输出缓冲电路obc可以输出每一个第i个扫描信号ssi和第i+1个扫描信号ssi+1各自具有对应于第三栅极公共电源gvss3的电压电平的栅极截止电压电平,并且可以输出具有栅极截止电压电平的第i个进位信号csi对应于第一栅极公共电源gvss1的电压电平。

244.根据实施方式的输出缓冲电路obc可以设置在平行于第一方向x的第i 条水平线的中心区域中。例如,当输出缓冲电路obc设置为与第一方向x的一端(或另一端)相邻时对于水平线,由于水平线的线电阻,扫描信号的电压电平可能在从栅极线的一端到其另一端的方向上降低,因此,为了防止这种问题,输出缓冲电路obc应设置在与第一方向x平行的第i条水平线的中心区域,但本发明实施方式不限于此,可以设置在第i条水平线的一侧或另一侧,当栅极线的总长度较短。

245.第一至第三栅极公共电源gvss1、gvss2和gvss3可以具有相同的电压电平或不同的电压电平。

246.根据本公开实施方式的第i级电路单元150i还可以包括第四控制节点线 qm、第一感测控制电路scc1和第二感测控制电路scc2。

247.第四控制节点线qm可以实现为电连接在第一感测控制电路scc1和第二感测控制电路scc2之间。第四控制节点线qm可以包括在分支网络153中并且可以通过网络线nl电连接在第一感测控制电路scc1和第二感测控制电路 scc2之间。

248.第一感测控制电路scc1可被实施为响应于第i进位信号csi、外部感测线选择信号slss、外部感测控制信号scs、外部感测复位信号srst和通过分支网络153提供的第一栅极驱动电源gvdd1。作为实施方式,第一感测控制电路scc1可以将第一栅极驱动电源gvdd1充入第四控制节点线qm中。响应于具有高电压电平的第i进位信号csi和具有高电压电平的外部感测线选择信号slss,然后,可以响应于充入第四控制的电压来控制第一控制节点线q的电压节点线qm、在垂直消隐期的前段期间提供的具有高电压电平的外部感测控制信号scs、以及第一栅极驱动电源gvdd1。因此,输出缓冲电路obc可以分别输出对应于进位时钟cclk的第i个进位信号csi、对应于奇数扫描时钟 sclko的第i个扫描信号ssi以及对应于以下的第i+1个扫描信号ssi+1。基于第一控制节点线q的电压,在垂直消隐周期期间的偶数扫描时钟sclke。

249.此外,第一感测控制电路scc1可以响应于通过分支网络153提供的外部感测复位信号srst来释放第一控制节点线q的电压。作为一个实施方式,第一感测控制电路scc1可以提供第一栅极响应于在垂直消隐期的后期期间提供的具有高电压电平的外部感测复位信号srst,向第一控制节点线q提供公共电源gvss1以复位或初始化第一控制节点线q的电压。

250.第二感测控制电路scc2可以被实现为响应于第四控制节点线qm的电压和通过提供的外部感测控制信号scs来释放第二控制节点线qbo和第三控制节点线qbe中的每一个的电压。分支网络153。作为一个实施方式,第二感测控制电路scc2可以向第二控制节点线qbo和第三控制节点线qbe中的每一个提供第一栅极公共电压gvss1,以同时对第二控制节点线qbo和qbe进行放电。第三控制节点线qbe,响应于具有高电压电平的第四控制节点线qm 的电压和具有高电压电平的外部感测控制信号scs。

251.图9是示出图8所示的节点控制电路、第一反相器电路、第二反相器电路和第一感测控制电路的电路图。

252.参照图8和图9,根据实施方式的节点控制电路ncc可以包括第一到第四节点控制电路ncc1到ncc4。

253.在正向扫描驱动中,第一节点控制电路ncc1可以响应于具有高电压电平的启动信号vst和具有高电压电平的正向驱动信号fws,将正向驱动信号fws 的高电压电平充入第一

控制节点线q。高电压电平。此外,在反向扫描驱动中,第一节点控制电路ncc1可以将具有低电压电平的正向驱动信号线电连接到第一控制节点线q,以将充入第一控制节点线q的电压放电到低电平。电压电平响应于具有高电压电平的启动信号vst和具有低电压电平的正向驱动信号fws。

254.根据实施方式的第一节点控制电路ncc1可以包括第一至第三tft t1至 t3。

255.第一tft t1可以响应于起始信号vst将正向驱动信号fws输出到第一连接节点nc1。例如,第一tft t1可以基于具有高电压电平的启动信号vst导通并且可以将通过正向驱动信号线提供的正向驱动信号fws输出到第一连接节点nc1。

256.响应于起始信号vst,第二tft t2可以将第一连接节点nc1电连接到第一控制节点线q。例如,第二tft t2可以基于具有高电压电平的启动信号vst 导通并且可以将通过第一tft t1和第一连接节点nc1提供的正向驱动信号 fws输出到第一控制节点线问。

257.第三tft t3可以响应于第一控制节点线q的电压向第一连接节点nc1 提供通过第一栅极驱动电源线提供的第一栅极驱动电源gvdd1。例如,第三 tft t3可以是基于具有高电压电平的第一控制节点线q的电压导通并且可以将第一栅极驱动电源gvdd1传输到第一tft t1和第二tft t2之间的第一连接节点nc1,从而防止电压泄漏例如,第三薄膜晶体管t3可以增加第二薄膜晶体管t2的栅极电压与第一连接节点nc1的电压之间的电压差,以关闭已经关闭的第二薄膜晶体管t2。在具有低电压电平的启动信号vst上,因此可以通过截止的第二tft t2防止第一控制节点线q的电压下降,从而稳定地保持第一控制节点线q的电压。

258.在反向扫描驱动中,第二节点控制电路ncc2可以响应于具有高电平的复位信号vrst和具有高电平的反向驱动信号bws,将反向驱动信号bws的高电平充入第一控制节点线q。高电压电平。此外,在正向扫描驱动中,第二节点控制电路ncc2可以将具有低电压电平的反向驱动信号线电连接到第一控制节点线q,以将充入第一控制节点线q的电压放电到低电平。电压电平响应于具有高电压电平的复位信号vrst和具有低电压电平的反向驱动信号 bws。

259.根据实施方式的第二节点控制电路ncc2可以包括第四tft t4和第五 tft t5。

260.第四tft t4可以响应于复位信号vrst输出反向驱动信号bws。例如,第四tft t4可以基于具有高电压电平的复位信号vrst导通并且可以将通过反向驱动信号线提供的反向驱动信号bws输出到第二连接节点nc2。

261.第五tft t5可以响应于复位信号vrst将第二连接节点nc2电连接到第一控制节点线q。例如,第五tft t5可以基于具有高电压电平的复位信号vrst 导通并且可以将通过第四tft t4和第二连接节点nc2提供的反向驱动信号 bws输出到第一控制节点线问。

262.第四tft t4和第五tft t5之间的第二连接节点nc2可以电连接到第一连接节点nc1。因此,可以通过第一节点控制电路ncc1的第三tft t3向第二连接节点nc2提供通过第一栅极驱动电源线提供的第一栅极驱动电源 gvdd1。因此,第一节点控制电路ncc1的第三薄膜晶体管t3可以增加第二节点控制电路ncc2的第五薄膜晶体管t5的栅极电压与第二连接节点nc2的电压之间的电压差,以完全关断第五薄膜晶体管。基于具有低电压电平的复位信号vrst已经截止的t5,因此可以通过截止的第五tft t5防止第一控制节点线q的压降(或漏电流),从而稳定维持第一控制节点线q的电压。

263.第三节点控制电路ncc3可以响应于第二控制节点线qbo的电压对第一控制节点线

q的电压进行放电。例如,第三节点控制电路ncc3可以基于第二控制节点线qbo的高电压电平在第一控制节点线q和第一栅极公共电源线之间形成电流通路,以对第一控制节点的电压进行放电。线q到第一栅极公共电源线。

264.根据实施方式的第三节点控制电路ncc3可以包括第六tft t6和第七 tft t7。

265.第六tft t6可以响应于第二控制节点线qbo的电压向第二连接节点nc2 提供通过第一栅极公共电源线供应的第一栅极公共电源gvss1。例如,第六 tft t6可以基于第二控制节点线qbo的高电压电平导通并且可以将第二连接节点nc2电连接到第一栅极公共电源线。

266.第七tft t7可以响应于第二控制节点线qbo的电压将第二连接节点nc2 电连接到第一控制节点线q。例如,第七tft t7可以基于第二控制节点线qbo 的高电压电平导通并且可以将第二连接节点nc2电连接到第一控制节点线q。

267.第七薄膜晶体管t7可以基于第二控制节点线qbo的低电压电平截止,并且关闭的第七薄膜晶体管t7的栅极电压与第二连接节点nc2的电压之间的电压差可以基于在通过第一节点控制电路ncc1的第三tft t3提供给第二连接节点nc2的第一栅极驱动电源gvdd1上,从而可以完全基于第二控制节点线 qbo的低电压电平关断第七tft t7基于提供给第二连接节点nc2的第一栅极驱动电源gvdd1而截止。因此,可以防止第一控制节点线q通过第三节点控制电路ncc3的压降(或电流泄漏),因为第七tft t7完全关断,从而稳定地维持第一控制节点线q的电压。

268.第四节点控制电路ncc4可以响应于第三控制节点线qbe的电压对第一控制节点线q的电压进行放电。例如,第四节点控制电路ncc4可以根据第三控制节点线qbe的高电压电平在第一控制节点线q和第一栅极公共电源线之间形成电流通路,以对第一控制节点的电压进行放电。线q到第一栅极公共电源线。

269.根据实施方式的第四节点控制电路ncc4可以包括第八tft t8和第九 tft t9。

270.第八tft t8可以响应于第三控制节点线qbe的电压将通过第一栅极公共电源线供应的第一栅极公共电源gvss1供应给第二连接节点nc2。例如,第八tft t8可以基于第三控制节点线qbe的高电压电平导通并且可以将第二连接节点nc2电连接到第一栅极公共电源线。

271.第九tft t9可以响应于第三控制节点线qbe的电压将第二连接节点nc2 电连接到第一控制节点线q。例如,第九tft t9可以基于第三控制节点线qbe 的高电压电平导通并且可以将第二连接节点nc2电连接到第一控制节点线q。

272.第九tft t9可以基于第三控制节点线qbe的低电压电平关断,并且关断的第九tft t9的栅极电压与第二连接节点nc2的电压之间的电压差可以基于在通过第一节点控制电路ncc1的第三tft t3提供给第二连接节点nc2的第一栅极驱动电源gvdd1上,从而可以完全基于第三控制节点线qbe的低电压电平关断第九tft t9基于提供给第二连接节点nc2的第一栅极驱动电源 gvdd1而截止。因此,由于第九tft t9完全关断,可以防止第一控制节点线 q通过第四节点控制电路ncc4的压降(或电流泄漏),从而稳定地保持第一控制节点线q的电压。

273.第一反相器电路ic1可以响应于第一控制节点线q的电压和第二栅极驱动功率gvdd2而对第二控制节点线qbo的电压进行放电。例如,第一反相电路ic1可以基于第一控制

节点线q的高电压电平在第二控制节点线qbo和第一栅极公共电源线之间形成电流通路,以对第二控制节点线的电压进行放电。 qbo到第一门公共电源线。

274.根据实施方式的第一反相器电路ic1可以包括第十至第十三tft t10至 t13和第一电容器c1。

275.第十tft t10可以基于第二栅极驱动电源gvdd2导通或截止,并且可以将导通时具有高电压电平的第二栅极驱动电源gvdd2输出到第一内部节点 ni1。根据实施方式的第十tft t10可以二极管连接在第二栅极驱动电源 gvdd2和第一内部节点ni1之间。

276.第十一tft t11可以基于第一控制节点线q的电压导通或截止,并且当导通时,可以将第一内部节点ni1的电压放电到第二栅极公共电源线。

277.第十二tft t12可以基于第一内部节点ni1的电压导通或截止,并且当导通时可以向第二控制节点线qbo提供第二栅极驱动电源gvdd2。

278.第十三tft t13可以根据第一控制节点线q的电压导通或截止,当导通时,可以将第二控制节点线qbo的电压提供给第一栅极公共电源线。

279.第一电容器c1可以形成在第一内部节点ni1与第十二tft t12和第十三 tft t13之间的节点(或第二控制节点线qbo)之间。例如,第一电容器c1 可以允许基于第二栅极驱动功率gvdd2的电压变化在第一内部节点ni1中发生自举。因此,当第二栅极驱动电源gvdd2的电压电平发生变化时,第一内部节点ni1的电压可能会因第二栅极驱动电源gvdd2的电压变化而发生变化,这是由于第一电容器c1和电容器c1的耦合引起的自举。第二栅极驱动功率 gvdd2,从而进一步增强第十二tft t12的输出特性。

280.第二逆变器电路ic2可以响应于第一控制节点线q的电压和第三栅极驱动功率gvdd3而对第三控制节点线qbe的电压进行放电。例如,第二反相电路ic2可以基于第一控制节点线q的高电压电平在第三控制节点线qbe和第一栅极公共电源线之间形成电流通路,以对第三控制节点线的电压进行放电。 qbe至第一栅极公共电源线。

281.根据实施方式的第二逆变器电路ic2可以包括第十四至第十七tft t14 至t17和第二电容器c2。

282.第十四tft t14可以基于第三栅极驱动电源gvdd3导通或截止,并且可以将导通时具有高电压电平的第三栅极驱动电源gvdd3输出到第二内部节点 ni2。根据实施方式的第十四tft t14可以二极管连接在第三栅极驱动电源 gvdd3和第二内部节点ni2之间。

283.第十五tft t15可以基于第一控制节点线q的电压导通或截止,并且当导通时,可以将第二内部节点ni2的电压放电到第二栅极公共电源线。

284.第十六tft t16可以基于第二内部节点ni2的电压导通或截止,并且当导通时可以向第三控制节点线qbe提供第三栅极驱动电源gvdd3。

285.第十七tft t17可以根据第一控制节点线q的电压导通或截止,当导通时,可以将第三控制节点线qbe的电压提供给第一栅极公共电源线。

286.第二电容器c2可以形成在第二内部节点ni2与第十六tft t16和第十七 tft t17之间的节点(或第三控制节点线qbe)之间。例如,基于第三栅极驱动电源gvdd3的电压变化,第二电容器c2可以允许自举发生在第二内部节点 ni2中。因此,当第三栅极驱动电源gvdd3的电压电平发生变化时,第二内部节点ni2的电压可能会因第二电容器c2和第二电容c2的耦合引起的自举而进一步随着第三栅极驱动电源gvdd3的电压变化而变化。第三栅极驱动

功率gvdd3,从而进一步增强第十六tft t16的输出特性。

287.第一感测控制电路scc1可以被实现为响应于第i个进位信号csi、外部感测线选择信号slss、外部感测控制信号scs、外部感测复位信号srst和第一栅极驱动电源gvdd1。

288.根据实施方式的第一感测控制电路scc1可以包括第五节点控制电路 ncc5和第六节点控制电路ncc6。

289.第五节点控制电路ncc5可以响应于第i个进位信号csi、外部感测线选择信号slss、外部感测控制信号scs、以及第一栅极驱动电源gvdd1。

290.根据实施方式的第五节点控制电路ncc5可以包括第三十三至第三十七 tft t33至t37和第三电容器c3。

291.第三十三tft t33可以响应于与起始信号vst一起提供的外部感测线选择信号slss将第i进位信号csi输出到第三连接节点nc3。例如,第三十三tftt33可以基于具有高电压电平的外部感测线选择信号slss导通并且可以将第i 进位信号csi输出到第三连接节点nc3。

292.第三十四tft t34可以响应于外部感测线选择信号slss将第三连接节点nc3电连接到第四控制节点线qm。例如,第三十四tft t34可以基于具有高电压电平的外部感测线选择信号slss导通并且可以提供通过第三十三tftt33和第三连接节点nc3提供的第i进位信号csi,到第四控制节点线qm。第三连接节点nc3可以是第三十三tft t33和第三十四tft t34之间的连接线。

293.第三十五tft t35可以响应于第四控制节点线qm的电压向第三连接节点nc3提供第一栅极驱动电源gvdd1。例如,第三十五tft t35可以基于具有高电压电平的第四控制节点线qm的电压而导通并且可以向第三连接节点 nc3提供第一栅极驱动电源gvdd1,从而防止电压泄漏。第四控制节点线qm。例如,第三十五薄膜晶体管t35可以增加第三十四薄膜晶体管t34的栅极电压和第三连接节点nc3的电压之间的电压差,从而可以完全关断第三十四薄膜晶体管t34,其具有基于具有低电压电平的外部感测线选择信号slss被关断,从而通过关断的第三十四tft t34防止第四控制节点线qm的压降(或电流泄漏)以稳定维持电压第四控制节点线qm。

294.第三十六tft t36可以响应于第四控制节点线qm的电压向第三十七tftt37输出第一栅极驱动功率gvdd1。例如,第三十六tft t36可以基于具有高电压电平的第四控制节点线qm的电压而导通并且可以向第三十七tft t37 提供第一栅极驱动电源gvdd1。

295.第三十七tft t37可以响应于外部感测控制信号scs将第三十六tft t36 电连接到第一控制节点线q。例如,第三十七tft t37可以基于具有高电压电平的外部感测控制信号scs而导通,并且可以将通过第三十六tft t36提供的第一栅极驱动电源gvdd1提供给第一控制节点线q将第一栅极驱动电源 gvdd1的电压电平充入第一控制节点线q。

296.第三电容器c3可以形成在第四控制节点线qm和第一栅极驱动电源线之间并且可以存储第四控制节点线qm和第一栅极驱动电源线之间的差电压。例如,第三电容器c3的第一电极可以电连接到第四控制节点线qm,第四控制节点线qm共同连接到第三十五tft t35的栅电极和第三十六tft t36的栅电极,第三电容器c3的第二电极可以电连接到第一栅极驱动电源线。第三电容器c3可以根据第三十三、第三十四和第三十五tft t33至t35的导通,以及当第三十三、第三十四和三十-第五tft t33至t35截止,第三电容器c3 可以利用存储

的电压将第四控制节点线qm的电压保持在高电压电平。例如,第三电容器c3可以在一个水平周期期间通过使用存储的电压将第四控制节点线qm的电压保持在高电压电平。

297.第六节点控制电路ncc6可以响应于外部感测复位信号srst来释放第一控制节点线q的电压。作为一个实施方式,第六节点控制电路ncc6可以响应于具有高电压电平的外部感测复位信号srst向第一控制节点线q提供第一栅极公共电源gvss1,从而复位或初始化第一控制的电压。节点线q。

298.根据实施方式的第六节点控制电路ncc6可以包括第三十八tft t38和第三十九tft t39。

299.第三十八tft t38可以响应于外部感测复位信号srst将通过第一栅极公共电源线供应的第一栅极公共电源gvss1供应到第二连接节点nc2。例如,第三十八tft t38可以基于具有高电压电平的外部感测复位信号srst导通并且可以将第一栅极公共电源gvss1输出到第二连接节点nc2。

300.第三十九tft t39可以响应于外部感测复位信号srst而将第二连接节点 nc2电连接到第一控制节点线q。例如,第三十九tft t39可以基于具有高电压电平的外部感测复位信号srst而导通并且可以提供通过第三十八tft t38 和第二连接节点nc2提供的第一栅极公共电源gvss1,到第一个控制节点线 q。

301.第三十八tft t38和第三十九tft t39之间的第二连接节点nc2可以电连接到第一连接节点nc1。因此,可以通过第一节点控制电路ncc1的第三 tft t3向第二连接节点nc2提供第一栅极驱动电源gvdd1。因此,第一节点控制电路ncc1的第三薄膜晶体管t3可以增加第六节点控制电路ncc6的第三十九薄膜晶体管t39的栅极电压与第二连接节点nc2的电压之间的电压差,以完全关断该电路。第三十九tft t39已经基于具有低电压电平的外部感测复位信号srst而被关断,因此可以通过关断来防止第一控制节点线q的压降 (或电流泄漏)第三十九tft t39,从而稳定地保持第一控制节点线q的电压。

302.图10是示出图8所示的节点复位电路、输出缓冲电路和第二感测控制电路的电路图。

303.参照图8和图10,根据实施方式的节点复位电路nrc可以保持第二控制节点线qbo和第三控制节点线qbe中的每一个的电压电平,而第一控制节点线q的电压具有高电压电平。

304.根据实施方式的节点复位电路nrc可以包括第十八至第二十三tft t18 至t23。

305.第十八tft t18可以响应于起始信号vst和正向驱动信号fws将第四连接节点nc4电连接到正向驱动信号线。作为实施方式,第十八tft t18可以基于具有高电压电平的启动信号vst导通并且可以向第四连接节点nc4提供正向驱动信号fws。

306.第十九tft t19可以响应于第四连接节点nc4的电压将第二控制节点线 qbo电连接到第一栅极公共电源线。作为一个实施方式,第十九薄膜晶体管 t19可以基于第四连接节点nc4的电压导通,并且可以在第二控制节点线qbo 和第一栅极公共电源线之间形成电流路径以释放第二控制节点的电压。节点线 qbo连接到第一栅极公共电源线,从而将第二控制节点线qbo的电压重置为第一栅极公共电源gvss1的电压电平。

307.响应于第二控制节点线qbo的电压,第二十tft t20可以将第四连接节点nc4电连接到第一栅极公共电源线。作为一个实施方式,第二十薄膜晶体管t20可以基于第二控制节

点线qbo的高电压电平而导通,并且可以在第四连接节点nc4和第一栅极公共电源线之间形成电流通路以释放控制节点线 qbo的电压。第四连接节点nc4连接到第一栅极公共电源线,从而将第四连接节点nc4的电压重置为第一栅极公共电源gvss1的电压电平。相应地,当第二控制节点线qbo的电压为高电平时,第二十薄膜晶体管t20可以将第四连接节点nc4的电压重置为第一栅极公共电源gvss1的电压电平,以关闭第十九薄膜晶体管t19。,从而可以防止第二控制节点线qbo的电压通过第十九tft t19放电到第一栅极公共电源线。

308.第二十一tft t21可以响应于复位信号vrst和反向驱动信号bws而将第四连接节点nc4电连接到反向驱动信号线。作为实施方式,第二十一tft t21 可以基于具有高电压电平的复位信号vrst被导通并且可以向第四连接节点 nc4提供具有高电压电平的反向驱动信号bws。

309.第二十二tft t22可以响应于第四连接节点nc4的电压将第三控制节点线qbe电连接到第一栅极公共电源线。作为一个实施方式,第二十二tft t22 可以基于第四连接节点nc4的电压导通,并且可以在第三控制节点线qbe和第一栅极公共电源线之间形成电流通路,以释放连接节点nc4的电压。第三控制节点线qbe连接到第一栅极公共电源线,从而将第三控制节点线qbe的电压重置为第一栅极公共电源gvss1的电压电平。

310.第二十三tft t23可以响应于第三控制节点线qbe的电压将第四连接节点nc4电连接到第一栅极公共电源线。作为一个实施方式,第二十三薄膜晶体管t23可以基于第三控制节点线qbe的高电压电平导通,并且可以在第四连接节点nc4和第一栅极公共电源线之间形成电流通路以释放电压。将第四连接节点nc4的电压连接到第一栅极公共电源线,从而将第四连接节点nc4 的电压重置为第一栅极公共电源gvss1的电压电平。相应地,当第三控制节点线qbe的电压为高电平时,第二十三薄膜晶体管t23可以将第四连接节点 nc4的电压重置为第一栅极公共电源gvss1的电压电平,以关闭二十-第二tftt22,从而可以防止第三控制节点线qbe的电压通过第二十二tft t22放电到第一栅极公共电源线。

311.第十九tft t19和第二十二tft t22可以基于第四连接节点nc4的电压同时导通或截止。

312.作为一个实施方式,在栅极驱动电路150的正向扫描驱动中,第十九薄膜晶体管t19和第二十二薄膜晶体管t22可以基于提供给第四连接节点nc4的正向驱动信号fws的高电平同时导通。通过第十八tft t18基于具有高电压电平的启动信号vst导通,并且可以基于提供给第四连接节点nc4的第一栅极公共电源gvss1同时截止,通过第二十tft t20基于高电平导通第二控制节点线qbo的电压电平可以同时关断,也可以根据通过第二十三tft t23提供给第四连接节点nc4的第一栅极公共电源gvss1同时关断,根据第三控制节点的高电压电平导通线qbe。

313.作为另一实施方式,在栅极驱动电路150的反向扫描驱动中,第十九薄膜晶体管t19和第二十二薄膜晶体管t22可以基于提供给第四连接节点nc4的反向驱动信号bws的高电平同时导通。通过第二十一tft t21基于具有高电压电平的复位信号vrst导通并且可以基于通过第二十三tft t23导通提供给第四连接节点nc4的第一栅极公共电源gvss1而同时截止基于第三控制节点线qbe的高电压电平,或者可以基于通过第二十tft t20提供给第四连接节点nc4的第一栅极公共电源gvss1同时关断,基于第二控制节点线的高电压电平导通。控制节点线qbo。

314.输出缓冲电路obc可以接收进位时钟cclk、奇数扫描时钟sclko、偶数扫描时钟sclke、第一栅极公共电源gvss1、第二栅极公共电源gvss2和第三栅极公共电源gvss3和可以响应于每个的电压,基于进位时钟cclk、扫描时钟sclk和第三栅极公共电源gvss3输出第i个扫描信号ssi、第i+1个扫描信号ssi+1和第i个进位信号csi。第一至第三控制节点线q、qbo和qbe。例如,当第一控制节点线q的电压为高电平时,输出缓冲电路obc可以输出对应进位时钟cclk的第i个进位信号csi,对应奇数扫描的第i个扫描信号 ssi。时钟sclko,以及对应偶数扫描时钟sclke的第i+1个扫描信号ssi+1。

315.根据实施方式的输出缓冲电路obc可以包括第一至第三输出缓冲电路 obc1至obc3。

316.第一输出缓冲电路obc1可以基于第一至第三控制节点线中的每一个的电压输出具有奇数扫描时钟sclko的电压电平或第三栅极公共电源gvss3的电压电平的第i扫描信号ssi q、qbo和qbe。

317.根据实施方式的第一输出缓冲电路obc1可以包括第二十四至第二十六 tft t24至t26和耦合电容器cc。

318.第二十四tft t24(或第一上拉tft)可以基于第一控制节点线q的电压通过第一输出节点no1将奇数扫描时钟sclko传输到第i栅极线gli。例如,第二十四tft t24可以包括连接到第一控制节点线q的栅电极、连接到第一输出节点no1的第一源/漏电极和连接到奇数扫描时钟的第二源/漏电极线。

319.第二十五tft t25(或奇数第一下拉tft)可以基于第二控制节点线qbo 的电压通过第一输出节点no1将第三栅极公共电源gvss3传输到第i栅极线 gli。例如,第二十五tft t25可以包括连接到第二控制节点线qbo的栅电极、连接到第一输出节点no1的第一源/漏电极和连接到第三栅极公共电源线的第二源/漏电极。。

320.第二十六tft t26(或者甚至第一下拉tft)可以基于第三控制节点线 qbe的电压通过第一输出节点no1将第三栅极公共电源gvss3传输到第i栅极线gli。例如,第二十六tft t26可以包括连接到第三控制节点线qbe的栅电极、连接到第一输出节点no1的第一源/漏电极和连接到第三栅极公共电源线的第二源/漏电极。

321.耦合电容器cc可以形成在第一控制节点线q和第一输出节点no1之间。例如,耦合电容cc可以是第二十四薄膜晶体管t24的栅极与第一输出节点 no1之间的寄生电容。基于奇数扫描时钟sclko的相移(或变化),耦合电容器cc可以允许自举发生在第一控制节点线q中。因此,当奇数扫描时钟 sclko从低电压电平转变为高电压电平时,第一控制节点线q的电压可以通过奇数扫描时钟的高电压电平被提升到更高的电压。时钟sclko基于由耦合电容器cc和具有高电压电平的奇数扫描时钟sclko之间的耦合引起的自举。例如,当具有高电压电平的奇数扫描时钟sclko被提供给第二十四tft t24 的第二源/漏电极时,第一控制节点线q的电压预充电有电压电平第一节点控制电路ncc1的正向驱动信号fws可以被提升到更高的电压,因此,第二十四tft t24可以完全导通,并且可以提供具有高电压电平的奇数扫描时钟 sclko作为第i扫描信号ssi,第i栅极线gli通过第一输出节点no1和导通的第二十四tft t24而没有电压损失。

322.第二输出缓冲电路obc2可以基于第一至第三栅极公共电源gvss3中的每一个的电压输出具有偶数扫描时钟sclke的电压电平或第三栅极公共电源 gvss3的电压电平的第i+

1扫描信号ssi+1。第三控制节点线q、qbo和qbe。

323.根据实施方式的第二输出缓冲电路obc2可以包括第二十七至第二十九 tft t27至t29。

324.第二十七tft t27(或第二上拉tft)可以基于第一控制节点线的电压通过第二输出节点no2将偶数扫描时钟sclke传输到第i+1栅极线gli+1q,例如,第二十七tft t27可以包括连接到第一控制节点线q的栅电极、连接到第二输出节点no2的第一源/漏电极和连接到偶数的第二源/漏电极。-编号的扫描时钟线。第二十七tft t27可以基于第一控制节点线q的自举电压导通,因此可以传输通过偶数扫描时钟线提供的具有高电压电平的偶数扫描时钟 sclke,作为第i+1扫描信号ssi+1通过第二输出节点no2到达第i+1栅极线gli+1而没有电压损失。

325.第二十八tft t28(或奇数第二下拉tft)可以基于第二控制节点线的电压通过第二输出节点no2将第三栅极公共电源gvss3传输到第i+1栅极线 gli+1qbo。例如,第二十八薄膜晶体管t28可以包括连接到第二控制节点线qbo的栅电极、连接到第二输出节点no2的第一源/漏电极和连接到第三栅极公共电源线的第二源/漏电极。。

326.第二十九tft t29(或偶数第二下拉tft)可以基于第三控制节点线的电压通过第二输出节点no2将第三栅极公共电源gvss3传输到第i+1栅极线 gli+1qbe。例如,第二十九薄膜晶体管t29可以包括与第三控制节点线qbe 连接的栅极、与第二输出节点no2连接的第一源/漏电极和与第三栅极公共电源线连接的第二源/漏电。。

327.第三输出缓冲电路obc3可以基于第一至第三控制节点线q、qbo和qbe 中的每一个的电压输出具有进位时钟cclk的电压电平或第一栅极公共电源 gvss1的电压电平的第i进位信号csi。

328.根据实施方式的第三输出缓冲电路obc3可以包括第三十至三十第二 tft t30至t32。

329.第三十tft t30(或第三上拉tft)可以基于第一控制节点线q的电压通过第三输出节点no3输出作为第i进位信号csi的进位时钟cclk。例如,第三十tft t30可以包括连接到第一控制节点线q的栅电极、连接到第三输出节点no3的第一源/漏电极和连接到进位时钟线的第二源/漏电极。第三十 tft t30可以基于第一控制节点线q的自举电压导通,并且可以输出具有高电压电平的进位时钟cclk作为第i进位信号csi,其具有高电压电平,通过进位时钟线,通过第三个输出节点no3没有电压损失。

330.第三十一tft t31(或奇数第三下拉tft)可以基于第二控制节点线qbo 的电压通过第三输出节点no3输出第一栅极公共电源gvss1作为第i进位信号csi。例如,第三十一薄膜晶体管t31可以包括连接到第二控制节点线qbo 的栅电极、连接到第三输出节点no3的第一源/漏电极和连接到第一栅极公共电源线的第二源/漏电极。

331.第三十二tft t32(或什至第三下拉tft)可以基于第三控制节点线qbe 的电压通过第三输出节点no3输出第一栅极公共电源gvss1作为第i个进位信号csi。例如,第三十二tft t32可以包括连接到第三控制节点线qbe的栅电极、连接到第三输出节点no3的第一源/漏电极和连接到第一栅极公共电源线的第二源/漏电极。

332.或者,耦合电容器cc可以形成在第一控制节点线q和第三输出节点no3 之间。此外,耦合电容器cc可以形成在第一控制节点线q和第一输出节点 no1之间的区域、第一控制

节点线q和第二输出节点no2之间的区域以及之间的区域中的至少一个中。第一控制节点线q和第三输出节点no3。

333.第二感测控制电路scc2可以被实现为响应于第四控制节点线qm的电压和外部感测控制信号scs而对第二控制节点线qbo和第三控制节点线qbe中的每一个的电压进行放电。

334.根据实施方式的第二感测控制电路scc2可以包括第一节点放电电路 ndc1和第二节点放电电路ndc2。

335.第一节点放电电路ndc1可以响应于第四控制节点线qm的电压和外部感测控制信号scs对第二控制节点线qbo的电压进行放电。作为一个实施方式,第一节点放电电路ndc1可以响应于具有高电压电平的第四控制节点线qm的电压和具有高电压电平,从而可以将第二控制节点线qbo的电压放电到第一栅极公共电源线或者可以将第二控制节点线qbo的电压重置为第一栅极公共电源gvss1。

336.根据实施方式的第一节点放电电路ndc1可以包括第四十tft t40和第四十一tft t41。

337.第四十tft t40可以响应于第四控制节点线qm的电压将第一栅极公共电源gvss1传输到第四十一tft t41。作为一个实施方式,第四十薄膜晶体管 t40可以基于第四控制节点线qm的高电压电平导通,并且可以在第四十一薄膜晶体管t41和第一栅极公共电源gvss1之间形成电流通路。

338.响应于外部感测控制信号scs,第四十一tft t41可以将第二控制节点线 qbo电连接到第四十tft t40。作为一个实施方式,第四十一薄膜晶体管t41 可以基于具有高电压电平的外部感测控制信号scs导通并且可以在第二控制节点线qbo和第四十薄膜晶体管t40之间形成电流路径。在基于第四控制节点线qm的高电压电平导通第四十tft t40的状态下,可以基于具有高电压电平的外部感测控制信号scs导通第四十一tft t41,因此如图所示,第二控制节点线qbo的电压可以通过第四十一个tft t41和第四十个tft t40中的每一个被放电到第一栅极公共电源线或者可以被重置为第一栅极公共电源 gvss1。

339.第二节点放电电路ndc2可以响应于第四控制节点线qm的电压和外部感测控制信号scs对第三控制节点线qbe的电压进行放电。作为一个实施方式,第二节点放电电路ndc2可以响应于具有高电压电平的第四控制节点线qm的电压和具有高电压电平,从而可以将第三控制节点线qbe的电压放电到第一栅极公共电源线或者可以将第三控制节点线qbe的电压重置为第一栅极公共电源gvss1

340.根据实施方式的第二节点放电电路ndc2可以包括第四十二tft t42和第四十三tft t43。

341.第四十二tft t42可以响应于第四控制节点线qm的电压将第一栅极公共电源gvss1传输到第四十三tft t43。作为一个实施方式,第四十二tft t42 可以基于第四控制节点线qm的高电压电平导通并且可以在第四十三tft t43 和第一栅极公共电源gvss1之间形成电流路径。

342.响应于外部感测控制信号scs,第四十三tft t43可以将第三控制节点线 qbe电连接到第四十二tft t42。作为一个实施方式,第四十三薄膜晶体管 t43可以基于具有高电压电平的外部感测控制信号scs导通并且可以在第三控制节点线qbe和第四十二薄膜晶体管

t42之间形成电流路径。在基于第四控制节点线qm的高电压电平导通第四十二tft t42的状态下,可以基于具有高电压电平的外部感测控制信号scs导通第四十三tft t43,因此,第三控制节点线qbe的电压可以通过第四十三层薄膜晶体管t43和第四十二层薄膜晶体管t42分别放电至第一栅极公共电源线或复位至第一栅极公共电源gvss1。

343.或者,可以与第一感测控制电路scc1一起省略第二感测控制电路scc2。即,第一感测控制电路scc1和第二感测控制电路scc2中的每一个可以是用于基于像素的外部感测模式来感测设置在像素的子像素中的驱动tft的特征值的电路,并且当像素没有在外部感测模式下被驱动时,第一感测控制电路 scc1和第二感测控制电路scc2中的每一个都可能是不期望的元件,因此可能被省略。

344.图1和2中所示的第一至第四十三tft t1至t43。图9和图10所示的多个分支电路1511至151n可以分别设置(或分布式设置)在显示区域aa的一条水平线上,并且可以通过分支网络153相互连接,因此,可以配置图15所示的多个分支电路1511至151n.5.例如,每一级电路单元1501至150m可包括第一至第n(其中n为43)分支电路1511至151n,其中布置或提供第一至第四十三tft t1至t43中的一个,但实施方式本公开的实施方式不限于此,并且多个分支电路1511至151n中的每一个可以基于布置在一条水平线上的像素的数量用第一至第四十三tft t1至t43中的至少一个来实现。

345.此外,在图1和图2所示的级电路单元150i中。参照图8至图10,当第一开关tft tsw1和第二开关tft tsw2设置在图1所示的多个子像素sp1至 sp4中的每一个的像素电路pc中时,图4所示的扫描信号基于不同的第一和第二扫描信号而导通,第i个扫描信号ssi可以用作通过奇数栅极线glo的第一条栅极线和第i+1个扫描信号ssi+1提供的第一扫描信号可以用作通过偶数栅极线gle的第一栅极线提供的第一扫描信号。因此,图1和图2所示的级电路单元150i的输出缓冲电路obc。图8至图10还可以包括第四输出缓冲电路和第五输出缓冲电路。

346.第四输出缓冲电路可以被实施为向奇数栅极线glo的第二栅极线输出第二扫描信号,第五输出缓冲电路可以被实施为向偶数栅极线gle的第二栅极线输出第二扫描信号。

347.根据实施方式的第四输出缓冲电路可以基于第一至第二扫描时钟中的每一个的电压输出具有第二扫描奇数扫描时钟的电压电平或第三栅极公共电源 gvss3的电压电平的第i个第二扫描信号。第三控制节点线q、qbo和qbe。除了第四输出缓冲电路基于第二扫描奇数扫描时钟输出第i个第二扫描信号之外,第四输出缓冲电路可以包括三个tft,与图1所示的第一输出缓冲电路 obc1的tft基本相同。如图。参照图10,因此省略其详细描述。

348.根据实施方式的第五输出缓冲电路可以基于每个的电压输出具有第二扫描偶数扫描时钟的电压电平或第三栅极公共电源gvss3的电压电平的第i+1 个第二扫描信号。第一至第三控制节点线q、qbo和qbe。除了第五输出缓冲电路基于第二扫描偶数扫描时钟输出第i+1个第二扫描信号外,第五输出缓冲电路可以包括与第二输出缓冲电路obc2基本相同的三个tft如图所示。参照图10,因此省略其详细描述。

349.在图1和图2所示的级电路单元150i中。参照图8和图10,奇数扫描时钟sclko可以被称为第一扫描奇数扫描时钟,偶数扫描时钟sclke可以被称为第一扫描偶数扫描时钟。例如,第一扫描扫描时钟和第二扫描扫描时钟可以具有相同的相位或不同的相位。此外,第一扫描扫描时钟和第二扫描扫描时钟可以具有相同的时钟宽度或不同的时钟宽度。

350.如图。图11是图示根据图10和10中图示的本公开的实施方式的分支网络和附加模式的图。参照图5和8至10,图。图12a是沿图12中所示的线i-i' 截取的截面图。11,图。图12b是沿图12b所示的线ii-ii'截取的截面图。11,和图。图12c是沿图12c中所示的线iii-iii'截取的截面图。11.

351.参考图。参照图5和图8至图11,在根据本公开实施方式的显示装置中,栅极驱动电路150的分支网络153可以设置在限定(例如,定位)在一侧的网络线形成部分nfp处。沿第一方向x布置的多个像素p中的每一个的像素。

352.网络线形成部分nfp可以包括平行于第一方向x或平行于栅极线gl的多个线形成区a1至a4。根据实施方式的网络线路形成部分nfp可以包括第一至第四线路形成区域a1至a4。例如,第一至第四线形成区a1至a4中的第一线形成区a1可以最靠近栅极线gl。

353.根据实施方式,包括在分支网络153中的网络线nl和第一到第三控制节点线q、qbo和qbe可以分别设置在第一到第四线形成区域a1到a4处。例如,第一控制节点线q可以设置在第一线形成区域a1,网络线nl可以设置在第二线形成区域a2,第四控制节点线qbm可以设置在第三线形成区域a3,第二控制节点线qbo可以设置在第四线形成区a4。例如,网络线路形成部分 nfp还可以包括第五线路形成区域,其中设置第三控制节点线qbe。第五线形成区可以设置在第三线形成区a3和第四线形成区a4之间。

354.布置在一条水平线上的多个像素p可以基于布置在一条水平线上的控制节点线q、qbo和qm以及网络线nl的数量被划分(或分类)为第一像素 p1、第二像素p2和第三像素p3栅极驱动电路的网络线形成部分nfp或分支网络153。例如,第一像素(或第一像素组)p1、第二像素(或第二像素组) p2以及第三像素(或第三像素组)p3中的每一个可以包括多个不同数量的网络线nl。网络线nl。例如,布置在第一像素p1、第二像素p2和第三像素 p3中的每一个的网络线形成部分nfp处的分支网络153的线数可以不同。

355.在分支网络153中,第一和第二控制节点线q和qbo中的每一个都可以布置在第一像素p1、第二像素p2和第三像素p3的所有处。第四控制节点线 qm可以设置在所有第二像素p2和第三像素p3处。网络线nl可以设置在第三像素p3处。

356.根据实施方式,第一像素p1可以包括分别设置在第一和第四线形成区域 a1和a4处的第一和第二控制节点线q和qbo。第二像素p2可以包括分别设置在第一、第三和第四线形成区域a1、a3和a4处的第一、第三和第四控制节点线q、qbo和qm。第三像素p3可以包括分别设置在第一至第四线形成区域a1至a4处的第一、第三和第四控制节点线q、qbo和qm以及网络线 nl。

357.布置在第一像素p1、第二像素p2和第三像素p3中的每一个处的线以及这些线的数量不限于图1所示的线的数量。11.例如,当分支网络153包括z(其中z是4或更多的自然数)条线时,网络线形成部分nfp可以包括第一至第z 线形成区域。在这种情况下,第一像素p1可以包括x(其中x是小于z的自然数)条线,其布置在第一至第z线形成区域的x个线形成区域处,第二像素p2 可以包括y(其中y是小于x的自然数)设置在第一到第z线形成区域的y个线形成区域处的线数,并且第三像素p3可以包括设置在第一到第z线形成区域的z个线.

358.第一像素p1和第二像素p2中的每一个的网络线形成部分nfp可以包括未布置网络线nl的线非布置区域lua(或空白空间)。例如,第一像素p1 处的线非布置lua可以是第二和第三线形成区域a2和a3。第二像素p2处的线非布置lua可以是第二线形成区域a2。

359.在根据本公开实施方式的显示装置10中,由于网络线形成部nfp的线非配置区域lua设置在每条水平线处,分支网络153的交叉线数量的偏差参考电压线rl可能发生,因此,由于参考电压线rl之间的线电容偏差,可能会发生提供给参考电压线rl的参考电压的偏差或通过参考电压线rl感测的感测原始数据的偏差用于像素p1、p2和p3中的每一个的电压线rl。例如,当通过参考电压线rl感测到的感测原始数据发生偏差时,会降低基于子像素的感测行数据的准确性,并且感测原始数据对应于驱动薄膜晶体管(tft)的特性变化。)的每个子像素可能无法准确感测。为了防止、减小或最小化参考电压线rl之间的线电容偏差,根据本公开实施方式的显示装置10或栅极驱动电路150还可以包括附加图案部分155。例如,附加图案部分155可以是补偿图案部分、虚拟图案部分、电容补偿图案部分、辅助图案部分或偏差补偿图案部分。

360.附加图案部分155可以设置在网络线形成部分nfp处以与分别设置在多个像素p中的一些像素p处的参考电压线rl重叠。附加图案部分155可以不电耦合到多个分支中的每一个电路1511至151n。

361.添加图案部分155可以被实现为补偿、减小或最小化设置在第一像素p1 处的参考电压线rl的线电容与设置在第三像素p3处的参考电压线rl的线电容之间的偏差并且可以是实施以补偿、减小或最小化设置在第二像素p2处的参考电压线rl的线电容与设置在第三像素p3处的参考电压线rl的线电容之间的偏差。

362.根据实施方式,附加图案部分155可以被实现为在第一像素p1和第二像素p2的每一个处具有不同的尺寸。例如,基于参考电压线rl和分支之间的重叠面积,附加图案部分155可以与参考电压线rl重叠以在第一像素p1和第二像素p2的每一个处具有不同的尺寸(或面积)。网络153在每个第三像素p3处。因此,在第一像素p1和第二像素p2中的每一个中,参考电压线rl 与分支网络153和附加图案部分155中的每一个之间的重叠区域的大小(或重叠区域的大小)可以与参考电压线rl与分支网络153在第三像素p3处的重叠区域的大小相同。

363.根据实施方式,附加图案部分155可以布置在第一像素p1和第二像素p2 中的每一个的线非布置区域lua处以与参考电压线rl重叠。例如,附加图案部分155可以被实现为与参考电压线rl重叠并且在第一像素p1和第二像素p2中的每一个的线非布置区域lua处具有不同的尺寸(或面积)。

364.根据实施方式,附加图案部分155可以补偿分别设置在多个像素p处的参考电压线rl之间的线电容偏差。例如,附加图案部分155可以补偿参考电压线rl之间的线电容偏差。参考电压线rl设置在第一像素p1和第二像素p2 中的每一个处,并且参考电压线rl的线电容设置在第三像素p3处。

365.根据实施方式的附加图案部分155可以包括设置在每个第一像素p1处的第一附加图案155a和设置在每个第二像素p2处的第二附加图案155b。例如,第一附加图案155a可以是第一补偿图案、第一虚拟图案部分、第一电容补偿图案部分、第一辅助图案部分或第一偏差补偿图案部分。第二附加图案155b 可以是第二补偿图案、第二虚拟图案部分、第二电容补偿图案部分、第二辅助图案部分或第二偏差补偿图案部分。

366.参考图。参照图11和12a,第一附加图案155a可以布置在网络线形成部分nfp的线非布置区域lua处以与布置在第一像素p1处的参考电压线rl 重叠。例如,第一附加图案

155a可以设置在第一线形成区a1和第四线形成区a4之间的第二和第三线形成区a2和a3处以与参考电压线rl重叠。

367.第一附加图案155a可以电耦合到设置在相邻的线形成区a1和a4处的线 q和qbo之一。根据实施方式的第一附加图案155a可以从设置在相邻线形成区域a1和a4处的线q和qbo之一延伸或突出以与参考电压线rl重叠。作为实施方式,第一附加图案155a可以从设置在第一线形成区a1处的第一控制节点线q向第四线形成区a4延伸或突出以与参考电压线rl重叠。作为另一实施方式,第一附加图案155a可以从设置在第四线形成区a4处的第二控制节点线qbo向第一线形成区a1延伸或突出以与参考电压线rl重叠。

368.关于第一方向x,第一附加图案155a可以具有比参考电压线rl宽的宽度。第一附加图案155a和第一像素p1的参考电压线rl之间的重叠区域的尺寸可以等于或对应于从分支网络153和参考电压之间的重叠区域的大小减去分支网络153和第一像素p1的参考电压线rl之间的重叠区域的大小获得的大小。第三像素p3的线rl。因此,第一附加图案155a可以与参考电压线rl 重叠,并且因此可以补偿、减小或最小化设置在第一像素p1处的参考电压线 rl的线电容与参考电压线的线电容之间的偏差。rl设置于第三像素p3。

369.参照图11和12b,第二附加图案155b可以布置在网络线形成部分nfp 的线非布置区域lua处以与布置在第二像素p2处的参考电压线rl重叠。例如,第二附加图案155b可以设置在第一线形成区a1和第三线形成区a3之间的第二线形成区a2处以与参考电压线rl重叠。

370.第二附加图案155b可以具有与第一附加图案155a不同的尺寸(或面积)。例如,第二附加图案155b可以具有小于第一附加图案155a的尺寸(或面积)。

371.第二附加图案155b可以电耦合到设置在相邻的线形成区a1和a3处的线 q和qm之一。根据实施方式的第二附加图案155b可以从设置在相邻线形成区域a1和a3处的线q和qm之一延伸或突出以与参考电压线rl重叠。作为实施方式,第二附加图案155b可以从设置在第一线形成区a1处的第一控制节点线q向第三线形成区a3延伸或突出以与参考电压线rl重叠。作为另一实施方式,第二附加图案155b可以从设置在第三线形成区a3处的第四控制节点线qm向第一线形成区a1延伸或突出以与参考电压线rl重叠。

372.相对于第一方向x,第二附加图案155b可以具有比参考电压线rl宽的宽度。第二附加图案155b和第二像素p2的参考电压线rl之间的重叠区域的尺寸可以等于或对应于从分支网络153和参考电压之间的重叠区域的大小减去分支网络153和第二像素p2的参考电压线rl之间的重叠区域的大小获得的大小。第三像素p3的线rl。因此,第二附加图案155b可以与参考电压线 rl重叠,从而可以补偿、减小或最小化设置在第二像素p2处的参考电压线 rl的线电容与参考电压线的线电容之间的偏差。rl设置于第三像素p3。

373.参照图11和12a至12c,多条参考电压线rl可以设置在第一衬底100 的第一表面100a之上并且可以被设置在第一衬底100之上的至少一个缓冲层 101覆盖。

374.分支网络153和附加图案155可以设置在缓冲层101上方。分支网络153 和附加图案155中的每一个可以设置在缓冲层101上方,栅极绝缘层102位于其间。此外,分支网络153和附加图案155可以被设置在第一衬底100上方的层间绝缘层103、钝化层104和平坦化层105覆盖。例如,可以省略钝化层104。

375.根据本公开的实施方式,布置在一条水平线上的第一像素p1、第二像素 p2和第三像素p3的第一像素p1和第二像素p2中的每一个可以包括布置在一条水平线上的附加图案

155。网络线形成部分nfp的线非布置区域lua,因此,可以补偿、减小或最小化布置在第一像素p1、第二像素p2和第二像素 p2中的每一个处的参考电压线rl之间的线电容偏差。第三个像素p3。因此,可以补偿、减少或最小化通过参考电压线rl提供给对应像素p的参考电压的偏差,以及由参考电压线rl之间的线电容偏差引起的基于子像素的感测原始数据的偏差。可以减少或最小化,从而可以提高基于子像素的感测原始数据的准确性。因此,在外部感测模式下,根据本公开实施方式的显示装置10可以更准确地感测与每个子像素的驱动tft的特性变化相对应的感测原始数据。

376.图13是图示图5和图8至图10图示的本公开的另一个实施方式的分支网络和附加模式的图,并且图示了通过修改图11.中图示的附加图案而实现的实施方式。因此,在以下描述中,省略了除了附加图案之外的元素和相关元素的重复描述。沿图12c中所示的线iii-iii'截取的截面图示出在图13中.

377.参照图12c和13,根据本公开另一实施方式的附加图案155可以包括设置在每个第一像素p1处的第一附加图案155a和设置在每个第二像素p2处的第二附加图案155b。

378.第一附加图案155a可以包括多条第一附加图案线155a1。根据本公开实施方式的第一附加图案155a可以包括两条第一附加图案线155a1。

379.两条第一附加图案线155a1中的每一条可以布置在网络线形成部分nfp 的线非布置区域lua处的第二和第三线形成区域a2和a3中的每一个处,以与布置在第一像素处的参考电压线rl重叠p1。两条第一附加图案线155a1 中的每条可以与设置在网络线形成部分nfp处以与参考电压线rl重叠的其他线q、qbo、qm和nl中的每条具有相同的线宽。两条第一附加图案线155a1 中的每一条可以与第一控制节点线q和第二控制节点线qbo中的每一条间隔开并且可以沿着第二方向y与其间隔开。因此,两条第一附加图案中的每一条都可以线155a1可以与参考电压线rl重叠,因此可以补偿、减小或最小化设置在第一像素p1处的参考电压线rl的线电容与设置在第三像素p3处的参考电压线rl的线电容之间的偏差。

380.第一附加图案155a还可以包括多个第一连接图案155a2。根据本公开实施方式的第一附加图案155a还可包括两个第一连接图案155a2。

381.两个第一连接图案155a2可以将两个第一附加图案线155a1中的每一个电连接到设置在相邻的线形成区域a1和a4处的线q和qbo之一。两个第一连接图案155a2可以不与参考电压线rl重叠。作为实施方式,两个第一连接图案155a2可以从设置在第一线形成区域a1处的第一控制节点线q向第四线形成区域a4突出或延伸,并且可以电耦合到两个第一连接图案中的每一个的两端。附加图案线155a1。作为另一实施方式,两个第一连接图案155a2可以从设置在第四线形成区a4处的第二控制节点线qbo向第一线形成区a1突出或延伸,并且可以电耦合到两个第一线形成区a1中的每一个的两端。第一附加图案线155a1。因此,两条第一附加图案线155a1中的每一条可通过两条第一连接图案155a2电耦合至第一控制节点线q(或第二控制节点线qbo),从而可具有与第一连接图案相同的电位。控制节点线q(或第二控制节点线qbo)。

382.第二附加图案155b还可包括至少一个第二附加图案155b1。例如,第二附加图案155b可以包括一个第二附加图案155b1。

383.一条第二附加图案线155b1可以布置在网络线形成部分nfp的线非布置区域lua中的第二线形成区域a2处以与布置在第二像素p2处的参考电压线 rl重叠。一条第一附加图

案线155b1可以具有与设置在网络线形成部分nfp 处以与参考电压线rl重叠的其他线q、qbo、qm和nl中的每条线相同的线宽。一条第二附加图案线155b1可以与第一控制节点线q和第二控制节点线qbo中的每一条间隔开。因此,一条第二附加图案线155b1可以与参考电压线rl重叠,从而可以补偿、减小或最小化设置在第二像素p2处的参考电压线rl的线电容与参考电压线rl的线电容之间的偏差。电压线rl设置在第三像素p3处。

384.第二附加图案155b还可以包括两个第二连接图案155b2。

385.两个第二连接图案155a2可以将一条第二附加图案线155b1电连接到设置在相邻的线形成区域a1和a3处的线q和qm之一。两个第二连接图案155b2 可以不与参考电压线rl重叠。作为实施方式,两个第二连接图案155b2可以从设置在第一线形成区域a1处的第一控制节点线q向第三线形成区域a3突出或延伸,并且可以电耦合到两个第二连接图案中的每一个的两端。附加图案线155b1。作为另一实施方式,两个第二连接图案155b2可以从设置在第三线形成区域a3处的第三控制节点线qm向第一线形成区域a1突出或延伸,并且可以电耦合到两个第二连接图案中的每一个的两端。第二附加图案线 155b1。因此,一条第二附加图案线155b1可以通过两个第二连接图案155b2 电耦合到第一控制节点线q(或第四控制节点线qm),从而可以具有与第一控制节点线等效的电位q(或第四控制节点线qm)。

386.此外,在图13中,已经描述了附加图案155包括包括设置在第一像素p1 处的两条第一附加图案线155a1的第一附加图案155a和包括设置在第二像素 p2处的两条第二附加图案线155b1的第二附加图案155b,但本公开的实施方式不限于此。例如,附加图案155的第一附加图案155a可以包括两条或更多条第一附加图案线155a1,使得第一像素p1处的网络线和参考电压线rl之间的重叠面积与重叠面积相同。第三像素p3处的网络线与参考电压线rl之间。同样地,附加图案155的第二附加图案155b可以包括一条或多条第二附加图案线155a1,其数量少于第一附加图案线155a1的数量,使得网络线和参考电压线rl之间的重叠区域第二像素p2处的重叠面积与第三像素p3处的网络线与参考电压线rl的重叠面积相同。

387.图14是图示图5和图8至图10中图示的本公开的另一个实施方式的分支网络和附加模式的图,并且图示了通过修改图11中图示的附加图案而实现的实施方式。因此,在以下描述中,省略了除了附加图案之外的元素和相关元素的重复描述。沿图12c中所示的线iii-iii'截取的截面图示出在图14中。

388.参照图12c和图14,根据本公开另一实施方式的附加图案155可以包括设置在每个第一像素p1处的两个第一附加图案155a和设置在每个第二像素 p2处的一个第二附加图案155b。

389.两个第一附加图案155a中的每一个可以设置在网络线形成部分nfp的线非设置区域lua中的第二和第三线形成区域a2和a3中的每一个处以与设置在第一像素p1处的参考电压线rl重叠.两个第一附加图案155a中的每一个可以具有与设置在网络线形成部分的第二和第三线形成区域a2和a3处的第四控制节点线qm和网络线nl中的每一个的线宽和尺寸相同的线宽和尺寸nfp 与参考电压线rl重叠。两个第一附加图案155a中的每一个可以与第一控制节点线q和第二控制节点线qbo中的每一个间隔开并且可以沿着第二方向y 与其间隔开。因此,两个第一附加图案线155a1中的每一个可以与参考电压线 rl重叠,因此可以补偿、减少或最小化设置在第一像素p1处的参考电压线 rl的线电容与设置在第三像素p3处的参考电压线rl的线电容之间的偏差.

390.两个第一附加图案155a中的每一个可以电耦合到设置在第一像素p1处的像素公共电压线cvl。例如,两个第一附加图案155a中的每一个可以通过穿过栅绝缘层102和覆盖设置在像素公共电压线cvl的缓冲层103的第一图案接触孔cha电耦合到像素公共电压线cvl。第一个像素p1。因此,两个第一附加图案155a中的每一个可以具有与像素公共电压线cvl相等的电势。

391.两个第二附加图案155b中的每一个可以设置在网络线形成部分nfp的线非设置区域lua中的第二线形成区域a2的每一个处,以与设置在第二像素 p2处的参考电压线rl重叠。一个第二附加图案155b可以具有与设置在网络线形成部分nfp的第二线形成区域a2处以与参考电压线rl重叠的网络线 nl的线宽和尺寸相同的线宽和尺寸。一个第二附加图案155b可以与第一控制节点线q和第四控制节点线qm中的每一个间隔开。因此,每条第二附加图案线155b可以与参考电压线rl重叠,并且因此可以补偿、减小或最小化设置在第二像素p2处的参考电压线rl的线电容和线电容之间的偏差。参考电压线rl设置在第三像素p3处。

392.一个第二附加图案155b可以电连接到设置在第二像素p2处的像素公共电压线cvl。例如,一个第一附加图案155b可以通过穿过栅绝缘层102和覆盖设置在第二附加图案处的像素公共电压线cvl的缓冲层103的第二图案接触孔chb电耦合到像素公共电压线cvl。因此,一第二附加图案155b可以具有与像素公共电压线cvl等效的电势。

393.此外,根据本公开的实施方式,由于附加图案155电耦合到像素公共电压线cvl,像素公共电压线cvl的线电阻可以降低,因此,像素公共电压线的电压降提供给像素公共电压线cvl的电压可以降低或最小化。

394.此外,在图14中,已经描述了附加图案155电耦合到像素公共电压线 cvl,但是本公开的实施方式不限于此。如图15所示,附加图案155可以电耦合到像素驱动电源线pl。

395.参照图15,两个第一附加图案155a中的每一个可以电耦合到设置在第一像素p1处的像素驱动电源线pl。例如,两个第一附加图案155a中的每一个可以通过穿过覆盖设置在第一像素p1处的像素驱动电源线pl的栅极绝缘层 102和缓冲层103的第一图案接触孔cha电耦合到像素驱动电源线pl。。因此,两个第一附加图案155a中的每一个可以具有与像素驱动电源线pl相等的电势。

396.一个第二附加图案155b可以电连接到设置在第二像素p2处的像素驱动电源线pl。例如,一个第一附加图案155b可以通过穿过栅绝缘层102和覆盖设置在第二附加图案处的像素驱动电源线pl的缓冲层103的第二图案接触孔 chb电耦合到像素驱动电源线pl。像素p2。因此,一第二附加图案155b可以具有与像素驱动电源线pl等效的电势。

397.因此,根据本公开的实施方式,当附加图案155电连接到像素驱动电源线 pl时,像素驱动电源线pl的线电阻可以降低,因此,像素公共端的电压降提供给像素驱动电源线pl的电压可以降低或最小化。

398.此外,在图参照图14和图15,已经描述了附加图案155包括设置在第一像素p1处的两个第一附加图案155a和设置在第二像素p2处的一个第二附加图案155b,但是本公开的实施方式不限于此.例如,附加图案155可以包括两个或更多个第一附加图案155a,使得第一像素p1处的网络线和参考电压线rl之间的重叠面积与网络线和参考电压线之间的重叠面积相同。第三像素p3 处的电压线rl。同样地,附加图案155可以包括一个或多个第二附加图案 155b,其数量少于第一附加图案155a的数量,使得网络线与参考电压线rl 在第二像素

p2处的重叠面积相同作为第三像素p3处的网络线与参考电压线 rl之间的重叠区域。

399.图16是示出了根据本公开实施方式的多屏幕显示装置的图,图16是示出了根据本公开的实施方式的多屏显示装置的示图。图17是沿图16所示的线 iv-iv'截取的截面图。图16和17示出了根据图1到图15所示的根据本公开的另一实施方式的发光显示装置的平铺实现的多屏幕显示装置。

400.参照图16和图17,根据本公开的实施方式的多屏幕显示装置(或拼接发光显示装置)可以包括多个显示装置dm1至dm4。

401.多个显示装置dm1至dm4可以各自显示单独的图像或者可以分开地显示一个图像。多个显示装置dm1至dm4中的每一个可以包括图1和图2所示的根据本公开实施方式的发光显示装置。与图1至15相同,因此省略或将简要给出它们的重复描述。

402.多个显示装置dm1至dm4可以平铺在单独的平铺框架上以在其侧表面彼此接触。例如,多个显示装置dm1至dm4可以平铺成具有n

×

m形式,从而实现具有大屏幕的多屏显示装置。例如,n为1以上的正整数,m为2 以上的正整数,但本公开的实施方式不限于此,例如,n为2以上的正整数, m为1或更大的正整数。

403.多个显示装置dm1至dm4中的每一个可以不包括围绕显示图像的所有显示区域aa的边框区域(或非显示部分),并且可以具有空气边框结构,其中显示区域aa被空气包围。例如,在多个显示装置dm1至dm4中的每一个中,第一基板100的第一表面的全部可以被实现为显示区域aa。

404.根据本公开的实施方式,在多个显示装置dm1至dm4中的每一个中,最外像素po的中心部分cp与第一基板100的最外表面vl之间的第二间隔 d2可以实现为为相邻像素之间的第一间隔d1(或像素间距)的一半或更小。因此,在基于横向耦合方式沿第一方向x和第二方向y在其侧表面彼此耦合(或接触)的两个相邻显示装置dm1至dm4中,相邻最外像素之间的间隔“d2+d2”面积pao可以等于或小于两个相邻像素之间的第一间隔d1。参照图17,在第一和第三显示装置dm1和dm3沿第二方向y在其侧表面处彼此耦合(或接触)中,第一显示器的最外像素po的中心部分cp之间的间隔“d2+d2”装置dm1和第三显示装置dm3的最外侧像素po的中心部分cp 可以等于或小于设置在第一和第三显示装置dm1中的每一个处的两个相邻像素之间的第一间隔d1(或像素间距)和dm3。

405.因此,沿第一方向x和第二方向y在其侧表面处彼此耦合(或接触)的两个相邻显示装置dm1至dm4的最外侧像素po的中心部分cp之间的间隔“d2+d2”可以相等设置在每个显示装置dm1至dm4处的两个相邻像素之间的第一间隔d1或小于第一间隔d1,因此,两个相邻显示装置dm1至dm4 之间不会有接缝或边界部分,从而不会有暗区由设置在显示装置dm1至 dm4之间的边界部分引起。结果,在多个显示装置dm1、dm2、dm3和dm4 以n

×

m形式平铺的多屏幕显示装置上显示的图像可以连续显示而没有断开 (或不连续)的感觉在多个显示装置dm1、dm2、dm3和dm4之间的边界部分。

406.在图15和图16中,示出了多个显示装置dm1至dm4以2

×

2的形式平铺,但是本公开的实施方式不限于此,多个显示装置dm1至dm4可以平铺成x

×

1形式、1

×

y形式或x

×

y形式。例如,在x

×

1形式中,x可以是大于或等于2的自然数,在1

×

y形式中,y可以是大于或等于2的自然数,而在x

×

y形式中,x和y可以是大于或等于2的自然数,并且可以彼此相等或不同。例如,在x

×

y形式中,x可以是大于或等于2且可以等于y的自然数,或者x和y可以是大于或

等于2且y大于或小于x的自然数.

407.在图15和图16中,示出了多个显示装置dm1至dm4以2

×

2的形式平铺,但是本公开的实施方式不限于此,多个显示装置dm1至dm4可以平铺成x

×

1形式、1

×

y形式或x

×

y形式。例如,在x

×

1形式中,x可以是大于或等于2的自然数,在1

×

y形式中,y可以是大于或等于2的自然数,而在x

×

y形式中,x和y可以是大于或等于2的自然数,并且可以彼此相等或不同。例如,在x

×

y形式中,x可以是大于或等于2且可以等于y的自然数,或者x和y可以是大于或等于2且y大于或小于x的自然数.

408.如上所述,当多个显示装置dm1至dm4中的每一个的显示区域aa是一个屏幕并且显示一个图像时,根据本公开的实施方式的多屏显示装置可以显示不断开的图像并且dm1至dm4在多个显示装置dm1至dm4之间的边界部分处是连续的,因此可以增强观看由多屏幕显示装置显示的图像的观看者的沉浸感。

409.下面将描述根据本公开的实施方式的显示装置和包括该显示装置的多屏幕显示装置。

410.根据本公开内容实施方式的显示装置,包括:显示区域,所述显示区域被配置成包括在基板上方沿着第一方向和与所述第一方向相交的第二方向布置的多个像素;设置在所述显示区域处且耦连至所述多个像素的多个栅极线、多个数据线、和多个基准电压线;和栅极驱动电路,所述栅极驱动电路被配置成包括多个级电路单元,所述多个级电路单元设置在所述显示区域处且耦连至所述多个栅极线中的每一者,其中所述多个级电路单元包括:沿着所述第一方向分开地设置在所述多个像素之间的多个分支电路;设置在网络线形成部处的分支网络,所述网络线形成部限定(例如,定位)在沿着所述第一方向设置的所述多个像素中的每一者的一侧处,所述分支网络包括多个控制节点线和选择性地耦连至所述多个分支电路的多个网络线;和附加图案部,所述附加图案部设置在所述网络线形成部处以交叠设置在所述多个像素中的一些各自处的基准电压线。

411.根据本公开内容的一些实施方式,所述多个像素可被分为第一像素、第二像素、和第三像素,所述第一像素和所述第二像素各自的一侧处限定的所述网络线形成部处设置的所述分支网络的线的数量可小于所述第三像素的所述网络线形成部处设置的所述分支网络的线的数量,并且所述附加图案部可设置在所述第一像素和所述第二像素各自的一侧处限定的所述网络线形成部处。

412.根据本公开内容的一些实施方式,所述基准电压线和设置在所述第一像素处的附加图案部之间的交叠区域的尺寸可不同于所述基准电压线和设置在所述第二像素处的附加图案部之间的交叠区域的尺寸。

413.根据本公开内容的一些实施方式,设置在所述第一像素的所述网络线形成部处的所述分支网络的线的数量可小于设置在所述第二像素的所述网络线形成部处的所述分支网络的线的数量,并且所述基准电压线和设置在所述第一像素处的附加图案部之间的交叠区域的尺寸可大于所述基准电压线和设置在所述第二像素处的附加图案部之间的交叠区域的尺寸。

414.根据本公开内容的一些实施方式,所述第一像素和所述第二像素各自的一侧处限定的所述网络线形成部可包括非线设置区域,并且所述附加图案部可设置在所述第一像素和所述第二像素各自的所述非线设置区域处以交叠所述第一像素和所述第二像素各自处

设置的基准电压线。

415.根据本公开内容的一些实施方式,所述附加图案部可包括:设置在所述第一像素的所述非线设置区域的第一附加图案;和设置在所述第二像素的所述非线设置区域以具有尺寸不同于所述第一附加图案的尺寸的第二附加图案。

416.根据本公开内容的一些实施方式,所述第二附加图案的尺寸可小于所述第一附加图案的尺寸。

417.根据本公开内容的一些实施方式,所述第一附加图案可被配置成从设置在所述第一像素处的所述多个控制节点线之一突出,并且所述第二附加图案可被配置成从设置在所述第二像素处的所述多个控制节点线之一突出。

418.根据本公开内容的一些实施方式,所述第一附加图案可包括与设置在所述第一像素处的基准电压线相交的多个第一附加图案,并且所述第二附加图案可包括与设置在所述第二像素处的基准电压线相交的多个第二附加图案。

419.根据本公开内容的一些实施方式,所述第一附加图案可进一步包括多个第一连接图案,所述多个第一连接图案被配置成将多个第一附加图案线电连接至设置在所述第一像素处的所述多个控制节点线之一,并且所述第二附加图案可进一步包括多个第二连接图案,所述多个第二连接图案被配置成将多个第二附加图案线电连接至设置在所述第二像素处的所述多个控制节点线之一。

420.根据本公开内容的一些实施方式,所述网络线形成部可包括第一至第z线形成区域,所述第一像素可包括设置在所述第一至第z线形成区域的x数量的线形成区域处的x(其中x是小于z的自然数)数量的线,所述第二像素可包括设置在所述第一至第z线形成区域的y数量的线形成区域处的y(其中y是小于x的自然数)数量的线,所述第三像素可包括设置在所述第一至第z线形成区域处的z数量的线,所述第一像素和所述第二像素各自可包括非线设置区域,并且所述附加图案部可设置在所述第一像素和所述第二像素各自的所述非线设置区域处以交叠设置在所述第一像素和所述第二像素各自处的所述基准电压线。

421.根据本公开内容的一些实施方式,所述附加图案和设置在所述第一像素处的所述基准电压线之间的交叠区域的尺寸可对应通过从所述分支网络和设置在所述第三像素处的所述基准电压线之间的交叠区域的尺寸减去所述分支网络和设置在所述第一像素处的所述基准电压线之间的交叠区域的尺寸而得到的尺寸,并且所述附加图案和设置在所述第二像素处的所述基准电压线之间的交叠区域的尺寸可对应通过从所述分支网络和设置在所述第三像素处的所述基准电压线之间的交叠区域的尺寸减去所述分支网络和设置在所述第二像素处的所述基准电压线之间的交叠区域的尺寸而得到的尺寸。

422.根据本公开内容的一些实施方式,所述显示装置可进一步包括设置在所述显示区域处且耦连至所述多个像素的多个像素驱动功率线和多个像素公共电压线,所述分支网络的线可与所述多个基准电压线、所述多个像素驱动功率线、和所述多个像素公共电压线相交,并且所述附加图案部可包括:多个第一附加图案,所述多个第一附加图案与设置在所述第一像素的所述非线设置区域处的所述多个数据线、所述基准电压线、所述像素驱动功率线、和所述像素公共电压线相交且设置在所述第一像素处,和多个第二附加图案,所述多个第二附加图案与设置在所述第二像素的所述非线设置区域处的所述多个数据线、所述基准电压线、所述像素驱动功率线、和所述像素公共电压线相交且设置在所述第二像素处。

423.根据本公开内容的一些实施方式,所述多个第一附加图案各自可电耦连至设置在所述第一像素处的所述像素驱动功率线或所述像素公共电压线,并且所述多个第二附加图案各自可电耦连至设置在所述第二像素处的所述像素驱动功率线或所述像素公共电压线。

424.根据本公开内容的一些实施方式,所述显示装置可进一步包括:覆盖设置在所述基板上的所述多个数据线、所述多个基准电压线、所述多个像素驱动功率线、和所述多个像素公共电压线的缓冲层;设置在所述缓冲层与所述多个栅极线、所述分支网络的线、和所述补偿图案部中的每一者之间的栅极绝缘层;和覆盖设置在所述缓冲层上方的所述多个栅极线、所述分支网络的线、和所述补偿图案部的层间绝缘层,所述多个第一附加图案和所述至少一个第二附加图案各自可通过穿过所述栅极绝缘层和所述缓冲层的图案接触孔电耦连至所述像素驱动功率线和所述像素公共电压线。

425.根据本公开内容的一些实施方式,所述显示区域的尺寸可与所述基板的尺寸相同。

426.根据本公开内容的一些实施方式,所述显示装置可进一步包括:包含设置在所述基板的一个周缘部处的多个第一焊盘的第一焊盘部件;包含交叠所述多个第一焊盘的多个第二焊盘的第二焊盘部件;和包括设置在所述基板的一个侧面处以将所述多个第一焊盘分别连接至所述多个第二焊盘的多个选路线的选路部。

427.根据本公开内容的一些实施方式,所述显示装置可进一步包括:包含设置在所述基板的一个周缘部处的多个第一焊盘的第一焊盘部件;包括含交叠所述多个第一焊盘的多个第二焊盘的第二焊盘部件的配线基板;设置在所述基板和所述配线基板之间的耦连元件;和包括设置在所述配线基板和所述基板各自的一个侧面处以将所述多个第一焊盘分别连接至所述多个第二焊盘的多个选路线的选路部。

428.根据本公开内容的一些实施方式的多屏幕显示装置可包括:沿着第一方向和与所述第一方向相交的第二方向中的至少一个方向设置的多个显示装置,所述多个显示装置各自可包括显示装置,并且所述显示装置可包括:显示区域,所述显示区域被配置成包括在基板上方沿着第一方向和与所述第一方向相交的第二方向布置的多个像素;设置在所述显示区域处且耦连至所述多个像素的多个栅极线、多个数据线、和多个基准电压线;和栅极驱动电路,所述栅极驱动电路被配置成包括多个级电路单元,所述多个级电路单元设置在所述显示区域处且耦连至所述多个栅极线中的每一者,其中所述多个级电路单元包括:沿着所述第一方向分开地设置在所述多个像素之间的多个分支电路;设置在网络线形成部处的分支网络,所述网络线形成部限定(例如,定位)在沿着所述第一方向设置的所述多个像素中的每一者的一侧处,所述分支网络包括多个控制节点线和选择性地耦连至所述多个分支电路的多个网络线;和附加图案部,所述附加图案部设置在所述网络线形成部处以交叠设置在所述多个像素中的一些各自处的基准电压线。

429.根据本公开内容的一些实施方式,在所述多个显示装置各自中,所述多个像素可被布置成沿着所述第一方向和所述第二方向具有像素节距,所述像素节距可以是沿着所述第一方向和/或所述第二方向的相邻像素的中心部之间的距离,并且在沿着所述第一方向和/或所述第二方向相邻的第一显示装置和第二显示装置中,所述第一显示装置的最外像素的中心部和所述第二显示装置的最外像素的中心部之间的距离可小于或等于所述像素节距。

430.根据本公开内容的一些实施方式的显示装置可以应用于包括显示面板的所有电子设备。例如,根据本公开的显示装置可以应用于移动装置、可视电话、智能手表、手表电话、可穿戴装置、可折叠装置、可卷曲装置、可弯曲装置、柔性装置、弯曲装置、电子组织器、电子书、便携式多媒体播放器(pmp)、个人数字助理(pda)、mp3播放器、移动医疗设备、台式个人电脑(pc)、膝上型电脑、上网本电脑、工作站、导航设备、汽车导航设备、汽车显示装置、汽车设备、剧院设备、剧院显示装置、电视、墙纸显示装置、标牌设备、游戏机、笔记本电脑、显示器、照相机、摄像机、家用电器等。

431.对于本领域技术人员会显而易见的是,在不脱离本发明的精神和范围的情况下可在本公开内容中做出各种改进和变形。因此,意在本公开内容覆盖本公开内容的改进和变形,只要它们落入随附的权利要求书和它们的等价体的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1