显示装置及其驱动方法与流程

1.本发明涉及一种显示装置及其驱动方法。

背景技术:

2.随着信息化技术的发展,作为使用者与信息之间的连接媒介的显示装置的重要性正在凸显。顺应于此,液晶显示装置(liquid crystal display device)、有机发光显示装置(organic light emitting display device)等之类显示装置的使用正在增加。

3.近年来,根据消费者需求,显示装置可以以各种显示频率来显示图像。然而,当显示频率发生变化时,即便相同灰度的图像也可能发生闪烁(flicker)。

4.为此,提出了当显示频率发生变化时,针对相同的灰度使用不同数据电压的方法,但在显示频率检测中需要一帧,因此存在最少一帧的亮度差被用户看到的问题。为了进一步解决此问题,提出了通过延迟一帧来显示图像的方法,但存在需要额外的帧存储器的缺点。

技术实现要素:

5.所要解决的技术课题在于,提供一种即便不具备帧存储器也可以防止显示频率变化时的闪烁的显示装置及其驱动方法。

6.根据本发明的一实施例的显示装置包括:处理器,在帧时段的有源时段中,供应灰度数据,在所述帧时段的消隐时段中,中断所述灰度数据的供应;开关控制部,当消隐时段比预定的时段长时,生成第一开关控制信号,当所述消隐时段结束时,生成第二开关控制信号;电源提供部,当接收所述第一开关控制信号时,将与第一电源电压不同的电压供应于第一电源线,当接收所述第二开关控制信号时,将所述第一电源电压供应于所述第一电源线;以及像素,共同连接于所述第一电源线。

7.可以是,当接收所述第一开关控制信号时,所述电源提供部将第二电源电压供应于所述第一电源线,所述像素共同连接于被施加所述第二电源电压的第二电源线。

8.可以是,所述第一电源电压大于所述第二电源电压。

9.可以是,当接收所述第一开关控制信号时,所述电源提供部将基准电压供应于所述第一电源线,所述像素共同连接于被施加第二电源电压的第二电源线,所述基准电压与所述第一电源电压和所述第二电源电压不同。

10.可以是,所述第一电源电压大于所述基准电压。

11.可以是,所述有源时段的长度彼此相同,所述消隐时段中的至少2个的长度彼此不同。

12.可以是,所述消隐时段包括第一消隐时段以及第二消隐时段,在所述第一消隐时段期间,所述第一电源线保持所述第一电源电压,在所述第二消隐时段的第一时段期间,所述第一电源线保持所述第一电源电压,在所述第二消隐时段的第二时段期间,所述第一电源线保持与所述第一电源电压不同的电压,所述第一时段比所述第一消隐时段长。

13.可以是,所述消隐时段还包括第三消隐时段,在所述第三消隐时段的第三时段期间,所述第一电源线保持所述第一电源电压,在所述第三消隐时段的第四时段期间,所述第一电源线保持与所述第一电源电压不同的电压,所述第三时段以及所述第一时段的长度彼此相同,所述第四时段比所述第二时段长。

14.可以是,所述像素在所述第二时段以及所述第四时段期间处于非发光状态。

15.所述开关控制部可以包括:计数器,当所述消隐时段比所述预定的时段长时,生成低频感测信号;以及开关控制信号生成部,当接收所述低频感测信号时,生成所述第一开关控制信号,当接收扫描起始信号时,生成所述第二开关控制信号。

16.可以是,当数据使能信号保持为禁用电平的时间比所述预定的时段长时,所述计数器生成所述低频感测信号。

17.可以是,当垂直同步信号保持为禁用电平的时间比所述预定的时段长时,所述计数器生成所述低频感测信号。

18.可以是,所述显示装置还包括:扫描驱动部,当接收所述扫描起始信号时,向连接于所述像素的扫描线依次提供导通电平的扫描信号。

19.可以是,所述电源提供部包括:第一电源,生成所述第一电源电压;第二电源,生成所述第二电源电压;以及开关,若接收所述第一开关控制信号,则将所述第一电源线与所述第二电源线进行连接,若接收所述第二开关控制信号,则将所述第一电源线与所述第一电源进行连接。

20.可以是,所述电源提供部包括:第一电源,生成所述第一电源电压;第二电源,生成所述第二电源电压;以及开关,若接收所述第一开关控制信号,则向所述第一电源线施加所述基准电压,若接收所述第二开关控制信号,则将所述第一电源线与所述第一电源进行连接。

21.根据本发明的一实施例的显示装置的驱动方法包括:处理器在帧时段的有源时段中供应灰度数据,在所述帧时段的消隐时段中中断所述灰度数据的供应的步骤;当所述消隐时段比预定的时段长时,开关控制部生成第一开关控制信号;当接收所述第一开关控制信号时,电源提供部将与第一电源电压不同的电压供应于第一电源线的步骤;共同连接于所述第一电源线的像素接收与所述第一电源电压不同的电压的步骤;当所述消隐时段结束时,所述开关控制部生成第二开关控制信号的步骤;当接收所述第二开关控制信号时,所述电源提供部将所述第一电源电压供应于所述第一电源线的步骤;以及所述像素接收所述第一电源电压的步骤。

22.可以是,所述处理器在帧时段的有源时段中供应所述灰度数据,在所述帧时段的消隐时段中中断所述灰度数据的供应,所述有源时段的长度彼此相同,所述消隐时段中的至少2个的长度彼此不同。。

23.可以是,所述消隐时段包括第一消隐时段以及第二消隐时段,在所述第一消隐时段期间,所述第一电源线保持所述第一电源电压,在所述第二消隐时段的第一时段期间,所述第一电源线保持所述第一电源电压,在所述第二消隐时段的第二时段期间,所述第一电源线保持与所述第一电源电压不同的电压,所述第一时段比所述第一消隐时段长。

24.可以是,所述消隐时段还包括第三消隐时段,在所述第三消隐时段的第三时段期间,所述第一电源线保持所述第一电源电压,在所述第三消隐时段的第四时段期间,所述第

integrated chip,集成芯片),或者也可以指称由多个ic构成的组。

46.处理器10可以通过执行渲染(rendering)生成针对各个图像的灰度数据rgb。

47.处理器10可以在帧时段(frame periods)的有源时段(active periods)供应灰度数据rgb,并在帧时段的消隐时段(blank periods)中断灰度数据rgb的供应。此时,处理器10可以利用数据使能信号de通知灰度数据rgb的供应与否。例如,可以是,数据使能信号de在供应灰度数据rgb的期间为使能电平(an enable level),在消隐时段期间为禁用电平(a disable level)。例如,数据使能信号de可以在各自的有源时段中以水平时段(a horizontal period)单位包括使能电平的脉冲。灰度数据rgb可以对应于数据使能信号de的使能电平的脉冲以水平线(a horizontal line)单位供应。水平线可以意指与相同的扫描线连接的像素(例如,像素行)。

48.垂直同步信号vsync的各个周期(cycles)可以与各个帧时段相对应。例如,可以是,垂直同步信号vsync当为使能电平(例如,逻辑高电平)时指称相应帧时段的有源时段,当为禁用电平(例如,逻辑低电平)时指称相应帧时段的消隐时段。水平同步信号hsync的各个周期(cycles)可以与各个水平时段相对应。

49.时序控制部11可以从处理器10接收数据使能信号de以及灰度数据rgb。根据实施例,时序控制部11也可以从处理器10还接收垂直同步信号vsync以及水平同步信号hsync。

50.时序控制部11可以对应于数据驱动部12、扫描驱动部13、感测部15、电源提供部16、开关控制部17等的规格(specification)而供应控制信号。另外,时序控制部11可以将加工或者未加工的灰度数据rgb提供于数据驱动部12。

51.数据驱动部12可以利用灰度数据rgb以及控制信号生成要向数据线d1、d2、d3、

…

dm提供的数据电压。例如,数据驱动部12可以利用时钟信号来采样灰度数据rgb,并将对应于灰度数据rgb的数据电压以像素行单位施加于数据线d1、d2、d3、

…

dm。m可以是大于0的整数。

52.扫描驱动部13可以从时序控制部11接收时钟信号、扫描起始信号等而生成要提供于第一扫描线s11、s12、

…

s1n的第一扫描信号以及要提供于第二扫描线s21、s22、

…

s2n的第二扫描信号。n可以是大于0的整数。

53.扫描驱动部13可以向第一扫描线s11、s12、

…

s1n依次供应具有导通电平的脉冲的第一扫描信号。另外,扫描驱动部13可以向第二扫描线s21、s22、

…

s2n依次供应具有导通电平的脉冲的第二扫描信号。

54.例如,扫描驱动部13可以包括以移位寄存器(shift register)形态构成的扫描级。各个扫描级可以连接于对应的第一扫描线以及第二扫描线。例如,可以是,当第一个扫描级接收使能电平(例如,导通电平)的扫描起始信号时,向第一扫描线s11提供导通电平的第一扫描信号,并向第二扫描线s21提供导通电平的第二扫描信号。当第二个扫描级之后的扫描级接收先前扫描级的使能电平(例如,导通电平)的进位信号(或者扫描信号)时,可以向连接的第一扫描线提供导通电平的第一扫描信号,并向连接的第二扫描线提供导通电平的第二扫描信号。

55.感测部15可以从时序控制部11接收控制信号并向感测线i1、i2、i3、

…

ip供应初始化电压或者接收感测信号。例如,在显示时段中的至少一部分时段期间,感测部15可以向感测线i1、i2、i3、

…

ip供应初始化电压。例如,在感测时段中的至少一部分时段期间,感测部

15可以通过感测线i1、i2、i3、

…

ip接收感测信号。p可以是大于0的整数。

56.感测部15可以包括连接于感测线i1、i2、i3、

…

ip的感测沟道。例如,感测线i1、i2、i3、

…

ip与感测沟道可以一比一对应。

57.像素部14包括像素pxij。各个像素pxij可以连接于对应的数据线、扫描线以及感测线。针对示例性的像素pxij的结构将参照图3后述。

58.电源提供部16可以通过第一电源线elvddl以及第二电源线elvssl与像素pxij连接。像素pxij可以与第一电源线elvddl以及第二电源线elvssl共同连接。一般来说,可以是,电源提供部16通过第一电源线elvddl供应第一电源电压,通过第二电源线elvssl供应第二电源电压。例如,在像素部14的显示时段中,第一电源线elvddl的电压可以大于第二电源线elvssl的电压。

59.可以是,当消隐时段比预定的时段长时,开关控制部17生成第一开关控制信号,并在消隐时段结束时生成第二开关控制信号。当消隐时段比预定的时段小时,开关控制部17可以保持第二开关控制信号。

60.可以是,当接收第一开关控制信号时,电源提供部16向第一电源线elvddl供应与第一电源电压不同的电压,当接收第二开关控制信号时,电源提供部16向第一电源线elvddl供应第一电源电压。与第一以及第二开关控制信号无关地,电源提供部16可以向第二电源线elvssl供应第二电源电压。

61.图2是用于说明根据本发明的另一实施例的显示装置的图。

62.参照图2,开关控制部17以及时序控制部11可以由一体的ic(integrated chip)构成。例如,开关控制部17作为时序控制部11的一部分,可以由硬件或者软件来实现。

63.另外,电源提供部16以及数据驱动部12可以由一体的ic构成。例如,电源提供部16作为数据驱动部12的一部分,可以由硬件或者软件来实现。

64.虽未图示,根据实施例,时序控制部11以及数据驱动部12也可以由一体的ic构成。另外,虽未图示,根据实施例,数据驱动部12和感测部15也可以由一体的ic构成。

65.图3是用于说明根据本发明的一实施例的像素的图。图4是用于说明根据本发明的一实施例的像素的驱动方法的图。

66.参照图3,像素pxij可以包括晶体管t1、t2、t3、存储电容器cst以及发光二极管ld。

67.晶体管t1、t2、t3可以由n型晶体管构成。在另一实施例中,晶体管t1、t2、t3也可以由p型晶体管构成。在另一实施例中,晶体管t1、t2、t3也可以由n型晶体管以及p型晶体管的组合构成。p型晶体管通称为当栅极电极和源极电极之间的电压差向负方向增加时流过的电流量增加的晶体管。n型晶体管通称为当栅极电极和源极电极之间的电压差向正方向增加时流过的电流量增加的晶体管。晶体管可以由tft(thin film transistor,薄膜晶体管)、fet(field effect transistor,场效应晶体管)、bjt(bipolar junction transistor,双极结型晶体管)等各种形态构成。

68.可以是,第一晶体管t1的栅极电极连接于第一节点n1,第一电极连接于第一电源线elvddl,第二电极连接于第二节点n2。第一晶体管t1可以命名为驱动晶体管。

69.可以是,第二晶体管t2的栅极电极连接于第一扫描线s1i,第一电极连接于数据线dj,第二电极连接于第一节点n1。第二晶体管t2可以命名为扫描晶体管。

70.可以是,第三晶体管t3的栅极电极连接于第二扫描线s2i,第一电极连接于第二节

点n2,第二电极连接于感测线ik。第三晶体管t3可以命名为感测晶体管。

71.可以是,存储电容器cst的第一电极连接于第一节点n1,第二电极连接于第二节点n2。

72.可以是,发光二极管ld的阳极连接于第二节点n2,阴极连接于第二电源线elvssl。发光二极管ld可以由有机发光二极管(organic light emitting diode)、无机发光二极管(inorganic light emitting diode)、量子点/量子阱发光二极管(quantum dot/well light emitting diode)等构成。另外,发光二极管ld也可以由以串联、并联或者串并联连接的多个发光二极管构成。

73.在显示时段中,第一电源线elvddl的电压可以大于第二电源线elvssl的电压。然而,在防止发光二极管ld的发光等的特殊状况下,第二电源线elvssl的电压也可以设定为与第一电源线elvddl的电压相同或者更大。

74.参照图4,示出了在与扫描线s1i、s2i对应的水平时段期间向与像素pxij连接的扫描线s1i、s2i、数据线dj以及感测线ik施加的信号的示例性波形。k可以是大于0的整数。一个帧时段可以包括与像素行对应的多个水平时段。

75.在感测线ik中可以施加初始化电压vint。

76.在数据线dj中可以以水平时段单位依次施加数据电压ds(i-1)j、dsij、ds(i+1)j。在相应的水平时段,在第一扫描线s1i中可以施加导通电平(逻辑高电平)的第一扫描信号。另外,与第一扫描线s1i同步,也可以在第二扫描线s2i中施加导通电平的第二扫描信号。

77.例如,若第一扫描线s1i以及第二扫描线s2i中施加导通电平的扫描信号,则第二晶体管t2以及第三晶体管t3可以处于导通状态。因此,在像素pxij的存储电容器cst中写入相当于数据电压dsij和初始化电压vint之差的电压。

78.此时,施加于第二节点n2的初始化电压vint以及第二电源线elvssl的第二电源电压之差可以小于发光二极管ld的阈值电压。因此,在此时间点,发光二极管ld可以是非发光状态(non-emission state)。

79.此后,若在第一扫描线s1i以及第二扫描线s2i中施加截止电平(逻辑低电平)的扫描信号,则第二晶体管t2以及第三晶体管t3可以处于截止状态。因此,与数据线dj的电压变化无关地,可以通过存储电容器cst保持第一晶体管t1的栅极电极和源极电极之间的电压差。

80.由此,可以形成连接第一电源线elvddl、第一晶体管t1、发光二极管ld以及第二电源线elvssl的驱动路径。可以根据流过驱动路径的驱动电流来确定发光二极管ld的发光亮度。

81.驱动电流可以表示为如下数学公式1。

82.[数学公式1]

[0083]

ids=(1/2)

×

(w/l)

×u×

cox

×

((vdata-vanode-vth)^2)

×

(1+lmd

×

(velvdd-vanode))

[0084]

在此,可以是,ids为第一晶体管t1的漏极电极和源极电极之间流过的驱动电流,w为第一晶体管t1的沟道宽度,l为第一晶体管t1的沟道长度,u为第一晶体管t1的迁移率(mobility),cox为由第一晶体管t1的沟道、绝缘层以及栅极电极形成的电容,vdata为数据电压dsij,vanode为发光二极管ld的阳极电压,vth为第一晶体管t1的阈值电压,lmd为常

数,velvdd为第一电源线elvddl的电压。

[0085]

另外,vanode可以表示为如下数学公式2。

[0086]

[数学公式2]

[0087]

vanode=velvss+vel

[0088]

在此,可以是,velvss为第二电源线elvssl的电压,vel为发光二极管ld的两端电压差。

[0089]

参照图1至图4说明的像素pxij的结构以及驱动方法相当于一个实施例。在基于现有技术的任何像素的结构以及驱动方法中也可以适用后述的实施例。例如,当不具备感测部15以及第二扫描线s21、s22、

…

s2n时,排除像素pxij的第三晶体管t3,从而可以适用后述的实施例。

[0090]

图5是用于说明根据本发明的一实施例的显示装置的驱动方法的图。

[0091]

参照图5,示例性地示出了连续的第一帧时段fp1以及第二帧时段fp2。第一帧时段fp1可以包括第一有源时段app1和第一消隐时段blk1。第二帧时段fp2可以包括第二有源时段app2和第二消隐时段。在下文中,虽然以第一帧时段fp1为基准进行说明,但这样的说明也可以同样适用于其它帧时段。

[0092]

在第一有源时段app1中,可以以水平时段单位供应使能电平(例如,逻辑高电平)的数据使能信号de。此时,可以与使能电平的数据使能信号de同步而供应水平线单位的灰度数据rgb1、rgb2、rgb3、

…

rgbn。

[0093]

数据驱动部12可以从时序控制部11接收加工或者未加工的灰度数据rgb1、rgb2、rgb3、

…

rgbn。根据一实施例,数据驱动部12将水平线单位的灰度数据rgb1以串联(serial)接收,当完成接收时,以并联(parallel)锁存(latch),从而可以生成数据电压。在这样的数据电压中的第j个数据电压ds1j可以施加于第j个数据线dj。类似地,可以是,灰度数据rgb2中的一部分在下一个水平时段中以数据电压ds2j输出,灰度数据rgbn中的一部分在下一个水平时段中以数据电压dsnj输出。

[0094]

当扫描驱动部13接收使能电平(例如,导通电平)的扫描起始信号stv时,可以向连接于像素的扫描线s11、s21、s12、s22、

…

s1n、s2n依次提供导通电平的扫描信号。

[0095]

根据导通电平(例如,逻辑高电平)的扫描信号依次施加于扫描线s11、s21、s12、s22、

…

s1n、s2n,施加于数据线的数据电压可以被写入对应的像素。例如,若导通电平的扫描信号施加于扫描线s11、s21,则数据电压ds1j可以被写入第一个水平线(或者像素行)的像素。其次,若导通电平的扫描信号施加于扫描线s12、s22,则数据电压ds2j可以被写入第二个水平线的像素。对此进行反复,若导通电平的扫描信号施加于扫描线s1n、s2n,则数据电压dsnj可以被写入最后水平线的像素。

[0096]

在第一消隐时段blk1中可以供应禁用电平(例如,逻辑低电平)的数据使能信号de。此时,灰度数据rgb1、rgb2、rgb3、

…

rgbn的供应可以被中断。

[0097]

图6是用于说明根据本发明的另一实施例的显示装置的驱动方法的图。

[0098]

参照图6,处理器10可以向时序控制部11供应垂直同步信号vsync以及水平同步信号hsync。

[0099]

例如,第一帧时段fp1可以包括第一前沿时段(a first front porch period)fpp1、第一有源时段app1、第一后沿时段(a first back porch period)bpp1以及第一消隐

时段blk1。例如,第二帧时段fp2可以包括第二前沿时段fpp2、第二有源时段app2、第二后沿时段、第二消隐时段。

[0100]

例如,第一前沿时段fpp1作为垂直同步信号vsync为使能电平(例如,逻辑高电平)且数据使能信号de为禁用电平(例如,逻辑低电平)的时段,可以是灰度数据rgb1、rgb2、rgb3、

…

rgbn的供应开始前的时段。

[0101]

例如,第一有源时段app1作为垂直同步信号vsync为使能电平且数据使能信号de为包括使能电平的脉冲的时段,可以是供应灰度数据rgb1、rgb2、rgb3、

…

rgbn的时段。

[0102]

例如,第一后沿时段bpp1作为垂直同步信号vsync为使能电平且数据使能信号de为禁用电平的时段,可以是灰度数据rgb1、rgb2、rgb3、

…

rgbn的供应结束之后的时段。

[0103]

例如,第一消隐时段blk1可以是垂直同步信号vsync为禁用电平且数据使能信号de为禁用电平的时段。

[0104]

关于数据使能信号de、灰度数据rgb1、rgb2、rgb3、

…

rgbn、数据电压ds1j、ds2j、

…

dsnj、扫描信号的说明与图5的说明相同,因此省略重复的说明。

[0105]

图7是用于说明根据本发明的一实施例的渲染速度和显示频率的匹配方法的图。

[0106]

参照图7的上端,示出了当渲染速度和显示频率不对应时用于使其匹配的比较例。在比较例中,消隐时段blk1’、blk2’、blk3’、blk4’的长度相同。因此,在比较例中,帧时段fp1’、fp2’、fp3’、fp4’、fp5’的长度相同。为了说明,假设渲染时段render_a’、render_c’、render_d’比帧时段短,假设渲染时段render_b’比帧时段长的情况。

[0107]

例如,处理器10可以在渲染时段render_a’期间针对a’图像执行渲染。在渲染时段render_a’结束后的时间点t1a’,a’图像的灰度数据rgb_a’可以向时序控制部11提供。可以对应于这样的灰度数据rgb_a’而进行第一帧时段fp1’的第一有源时段app1’以及第一消隐时段blk1’(参照图5或者图6的驱动方法)。即,第一帧可以显示a’图像。

[0108]

在时间点t1a’之后,处理器10可以在渲染时段render_b’期间针对b’图像执行渲染。例如,渲染时段render_b’可以晚于第二帧时段fp2’开始的时间点t2a’结束。如果第二有源时段app2’中提供灰度数据rgb_b’,则第二帧同时显示a’图像以及b’图像而可能发生撕裂问题(tearing issue)。因此,在第二帧时段fp2’期间,处理器10不提供灰度数据rgb_b’,因此第二帧显示a’图像。由此,产生第一帧以及第二帧显示相同的a’图像的溅射问题。

[0109]

处理器10可以在第三帧时段fp3’开始的时间点t3a’提供关于b’图像的灰度数据rgb_b’。由此,第三帧显示b’图像。

[0110]

类似地,可以是,在时间点t4a’提供c’图像的灰度数据rgb_c’而第四帧显示c’图像,在时间点t5a’提供d’图像的灰度数据rgb_d’而第五帧显示d’图像。

[0111]

参照图7的下端,示出了当渲染速度和显示频率不对应时用于使其匹配的一实施例。在本实施例中,消隐时段blk1、blk2、blk3的长度可以彼此不同。因此,在本实施例中,帧时段fp1、fp2、fp3、fp4的长度可以彼此不同。类似地,假设渲染时段render_a、render_c、render_d比帧时段短,假设渲染时段render_b比帧时段长的情况。

[0112]

处理器10在时间点t1a’提供关于a图像的灰度数据rgb_a,从而第一帧可以显示a图像。

[0113]

当在时间点t2a’未终止关于b图像的渲染时段render_b时,处理器10可以延长第一消隐时段blk1的长度。例如,处理器10可以通过延长将数据使能信号de保持为禁用电平

的时段来延长第一消隐时段blk1的长度(参照图5以及图6)。另一方面,处理器10可以通过延长将垂直同步信号vsync保持为禁用电平的时段来延长第一消隐时段blk1的长度(参照图6)。

[0114]

处理器10可以在渲染时段render_b结束后的时间点t2a提供灰度数据rgb_b。由此,第二帧可以显示b图像。另一方面,可以是,第三帧显示c图像,第四帧显示d图像。

[0115]

根据本实施例,具有在没有撕裂以及溅射问题的情况下可以比比较例更快地显示图像的优点。

[0116]

图8是用于说明在显示频率较小时一像素的亮度变化的图。图9是用于说明在显示频率较大时一像素的亮度变化的图。

[0117]

参照图8,例如,时间点t1b可以是在一水平时段中向像素pxij的第二节点n2施加初始化电压vint的时间点。如前所述,此时,发光二极管ld为非发光状态,因此可以减少像素pxij的亮度。

[0118]

时间点t2b可以是在下一个水平时段中向像素pxij的第二节点n2施加初始化电压vint的时间点。如前所述,此时,发光二极管ld为非发光状态,因此可以减少像素pxij的亮度。

[0119]

图9的情况也相同地,时间点t1c以及时间点t2c可以是在各个水平时段中发光二极管ld为非发光状态的时间点。图8为显示频率较小时(即,帧时段较长时),图9为显示频率较大时(即,帧时段较短时),因此时段t1c~t2c比时段t1b~t2b短。以相同的时段为基准,图9的情况与图8的情况相比,发光二极管ld的非发光时段更长。由此,图9的情况的平均亮度avg2小于图8的情况的平均亮度avg1。即,显示频率越高,平均亮度减少,而显示频率越低,平均亮度增加,因此需要补偿这样的情况。

[0120]

因此,当显示频率变低时,需要进行补偿以降低亮度。参照数学公式1以及数学公式2,当降低第一电源线elvddl的电压(velvdd)时,可以减少驱动电流(ids)。另一方面,在一部分时段期间,也可以通过使第一电源线elvddl的电压(velvdd)与第二电源线elvssl的电压相同而阻断驱动电流(ids)。

[0121]

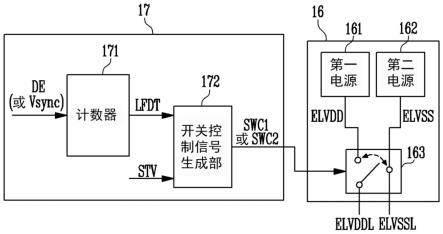

图10是用于说明根据本发明的一实施例的开关控制部以及电源提供部的图。

[0122]

可以是,当消隐时段比预定的时段长时,开关控制部17生成第一开关控制信号swc1,当消隐时段结束时,生成第二开关控制信号swc2。在一实施例中,当消隐时段比预定的时段短时,开关控制部17可以保持第二开关控制信号swc2。

[0123]

开关控制部17可以包括计数器171以及开关控制信号生成部172。

[0124]

当消隐时段比预定的时段长时,计数器171可以生成低频感测信号lfdt。例如,当数据使能信号de保持为禁用电平的时间比预定的时段长时,计数器171可以生成低频感测信号lfdt。例如,计数器171可以利用时钟信号来计算数据使能信号de保持为禁用电平的时间。此时,当计算的数量超过基准计算值时,计数器171可以生成低频感测信号lfdt。

[0125]

在另一实施例中,当垂直同步信号vsync保持为禁用电平的时间比预定的时段长时,计数器171也可以生成低频感测信号lfdt。例如,计数器171可以利用时钟信号来计算垂直同步信号vsync保持为禁用电平的时间。此时,当计算的数量超过基准计算值时,计数器171可以生成低频感测信号lfdt。此时,计数器171也可以利用水平同步信号hsync代替时钟信号。

[0126]

可以是,当开关控制信号生成部172接收低频感测信号lfdt时,生成第一开关控制信号swc1,当接收使能电平的扫描起始信号stv时,生成第二开关控制信号swc2。

[0127]

可以是,当电源提供部16接收第一开关控制信号swc1时,将与第一电源电压elvdd不同的电压供应于第一电源线elvddl,当接收第二开关控制信号swc2时,将第一电源电压elvdd供应于第一电源线elvddl。在图10的实施例中,当电源提供部16接收第一开关控制信号swc1时,将第二电源电压elvss供应于第一电源线elvddl。第一电源电压elvdd大于第二电源电压elvss。

[0128]

电源提供部16可以包括第一电源161、第二电源162以及开关163。

[0129]

第一电源161可以生成第一电源电压elvdd。例如,第一电源161可以是升压转换器(a boost converter)。然而,在此,第一电源161并非必须由dc-dc转换器构成。例如,也可以是,dc-dc转换器由pmic(power management integrated chip,电源管理集成芯片)独立地构成,第一电源161从pmic接收第一电源电压elvdd的传送,从而生成第一电源电压elvdd。

[0130]

第二电源162可以生成第二电源电压elvss。例如,第二电源162可以是升降压转换器(a buck-boost converter)。然而,在此,第二电源162并非必须由dc-dc转换器构成。例如,也可以是,dc-dc转换器由pmic独立地构成,第二电源162从pmic接收第二电源电压elvss的传送,从而生成第二电源电压elvss。

[0131]

可以是,若开关163接收第一开关控制信号swc1,则将第一电源线elvddl与第二电源线elvssl连接,若接收第二开关控制信号swc2,则将第一电源线elvddl与第一电源161连接。

[0132]

图11以及图12是用于说明基于显示频率的示例性亮度校正的图。

[0133]

参照图11,示例性地示出了连续的3个帧时段fp1、fp2、fp3。第一帧时段fp1包括第一有源时段app1以及第一消隐时段blk1。第二帧时段fp2包括第二有源时段app2以及第二消隐时段blk2。第三帧时段fp3包括第三有源时段app3以及第三消隐时段blk3。

[0134]

在此,假设第二帧时段fp2比第一帧时段fp1长,第三帧时段fp3比第二帧时段fp2长的情况。即,假设随着时间的经过,显示频率减少的情况。有源时段app1、app2、app3的长度彼此相同,消隐时段blk1、blk2、blk3中的至少2个的长度彼此不同。在此,假设第二消隐时段blk2比第一消隐时段blk1长,第三消隐时段blk3比第二消隐时段blk2长的情况。在此,假设第一消隐时段blk1比预定的时段p(cntref)短,第二消隐时段blk2以及第三消隐时段blk3比预定的时段p(cntref)长的情况。预定的时段p(cntref)意指直到通过计数器171计算的值与基准计算值(cntref)相同时所需的时间。

[0135]

首先,由于第一消隐时段blk1比预定的时段p(cntref)短,计数器171不生成低频感测信号lfdt。因此,在第一消隐时段blk1期间,第一电源线elvddl可以保持第一电源电压elvdd。

[0136]

接着,由于第二消隐时段blk2比预定的时段p(cntref)长,计数器171生成低频感测信号lfdt。接收低频感测信号lfdt的开关控制信号生成部172可以在从第二消隐时段blk2开始的时间点到经过第一时段p1的时间点生成第一开关控制信号swc1。开关163将第一电源线elvddl和第二电源线elvssl进行连接。此时,第一时段p1以及预定的时段p(cntref)可以实质上相同。第一时段p1可以比第一消隐时段blk1长。因此,可以是,在第二

消隐时段blk2的第一时段p1期间,第一电源线elvddl保持第一电源电压elvdd,在第二消隐时段blk2的第二时段p2期间,第一电源线elvddl保持与第一电源电压elvdd不同的电压(第二电源电压elvss)。因此,像素部14的像素pxij在第二时段p2期间处于非发光状态。第二时段p2为第一时段p1和第三有源时段app3之间的时段。

[0137]

接着,随着第二消隐时段blk2结束且第三有源时段app3开始,被供应使能电平的扫描起始信号stv。因此,接收使能电平的扫描起始信号stv的开关控制信号生成部172可以生成第二开关控制信号swc2。因此,开关163将第一电源线elvddl与第一电源161进行连接,第一电源电压elvdd施加于第一电源线elvddl。因此,像素部14的像素pxij重新处于发光状态。

[0138]

接着,由于第三消隐时段blk3比预定的时段p(cntref)长,计数器171生成低频感测信号lfdt。接收低频感测信号lfdt的开关控制信号生成部172可以在从第三消隐时段blk3开始的时间点到经过第三时段p3的时间点生成第一开关控制信号swc1。开关163将第一电源线elvddl与第二电源线elvssl进行连接。此时,第三时段p3以及预定的时段p(cntref)可以实质上相同。因此,第一时段p1和第三时段p3可以相同。因此,可以是,在第三消隐时段blk3的第三时段p3期间,第一电源线elvddl保持第一电源电压elvdd,在第三消隐时段blk3的第四时段p4期间,第一电源线elvddl保持与第一电源电压elvdd不同的电压(第二电源电压elvss)。因此,像素部14的像素pxij在第四时段p4期间处于非发光状态。第四时段p4为第三时段p3和第四有源时段的之间的时段。第四时段p4可以比第二时段p2长。

[0139]

参照图12,可以是,在第一帧时段fp1中没有附加的非发光时段,但第二帧时段fp2具有第二时段p2的非发光时段,第三帧时段fp3具有第四时段p4的非发光时段。

[0140]

由此,针对显示频率相对小的帧时段,使非发光时段相对长,从而可以减少显示频率相对小的帧时段的平均亮度。因此,可以与显示频率的变化无关地保持类似的平均亮度,因此可以防止闪烁的发生。

[0141]

图13是用于说明根据本发明的另一实施例的开关控制部以及电源提供部的图。在下文中,仅针对与图10的实施例不同的结构进行说明,省略针对相同的结构的重复说明。

[0142]

参照图13,当电源提供部16’接收第一开关控制信号swc1时,可以将基准电压vref供应于第一电源线elvddl。此时,基准电压vref可以是与第一电源电压elvdd和第二电源电压elvss不同的(独立的)电压。第一电源电压elvdd可以大于基准电压vref。

[0143]

可以是,若开关163’接收第一开关控制信号swc1,则向第一电源线elvddl施加基准电压vref,若接收第二开关控制信号swc2,则将第一电源线elvddl与第一电源161连接。

[0144]

图13的开关控制部17以及电源提供部16’的工作与图11以及图12相同,因此省略与重复特征有关的说明。

[0145]

目前为止参照的附图和所记载的发明的详细说明仅仅是本发明的例示,其仅在用于说明本发明的目的中使用,并不是用于含义限定或限制记载于权利要求书中的本发明的范围而使用。因此,具有本技术领域的通常知识的人由此可以理解各种变形以及等同的其它实施例是可能的。因此,本发明的真正的技术保护范围应通过所附的权利要求书的技术构思来确定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1