栅极驱动部及包括其的显示装置的制作方法

1.本发明涉及一种栅极驱动部及包括其的显示装置,涉及一种包括多个前置级的栅极驱动部及包括其的显示装置。

背景技术:

2.通常,显示装置包括显示面板以及显示面板驱动部。所述显示面板包括多个栅极线以及多个数据线。所述显示面板驱动部包括将栅极信号提供于所述多个栅极线的栅极驱动部以及将栅极电压提供于所述数据线的数据驱动部。

3.所述栅极驱动部可以利用在显示面板上集成的多个级而输出所述栅极信号。所述栅极驱动部可以包括将所述栅极信号输出于所述显示面板的有源级和不将所述栅极信号输出于所述显示面板的前置级。

4.前置级可以基于垂直起始信号对q节点充电(pre-charge)。可以是,在前置级中晶体管的泄漏电流产生的情况下,q节点的电压不保持(holding)。在q节点的电压不保持的情况下,有源级可以输出非正常的感测信号以及非正常的栅极信号。

技术实现要素:

5.本发明的一目的是提供一种可以在前置级之间反馈进位信号而在保持时间期间使q节点的电压一定地保持的栅极驱动部。

6.本发明的另一目的是提供一种包括所述栅极驱动部的显示装置。

7.用于实现上述本发明的目的的根据一实施例的栅极驱动部可以包括:多个有源级,将栅极信号输出于显示部;以及多个前置级,连接于所述有源级而向所述有源级输出进位信号。可以是,所述多个前置级包括第一前置级以及第二前置级。在此,可以是,所述第二前置级包括:q节点补偿部,从所述第一前置级接收时钟信号的输入,并基于所述第一前置级的所述时钟信号补偿q节点的电压。可以是,所述q节点补偿部包括:反馈晶体管,将接收所述第一前置级的所述时钟信号的输入的反馈输入端子与所述第二前置级的反馈节点二极管连接。可以是,所述反馈晶体管包括源极电极、栅极电极以及漏极电极,所述源极电极与所述反馈输入端子连接,所述栅极电极与所述源极电极连接,所述漏极电极与所述反馈节点连接。

8.在一实施例中,可以是,所述第一前置级的所述时钟信号是所述第一前置级的进位信号、所述第一前置级的感测信号以及所述第一前置级的栅极信号中的一个。

9.在一实施例中,可以是,所述q节点补偿部调节施加于所述反馈节点的电压电平,从而减小连接所述反馈节点与所述q节点的晶体管中的至少一个晶体管的漏极-源极电压。

10.在一实施例中,可以是,所述第二前置级包括:q节点充电部,接收垂直起始信号的输入而对所述q节点充电;q节点稳定化部,接收所述有源级的进位信号的输入而将所述q节点稳定化;以及反相部,基于所述q节点的所述电压,生成反相信号。

11.在一实施例中,可以是,所述第二前置级的所述反馈节点与所述q节点充电部、所

述q节点稳定化部以及所述反相部连接。

12.在一实施例中,可以是,所述第二前置级包括:晶体管稳定化部,基于晶体管稳定化信号,将连接于所述反馈节点的多个晶体管稳定化。可以是,所述晶体管稳定化部包括第一晶体管稳定化晶体管以及第二晶体管稳定化晶体管。可以是,所述第一晶体管稳定化晶体管包括:源极电极,连接于所述第二晶体管稳定化晶体管;栅极电极,连接于所述q节点;以及漏极电极,连接于所述反馈节点。可以是,所述第二晶体管稳定化晶体管包括:源极电极,被施加栅极高电压;栅极电极,连接于所述q节点;以及漏极电极,连接于所述第一晶体管稳定化晶体管。

13.在一实施例中,可以是,所述q节点充电部包括第一充电晶体管以及第二充电晶体管。可以是,所述第二充电晶体管包括:源极电极,接收所述垂直起始信号的输入;栅极电极,连接于所述第二充电晶体管的所述源极电极;以及漏极电极,连接于所述第一充电晶体管。可以是,所述第一充电晶体管包括:源极电极,连接于所述第二充电晶体管;栅极电极,连接于所述第二充电晶体管的所述源极电极;以及漏极电极,连接于所述q节点。

14.在一实施例中,可以是,所述q节点稳定化部包括第一稳定化晶体管以及第二稳定化晶体管。可以是,所述第一稳定化晶体管包括:源极电极,连接于所述第二稳定化晶体管;栅极电极,被施加之后进位信号中的任一个;以及漏极电极,连接于所述q节点。可以是,所述第二稳定化晶体管包括:源极电极,被施加第一低电压;栅极电极,被施加所述之后进位信号中的任一个;以及漏极电极,连接于所述第一稳定化晶体管。

15.在一实施例中,可以是,所述q节点充电部、所述q节点稳定化部以及所述反相部各自由氧化物半导体晶体管构成。

16.在一实施例中,可以是,所述第二前置级调节所述反馈节点的电压电平,从而减小连接所述反馈节点与所述q节点的晶体管的泄漏电流,基于所述q节点的所述电压生成进位信号,并将所述进位信号输出于所述有源级。

17.用于实现上述本发明的另一目的的根据一实施例的显示装置可以包括显示面板、数据驱动部以及栅极驱动部。可以是,所述显示面板包括显示图像的显示部以及与所述显示部相邻的周边部。可以是,所述数据驱动部将数据电压施加于所述显示面板。可以是,所述栅极驱动部包括:多个有源级,将栅极信号输出于所述显示部;以及多个前置级,连接于所述有源级而向所述有源级输出进位信号。可以是,所述多个前置级包括第一前置级以及第二前置级。在此,可以是,所述第二前置级包括:q节点补偿部,从所述第一前置级接收时钟信号的输入,并基于所述第一前置级的所述时钟信号补偿q节点的电压。可以是,所述q节点补偿部包括:反馈晶体管,将接收所述第一前置级的所述时钟信号的输入的反馈输入端子与所述第二前置级的反馈节点二极管连接。可以是,所述反馈晶体管包括源极电极、栅极电极以及漏极电极,所述源极电极与所述反馈输入端子连接,所述栅极电极与所述源极电极连接,所述漏极电极与所述反馈节点连接。

18.在一实施例中,可以是,所述第一前置级的所述时钟信号是所述第一前置级的进位信号、所述第一前置级的感测信号以及所述第一前置级的栅极信号中的一个。

19.在一实施例中,可以是,所述q节点补偿部调节施加于所述反馈节点的电压电平,从而减小连接所述反馈节点与所述q节点的晶体管中的至少一个晶体管的漏极-源极电压。

20.在一实施例中,可以是,所述第二前置级包括:q节点充电部,接收垂直起始信号的

输入而对所述q节点充电;q节点稳定化部,接收所述有源级的进位信号的输入而将所述q节点稳定化;以及反相部,基于所述q节点的所述电压,生成反相信号。

21.在一实施例中,可以是,所述第二前置级的所述反馈节点与所述q节点充电部、所述q节点稳定化部以及所述反相部连接。

22.在一实施例中,可以是,所述第二前置级包括:晶体管稳定化部,基于晶体管稳定化信号,将连接于所述反馈节点的多个晶体管稳定化。可以是,所述晶体管稳定化部包括第一晶体管稳定化晶体管以及第二晶体管稳定化晶体管。可以是,所述第一晶体管稳定化晶体管包括:源极电极,连接于所述第二晶体管稳定化晶体管;栅极电极,连接于所述q节点;以及漏极电极,连接于所述反馈节点。可以是,所述第二晶体管稳定化晶体管包括:源极电极,被施加栅极高电压;栅极电极,连接于所述q节点;以及漏极电极,连接于所述第一晶体管稳定化晶体管。

23.在一实施例中,可以是,所述q节点充电部包括第一充电晶体管以及第二充电晶体管。可以是,所述第二充电晶体管包括:源极电极,接收所述垂直起始信号的输入;栅极电极,连接于所述第二充电晶体管的所述源极电极;以及漏极电极,连接于所述第一充电晶体管。可以是,所述第一充电晶体管包括:源极电极,连接于所述第二充电晶体管;栅极电极,连接于所述第二充电晶体管的所述源极电极;以及漏极电极,连接于所述q节点。

24.在一实施例中,可以是,所述q节点稳定化部包括第一稳定化晶体管以及第二稳定化晶体管。可以是,所述第一稳定化晶体管包括:源极电极,连接于所述第二稳定化晶体管;栅极电极,被施加之后进位信号中的任一个;以及漏极电极,连接于所述q节点。可以是,所述第二稳定化晶体管包括:源极电极,被施加第一低电压;栅极电极,被施加所述之后进位信号中的任一个;以及漏极电极,连接于所述第一稳定化晶体管。

25.在一实施例中,可以是,所述q节点充电部、所述q节点稳定化部以及所述反相部各自由氧化物半导体晶体管构成。

26.在一实施例中,可以是,所述第二前置级调节所述反馈节点的电压电平,从而减小连接所述反馈节点与所述q节点的晶体管的泄漏电流,基于所述q节点的所述电压生成进位信号,并将所述进位信号输出于所述有源级。

27.根据这样的栅极驱动部及包括其的显示装置,包括在栅极驱动部中的前置级可以从之前前置级接收时钟信号的输入,并基于所述之前前置级的所述时钟信号补偿q节点的电压,以保持所述q节点的电压。结果,所述栅极驱动部及包括其的显示装置可以使显示装置的显示品质提升。

附图说明

28.图1是示出根据本发明的一实施例的显示装置的框图。

29.图2是示出包括在图1的显示装置中的栅极驱动部的框图。

30.图3a是示出图2的栅极驱动部的级间的进位输出线的框图。

31.图3b是示出包括在图2的栅极驱动部中的有源级的电路图。

32.图4是示出包括在图2的栅极驱动部中的前置级的电路图。

33.图5是示出图4的前置级的q节点的电压的时序图。

34.图6是示出在初始前置级与反馈前置级通过反馈线连接的情况下,级间的进位输

出线的框图。

35.图7是示出包括在图6中的反馈前置级的电路图。

36.图8是示出包括在图6中的初始前置级以及反馈前置级的输入输出信号的时序图。

37.图9是示出包括在图6中的初始前置级以及反馈前置级的q节点的电压的时序图。

38.图10是示出根据本发明的实施例的电子设备的框图。

39.图11是示出图10的电子设备实现为智能电话的一例的图。

40.(附图标记说明)

41.100:显示面板

ꢀꢀꢀꢀꢀꢀ

200:驱动控制部

42.300:栅极驱动部

ꢀꢀꢀꢀ

400:伽马基准电压生成部

43.500:数据驱动部

具体实施方式

44.以下,将参照所附的附图,更详细地说明本发明。

45.图1是示出根据本发明的一实施例的显示装置的框图。

46.参照图1,所述显示装置可以包括显示面板100以及显示面板驱动部。所述显示面板驱动部可以包括驱动控制部200、栅极驱动部300、伽马基准电压生成部400以及数据驱动部500。

47.例如,所述驱动控制部200以及所述数据驱动部500可以一体地形成。例如,所述驱动控制部200、所述伽马基准电压生成部400以及所述数据驱动部500可以一体地形成。可以将至少所述驱动控制部200以及所述数据驱动部500一体地形成的驱动模组命名为时序控制器嵌入式数据驱动部(timing controller embedded data driver,ted)。

48.所述显示面板100可以包括显示图像的显示部aa以及与所述显示部aa相邻配置的周边部pa。

49.所述显示面板100可以包括多个栅极线gl、多个数据线dl以及电连接于所述栅极线gl和所述数据线dl各自的多个像素p。可以是,所述栅极线gl向第一方向d1延伸,所述数据线dl向与所述第一方向d1交叉的第二方向d2延伸。

50.所述驱动控制部200可以从外部的装置(未图示)接收输入图像数据img以及输入控制信号cont。例如,所述输入图像数据img可以包括红色图像数据、绿色图像数据以及蓝色图像数据。所述输入图像数据img可以包括白色图像数据。所述输入图像数据img可以包括品红色(magenta)图像数据、黄色(yellow)图像数据以及青色(cyan)图像数据。所述输入控制信号cont可以包括主时钟信号、数据使能信号。所述输入控制信号cont可以还包括垂直同步信号以及水平同步信号。

51.所述驱动控制部200可以依据所述输入图像数据img以及所述输入控制信号cont,生成第一控制信号cont1、第二控制信号cont2、第三控制信号cont3以及数据信号data。

52.所述驱动控制部200依据所述输入控制信号cont,生成用于控制所述栅极驱动部300的工作的所述第一控制信号cont1而将其输出于所述栅极驱动部300。所述第一控制信号cont1可以包括垂直起始信号以及栅极时钟信号。

53.所述驱动控制部200依据所述输入控制信号cont,生成用于控制所述数据驱动部500的工作的所述第二控制信号cont2而将其输出于所述数据驱动部500。所述第二控制信

号cont2可以包括水平起始信号以及负载信号。

54.所述驱动控制部200可以依据所述输入图像数据img,生成数据信号data。所述驱动控制部200可以将所述数据信号data输出于所述数据驱动部500。

55.所述驱动控制部200可以依据所述输入控制信号cont,生成用于控制所述伽马基准电压生成部400的工作的所述第三控制信号cont3而将其输出于所述伽马基准电压生成部400。

56.所述栅极驱动部300可以响应于从所述驱动控制部200接收的所述第一控制信号cont1,生成用于驱动所述栅极线gl的栅极信号。所述栅极驱动部300可以将所述栅极信号输出于所述栅极线gl。例如,所述栅极驱动部300可以将所述栅极信号依次输出于所述栅极线gl。

57.在本实施例中,所述栅极驱动部300可以集成在所述显示面板100的所述周边部pa上。

58.所述伽马基准电压生成部400可以响应于从所述驱动控制部200接收的所述第三控制信号cont3,生成伽马基准电压vgref。所述伽马基准电压生成部400可以将所述伽马基准电压vgref提供于所述数据驱动部500。所述伽马基准电压vgref可以具有与各个数据信号data对应的值。

59.在本发明的一实施例中,所述伽马基准电压生成部400可以配置于所述驱动控制部200内或配置于所述数据驱动部500内。

60.所述数据驱动部500可以从所述驱动控制部200接收所述第二控制信号cont2以及所述数据信号data的输入,并从所述伽马基准电压生成部400接收所述伽马基准电压vgref的输入。所述数据驱动部500可以利用所述伽马基准电压vgref,将所述数据信号data转换为模拟形式的数据电压。所述数据驱动部500可以将所述数据电压输出于所述数据线dl。

61.图2是示出包括在图1的显示装置中的栅极驱动部300的框图,图3a是示出图2的栅极驱动部300的级间的进位输出线的框图,图3b是示出包括在图2的栅极驱动部300中的有源级的电路图。

62.参照图1至图3b,所述栅极驱动部300可以包括多个有源级ast1~astx以及多个前置级pst1~pst4。

63.所述多个有源级ast1~astx可以将所述栅极信号输出于所述显示部aa。例如,所述多个有源级ast1~astx的数量可以与所述显示面板100的所述显示部aa的所述栅极线的数量相同。例如,所述多个有源级ast1~astx的数量可以与所述显示面板100的所述显示部aa的像素行的数量相同。各个所述有源级ast1~astx可以输出所述栅极信号以及进位信号。

64.所述多个前置级pst1~pst4可以连接于所述有源级ast1~astx而向所述有源级ast1~astx输出进位信号。在图2中,所述多个前置级pst1~pst4示例为四个,但是本发明的多个前置级的数量不限于此。

65.可以是,在所述第n有源级astn施加第一至第六输入信号(例如,s1~s6),施加第n时钟信号,并施加第一至第三低电压(例如,vss1、vss2、vss3)。所述第n时钟信号可以包括栅极时钟信号sc_ckn、感测时钟信号ss_ckn以及进位时钟信号cr_ckn。在有源区间中所述栅极时钟信号sc_ckn、所述感测时钟信号ss_ckn以及所述进位时钟信号cr_ckn可以具有相同

的时序。在所述栅极驱动部300的所述多个有源级ast1~astx可以依次施加具有彼此不同相位的六个时钟信号。在此,各时钟信号的波形的周期可以为六个水平区间。

66.例如,可以是,第一有源级ast1被施加第一时钟信号,第二有源级ast2被施加第二时钟信号,第三有源级ast3被施加第三时钟信号,第四有源级ast4被施加第四时钟信号,第五有源级ast5被施加第五时钟信号,第六有源级ast6被施加第六时钟信号,第七有源级ast7被施加所述第一时钟信号,第八有源级ast8被施加所述第二时钟信号,第九有源级ast9被施加所述第三时钟信号,第十有源级ast10被施加所述第四时钟信号,第十一有源级ast11被施加所述第五时钟信号,第十二有源级ast12被施加所述第六时钟信号。

67.所述第n有源级astn可以包括第一感测部31、第二感测部32、q节点充电部33、q节点稳定化部34、反相部35、进位信号输出部36、感测信号输出部37、栅极信号输出部38以及晶体管稳定化部39。

68.所述第一感测部31以及所述第二感测部32可以基于第一输入信号s1、第二输入信号s2、第四输出信号s4以及q节点nq信号工作,并感测所述显示面板100的像素部内的晶体管的特性。所述第一感测部31可以包括第一感测晶体管t24a及第二感测晶体管t25a以及感测电容器c3a。所述第二感测部32可以包括第三感测晶体管t21a、第四感测晶体管t22a、第五感测晶体管t23a、第六感测晶体管t26a以及第七感测晶体管t27a。

69.所述q节点充电部33可以基于之前进位信号中的任一个,对所述q节点nq充电。在此,所述之前进位信号中的任一个可以是从当前级起第三个之前级的进位信号in n-3。所述q节点充电部33可以包括第一充电晶体管t4_1a以及第二充电晶体管t4_2a。

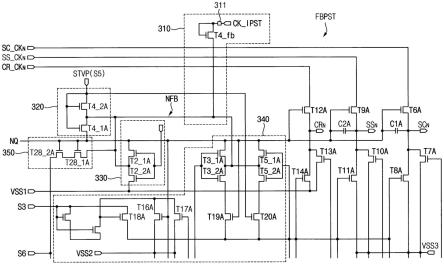

70.所述q节点稳定化部34可以基于之后进位信号中的任一个以及第五输入信号s5,将所述q节点nq稳定化。在此,所述之后进位信号中的任一个可以是从当前级起第四个之后级的进位信号in n+4。例如,所述q节点稳定化部34可以接收从所述当前级起第四个之后级的进位信号in n+4。在此,所述第五输入信号s5可以是垂直起始信号stvp。所述q节点稳定化部34可以包括第一稳定化晶体管t1_1a、第二稳定化晶体管t1_2a、第三稳定化晶体管t2_1a以及第四稳定化晶体管t2_2a。

71.所述反相部35可以基于第三输入信号s3以及所述q节点nq信号,生成反相信号inv n。所述反相部35可以包括第一反相晶体管t3_1a、第二反相晶体管t3_2a、第三反相晶体管t19a、第四反相晶体管t5_1a、第五反相晶体管t5_2a、第六反相晶体管t20a、第七反相晶体管t15a、第八反相晶体管t16a、第九反相晶体管t17a、第十反相晶体管t18a。

72.所述进位信号输出部36可以基于所述q节点nq信号以及反相信号inv n,输出进位信号cr n。所述进位信号输出部36可以包括第一进位晶体管t12a、第二进位晶体管t13a以及第三进位晶体管t14a。

73.所述感测信号输出部37可以基于所述q节点nq信号以及反相信号inv n,输出感测信号ss n。所述感测信号输出部37可以包括第一感测输出晶体管t9a、第二感测输出晶体管t10a以及第三感测输出晶体管t11a。所述感测信号输出部37可以还包括连接于所述第一感测输出晶体管t9a的所述控制电极与所述输出电极之间的感测输出电容器c2a。

74.所述栅极信号输出部38可以基于所述q节点nq信号以及反相信号inv n,输出栅极信号sc n。所述栅极信号输出部38可以包括第一栅极晶体管t6a、第二栅极晶体管t7a以及第三栅极晶体管t8a。所述栅极信号输出部38可以还包括连接于所述第一栅极晶体管t6a的

所述控制电极与所述输出电极之间的栅极电容器c1a。

75.所述晶体管稳定化部39可以响应于所述q节点nq,将所述第六输入信号s6传输于串联连接的晶体管的中间节点而将所述串联连接的晶体管的工作稳定化。所述晶体管稳定化部39可以包括第一晶体管稳定化晶体管t28_1a以及第二晶体管稳定化晶体管t28_2a。

76.在一实施例中,所述栅极驱动部300可以包括第一前置级pst1、第二前置级pst2、第三前置级pst3以及第四前置级pst4。所述第一前置级pst1可以与所述第二前置级pst2以一对工作。所述第二前置级pst2可以将前置进位信号输出于第一有源级ast1以及第二有源级ast2。所述第三前置级pst3可以与所述第四前置级pst4以一对工作。所述第四前置级pst4可以将前置进位信号输出于第三有源级ast3以及第四有源级ast4。

77.图4是示出包括在图2的栅极驱动部中的前置级的电路图,图5是示出图4的前置级的q节点的电压的时序图。

78.参照图4至图5,所述前置级pst1~pst4的电路结构可以与所述有源级ast1~astx(参照图2)的电路结构相同。相比于所述有源级ast1~astx的电路结构,所述前置级pst1~pst4的电路可以为从所述有源级ast1~astx的电路中排除了第一感测部以及第二感测部的结构。前置级pst1~pst4可以包括q节点nq。

79.前置级pst1~pst4可以基于垂直起始信号stvp,对所述q节点nq充电(pre-charge)。可以是,在前置级pst1~pst4中晶体管的泄漏电流产生的情况下,q节点nq的电压不保持(holding)。在前置级pst1~pst4的q节点nq的电压不保持的情况下,有源级ast1~astx可以输出非正常的感测信号以及非正常的栅极信号。

80.具体地,在q节点充电之后,q节点nq的电压可以具有保持时间ht。在前置级pst1~pst4以及有源级ast1~astx中,阈值电压的感测(vth sensing)工作时,为了确保充分的感测时间,q节点nq的电压可以保持为浮置(floating)状态。即,保持时间ht可以是在q节点nq充电之后,将q节点nq的电压保持为浮置状态的时间。尤其是,前置级pst1~pst4基于垂直起始信号stvp对所述q节点nq充电,因此从第一前置级pst1增加至第四前置级pst4,q节点nq的保持时间ht可以增加。

81.例如,在图5中将各个前置级pst1~pst4的q节点示出为第一q节点nq1至第四q节点nq4。在第一q节点nq1处第一q节点电压vnq1可以保持正常的电压电平。相反地,根据晶体管的泄漏电流,在第四q节点nq4处,随着保持时间的增加,第四q节点电压vnq4可以具有非正常的电压电平。在此情况下,接收基于第四q节点电压vnq4生成的进位信号的有源级ast1~astx可以输出非正常的感测信号以及非正常的栅极信号。

82.为了解决这样的问题,本发明的所述前置级可以包括q节点补偿部310(参照图7),q节点补偿部310从之前前置级接收时钟信号的输入,并基于所述之前前置级的所述时钟信号补偿q节点的电压,以保持所述q节点nq的电压。

83.图6是示出在初始前置级ipst与反馈前置级fbpst通过反馈线连接的情况下,级间的进位输出线的框图,图7是示出包括在图6中的反馈前置级fbpst的电路图,图8是示出包括在图6中的初始前置级以及反馈前置级的输入输出信号的时序图,图9是示出包括在图6中的初始前置级以及反馈前置级的q节点nq的电压的时序图。

84.参照图6至图9,前置级pst1~pst4可以包括初始前置级ipst以及反馈前置级fbpst。所述反馈前置级fbpst可以包括q节点补偿部310,q节点补偿部310从所述初始前置

级ipst接收时钟信号ck_ipst的输入,并基于所述初始前置级ipst的所述时钟信号ck_ipst补偿q节点nq的电压。在图6中示出了第一前置级pst1为初始前置级ipst,第二至第四前置级pst2~pst4为反馈前置级fbpst,但是本发明的初始前置级ipst以及反馈前置级fbpst不限于此。例如,初始前置级ipst可以是多个。

85.如在图7中看到的,反馈前置级fbpst可以包括q节点充电部320、q节点稳定化部330、反相部340以及晶体管稳定化部350。此时,反馈前置级fbpst可以还包括q节点补偿部310。所述q节点充电部320、所述q节点稳定化部330以及所述反相部340各自可以由氧化物半导体晶体管构成。

86.所述q节点充电部320可以基于垂直起始信号stvp,对所述q节点nq充电。所述q节点充电部320可以包括第一充电晶体管t4_1a以及第二充电晶体管t4_2a。所述第二充电晶体管t4_2a可以包括接收所述垂直起始信号stvp的输入的源极电极、连接于所述源极电极的栅极电极以及连接于所述第一充电晶体管t4_1a的漏极电极。所述第一充电晶体管t4_1a可以包括连接于所述第二充电晶体管t4_2a的源极电极、连接于所述第二充电晶体管t4_2a的所述源极电极的栅极电极以及连接于所述q节点nq的漏极电极。

87.所述q节点稳定化部330可以基于所述有源级的进位信号,将所述q节点nq稳定化。所述q节点稳定化部330可以包括第一稳定化晶体管t2_1a以及第二稳定化晶体管t2_2a。所述第一稳定化晶体管t2_1a可以包括连接于所述第二稳定化晶体管t2_2a的源极电极、被施加之后进位信号中的任一个的栅极电极以及连接于所述q节点nq的漏极电极。所述第二稳定化晶体管t2_2a包括被施加第一低电压vss1的源极电极、被施加所述之后进位信号中的任一个的栅极电极以及连接于所述第一稳定化晶体管t2_1a的漏极电极。

88.所述反相部340可以基于所述q节点nq的所述电压,生成反相信号。所述反相部340可以包括第一反相晶体管t3_1a、第二反相晶体管t3_2a、第三反相晶体管t5_1a以及第四反相晶体管t5_2a。

89.晶体管稳定化部350可以基于晶体管稳定化信号,将连接于所述反馈节点nfb的多个晶体管稳定化。所述晶体管稳定化部350可以包括第一晶体管稳定化晶体管t28_1a、第二晶体管稳定化晶体管t28_2a。所述第一晶体管稳定化晶体管t28_1a可以包括连接于所述第二晶体管稳定化晶体管t28_2a的源极电极、连接于所述q节点nq的栅极电极以及连接于所述反馈节点nfb的漏极电极。所述第二晶体管稳定化晶体管t28_2a可以包括被施加栅极高电压s6(上述的第六输入信号)的源极电极、连接于所述q节点nq的栅极电极以及连接于所述第一晶体管稳定化晶体管t28_1a的漏极电极。

90.所述q节点补偿部310可以从所述初始前置级ipst接收时钟信号ck_ipst的输入,并基于所述初始前置级ipst的所述时钟信号ck_ipst,补偿q节点nq的电压。所述q节点补偿部310可以包括反馈晶体管t4_fb,反馈晶体管t4_fb将接收所述初始前置级ipst的所述时钟信号ck_ipst的输入的反馈输入端子311与所述反馈前置级fbpst的反馈节点nfb二极管连接。在此,所述初始前置级ipst的所述时钟信号ck_ipst可以是所述初始前置级ipst的进位信号crn、所述初始前置级ipst的感测信号ssn以及所述初始前置级ipst的栅极信号scn中的一个。

91.在向所述反馈节点nfb输入所述初始前置级ipst的时钟信号ck_ipst的情况下,所述反馈节点nfb的电压电平可以被补偿。在通过所述初始前置级ipst的时钟信号ck_ipst补

偿所述反馈节点nfb的电压电平的情况下,所述q节点nq的电压电平可以保持为正常的电平。

92.具体地,所述反馈前置级fbpst的所述反馈节点nfb可以与所述q节点充电部320、所述q节点稳定化部330以及所述反相部340连接。在所述反馈节点nfb输入所述初始前置级ipst的时钟信号ck_ipst而所述反馈节点nfb的电压电平被补偿的情况下,连接所述反馈节点nfb与所述q节点nq的晶体管的漏极-源极电压可以减小。即,在所述反馈节点nfb输入所述初始前置级ipst的时钟信号ck_ipst而所述反馈节点nfb的电压电平保持为所述初始前置级ipst的时钟信号ck_ipst的激活电平(即,高电平)的情况下,连接所述反馈节点nfb与所述q节点nq的晶体管的漏极-源极电压可以、减小。在连接所述反馈节点nfb与所述q节点nq的晶体管的漏极-源极电压减小的情况下,所述q节点nq的电压电平可以保持为正常的电平。另外,在所述反馈节点nfb输入所述初始前置级ipst的时钟信号ck_ipst而所述反馈节点nfb的电压电平被补偿的情况下,连接所述反馈节点nfb与所述q节点nq的晶体管的泄漏电流可以减小。即,在所述q节点充电部320、所述q节点稳定化部330以及所述反相部340中产生的泄漏电流可以减小。在连接所述反馈节点nfb与所述q节点nq的晶体管的泄漏电流减小的情况下,所述q节点nq的电压电平可以保持为正常的电平。

93.如在图8中看到的,在所述反馈节点nfb(参照图7)输入所述初始前置级ipst(参照图6)的时钟信号ck_ipst而所述反馈节点nfb的电压电平被补偿的情况下,在所述反馈前置级fbpst(参照图7)的保持时间ht期间,包括在所述反馈前置级fbpst中的第一充电晶体管t4_1a(参照图7)的漏极-源极电压、第一稳定化晶体管t2_1a(参照图7)的漏极-源极电压、第一反相晶体管t3_1a(参照图7)的漏极-源极电压、第三反相晶体管t5_1a(参照图7)的漏极-源极电压可以减小。在所述反馈节点nfb输入所述初始前置级ipst的时钟信号ck_ipst而所述反馈节点nfb的电压电平被补偿的情况下,在所述反馈前置级fbpst的保持时间ht期间,包括在所述反馈前置级fbpst中的第一充电晶体管t4_1a的泄漏电流、第一稳定化晶体管t2_1a的泄漏电流、第一反相晶体管t3_1a的泄漏电流、第三反相晶体管t5_1a的泄漏电流可以减小。

94.例如,在第二前置级pst2中,在保持时间ht期间在反馈节点nfb持续输入所述初始前置级ipst的时钟信号ck_ipst,因此第二q节点nq2可以在保持时间ht期间不产生由于连接所述反馈节点nfb与所述q节点nq的晶体管的泄漏电流。

95.例如,在第三前置级pst3中,在保持时间ht期间在反馈节点nfb持续输入所述初始前置级ipst的时钟信号ck_ipst,因此第三q节点nq3可以在保持时间ht期间不产生由于连接所述反馈节点nfb与所述q节点nq的晶体管的泄漏电流。

96.例如,在第四前置级pst4中,在保持时间ht的一部分区间期间在反馈节点nfb输入所述初始前置级ipst的时钟信号ck_ipst,因此第四q节点nq4可以在保持时间ht期间由于连接所述反馈节点nfb与所述q节点nq的晶体管的泄漏电流产生的区间相比于现有技术减小为1/3。例如,第四q节点nq4可以在保持时间ht期间由于连接所述反馈节点nfb与所述q节点nq的晶体管的泄漏电流产生的区间从3h减小为1h。即,在保持时间ht期间,可以将由于连接所述反馈节点nfb与所述q节点nq的晶体管的泄漏电流最小化。

97.如在图9中看到的,所述反馈前置级fbpst(参照图7)可以基于保持为正常电平的q节点nq的电压,生成进位信号。所述反馈前置级fbpst可以将所述进位信号输出于所述有源

级。在从所述反馈前置级fbpst接收所述进位信号的输入的情况下,有源级ast1~astx(参照图2)可以输出正常的感测信号以及正常的栅极信号。结果,所述栅极驱动部及包括其的显示装置可以使显示装置的显示品质提升。

98.图10是示出根据本发明的实施例的电子设备1000的框图,图11是示出图10的电子设备1000实现为智能电话的一例的图.

99.参照图10和图11,电子设备1000可以包括处理器1010、内存装置1020、存储装置1030、输入输出装置1040、电源1050以及显示装置1060。此时,显示装置1060可以是图1的显示装置。另外,电子设备1000可以还包括可以与视频卡、声卡、内存卡、usb装置等通信或者与其它系统通信的多种端口(port)。在一实施例中,如图11所示,电子设备1000可以实现为智能电话。但是,这是示例性的,电子设备1000不限于此。例如,电子设备1000也可以实现为移动电话、视频电话、智能平板、智能手表、平板pc、车用导航仪、计算机监视器、笔记本计算机、头戴式显示装置等。

100.处理器1010可以执行特定计算或者任务(task)。根据实施例,处理器1010可以为微处理器(micro processor)、中央处理单元(central processing unit)、应用处理器(application processor)等。处理器1010可以通过地址总线(address bus)、控制总线(control bus)以及数据总线(data bus)等与其它构成要件连接。根据实施例,处理器1010也可以与外设部件互连标准(peripheral component interconnect;pci)总线之类扩展总线连接。内存装置1020可以存储电子设备1000的工作需要的数据。例如,内存装置1020可以包括可擦可编程只读存储器(erasable programmable read-only memory;eprom)装置、带电可擦可编程只读存储器(electrically erasable programmable read-only memory;eeprom)装置、闪速存储器装置(flash memory device)、相变随机存取存储器(phase change random access memory;pram)装置、电阻随机存取存储器(resistance random access memory;rram)装置、纳米浮栅存储器(nano floating gate memory;nfgm)装置、聚合物随机存取存储器(polymer random access memory;poram)装置、磁性随机存取存储器(magnetic random access memory;mram)、铁电随机存取存储器(ferroelectric random access memory;fram)装置等之类非挥发性内存装置及/或动态随机存取存储器(dynamic random access memory;dram)装置、静态随机存取存储器(static random access memory;sram)装置、移动dram装置等之类挥发性内存装置。存储装置1030可以包括固态驱动器(solid state drive;ssd)、硬盘驱动器(hard disk drive;hdd)、光盘只读存储器(cd-rom)等。输入输出装置1040可以包括键盘、小键盘、触摸板、触摸屏、鼠标等之类输入部件以及扬声器、打印机等之类输出部件。根据实施例,显示装置1060也可以包括在输入输出装置1040中。电源1050可以供应电子设备1000的工作需要的电力。显示装置1060可以通过总线或者其它通信链路与其它构成要件连接。

101.显示装置1060可以显示与电子设备1000的视觉信息相应的图像。此时,显示装置1060可以将前置级的q节点的电压电平稳定化,从而使图像品质提升。为了此,显示装置1060可以包括显示面板、数据驱动部以及栅极驱动部。所述显示面板可以包括显示图像的显示部以及与所述显示部相邻的周边部。所述数据驱动部可以将数据电压施加于所述显示面板。所述栅极驱动部可以包括将栅极信号输出于所述显示部的多个有源级以及连接于所述有源级而向所述有源级输出进位信号的多个前置级。所述多个前置级可以包括第一前置

级以及第二前置级。在此,所述第二前置级可以包括q节点补偿部,q节点补偿部从所述第一前置级接收时钟信号的输入,并基于所述第一前置级的所述时钟信号补偿q节点的电压。

102.如此,根据本发明的前置级可以从之前前置级接收时钟信号的输入,并基于所述之前前置级的所述时钟信号补偿q节点的电压,以保持所述q节点的电压。结果,所述栅极驱动部及包括其的显示装置可以使显示装置的显示品质提升。但是,针对此有上述内容,因此关于其的重复说明将省略。

103.本发明可以适用于显示装置及包括其的电子设备。例如,本发明可以适用于移动电话、智能电话、视频电话、智能平板、智能手表、平板pc(个人计算机)、车用导航系统、电视、计算机监视器、笔记本计算机、数码相机、头戴式显示器等。

104.以上参照本发明的示例性实施例进行了说明,但是在本技术领域中具有通常的知识的人将可以理解在不脱离所附的权利要求书中记载的本发明的构思以及领域的范围内可以对本发明进行各种修改以及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1