收发器装置及其驱动方法与流程

收发器装置及其驱动方法

1.本技术要求于2021年6月25日提交的第10-2021-0083040号韩国专利申请的优先权和从该韩国申请获得的所有权益,上述韩国专利申请的内容通过引用全部并入本文。

技术领域

2.本公开涉及一种收发器装置和驱动收发器的方法。

背景技术:

3.随着信息技术的发展,作为用户和信息之间的连接媒介的显示装置的重要性被重视。因此,诸如液晶显示装置和有机发光显示装置的显示装置的使用日益增加。

技术实现要素:

4.通常,显示装置可以使用移动产业处理器接口(“mipi”)协议来执行内部通信。在使用mipi协议时,可以单独地使用时钟通道(例如,时钟线),从而物理/空间成本增加,并且功耗增加。

5.在具有时钟通道的发送器基于改变后的时钟信号而操作的情况下,即使发送器和接收器之间的数据传输速度由于执行跳频而改变以防止与基站的频率干扰,仍可能无法有效地执行水平同步信号的同步。另一方面,在使用时钟嵌入方法的发送器的情况下,当发送器和接收器之间的数据传输速度由于跳频而改变时,接收器(或时钟数据恢复电路)可能请求更多时间用于追踪改变后的频率信息和相位信息。

6.本公开的实施例提供了即使包括跳频时段但是仍能够使从发送器发送的水平同步信号与由接收器恢复的水平同步信号同步的时钟嵌入式收发器装置以及驱动收发器装置的方法。

7.根据本公开的实施例,收发器装置包括通过第一线和第二线彼此连接的发送器和接收器。在这样的实施例中,第一帧周期包括激活时段和垂直空白时段,在所述激活时段中,第一有效载荷从所述发送器传输到所述接收器,所述垂直空白时段包括跳频时段,在所述跳频时段中,所述发送器和所述接收器之间的数据传输速度是可变的。在这样的实施例中,所述发送器在第一模式中将具有第一电压范围的信号发送到所述第一线和所述第二线,并且在第二模式中将具有小于所述第一电压范围的第二电压范围的信号发送到所述第一线和所述第二线。在这样的实施例中,所述发送器在所述垂直空白时段的除了所述跳频时段之外的时段中在所述第二模式中生成第一水平同步信号,将所述第一水平同步信号编码为水平同步数据,并且在所述跳频时段中在所述第一模式中生成第二水平同步信号。在这样的实施例中,所述发送器在所述垂直空白时段的除了所述跳频时段之外的所述时段中将第一时钟训练图案添加到所述水平同步数据,并且在所述跳频时段结束之后将不同于所述第一时钟训练图案的第二时钟训练图案添加到第一水平同步数据。

8.在实施例中,所述第二时钟训练图案的长度可以比所述第一时钟训练图案的长度长。

9.在实施例中,所述第二时钟训练图案的长度可以基于所述数据传输速度的变化范围是可变的。

10.在实施例中,随着所述数据传输速度的所述变化范围增加,所述第二时钟训练图案的所述长度可以增加。

11.在实施例中,所述发送器可以通过在所述激活时段期间在所述第二模式中对原始有效载荷进行编码来生成所述第一有效载荷,并且通过所述第一线和所述第二线发送第三时钟训练图案和所述第一有效载荷。

12.在实施例中,所述发送器可以包括:数据发送器,生成第一内部时钟信号和第二内部时钟信号,并且在所述垂直空白时段期间将添加有所述第一时钟训练图案或所述第二时钟训练图案的第一编码数据发送到所述第一线和所述第二线;发送控制器,接收所述第一内部时钟信号和所述第二内部时钟信号,基于所述第一内部时钟信号在所述第二模式中生成所述第一水平同步信号,并且基于所述第二内部时钟信号在所述第一模式中生成所述第二水平同步信号;以及编码器单元,仅接收所述第一内部时钟信号和所述第二内部时钟信号中的所述第一内部时钟信号,通过基于所述第一内部时钟信号对从所述发送控制器接收的所述第一水平同步信号进行编码来生成所述水平同步数据,并且通过将所述第一时钟训练图案或所述第二时钟训练图案添加到所述水平同步数据来生成所述第一编码数据。

13.在实施例中,所述数据发送器可以在所述跳频时段期间仅生成所述第二内部时钟信号而不生成所述第一内部时钟信号。

14.在实施例中,所述发送控制器可以基于所述第一内部时钟信号将所述原始有效载荷发送到所述编码器单元。

15.在实施例中,所述编码器单元可以将从所述发送控制器提供的所述原始有效载荷编码为所述第一有效载荷。

16.在实施例中,所述发送器还可以包括跳频控制器,所述跳频控制器将关于所述跳频时段是否处于激活状态的第一寄存器值提供到所述编码器单元,并且所述第一寄存器值可以包括指示所述跳频时段从所述激活状态改变为非激活状态的第(1-1)寄存器值和指示所述跳频时段保持为所述激活状态或所述非激活状态的第(1-2)寄存器值。

17.在实施例中,所述发送控制器可以基于所述第一内部时钟信号向所述编码器单元提供指示所述跳频时段结束的结束标志信号。

18.在实施例中,所述编码器单元可以基于所述第(1-1)寄存器值和所述结束标志信号将所述第二时钟训练图案添加到所述水平同步数据。

19.在实施例中,所述跳频控制器可以将包括所述数据传输速度的变化范围信息的第二寄存器值提供到所述编码器单元。

20.在实施例中,所述第二寄存器值可以包括与第一数据传输速度变化范围对应的第(2-1)寄存器值、与第二数据传输速度变化范围对应的第(2-2)寄存器值和与第三数据传输速度变化范围对应的第(2-3)寄存器值,并且所述数据传输速度变化范围可以以所述第一数据传输速度变化范围、所述第二数据传输速度变化范围和所述第三数据传输速度变化范围的顺序增加。

21.在实施例中,所述编码器单元可以以所述第(2-1)寄存器值、所述第(2-2)寄存器值和所述第(2-3)寄存器值的顺序增加所述第二时钟训练图案的长度。

22.在实施例中,在所述第一模式中,所述第一线和所述第二线可以在单端方法中使用,并且在所述第二模式中,所述第一线和所述第二线可以在差分方法中使用。

23.根据本公开的实施例,一种驱动收发器装置的方法,所述收发器装置包括通过第一线和第二线彼此连接的发送器和接收器,第一帧周期包括激活时段和垂直空白时段,在所述激活时段中,第一有效载荷从所述发送器传输到所述接收器,所述垂直空白时段包括跳频时段,在所述跳频时段中,所述发送器和所述接收器之间的数据传输速度是可变的,所述方法包括:在第一模式中从所述发送器向所述接收器发送具有第一电压范围的信号;在第二模式中从所述发送器向所述接收器发送具有小于所述第一电压范围的第二电压范围的信号;由包括在所述发送器中的数据发送器生成第一内部时钟信号和第二内部时钟信号;由包括在所述发送器中的所述发送控制器在所述垂直空白时段的除了所述跳频时段之外的时段中基于所述第一内部时钟信号在所述第二模式中生成第一水平同步信号,并且由包括在所述发送器中的所述发送控制器在所述跳频时段中在所述第一模式中生成第二水平同步信号;以及由包括在所述发送器中的编码器单元在所述垂直空白时段的除了所述跳频时段之外的所述时段中在所述第二模式中将所述第一水平同步信号编码为水平同步数据,并且将第一时钟训练图案添加到所述水平同步数据,所述方法还可以包括:由所述编码器单元确定是否发生了跳频,并且所述方法还可以包括:当确定出发生了所述跳频时,由所述编码器单元在所述跳频时段结束之后将不同于所述第一时钟训练图案的第二时钟训练图案添加到第一水平同步数据。

24.在实施例中,所述第二时钟训练图案的长度可以比所述第一时钟训练图案的长度长。

25.在实施例中,所述添加所述第二时钟训练图案可以包括:响应于所述数据传输速度的变化范围改变所述第二时钟训练图案的长度。

26.在实施例中,所述改变所述第二时钟训练图案的所述长度可以包括:随着数据传输速度变化范围增加,增加所述第二时钟训练图案的所述长度。

27.在实施例中,所述方法还可以包括由包括在所述发送器中的跳频控制器将关于所述跳频时段是否处于激活状态的第一寄存器值提供到所述编码器单元,并且所述第一寄存器值可以包括指示所述跳频时段从所述激活状态改变为非激活状态的第(1-1)寄存器值和指示所述跳频时段保持为所述激活状态或所述非激活状态的第(1-2)寄存器值。

28.在实施例中,所述方法还可以包括:由所述发送控制器基于所述第一内部时钟信号向所述编码器单元提供指示所述跳频时段结束的结束标志信号。

29.在实施例中,所述确定是否发生了所述跳频可以包括:当所述编码器单元接收到所述第(1-1)寄存器值和所述结束标志信号时,由所述编码器单元确定发生了所述跳频。

30.在收发器装置和驱动收发器装置的方法的实施例中,即使包括跳频时段,但是通过调整添加到编码的水平同步信号的时钟训练图案的长度,可以使从发送器发送的水平同步信号和由接收器恢复的水平同步信号同步。

附图说明

31.通过参考附图进一步详细描述本公开的实施例,本公开的以上和其他特征将变得更加明显,在附图中:

32.图1a是示出了根据本公开的实施例的显示装置的框图;

33.图1b是根据本公开的实施例的在显示装置中生成的信号的时序图;

34.图2和图3是示出了收发器装置的实施例的图;

35.图4和图5是示出了包括在图2和图3的收发器装置中的发送器的操作的实施例的图;

36.图6是示出了包括在图2和图3的收发器装置中的接收器的操作的实施例的图;

37.图7a和图7b是示出了根据本公开的实施例的收发器装置的图;

38.图8和图9是示出了包括在图7a和图7b的收发器装置中的发送器的操作的实施例的图;

39.图10是示出了包括在图7a和图7b的收发器装置中的接收器的操作的实施例的图;

40.图11是示出了包括在图7a和图7b的收发器装置中的发送器的实施例的框图;

41.图12是示出了在垂直空白时段中发送器的操作的图;

42.图13是示出了包括在图7a和图7b的收发器装置中的发送器的另一实施例的框图;

43.图14是示出了第二时钟训练图案(pattern)的长度响应于收发器装置的数据传输速度变化范围而改变的实施例的曲线图;以及

44.图15是示出了响应于收发器装置的数据传输速度变化范围来改变第二时钟训练图案的长度的发送器的操作的图。

具体实施方式

45.现在将在下文中参照附图更充分地描述本发明,在附图中示出了各种实施例。然而,本发明可以以许多不同的形式来实施,而不应该被解释为局限于这里阐述的实施例。而是,提供这些实施例使本公开将是彻底的且完整的,并将把本发明的范围充分地传达给本领域的技术人员。

46.为了清楚地描述本公开,省略了与描述无关的部分,并且贯穿说明书,相同的或类似的组件由相同的附图标记指示。因此,在其他附图中可以使用上面描述的附图标记。

47.另外,为了便于描述而任意地示出了在附图中示出的每个组件的尺寸和厚度,并且因此,本公开不必限于在附图中示出的那样。在附图中,为了清楚地表达各种层和区域,可能夸大了厚度。

48.另外,在描述中,表述“相同”可以意味着“基本上相同”。即,表述“相同”可以是足以使本领域普通技术人员理解其是相同的相同。其他表述也可以是其中省略了“基本上”的表述。

49.本文中使用的术语仅是为了描述特定实施例的目的,而不意图是限制性的。如这里使用的,除非上下文另外明确指出,否则“一个”、“一种”、“所述(该)”和“至少一个(种)”并不指示对量的限制,并且旨在包括单数和复数两者。例如,除非上下文另外明确指出,否则“元件”具有与“至少一个元件”相同的含义。“至少一个(种)”不应解释为限制性的“一个”或“一种”。“或”是指“和/或”。如本文中使用的,术语“和/或”包括一个或多个相关所列项的任何和所有组合。将进一步理解,当在本说明书中使用术语“包括”和/或“包含”或“含有”和/或“包含有”时,说明存在陈述的特征、区域、整数、步骤、操作、元件、组件和/或它们的组,但不排除存在或附加一个或多个其他特征、区域、整数、步骤、操作、元件、组件和/或它

们的组。

50.此外,本文中可以使用诸如“下”或“底”和“上”或“顶”的相对术语来描述如图中所示的一个元件与另一元件的关系。将理解的是,相对术语意在涵盖除了在附图中描绘的方位之外的装置的不同方位。例如,如果一幅附图中的装置被翻转,则描述为在其他元件的“下”侧的元件将随后定向在其他元件的“上”侧。因此,根据附图的特定方位,术语“下”可涵盖“下”和“上”这两个方位。类似地,如果一幅附图中的装置被翻转,则描述为“在”其他元件“下方”或“之下”的元件将随后定向为“在”其他元件“上方”。因此,术语“在

…

下方”或“在...之下”可以覆盖上方和下方两个方位。

51.除非另有定义,否则这里使用的所有术语(包括技术术语和科学术语)具有与本公开所属领域的普通技术人员所通常理解的相同的意思。将进一步理解,除非这里明确地如此定义,否则术语(例如在通用的字典中定义的术语)应该被解释为具有与它们在相关领域和本公开的上下文中的意思一致的意思,并且将不以理想的或过于形式化的意思来解释。

52.在下文中,将参照附图详细地描述本公开的实施例。

53.图1a是示出了根据本公开的实施例的显示装置的框图。图1b是根据本公开的实施例的在显示装置中生成的信号的时序图。

54.参照图1a,显示装置1000的实施例可以包括显示模块10和处理器20。

55.在实施例中,稍后将描述的图7a或图7b的收发器装置tscv可以在显示模块10和处理器20之间执行通信和数据发送/接收。

56.显示模块10可以包括时序控制器11、数据驱动器12、扫描驱动器13、像素单元14和发射驱动器15。在实施例中,根据显示装置1000的规范,显示模块10的功能单元可以集成到单个集成电路(“ic”)中,集成到多个ic中,或安装在显示基底上。在实施例中,时序控制器11和数据驱动器12可以集成到单个ic中,以构成一个显示驱动器100。在这样的实施例中,稍后将详细描述的显示驱动器100可以被称为时序控制器嵌入式驱动器ic(“ted”)。根据类型,显示驱动器100还可以包括扫描驱动器13和发射驱动器15中的至少一个。

57.处理器20可以对应于从图形处理单元(“gpu”)、中央处理单元(“cpu”)和应用处理器(“ap”)等中选择的至少一个。在实施例中,处理器20可以输出将在显示模块10中使用的图像数据。

58.处理器20可以包括稍后将描述的图7a或图7b的发送器txd。在实施例中,时序控制器11、数据驱动器12或显示驱动器100可以包括稍后将描述的图7a或图7b的接收器rxd。

59.时序控制器11可以从处理器20接收用于每个显示帧周期的灰度和时序信号。时序信号可以包括垂直同步信号vsync、水平同步信号hsync和数据使能信号de等。

60.垂直同步信号vsync可以包括多个脉冲,并且可以基于生成每个脉冲的时间点指示前一帧周期结束并且当前帧周期开始。在垂直同步信号vsync中,相邻的脉冲之间的间隔可以对应于一个帧周期。水平同步信号hsync可以包括多个脉冲,并且可以基于生成每个脉冲的时间点指示前一水平周期结束并且新的水平周期开始。数据使能信号de可以指示在水平周期中供给图像数据。响应于数据使能信号de,可以在水平周期中在像素行中供给图像数据。与一个帧对应的图像数据可以被称为一个输入图像。

61.时序控制器11可以将渲染的或未渲染的灰度提供到数据驱动器12。另外,时序控制器11可以将数据驱动控制信号提供到数据驱动器12。

62.时序控制器11可以将扫描驱动控制信号提供到扫描驱动器13,并且可以将发射驱动控制信号提供到发射驱动器15。

63.数据驱动器12可以使用从时序控制器11接收的灰度和数据驱动控制信号生成将提供到数据线dl1、dl2、dl3、dl4、...和dln(其中,n是大于0的整数)的数据电压(即,数据信号)。

64.扫描驱动器13可以使用从时序控制器11接收的扫描驱动控制信号(例如,时钟信号和扫描开始信号等)分别生成将提供到扫描线sl0、sl1、sl2、...和slm的扫描信号s0、s1、s2、...和sm(其中,m是大于0的整数)。扫描驱动器13可以将包括导通电平的脉冲的扫描信号s0、s1、s2、...和sm顺序地供给到扫描线sl0、sl1、sl2、...和slm。

65.发射驱动器15可以使用从时序控制器11接收的发射驱动控制信号(例如,时钟信号和发射控制开始信号等)生成将提供到发射控制线el1、el2、el3、

…

和elo(其中,o是大于0的整数)的发射控制信号。发射驱动器15可以将发射控制信号顺序地供给到发射控制线el1、el2、el3、

…

和elo。

66.像素单元14包括像素pxij(其中,i是小于或等于m的正整数,并且j是小于或等于n的正整数)。像素pxij可以连接到相应的数据线、扫描线和发射控制线。像素pxij可以发射具有与数据信号对应的亮度的光。

67.参照图1a和图1b,一个帧周期f可以包括激活时段actp和垂直空白时段bp。为了便于描述,在图1b中,垂直空白时段bp仅包括帧周期f结束的时间点处的后肩时段,但是本公开不限于此,并且在实施例中,垂直空白时段bp还可以包括帧周期f开始的时间点处的前肩时段。在这样的实施例中,前肩时段可以指帧周期f开始的时间点和数据信号的输入开始的时间点之间的时段,并且后肩时段可以指数据信号的输入结束的时间点和帧周期f结束的时间点之间的时段。

68.垂直同步信号vsync限定帧周期f,并且水平同步信号hsync限定一个水平周期1h。水平同步信号hsync可以包括在激活时段actp和垂直空白时段bp中具有预定间隔(例如,一个水平周期1h)的脉冲。

69.在激活时段actp期间,数据使能信号de可以包括与扫描线sl0、sl1、sl2、...和slm的数目对应的脉冲数目。在垂直空白时段bp期间,数据使能信号de可以保持在预定电平(例如,低电平)。

70.扫描信号s0、s1、s2、...和sm是由扫描驱动器13生成并提供到扫描线sl0、sl1、sl2、...和slm的信号。在一个帧周期f期间,扫描信号s0、s1、s2、...和sm顺序地被激活至高电平。在一个实施例中,例如,在提供到扫描线sl1的扫描信号s1处于高电平的同时,数据信号可以被提供到连接到扫描线sl1的一行像素pxij。即,一个水平周期1h是当一行像素pxij被驱动时的时间。在下文中,将参照图2至图10详细地描述收发器装置的实施例。

71.图2和图3是示出了收发器装置的实施例的图。

72.参照图2和图3,收发器装置tscvr的实施例可以包括发送器txdr和接收器rxdr。

73.在实施例中,如图2中所示,发送器txdr可以包括发送控制器txcr、多个数据发送器tx1r、tx2r、tx3r和tx4r以及时钟发送器tcr。接收器rxdr可以包括接收控制器rxcr、多个数据接收器rx1r、rx2r、rx3r和rx4r以及时钟接收器rcr。

74.第一数据发送器tx1r可以通过第一线dp1r(或第一数据通道)和第二线dn1r(或第

二数据通道)连接到第一数据接收器rx1r。第一数据发送器tx1r和第一数据接收器rx1r可以被称为第一数据信道。第二数据发送器tx2r可以通过第一线dp2r和第二线dn2r连接到第二数据接收器rx2r。第二数据发送器tx2r和第二数据接收器rx2r可以被称为第二数据信道。第三数据发送器tx3r可以通过第一线dp3r和第二线dn3r连接到第三数据接收器rx3r。第三数据发送器tx3r和第三数据接收器rx3r可以被称为第三数据信道。第四数据发送器tx4r可以通过第一线dp4r和第二线dn4r连接到第四数据接收器rx4r。第四数据发送器tx4r和第四数据接收器rx4r可以被称为第四数据信道。

75.时钟发送器tcr可以通过第一时钟线cp1r(或第一时钟通道)和第二时钟线cn1r(或第二时钟通道)连接到时钟接收器rcr。时钟发送器tcr和时钟接收器rcr可以被称为时钟信道。

76.数据发送器tx1r、tx2r、tx3r和tx4r、时钟发送器tcr、数据接收器rx1r、rx2r、rx3r和rx4r以及时钟接收器rcr可以对应于osi 7层模型的物理层和数据链路层,可以对应于tcp/ip协议的网络接口,或可以对应于移动产业处理器接口(“mipi”)协议的物理层。mipi协议的物理层可以根据诸如d-phy、c-phy和m-phy的各种预定的规范来配置。在下文中,为了便于描述,将详细地描述多个数据发送器tx1r、tx2r、tx3r和tx4r、时钟发送器tcr、多个数据接收器rx1r、rx2r、rx3r和rx4r以及时钟接收器rcr根据mipi协议的物理层之中的d-phy规范来配置的实施例。

77.发送控制器txcr和接收控制器rxcr可以对应于osi 7层模型的网络层和传输层,可以对应于tcp/ip协议的因特网和传输,或可以对应于mipi协议的协议层。mipi协议的协议层可以根据诸如显示串行接口(“dsi”)和相机串行接口(“csi”)的各种预定义的规范来配置。在下文中,为了便于描述,将详细地描述发送控制器txcr和接收控制器rxcr根据mipi协议的协议层之中的dsi规范来配置的实施例。

78.在实施例中,发送控制器txcr、数据发送器tx1r、tx2r、tx3r和tx4r以及时钟发送器tcr可以在硬件中彼此分开地配置,或可以具有其至少两个集成在硬件中的配置。在可选的实施例中,发送控制器txcr、数据发送器tx1r、tx2r、tx3r和tx4r以及时钟发送器tcr可以在软件中彼此分开地配置,或可以具有其至少两个集成在软件中的配置。

79.根据实施例,发送器txdr可以被配置为另一控制器(例如,ap、gpu或cpu等)的一部分(硬件或软件),或可以被配置为独立的硬件(例如,发送专用ic)。

80.接收控制器rxcr、数据接收器rx1r、rx2r、rx3r和rx4r以及时钟接收器rcr可以在硬件中彼此分开地配置,或可以具有其至少两个集成在硬件中的配置。接收控制器rxcr、数据接收器rx1r、rx2r、rx3r和rx4r以及时钟接收器rcr可以在软件中彼此分开地配置,或可以具有其至少两个集成在软件中的配置。

81.根据实施例,接收器rxdr可以被配置为另一控制器(例如,包括在显示装置中的时序控制器、ted或驱动器ic(“d-ic”)等)的一部分(硬件或软件),或可以被配置为独立的硬件(例如,接收专用ic)。

82.在实施例中,如图2中所示,收发器装置tscvr可以包括四个数据信道,并且这四个数据信道可以彼此独立地发送和接收数据。这四个数据信道可以共享提供到一个时钟信道的时钟信号。

83.在可选的实施例中,如图3中所示,可以提供包括单个数据信道的收发器装置

tscvr。在一个实施例中,例如,发送器txdr可以包括单个第一数据发送器tx1r,并且接收器rxdr可以包括单个第一数据接收器rx1r。

84.发送控制器txcr可以将第一数据data1提供到第一数据发送器tx1r,并且将发送时钟信号txclk提供到时钟发送器tcr。

85.第一数据发送器tx1r可以通过第一线dp1r和第二线dn1r发送第一数据data1。在这样的实施例中,第一数据发送器tx1r可以根据预定协议通过在第一数据data1之前和之后(或前面和后面)添加其他数据来发送其他数据。

86.时钟发送器tcr可以通过第一时钟线cp1r和第二时钟线cn1r发送发送时钟信号txclk。

87.时钟接收器rcr可以将通过第一时钟线cp1r和第二时钟线cn1r接收的接收时钟信号rxclk提供到第一数据接收器rx1r。

88.第一数据接收器rx1r可以基于接收时钟信号rxclk对通过第一线dp1r和第二线dn1r接收的数据进行采样。第一数据接收器rx1r可以将包括与第一数据data1相同的有效载荷的第二数据data2提供到接收控制器rxcr。在实施例中,第一数据接收器rx1r可以将根据协议的多个控制信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs提供到接收控制器rxcr。

89.图4和图5是示出了包括在图2和图3的收发器装置中的发送器的操作的实施例的图。

90.参照图2、图4和图5,发送器txdr(例如,第一数据发送器tx1r)的实施例可以通过根据预定协议在有效载荷payload之前和之后(或前面和后面)添加其他数据来发送数据。

91.在实施例中,如图4中所示,第一数据发送器tx1r可以接收包括有效载荷payload的第一数据data1。第一数据data1可以包括图像信息等。在实施例中,第一数据发送器tx1r可以基于mipi协议顺序地发送第一图案hs-zero、第二图案hs-sync、有效载荷payload、第三图案hs-trail和第四图案hs-exit。

92.在实施例中,如图5中所示,发送器txdr(例如,第一数据发送器tx1r)可以在第一模式mode1中将具有第一电压范围vr1的信号发送到第一线dp1r和第二线dn1r。在实施例中,发送器txdr可以在第二模式mode2中将具有小于第一电压范围vr1的第二电压范围vr2的信号发送到第一线dp1r和第二线dn1r。

93.在一个实施例中,例如,第一电压范围vr1的上限可以大于第二电压范围vr2的上限,并且第一电压范围vr1的下限可以小于或等于第二电压范围vr2的下限。在mipi协议应用于收发器装置tscvr的实施例中,第一模式mode1可以是低功率(“lp”)模式,并且第二模式mode2可以是高速(“hs”)模式。

94.在第一模式mode1中,第一线dp1r和第二线dn1r可以彼此独立地在单端方法中使用(或使用单端信令而操作)。即,在第一模式mode1中传输到第一线dp1r和第二线dn1r中的每一者的信号可以彼此相同或不同。在一个实施例中,例如,在第一模式mode1中第一线dp1r和第二线dn1r的组合可以具有四种状态(例如,第一线dp1r高并且第二线dn1r高,第一线dp1r高并且第二线dn1r低,第一线dp1r低并且第二线dn1r高,以及第一线dp1r低并且第二线dn1r低)之一。

95.在第二模式mode2中,第一线dp1r和第二线dn1r可以在差分方法中使用(或使用差

分信令而操作)。即,在第二模式mode2中传输到第一线dp1r和第二线dn1r中的每一者的信号可以彼此不同。因此,在第二模式mode2中第一线dp1r和第二线dn1r的组合可以具有两种状态(例如,第一线dp1r高并且第二线dn1r低,以及第一线dp1r低并且第二线dn1r高)之一。

96.为了通知从第一模式mode1向第二模式mode2的切换,发送器txdr可以将预定义的图案(例如,图案lp-11、图案lp-01和图案lp-00)发送到第一线dp1r和第二线dn1r。在一个实施例中,例如,发送器txdr可以在第一时间点t1a(lp-11图案)之前将施加到第一线dp1r和第二线dn1r的信号保持在逻辑高电平。当供给的信号的电压电平大于预定义的第一阈值电压电平时,发送的信号可以被确定为逻辑高电平,并且当供给的信号的电压电平小于预定义的第二阈值电压电平时,发送的信号可以被确定为逻辑低电平。

97.之后,发送器txdr可以在包括时间点t1a的时段期间将第一线dp1r的信号改变为逻辑低电平,并且将第二线dn1r的信号保持为逻辑高电平(即,图案lp-01)。

98.在包括第二时间点t2a的时段期间,发送器txdr可以将第一线dp1r的信号保持为逻辑低电平,并且将第二线dn1r的信号改变为逻辑低电平(即,图案lp-00)。在第一模式mode1中的数据发送通过图案lp-11、lp-01和lp-00而结束,并且收发器装置tscvr可以指示收发器装置tscvr处于从第一模式mode1切换到第二模式mode2的转变状态。

99.在第二模式mode2中,发送器txdr可以将第一图案hs-zero、第二图案hs-sync、有效载荷payload、第三图案hs-trail和第四图案hs-exit顺序地发送到接收器rxdr。在一个实施例中,例如,发送器txdr可以在从第三时间点t3a到第四时间点t4a的时段期间发送第一图案hs-zero,在从第四时间点t4a到第五时间点t5a的时段期间发送第二图案hs-sync,在从第五时间点t5a到第六时间点t6a的时段期间发送有效载荷payload,在从第六时间点t6a到第七时间点t7a的时段期间发送第三图案hs-trail,并且在第七时间点t7a之后发送第四图案hs-exit。第一图案hs-zero、第二图案hs-sync、第三图案hs-trail和第四图案hs-exit中的每一个可以是数字格式的数据图案。

100.第一图案hs-zero可以是用于通知在从第一模式mode1进入第二模式mode2之后的等待时段的图案。在一个实施例中,例如,第一图案hs-zero可以是其中重复0的图案。

101.第二图案hs-sync可以是通知有效载荷payload的传输开始的图案。在一个实施例中,例如,第二图案hs-sync可以具有oxb8h值或00011101值。

102.有效载荷payload可以是待传输的有效数据。因此,有效载荷payload可以包括除了预定图案之外的可变值。在一个实施例中,例如,有效载荷payload可以包括图像数据。

103.第三图案hs-trail可以是通知有效载荷payload的传输结束的图案。第三图案hs-trail可以是其中重复与有效载荷payload的最后数据相反的值的图案。在一个实施例中,例如,当有效载荷payload的最后数据(位)是0时,第三图案hs-trail可以是其中重复1的图案。可选地,当有效载荷payload的最后数据(位)是1时,第三图案hs-trail可以是其中重复0的图案。

104.第四图案hs-exit可以是通知第二模式mode2结束并且第一模式mode1开始的图案。第四图案hs-exit可以不由特定位构成,而可以是其中电压升高以超出第二电压范围vr2的传统图案。

105.发送器txdr可以在从第八时间点t8a到第九时间点t9a的时段期间将施加到第一线dp1r和第二线dn1r的信号改变为逻辑高电平(即,图案lp-11)。因此,发送器txdr可以通

知第二模式mode2结束并且第一模式mode1开始。

106.发送器txdr(具体地,时钟发送器tcr)可以在第一模式mode1和第二模式mode2中通过第一时钟线cp1r和第二时钟线cn1r以差分模式将发送时钟信号txclk发送到接收器rxdr的时钟接收器rcr。第一数据接收器rx1r可以基于接收时钟信号rxclk(参考图3)对在第二模式mode2中接收的数据进行采样。

107.图6是示出了包括在图2和图3的收发器装置中的接收器的操作的实施例的图。

108.参照图2和图6,接收器rxdr(例如,第一数据接收器rx1r)的实施例可以根据预设的通信协议(例如,mipi协议)生成第二数据data2以及信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs。

109.时钟信号rxbyteclkhs可以是用于通知字节单元的数据传输单元的高速传输字节时钟信号。在一个实施例中,例如,控制信号rxbyteclkhs可以指示对于控制信号rxbyteclkhs的每一个循环传输第二数据data2的一个字节。

110.第二数据data2可以包括附加信息c和由字节单元b1、b2、b3、b4、b5、...和bn构成的有效载荷payload。在一个实施例中,例如,附加信息c可以是与从时间点t3b到时间点t4b的第三图案hs-trail对应的信息。在一个实施例中,例如,附加信息c可以是其中重复0或重复1的8位信息。

111.在一个实施例中,例如,第一数据接收器rx1r可以通过解串器将采样的有效载荷payload和第三图案hs-trail并行化(例如,并行化为8行),并且将并行化的第二数据data2发送到接收控制器rxcr。

112.在第一时间点t1b处,第一接收控制信号rxactivehs的逻辑电平可以从第一电平(例如,逻辑低电平)改变为第二电平(例如,逻辑高电平)。第一时间点t1b可以对应于从在第二数据data2的传输开始的第二时间点t2b的时钟信号rxbyteclkhs之前的一个循环。第一数据接收器rx1r可以基于图5的在第二图案hs-sync结束的第五时间点t5a确定第一时间点t1b。

113.在第二时间点t2b处,第二接收控制信号rxvalidhs的逻辑电平可以从第一电平改变为第二电平。在第二时间点t2b处,第二数据data2的有效载荷payload的第一数据b1的输出可以开始。第二时间点t2b可以是从第一时间点t1b开始的时钟信号rxbyteclkhs之后的一个周期。

114.在第一时间点t1b处,第三接收控制信号rxsynchs的逻辑电平可以从第一电平改变为第二电平,并且在第二时间点t2b处,第三接收控制信号rxsynchs的逻辑电平可以从第二电平改变为第一电平。第三接收控制信号rxsynchs可以限定第一接收控制信号rxactivehs和第二接收控制信号rxvalidhs之间的转变间隔,并且可以根据mipi协议来确定输出和功能。

115.图7a和图7b是示出了根据本公开的实施例的收发器装置的图。

116.除了去除了时钟发送器tcr、时钟接收器rcr以及时钟线cp1r和cn1r并且添加了编码器单元enc、解码器单元dec和延迟单元dly之外,图7a和图7b的收发器装置tscv具有与图2和图3的收发器装置tscvr的配置基本上相同或类似的配置。图7a和图7b中示出的相同或类似的元件已经用如上面用于描述图2和图3中示出的收发器装置tscvr的实施例的相同的附图标记来标记,并且在下文中将省略或简化其任何重复的详细描述。

117.参照图7a和图7b,收发器装置tscv的实施例可以包括发送器txd和接收器rxd。

118.发送器txd可以包括发送控制器txc(例如,发送链路模块)、第一数据发送器tx1(例如,发送d-phy模块)和编码器单元enc。接收器rxd可以包括接收控制器rxc(例如,接收链路模块)、第一数据接收器rx1(例如,接收d-phy模块)和解码器单元dec。

119.第一数据发送器tx1可以通过第一线dp1和第二线dn1连接到第一数据接收器rx1。第一数据发送器tx1和第一数据接收器rx1可以被称为第一数据信道。在下文中,为了便于描述,将详细地描述第一数据发送器tx1和第一数据接收器rx1根据mipi协议的物理层之中的d-phy规范来配置并且发送控制器txc和接收控制器rxc根据mipi协议的协议层之中的dsi规范来配置的实施例。然而,第一数据发送器tx1、第一数据接收器rx1、发送控制器txc和接收控制器rxc不限于此,并且可以应用于各种标准的接口。

120.在实施例中,发送控制器txc、第一数据发送器tx1和编码器单元enc可以在硬件中彼此分开地配置,或可以具有其两个或多个集成在硬件中的配置。在实施例中,发送控制器txc、第一数据发送器tx1和编码器单元enc可以在软件中彼此分开地配置,或可以具有其两个或多个集成在软件中的配置。在实施例中,发送器txd可以被配置为预定处理装置(例如,ap、gpu或cpu等)的一部分(硬件或软件),或可以被配置为独立的硬件(例如,发送专用ic)。

121.在实施例中,接收控制器rxc、第一数据接收器rx1、解码器单元dec和延迟单元dly可以在硬件中彼此分开地配置,或可以具有其两个或多个集成在硬件中的配置。在实施例中,接收控制器rxc、第一数据接收器rx1、解码器单元dec和延迟单元dly可以在软件中彼此分开地配置,或可以具有其两个或多个集成在软件中的配置。在实施例中,接收器rxd可以被配置为预定装置(例如,时序控制器、ted或d-ic等)的一部分(硬件或软件),或可以被配置为独立的硬件(例如,接收专用ic)。

122.发送控制器txc可以将包括原始有效载荷payload的第一数据data1提供到编码器单元enc。编码器单元enc可以对第一数据data1进行编码以生成包括第一有效载荷epayload(或编码有效载荷)的第一编码数据edata1,并且将第一编码数据edata1提供到第一数据发送器tx1。第一数据发送器tx1可以根据预定协议通过在第一编码数据edata1之前和之后(或前面和后面)添加其他数据来发送其他数据。

123.在实施例中,在稍后将参照图12描述的跳频时段fhp中,发送控制器txc可以在第一模式中生成水平同步信号hsync_m1,并且将水平同步信号hsync_m1直接发送到第一数据发送器tx1。在垂直空白时段bp的除了跳频时段fhp之外的时段bp1和bp2(在图12中示出)中,发送控制器txc可以在第二模式中生成水平同步信号hsync_m2,并且将水平同步信号hsync_m2发送到编码器单元enc,并且编码器单元enc可以对水平同步信号hsync_m2进行编码以生成图8的第一有效载荷epayload(或水平同步数据hsync_m2’),并且通过在图8的第一有效载荷epayload(或水平同步数据hsync_m2’)之前和之后(或前面和后面)添加预定数据来生成图8的第一编码数据edata1。在一个实施例中,例如,图8的第一编码数据edata1可以依次包括图8的时钟训练图案clk-t、图8的开始图案stp、图8的第一有效载荷epayload和图8的结束图案edp。

124.第一数据接收器rx1可以使用第一编码数据edata1生成时钟信号rxbyteclkhs,并且基于生成的时钟信号rxbyteclkhs对通过第一线dp1和第二线dn1接收的数据进行采样。在一个实施例中,例如,第一数据接收器rx1可以包括时钟数据恢复电路。

125.第一数据接收器rx1可以将包括与第一编码数据edata1基本上相同的第一有效载荷epayload的第二编码数据edata2提供到解码器单元dec。

126.解码器单元dec可以对第二编码数据edata2进行解码以生成包括与第一数据data1相同的有效载荷payload的第二数据data2,并且将第二数据data2提供到接收控制器rxc。

127.在实施例中,在除了图12的垂直空白时段bp的跳频时段fhp之外的图12的时段bp1和bp2中,第一数据接收器rx1可以将包括与第一编码数据edata1基本上相同的图8的第一有效载荷epayload的第二编码数据edata2(或水平同步数据hsync_m2’)提供到解码器单元dec。

128.解码器单元dec可以对第二编码数据edata2进行解码以生成包括与第一数据data1相同的有效载荷payload的第二数据data2以及水平同步信号hsync_m2,并且将第二数据data2和水平同步信号hsync_m2提供到接收控制器rxc。

129.在实施例中,第一数据接收器rx1可以根据应用于收发器装置tscv的协议生成多个信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs。在这样的实施例中,延迟单元dly可以将信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs延迟解码时间,并且将信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs提供到接收控制器rxc。解码时间可以是解码器单元dec用于解码第二编码数据edata2以生成第二数据data2所用的时间。

130.根据实施例,如图7a中所示,收发器装置tscv可以配置有单个数据信道,但是不限于此。可选地,收发器装置tscv可以配置有多个数据信道(例如,四个数据信道),如图7b中所示。

131.在实施例中,如图7b中所示,发送器txd还可以包括第二数据发送器tx2、第三数据发送器tx3和第四数据发送器tx4以及相应的编码器单元encb、encc和encd。接收器rxd可以包括第二数据接收器rx2、第三数据接收器rx3和第四数据接收器rx4以及相应的解码器单元decb、decc和decd。在这样的实施例中,接收器rxd还可以包括控制信号生成器csg和延迟单元dly。

132.第二数据发送器tx2可以通过第一线dp2和第二线dn2连接到第二数据接收器rx2。第二数据发送器tx2和第二数据接收器rx2可以被称为第二数据信道。第三数据发送器tx3可以通过第一线dp3和第二线dn3连接到第三数据接收器rx3。第三数据发送器tx3和第三数据接收器rx3可以被称为第三数据信道。第四数据发送器tx4可以通过第一线dp4和第二线dn4连接到第四数据接收器rx4。第四数据发送器tx4和第四数据接收器rx4可以被称为第四数据信道。多个数据信道可以彼此独立地发送和接收数据。

133.因为在第一模式中生成水平同步信号hsync_m1b、hsync_m1c和hsync_m1d并且在跳频时段fhp(参照图12)中将水平同步信号hsync_m1b、hsync_m1c和hsync_m1d直接发送到第二数据发送器tx2、第三数据发送器tx3和第四数据发送器tx4中的每一者的发送控制器txc的操作与上面描述的在第一模式中生成水平同步信号hsync_m1并且在跳频时段fhp中将水平同步信号hsync_m1直接发送到第一数据发送器tx1的发送控制器txc的操作相同,所以将省略其任何重复的详细描述。

134.因为在第二模式中生成水平同步信号hsync_m2b、hsync_m2c和hsync_m2d并且在垂直空白时段bp的除了跳频时段之外的时段bp1和bp2(图12中示出)中将水平同步信号

hsync_m2b、hsync_m2c和hsync_m2d发送到编码器单元encb、encc和encd中的每一者的发送控制器txc的操作以及对水平同步信号hsync_m2b、hsync_m2c和hsync_m2d中的每一者进行编码以生成图8的第一有效载荷epayload(或水平同步数据hsync_m2b’、hsync_m2c’和hsync_m2d’)并且通过在图8的第一有效载荷epayload(或水平同步数据hsync_m2b’、hsync_m2c’和hsync_m2d’)之前和之后(或前面和后面)添加预定数据来生成图8的第一编码数据edata1b、edata1c和edata1d的编码器单元encb、encc和encd中的每一者的操作与上面描述的在第二模式中生成水平同步信号hsync_m2并且在垂直空白时段bp的除了跳频时段之外的时段bp1和bp2中将水平同步信号hsync_m2发送到编码器单元enc的发送控制器txc的操作以及对水平同步信号hsync_m2进行编码以生成图8的第一有效载荷epayload(或水平同步数据hsync_m2’)并且通过在图8的第一有效载荷epayload(或水平同步数据hsync_m2’)之前和之后(或前面和后面)添加预定数据来生成图8的第一编码数据edata1的编码器单元enc的操作相同,所以将省略其任何重复的详细描述。

135.因为对数据data1b、data1c和data1d进行编码以生成编码数据edata1b、edata1c和edata1d的编码器单元encb、encc和encd的操作与上面描述的编码器单元enc的操作基本上相同,所以将省略其任何重复的详细描述。

136.因为对编码数据edata2b、edata2c和edata2d(或水平同步数据hsync_m2b’、hsync_m2c’和hsync_m2d’)进行解码以生成数据data2b、data2c和data2d以及水平同步信号hsync_m2b、hsync_m2c和hsync_m2d的解码器单元decb、decc和decd的操作与上面描述的解码器单元dec的操作基本上相同,所以将省略其任何重复的详细描述。

137.控制信号生成器csg可以使用由第一数据接收器rx1、第二数据接收器rx2、第三数据接收器rx3和第四数据接收器rx4接收的数据生成控制信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs以及时钟信号rxbyteclkhs。在一个实施例中,例如,控制信号生成器csg可以将由第一数据接收器rx1、第二数据接收器rx2、第三数据接收器rx3和第四数据接收器rx4接收的数据的时序对齐,并且基于对齐的数据生成控制信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs以及时钟信号rxbyteclkhs。

138.延迟单元dly可以将控制信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs以及时钟信号rxbyteclkhs延迟解码时间,并且将多个控制信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs以及时钟信号rxbyteclkhs提供到接收控制器rxc。在本文中,解码时间可以是解码器单元dec、decb、decc和decd用于对第二编码数据edata2、edata2b、edata2c和edata2d进行解码以生成第二数据data2、data2b、data2c和data2d所用的时间。在一个实施例中,例如,当解码器单元dec、decb、decc和decd的解码时间彼此不同时,延迟单元dly可以基于最慢的解码时间将控制信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs以及时钟信号rxbyteclkhs中的至少一者延迟。

139.在实施例中,如上所述,在基于mipi协议进行通信的收发器装置tscv中,可以省略(移除)连接在发送器txd和接收器rxd之间的时钟线。在这样的实施例中,时钟信息(或关于时钟信号的信息)可以被包括(内置)在供给到第一线dp1和第二线dn1的编码数据(例如,编码数据edata1、edata1b、edata1c和edata1d)中。因此,可以减小由于时钟线设置导致的物理/空间成本和功耗。

140.图8和图9是示出了包括在图7a和图7b的收发器装置中的发送器的操作的实施例

的图。

141.参照图7a、图7b、图8和图9,发送器txd可以通过根据预定协议在有效载荷payload之前和之后(或前面和后面)添加其他数据来通过第一线dp1和第二线dn1发送数据。

142.编码器单元enc可以接收包括原始有效载荷payload的第一数据data1。编码器单元enc可以对原始有效载荷payload进行编码以生成第一有效载荷epayload,并且在第一有效载荷epayload之前和之后(或前面和后面)添加数据来生成第一编码数据edata1。在一个实施例中,例如,如图8所示,第一编码数据edata1可以依次包括时钟训练图案clk-t、开始图案stp、第一有效载荷epayload和结束图案edp。

143.时钟训练图案clk-t可以包括时钟信息的频率信息。时钟训练图案clk-t可以是用于恢复接收器rxd中的时钟信号的数据。接收器rxd可以通过使用时钟信息生成具有特定频率和特定相位的时钟信号。

144.在一个实施例中,例如,如图9所示,时钟训练图案clk-t可以是其中一个1和一个0彼此交替地重复的图案(例如,01010101

…

)。由接收器rxd的时钟数据恢复电路生成的时钟信号的频率和相位可能由于外部因素(噪声和温度等)而不期望地改变。接收器rxd可以使用时钟训练图案clk-t校正时钟信号的频率和相位。

145.在实施例中,时钟训练图案clk-t可以重复地包括多个连续的0和多个连续的1(例如,00001111000001111

…

)。由时钟训练图案clk-t指示的频率信息和相位信息可以根据多个连续的0的数量或多个连续的1的数量而改变。

146.开始图案stp可以是通知第一有效载荷epayload的发送开始的图案。开始图案stp可以是处于编码状态的第一有效载荷epayload可以不包括(=使用禁止)的图案。在一个实施例中,例如,开始图案stp可以被配置为24b’(24位)011100_000000_111111_110001’。

147.第一有效载荷epayload可以包括时钟信息。在一个实施例中,例如,当在原始有效载荷payload中存在许多连续的0或许多连续的1时,因为信号的转变可能小,所以基于时钟训练图案的时钟信号的相位校正可能在第一数据接收器rx1中无法充分地执行,并且可能由于时钟训练图案而发生时钟信号的偏差。因此,编码器单元enc可以执行编码,使得与原始有效载荷payload相比,第一有效载荷epayload的转变次数(从0变为1或从1变为0)足够多。在实施例中,编码器单元enc可以对第一有效载荷epayload进行编码以周期性地具有特定规则的位。

148.结束图案edp可以是通知第一有效载荷epayload的发送结束的图案。结束图案edp可以是处于编码状态的第一有效载荷epayload可以不包括(=使用禁止)的图案。在一个实施例中,例如,结束图案edp可以被配置为24b’(24位)011100_111111_000000_110001’。

149.第一数据发送器tx1可以接收包括第一有效载荷epayload的第一编码数据edata1。第一数据发送器tx1可以通过根据预定协议在第一编码数据edata1之前和之后(或前面和后面)添加其他数据来发送其他数据。在一个实施例中,例如,当预定协议是mipi协议时,第一数据发送器tx1可以依次发送第一图案hs-zero、第二图案hs-sync、第一编码数据edata1、第三图案hs-trail和第四图案hs-exit。

150.如图9中所示,发送器txd(具体地,第一数据发送器tx1)可以在第一模式mode1中将具有第一电压范围vr1的信号发送到第一线dp1和第二线dn1。在实施例中,发送器txd可以在第二模式mode2中将具有小于第一电压范围vr1的第二电压范围vr2的信号发送到第一

线dp1和第二线dn1。

151.在第一模式mode1中,第一线dp1和第二线dn1可以在单端方法中使用或者基于单端信令而操作。即,在第一模式mode1中发送到第一线dp1和第二线dn1中的每一者的信号可以彼此相同或不同。

152.在第二模式mode2中,第一线dp1和第二线dn1可以在差分方法中使用或者基于差分信令而操作。即,在第二模式mode2中发送到第一线dp1和第二线dn1中的每一者的信号彼此不同。

153.发送器txd可以在第二模式mode2中发送时钟训练图案clk-t和第一有效载荷epayload。

154.在实施例中,发送器txd可以将预定义的图案(例如,图案lp-11、图案lp-01和图案lp-00)发送到第一线dp1和第二线dn1,以通知从第一模式mode1向第二模式mode2的切换。

155.在一个实施例中,例如,发送器txd可以在第一时间点t1c之前将施加到第一线dp1和第二线dn1的信号保持为逻辑高电平(lp-11图案)。

156.在包括第一时间点t1c的时段期间,发送器txd可以将第一线dp1的信号改变为逻辑低电平并且将第二线dn1的信号保持为逻辑高电平(即,图案lp-01)。接下来,在包括第二时间点t2c的时段期间,发送器txd可以将第一线dp1的信号保持为逻辑低电平并且将第二线dn1的信号改变为逻辑低电平(即,图案lp-00)。

157.之后,在第二模式mode2中,发送器txd可以依次发送第一图案hs-zero、第二图案hs-sync、第一编码数据edata1、第三图案hs-trail和第四图案hs-exit。在一个实施例中,例如,发送器txd可以在从第三时间点t3c到第四时间点t4c的时段期间发送第一图案hs-zero,在从第四时间点t4c到第五时间点t5c的时段期间发送第二图案hs-sync,并且在从第五时间点t5c到第六时间点t6c的时段期间发送时钟训练图案clk-t。

158.另外,发送器txd可以在从第六时间点t6c到第七时间点t7c的期间发送开始图案stp,在从第七时间点t7c到第八时间点t8c的时段期间发送第一有效载荷epayload,并且在从第八时间点t8c到第九时间点t9c的时段期间发送结束图案edp。

159.之后,发送器txd可以在从第九时间点t9c到第十时间点t10c的时段期间发送第三图案hs-trail,并且在第十时间点t10c之后发送第四图案hs-exit。

160.第一图案hs-zero可以是用于通知在从第一模式mode1进入第二模式mode2之后的等待时段的图案。第二图案hs-sync可以是通知第一编码数据edata1的发送开始的图案。

161.第三图案hs-trail可以是通知第一编码数据edata1的发送结束的图案。第三图案hs-trail可以是其中重复与第一编码数据edata1的最后数据相反的值的图案。

162.第四图案hs-exit可以是通知第二模式mode2结束并且第一模式mode1开始的图案。图案hs-exit可以不由特定位配置,而可以是其中电压升高以超出第二电压范围vr2的传统图案。

163.发送器txd可以在从第十时间点t10c到第十二时间点t12c的时段期间将施加到第一线dp1和第二线dn1的信号改变为逻辑高电平。在一个实施例中,例如,图案lp-11的输出可以从第十一时间点t11c开始进行。因此,发送器txd可以通知第二模式mode2结束并且第一模式mode1开始。

164.在实施例中,接收器rxd可以使用时钟训练图案clk-t和第一有效载荷epayload生

成图7a或图7b的时钟信号rxbyteclkhs(例如,高速发送字节时钟信号)。第一数据接收器rx1可以包括时钟数据恢复电路,并且可以使用时钟训练图案clk-t生成具有特定频率和相位的时钟信号。

165.在实施例中,第一数据接收器rx1可以使用第一有效载荷epayload连续地校正时钟信号的相位以防止时钟信号的偏差。第一数据接收器rx1可以使用生成的时钟信号对接收的信号进行采样。

166.因此,根据实施例,可以提供能够在没有时钟线的情况下使用mipi协议进行通信的收发器装置tscv。

167.图10是示出了包括在图7a和图7b的收发器装置中的接收器的操作的实施例的图。

168.参照图6、图7a、图7b和图10,第一数据接收器rx1可以将包括第一有效载荷epayload的第二编码数据edata2提供到解码器单元dec。

169.解码器单元dec可以对第二编码数据edata2(即,第一有效载荷epayload)进行解码以生成第二数据data2,并且将生成的第二数据data2提供到接收控制器rxc。

170.第二数据data2可以包括第二有效载荷payload和虚拟图案dummy。因为第二有效载荷payload与由发送控制器txc提供的第一数据data1的原始有效载荷payload相同,所以第二数据data2不包括单独的相位信息。

171.虚拟图案dummy可以提前由编码器单元enc编码以嵌入在第一有效载荷epayload中,或者可以由解码器单元dec添加。虚拟图案dummy可以是其中重复相同值的数据。

172.在一个实施例中,例如,当第二有效载荷payload的最后值是0时,虚拟图案dummy可以是其中重复1的数据,并且当第二有效载荷payload的最后值是1时,虚拟图案dummy可以是其中重复0的数据。因此,因为由图7a的接收控制器rxc接收的第二数据data2的格式(有效载荷payload和虚拟图案dummy)可以与由图2的接收控制器rxcr接收的第二数据data2的格式(有效载荷payload和附加信息c)相同,所以即使从收发器装置tscv移除了时钟线,mipi协议接口也可以不用改变其格式。

173.类似于参照图6描述的第二数据data2的情况,由接收器rxd(例如,第一数据接收器rx1)生成的信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs的格式可以与由参照图3描述的接收器rxdr(例如,第一数据接收器rx1r)生成的信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs的格式相同。因此,根据实施例,即使从收发器装置tscv移除了时钟线,mipi协议接口也可以不用改变其格式。

174.因为参照图6详细描述了第二数据data2的发送以及信号rxactivehs、rxvalidhs、rxsynchs和rxbyteclkhs的电平变化,所以将省略其任何重复的详细描述。

175.第二数据data2可以包括附加信息c以及由字节单元b1、b2、b3、b4、b5、...和bn构成的第二有效载荷payload。在本文中,附加信息c可以是与除了图案hs-trail之外的虚拟图案dummy对应的信息。在一个实施例中,例如,附加信息c可以是其中重复0或重复1的8位信息。在一个实施例中,例如,第一数据接收器rx1可以通过解串器将第二数据data2的第二有效载荷payload和虚拟图案dummy并行化(例如,并行化为8行),并且将并行化的第二数据data2发送到接收控制器rxc。

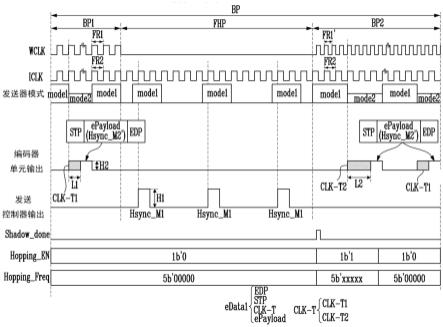

176.图11是示出了包括在图7a和图7b的收发器装置中的发送器的实施例的框图。图12是示出了发送器在垂直空白时段中的操作的图。

177.参照图11,发送器txd的实施例可以包括发送控制器txc、第一数据发送器tx1(在下文中称为数据发送器)、编码器单元enc和跳频控制器fhc。

178.在下文中,将参照在图1b中示出的激活时段actp和垂直空白时段bp来描述发送器txd的操作方法。

179.首先,将参照图7a至图11描述发送器txd在激活时段actp中的操作。发送控制器txc可以基于第一内部时钟信号wclk将包括原始有效载荷payload的第一传输数据txdata_1发送到编码器单元enc。在一个实施例中,例如,发送控制器txc可以与第一内部时钟信号wclk的栅极导通电平同步地将包括原始有效载荷payload的第一传输数据txdata_1发送到编码器单元enc。在这样的实施例中,第一传输数据txdata_1可以对应于图7a的第一数据data1。

180.发送控制器txc可以将第一传输请求信号txrequesths_1和第一指示信号txwordvalidhs_1提供到编码器单元enc。

181.第一传输请求信号txrequesths_1可以指高速传输请求。当激活第一传输请求信号txrequesths_1时,可以输出用于从第一模式mode1切换到第二模式mode2的数据,并且可以将包括原始有效载荷payload的有效数据从发送控制器txc提供到编码器单元enc。

182.第一指示信号txwordvalidhs_1可以是由mipi协议定义的信号,并且可以指示要传输到编码器单元enc的数据是有效数据。

183.编码器单元enc可以将第二传输数据txdata_2发送到数据发送器tx1。在一个实施例中,例如,编码器单元enc可以基于第一内部时钟信号wclk输出第二传输数据txdata_2。

184.编码器单元enc可以对第一传输数据txdata_1的至少一部分进行编码。在一个实施例中,例如,编码器单元enc可以将包括在第一传输数据txdata_1中的原始有效载荷payload编码为第一有效载荷epayload。

185.编码器单元enc可以根据预定协议执行数据编码。在实施例中,编码器单元enc可以执行数据编码,使得第一传输数据txdata_1的每n位(n是大于2的整数)发生数据切换(toggling)至少一次。在一个实施例中,例如,通过编码器单元enc的编码,数据可以每6位切换至少一次。

186.在实施例中,编码器单元enc可以通过在第一有效载荷epayload之前和之后(或前面和后面)添加数据来生成第二传输数据txdata_2。在这样的实施例中,第二传输数据txdata_2可以对应于图7a的第一编码数据edata1。

187.在实施例中,编码器单元enc可以响应于第一传输请求信号txrequesths_1生成时钟训练图案clk-t(或第三时钟训练图案),并且将时钟训练图案clk-t发送到数据发送器tx1。在一个实施例中,例如,第二传输数据txdata_2可以依次包括时钟训练图案clk-t(或第三时钟训练图案)、开始图案stp、第一有效载荷epayload和结束图案edp。

188.在实施例中,编码器单元enc可以将第二传输请求信号txrequesths_2和第二指示信号txwordvalidhs_2提供到数据发送器tx1。

189.第二传输请求信号txrequesths_2可以指高速传输请求。在实施例中,编码器单元enc可以响应于第一传输请求信号txrequesths_1激活第二传输请求信号txrequesths_2。当第二传输请求信号txrequesths_2被激活时,编码器单元enc可以将时钟训练图案clk-t(或第三时钟训练图案)发送到数据发送器tx1。

190.第二指示信号txwordvalidhs_2可以是由mipi协议定义的信号,并且可以指示要传输到数据发送器tx1的数据是有效数据。

191.在实施例中,编码器单元enc可以与从数据发送器tx1提供的第一内部时钟信号wclk的栅极导通电平同步地将包括第一有效载荷epayload的第二传输数据txdata_2发送到数据发送器tx1。

192.数据发送器tx1可以生成第一内部时钟信号wclk,并且将包括时钟训练图案clk-t(或第三时钟训练图案)和第一有效载荷epayload的第二传输数据txdata_2发送到第一线dp1和第二线dn1。第一内部时钟信号wclk可以被提供到发送控制器txc和编码器单元enc。

193.数据发送器tx1可以响应于第二传输请求信号txrequesths_2将用于从第一模式mode1切换到第二模式mode2的数据发送到接收器rxd。

194.数据发送器tx1可以将第二传输准备信号txreadyhs_2提供到编码器单元enc。第二传输准备信号txreadyhs_2可以指示高速传输准备。当第二传输准备信号txreadyhs_2被激活时,提供到数据发送器tx1的时钟训练图案clk-t(或第三时钟训练图案)可以被发送到接收器rxd。

195.之后,数据发送器tx1可以将从编码器单元enc提供的第一有效载荷epayload发送到接收器rxd。

196.接下来,将参照图7a至图12描述发送器txd在垂直空白时段bp中的操作。

197.在图1a中示出的显示装置1000的实施例可以是与基站通信的移动终端。当移动终端从连接的基站的服务空间移动到另一基站的服务空间时,在移动终端调谐到分配给其他基站的服务空间的呼叫信道的过程中,基站和移动终端之间使用的频带可能改变。在这种情况下,可能发生与在包括在移动终端中的发送器txd和接收器rxd之间使用的频率的干扰现象。

198.在实施例中,移动终端(或收发器装置tscv)可以使用跳频方法来防止这样的频率干扰现象。在这样的实施例中,跳频方法是指在根据预定功能在无线通信网络中改变在发送器txd和接收器rxd之间的数据通信中使用的频率(或数据传输速度)的同时执行通信的方法。

199.跳频控制器fhc可以确定在基站和移动终端(或收发器装置tscv)之间发生频率干扰现象的可能性。当确定出发生频率干扰现象时,跳频控制器fhc可以确定在垂直空白时段bp中是否包括跳频时段fhp。根据实施例,跳频控制器fhc可以将关于跳频时段fhp是否处于激活状态的第一寄存器值hopping_en提供到编码器单元enc。在一个实施例中,例如,第一寄存器值hopping_en可以由1位构成,并且可以包括指示跳频时段fhp从激活状态改变为非激活状态的第(1-1)寄存器值1’b1和指示跳频时段fhp保持为激活状态或非激活状态的第(1-2)寄存器值1’b0中的任何一者。在这样的实施例中,第(1-1)寄存器值1’b1可以是指示第一内部时钟信号wclk的频率改变的信号,并且第(1-2)寄存器值1’b0可以是指示第一内部时钟信号wclk的频率保持而不改变的信号。

200.数据发送器tx1可以在垂直空白部分bp中改变第一内部时钟信号wclk的频率设置值,以在与预设的参考数据传输速度(例如:67gbps)相比的预定范围(例如:

±

2.5%)内改变数据传输速度。当第一内部时钟信号wclk的频率设置值改变时,数据发送器tx1可以基于改变后的第一内部时钟信号wclk发送数据。

201.数据发送器tx1可以在改变第一内部时钟信号wclk的频率设置值的同时不将第一内部时钟信号wclk发送到发送控制器txc和编码器单元enc。在一个实施例中,例如,第一内部时钟信号wclk可以在跳频时段fhp(参照图12)中保持为预定电平(例如,低电平,参照图12)。在这样的实施例中,数据发送器tx1可以不在跳频时段fhp中产生第一内部时钟wclk。

202.根据实施例,数据发送器tx1可以生成第二内部时钟信号iclk。数据发送器tx1可以将第二内部时钟信号iclk提供到发送控制器txc。根据可选的实施例,发送控制器txc还可以包括自身生成第二内部时钟信号iclk的第二内部时钟信号生成器iclk_g。

203.在这样的实施例中,可以不将第二内部时钟信号iclk提供到编码器单元enc。因此,数据发送器tx1可以在跳频时段fhp中基于第二内部时钟信号iclk而操作,并且可以在除了跳频时段fhp之外的时段bp1和bp2中基于第一内部时钟信号wclk而操作。在这样的实施例中,仅基于第一内部时钟信号wclk而操作的编码器单元enc在跳频时段fhp中可以不操作或可以保持先前的操作。

204.在实施例中,如图1b中所示,水平同步信号hsync可以包括同样在垂直空白时段bp中具有预定间隔(例如,一个水平周期1h)的脉冲。因此,在垂直空白时段bp中,在除了跳频时段fhp之外的时段bp1和bp2中,发送控制器txc可以在图9的第二模式mode2中生成水平同步信号hsync_m2并将水平同步信号hsync_m2发送到编码器单元enc,并且编码器单元enc可以对水平同步信号hsync_m2进行编码以生成水平同步数据hsync_m2’并通过在水平同步数据hsync_m2’中添加预定的时钟训练图案clk-t生成第一编码数据edata1。在这样的实施例中,在跳频时段fhp中,发送控制器txc可以在第一模式mode1中生成水平同步信号hsync_m1。

205.在实施例中,如图12中所示,在垂直空白时段bp(在跳频之前的时段bp1)期间,发送控制器txc可以基于第一内部时钟信号wclk在第二模式mode2中生成水平同步信号hsync_m2,并且将水平同步信号hsync_m2提供到编码器单元enc。之后,编码器单元enc可以对水平同步信号hsync_m2进行编码以生成第一有效载荷epayload(或水平同步数据hsync_m2’),并且通过在第一有效载荷epayload(或水平同步数据hsync_m2’)之前和之后(或前面和后面)添加预定数据来生成第一编码数据edata1。在一个实施例中,例如,第一编码数据edata1可以依次包括时钟训练图案clk-t、开始图案stp、第一有效载荷epayload(或水平同步数据hsync_m2’)和结束图案edp。在这样的实施例中,编码器单元enc可以在第一内部时钟信号wclk的上升沿输出第一编码数据edata1。

206.在垂直空白时段bp期间,在跳频时段fhp中,发送控制器txc可以基于第二内部时钟信号iclk在图9的第一模式mode1中生成水平同步信号hsync_m1,并且将水平同步信号hsync_m1发送到数据发送器tx1。在一个实施例中,例如,发送控制器txc可以在第二内部时钟信号iclk的上升沿输出水平同步信号hsync_m2。在这样的实施例中,第二内部时钟信号iclk的时段可以保持恒定的第二时段fr2而与跳频无关。

207.因为编码器单元enc在跳频时段fhp中不操作,所以水平同步信号hsync_m1可以直接从发送控制器txc发送到数据发送器tx1。在这样的实施例中,在图9的第一模式mode1中生成的水平同步信号hsync_m1的幅度h1可以大于在图9的第二模式mode2中生成的水平同步信号hsync_m2(或水平同步数据hsync_m2')的幅度h2。

208.在垂直空白时段bp期间,同样在跳频之后的时段bp2中,发送控制器txc可以基于

第一内部时钟信号wclk在图8的第二模式mode2中生成水平同步信号hsync_m2。然而,在跳频之后的时段bp2中,编码器单元enc可以通过包括第二时钟训练图案clk-t2而不是第一时钟训练图案clk-t1来生成第一编码数据edata1。在这样的实施例中,第二时钟训练图案clk-t2的长度l2可以比第一时钟训练图案clk-t1的长度l1长。在跳频时段fhp之后,第一内部时钟信号wclk的频率可以改变。在一个实施例中,例如,第一内部时钟信号wclk的时段可以具有在跳频时段fhp之前的第一时段fr1并且可以具有在跳频时段fhp之后的第一’时段fr1’。第一’时段fr1’可以比第一时段fr1短。为了便于示出,包括开始图案stp、第一有效载荷epayload(或水平同步数据hsync_m2’)和结束图案edp的图案的长度在图12中被示出为在跳频时段fhp之前和之后(或前面和后面)基本上彼此相同,但是因为第一内部时钟信号wclk每一个时钟传输16位,所以在跳频时段fhp之后包括开始图案stp、第一有效载荷epayload(或水平同步数据hsync_m2’)和结束图案edp的图案的长度可以比在跳频时段fhp之前包括开始图案stp、第一有效载荷epayload(或水平同步数据hsync_m2’)和结束图案edp的图案的长度短。

209.因为编码器单元enc基于改变后的第一内部时钟信号wclk而操作,所以接收器rxd(或时钟数据恢复电路)可以使用更多(或更长)时间来追踪改变后的频率信息和相位信息。在一个实施例中,例如,用于接收器rxd(或时钟数据恢复电路)追踪第二时钟训练图案clk_t2的第二频率信息和/或第二相位信息的时间(即,锁定时间)可以比用于追踪第一时钟训练图案clk_t1的第一频率信息和第一相位信息的时间(即,锁定时间)长。

210.根据实施例,发送控制器txc可以基于第一内部时钟信号wclk向编码器单元enc提供作为关于跳频时段fhp是否处于激活状态的信息的结束标志信号shadow_done。在一个实施例中,例如,当结束标志信号shadow_done具有逻辑高电平时,可以确定出跳频时段fhp从激活状态改变为非激活状态。

211.在实施例中,如上所述,跳频控制器fhc可以将关于跳频时段fhp是否处于激活状态的第一寄存器值hopping_en提供到编码器单元enc。在一个实施例中,例如,第一寄存器值hopping_en可以由1位构成,并且可以包括指示跳频时段fhp从激活状态改变为非激活状态的第(1-1)寄存器值1’b1和指示跳频时段fhp保持为激活状态或非激活状态的第(1-2)寄存器值1’b0中的任何一者。在实施例中,第(1-1)寄存器值1’b1可以是指示第一内部时钟信号wclk的频率改变的信号,并且第(1-2)寄存器值1’b0可以是指示第一内部时钟信号wclk的频率保持而不改变的信号。编码器单元enc可以从发送控制器txc接收结束标志信号shadow_done(例如,逻辑高电平信号),并且当从跳频控制器fhc接收到第(1-1)寄存器值(例如,1’b1)时,在图9的第二模式mode2中,编码器单元enc可以通过将第二时钟训练图案clk-t2添加到第一有效载荷epayload(或水平同步数据hsync_m2’)来生成第一编码数据edata1。在这样的实施例中,第二时钟训练图案clk-t2的长度可以比第一时钟训练图案clk-t1的长度长了预设长度。在一个实施例中,例如,当收发器装置tscv的数据传输速度在跳频期间在

±

2.5%内改变时,预设长度可以设置为对应于中间值(即,

±

1.25%)。

212.根据实施例,可以通过在第一时钟训练图案clk-t1中进一步包括其中一个1和一个0彼此交替重复的图案(即,增加0和1的切换次数)来增加第二时钟训练图案clk-t2的长度。然而,本公开不限于此,并且在一个可选的实施例中,例如,可以通过在第一时钟训练图案clk-t1中进一步包括其中多个连续的1和多个连续的0彼此交替重复的图案来增加第二

时钟训练图案clk-t2的长度。

213.在图2和图3中示出的发送器txdr包括与数据发送器tx1r、tx2r、tx3r和tx4r分开的时钟发送器tcr。因此,即使发送器txdr和接收器rxdr之间的数据传输速度随着跳频发生而改变,但是因为发送器txdr基于改变后的时钟信号而操作,所以可以有效地执行水平同步信号hsync和hsync’的同步。

214.然而,在图7a和图7b中示出的使用时钟嵌入方法的发送器txd的实施例中,当发送器txdr和接收器rxdr之间的数据传输速度随着跳频发生而改变时,接收器rxd(或时钟数据恢复电路)可能使用更多时间来追踪改变后的频率信息和相位信息。根据本公开的实施例,通过在跳频时段fhp结束之后在第一有效载荷epayload(或水平同步数据hsync_m2’)中添加比第一时钟训练图案clk-t1的长度长的第二时钟训练图案clk-t2,即使垂直空白时段bp包括跳频时段fhp,收发器装置tscv仍可以使从发送器txd提供的水平同步信号和由接收器rxd恢复的水平同步信号同步。在这样的实施例中,即使与在图2和图3中示出的情况不同,收发器装置tscv不包括在发送器txdr中与数据发送器tx1r、tx2r、tx3r和tx4r分开的时钟发送器tcr,仍可以有效地执行跳频方法。

215.在下文中,将描述可选的实施例。在这样的实施例中,将省略或简化与上面描述的实施例的配置相同或类似的配置的任何重复的详细描述,并且将主要描述不同之处。

216.图13是示出了包括在图7a和图7b的收发器装置中的发送器的另一示例的框图。图14是示出了其中第二时钟训练图案的长度响应于收发器装置的数据传输速度变化范围而改变的实施例的曲线图。图15是示出了响应于收发器装置的数据传输速度变化范围来改变第二时钟训练图案的长度的发送器的操作的图。

217.在图13中示出的发送器txd_1的跳频控制器fhc与在图11中示出的仅接收关于跳频时段fhp是否处于激活状态的第一寄存器值hopping_en的收发器装置tscv的跳频控制器fhc的不同之处在于,在图13中示出的发送器txd_1的跳频控制器fhc还提供与收发器装置tscv的数据传输速度的变化范围对应的多个第二寄存器值hopping_freq。因为收发器装置tscv在激活时段actp中的操作与在图11中示出的实施例的操作基本上相同,所以将省略其任何重复的详细描述,并且主要描述收发器装置tscv在垂直空白时段bp中的操作。

218.参照图7a至图13,发送器txd_1的实施例可以包括发送控制器txc、数据发送器tx1、编码器单元enc和跳频控制器fhc。

219.在实施例中,如上面参照图12描述的,在垂直空白时段bp(跳频之前的时段bp1)期间,发送控制器txc可以基于第一内部时钟信号wclk在图8的第二模式mode2中生成水平同步信号hsync_m2,并且将水平同步信号hsync_m2提供到编码器单元enc。之后,编码器单元enc可以对水平同步信号hsync_m2进行编码以生成第一有效载荷epayload(或水平同步数据hsync_m2’),并且通过在第一有效载荷epayload(或水平同步数据hsync_m2’)之前和之后(或前面和后面)添加预定数据来生成第一编码数据edata1。

220.在垂直空白时段bp期间,在跳频时段fhp中,发送控制器txc可以基于第二内部时钟信号iclk在图9的第一模式mode1中生成水平同步信号hsync_m1,并且将水平同步信号hsync_m1发送到数据发送器tx1。在这样的实施例中,因为编码器单元enc在跳频时段fhp中不操作,所以水平同步信号hsync_m1可以直接从发送控制器txc发送到数据发送器tx1。在这样的实施例中,在图9的第一模式mode1中生成的水平同步信号hsync_m1的幅度h1可以大

于在图9的第二模式mode2中生成的水平同步信号hsync_m2(或水平同步数据hsync_m2’)的幅度h2。

221.在垂直空白时段bp期间,同样在跳频之后的时段bp2中,发送控制器txc可以基于第一内部时钟信号wclk在图8的第二模式mode2中生成第一有效载荷epayload(或水平同步数据hsync_m2’),并且通过在第一有效载荷epayload(或水平同步数据hsync_m2’)之前和之后(或前面和后面)添加预定数据(例如,时钟训练图案clk-t、开始图案stp和结束图案edp)来生成第一编码数据edata1。然而,在跳频之后的时段bp2中,编码器单元enc可以通过添加第二时钟训练图案clk-t2而不是第一时钟训练图案clk-t1来生成第一编码数据edata1。在这样的实施例中,第二时钟训练图案clk-t2的长度l2可以比第一时钟训练图案clk-t1的长度l1长。

222.第一内部时钟信号wclk的频率可以在跳频时段fhp之后改变。在一个实施例中,例如,第一内部时钟信号wclk的时段可以在跳频时段fhp之前具有第一时段fr1,并且可以在跳频时段fhp之后具有第一’时段fr1’。第一’时段fr1’可以比第一时段fr1短。为了便于示出和描述,包括开始图案stp、第一有效载荷epayload(或水平同步数据hsync_m2’)和结束图案edp的图案的长度在图12中被示出为在跳频时段fhp之前和之后(或前面和后面)相同,但是因为第一内部时钟信号wclk每一个时钟传输16位,所以在跳频时段fhp之后包括开始图案stp、第一有效载荷epayload(或水平同步数据hsync_m2’)和结束图案edp的图案的长度可以比在跳频时段fhp之前包括开始图案stp、第一有效载荷epayload(或水平同步数据hsync_m2’)和结束图案edp的图案的长度短。

223.因为编码器单元enc基于改变后的第一内部时钟信号wclk而操作,所以接收器rxd(或时钟数据恢复电路)可能使用更多时间用于追踪改变后的频率信息和相位信息。在一个实施例中,例如,用于追踪第二时钟训练图案clk_t2的第二频率信息和/或第二相位信息的时间(即,锁定时间)可以比用于追踪第一时钟训练图案clk_t1的第一频率信息和第一相位信息的时间(即,锁定时间)长。

224.此时,接收器rxd(或时钟数据恢复电路)用于追踪第二时钟训练图案clk_t2的第二频率信息和/或第二相位信息的时间(即,锁定时间)可以响应于数据传输速度变化范围而改变。在一个实施例中,例如,随着数据传输速度变化范围增加,用于追踪第二时钟训练图案clk_t2的第二频率信息和/或第二相位信息的时间(即,锁定时间)会更长。

225.根据实施例,发送控制器txc可以基于第一内部时钟信号wclk将作为关于跳频时段fhp是否处于激活状态的信息的结束标志信号shadow_done提供到编码器单元enc。在一个实施例中,例如,当结束标志信号shadow_done具有逻辑高电平时,可以确定出跳频时段fhp从激活状态改变为非激活状态。

226.在这样的实施例中,跳频控制器fhc可以将关于跳频时段fhp是否处于激活状态的第一寄存器值hopping_en提供到编码器单元enc。在一个实施例中,例如,第一寄存器值hopping_en可以由1位构成,并且可以包括指示跳频时段fhp从激活状态改变为非激活状态的第(1-1)寄存器值1’b1和指示跳频时段fhp保持为激活状态或非激活状态的第(1-2)寄存器值1’b0中的任何一者。在这样的实施例中,第(1-1)寄存器值1’b1可以是指示第一内部时钟信号wclk的频率改变的信号,并且第(1-2)寄存器值1’b0可以是指示第一内部时钟信号wclk的频率保持而不改变的信号。

227.在这样的实施例中,当确定出发生频率干扰现象时,跳频控制器fhc可以附加地将包括关于收发器装置tscv的数据传输速度的变化范围的信息的第二寄存器值hopping_freq提供到编码器单元enc。

228.根据实施例,通过以预设间隔划分数据发送器tx1的数据传输速度的变化范围,第二寄存器值hopping_freq可以由与每个预设间隔对应的寄存器值构成。

229.在一个实施例中,例如,第二寄存器值hopping_freq可以由5位构成,并且可以包括通过以

±

0.1%的间隔划分数据传输速度的变化范围(例如:

±

2.5%)所产生的25个寄存器值。然而,包括在第二寄存器值hopping_freq中的寄存器值的数量不限于此。在一个实施例中,例如,根据接收器rxd(或时钟数据恢复电路)的锁定时间分辨率设计,当以更大的间隔来划分数据传输速度的变化范围(或跳频程度)时,包括在第二寄存器值hopping_freq中的寄存器值的数量可以减少,并且当数据传输速度的变化范围以较小的间隔划分时,包括在第二寄存器值hopping_freq中的寄存器值的数量可以增加。

230.下面的表1示出了响应于跳频程度的数据发送器tx1的数据传输速度、第二时钟训练图案clk-t2的长度、第二时钟训练图案clk-t2的实际长度、第一内部时钟信号wclk的频率变化程度的实施例。此时,单位间隔(ui)是指1位。表1的“1ui”被定义为数据传输速度的倒数。

231.在一个实施例中,例如,跳频不存在(即,数据传输速度变化范围为0%),数据发送器tx1的传输速度可以为6gbps,并且第二时钟训练图案clk-t2可以具有1800ui。因为1ui此时为0.167纳秒(ns),所以第二时钟训练图案clk-t2的实际长度(或时间)可以为1800

×

0.167=300ns。另外,因为第一内部时钟信号wclk每一个时钟传输16位,所以第一内部时钟信号wclk的频率可以为6g/16=375兆赫(mhz)。

232.在这样的实施例中,当数据传输速度变化范围增加0.8%时,数据发送器tx1的传输速度可以为6.05gbps,并且第二时钟训练图案clk-t2可以具有2760ui。因为1ui此时为0.165ns,所以第二时钟训练图案clk-t2的实际长度(或时间)可以为2760

×

0.165=456ns。另外,因为第一内部时钟信号wclk每一个时钟传输16位,所以第一内部时钟信号wclk的频率可以为6.05g/16=378mhz。

233.在这样的实施例中,当数据传输速度变化范围增加1.7%时,数据发送器tx1的传输速度可以为6.1gbps,并且第二时钟训练图案clk-t2可以具有3840ui。因为1ui此时为0.164ns,所以第二时钟训练图案clk-t2的实际长度(或时间)可以为3840

×

0.164=630ns。在这样的实施例中,因为第一内部时钟信号wclk每一个时钟传输16位,所以第一内部时钟信号wclk的频率可以为6.1g/16=381mhz。

234.在这样的实施例中,当数据传输速度变化范围增加2.5%时,数据发送器tx1的传输速度可以为6.15gbps,并且第二时钟训练图案clk-t2可以具有4800ui。因为1ui此时为0.163ns,所以第二时钟训练图案clk-t2的实际长度(或时间)可以为4800

×

0.163=780ns。在这样的实施例中,因为第一内部时钟信号wclk每一个时钟传输16位,所以第一内部时钟信号wclk的频率可以为6.15g/16=384mhz。

235.在这样的实施例中,随着数据传输速度变化范围以0.8%、1.7%和2.5%的顺序增加,第二时钟训练图案clk-t2的长度(或时间)可以增加至456ns、630ns和780ns,并且第一内部时钟信号wclk的频率也可以增加至378mhz、381mhz和384mhz。

236.在这样的实施例中,当数据传输速度变化范围减小0.8%时,数据发送器tx1的传输速度可以为5.95gbps,并且第二时钟训练图案clk-t2可以具有2760ui。因为1ui此时为0.168ns,所以第二时钟训练图案clk-t2的实际长度(或时间)可以为2760

×

0.168=464ns。在这样的实施例中,因为第一内部时钟信号wclk每一个时钟传输16位,所以第一内部时钟信号wclk的频率可以为5.95g/16=372mhz。

237.在这样的实施例中,当数据传输速度变化范围减小1.7%时,数据发送器tx1的传输速度可以为5.9gbps,并且第二时钟训练图案clk-t2可以具有3840ui。因为1ui此时为0.169ns,所以第二时钟训练图案clk-t2的实际长度(或时间)可以为3840

×

0.169=651ns。另外,因为第一内部时钟信号wclk每一个时钟传输16位,所以第一内部时钟信号wclk的频率可以为5.9g/16=369mhz。

238.在这样的实施例中,当数据传输速度变化范围减小2.5%时,数据发送器tx1的传输速度可以为5.85gbps,并且第二时钟训练图案clk-t2可以具有4800ui。因为1ui此时为0.171ns,所以第二时钟训练图案clk-t2的实际长度(或时间)可以为4800

×

0.171=821ns。在这样的实施例中,因为第一内部时钟信号wclk每一个时钟传输16位,所以第一内部时钟信号wclk的频率可以为5.85g/16=366mhz。

239.在这样的实施例中,随着数据传输速度变化范围以0.8%、1.7%和2.5%的顺序减小,第二时钟训练图案clk-t2的长度(或时间)可以减小至464ns、651ns和821ns,并且第一内部时钟信号wclk的频率可以减小至372mhz、369mhz和366mhz。

240.[表1]

[0241][0242][0243]

参照图14,随着数据传输速度变化范围增加至

±

0.8%、

±

1.7%和

±

2.5%时,第二时钟训练图案clk-t2的长度可以增大。在实施例中,当跳频不存在时,第二时钟训练图案clk-t2的长度可以预设为1800ui,当数据传输速度由于跳频而改变达到

±

2.5%时,第二时钟训练图案clk-t2的长度可以预设为4800ui,并且基于上面描述的第二时钟训练图案的长度和数据传输速度变化范围,第二时钟训练图案clk-t2的长度可以成比例地应用于数据传输速度的其他变化范围。

[0244]

参照图13至图15,当编码器单元enc从发送控制器txc接收到结束标志信号shadow_done并且从跳频控制器fhc接收到第(1-1)寄存器值hopping_en时,编码器单元enc可以对从发送控制器txc接收到的水平同步信号hsync_m2进行编码以生成第一有效载荷epayload(或水平同步数据hsync_m2’),并且可以通过在第一有效载荷epayload(或水平同步数据hsync_m2’)之前和之后(或前面和后面)添加预定数据来生成第一编码数据edata1。

在实施例中,编码器单元enc可以通过在第一有效载荷epayload(或水平同步数据hsync_m2’)中包括第二时钟训练图案clk-t2而不是第一时钟训练图案clk-t1来生成图8的第一编码数据edata1。

[0245]

在实施例中,编码器单元enc可以附加地从跳频控制器fhc接收第二寄存器值hopping_freq。根据实施例,第二寄存器值hopping_freq可以包括与第一数据传输速度变化范围(例如:

±

0.8%)对应的第(2-1)寄存器值、与第二数据传输速度变化范围(例如:

±

1.7%)对应的第(2-2)寄存器值和与第三数据传输速度变化范围(例如:

±

2.5%)对应的第(2-3)寄存器值。跳频控制器fhc可以基于数据传输速度的变化范围将第(2-1)寄存器值、第(2-2)寄存器值和第(2-3)寄存器值中的任何一者提供到编码器单元enc。然而,包括在第二寄存器值hopping_freq中的寄存器值的数量是示例性的,并且可以改变。这里,5b’00000可以是当数据传输速度不改变时的寄存器值,并且5b’xxxxx可以是与第(2-1)寄存器值、第(2-2)寄存器值和第(2-3)寄存器值中的任何一者对应的寄存器值。

[0246]

编码器单元enc可以响应于接收到的第二寄存器值hopping_freq确定第二时钟训练图案clk-t2的长度。在一个实施例中,例如,如图15中所示,当编码器单元enc接收到第(2-1)寄存器值时,编码器单元enc可以通过在第二模式mode2中在水平同步数据hsync_m2’中包括第二十一时钟训练图案clk-t21来生成第一编码数据edata1,当编码器单元enc接收到第(2-2)寄存器值时,编码器单元enc可以通过在第二模式mode2中在水平同步数据hsync_m2’中包括第二十二时钟训练图案clk-t22来生成第一编码数据edata1,并且当编码器单元enc接收到第(2-3)寄存器值时,编码器单元enc可以通过在第二模式mode2中在水平同步数据hsync_m2’中包括第二十三时钟训练图案clk-t23来生成第一编码数据edata1。在这样的实施例中,长度可以以第二十一时钟训练图案clk-t21、第二十二时钟训练图案clk-t22和第二十三时钟训练图案clk-t23的顺序更长。为了便于示出和描述,在图15中仅示出了将第二时钟训练图案clk-t2添加到水平同步数据hsync_m2’,但是如图12中所示,可以在水平同步数据hsync_m2’之前和之后(或前面和后面)包括开始图案stp和结束图案edp。

[0247]

第二时钟训练图案clk-t2的长度可以比第一时钟训练图案clk-t1的长度长。根据实施例,可以通过在第一时钟训练图案clk-t1中进一步包括其中一个1和一个0重复的图案(即,增加0和1的切换次数)来增加第二时钟训练图案clk-t2的长度。在一个实施例中,例如,第(2-1)寄存器值、第(2-2)寄存器值和第(2-3)寄存器值可以分别对应于2760ui、3840ui和4800ui。因此,与第一数据传输速度变化范围(例如:

±

0.8%)相比,在第二数据传输速度变化范围(例如:

±

1.7%)中,第二时钟训练图案clk-t2(即,第二十二时钟训练图案clk-t22)的长度增加了1080ui(或将0和1的切换次数增加540),并且与第二数据传输速度变化范围(例如:

±

1.7%)相比,在第三数据传输速度变化范围(例如:

±

2.5%)中,第二时钟训练图案clk-t2(即,第二十三时钟训练图案clk-t23)的长度增加了960ui(或将0和1的切换次数增加480)。

[0248]

因此,因为第二时钟训练图案clk-t2的长度可以响应于跳频变化程度更精确地变化,所以可以优化用于追踪接收器rxd的第二时钟训练图案clk_t2的第二频率信息和/或第二相位信息的时间(即,锁定时间)。

[0249]

本发明不应被解释为限于在此阐述的实施例。相反,提供这些实施例以使本公开将是彻底的和完整的,并且将本发明的构思充分传达给本领域技术人员。

[0250]

尽管已经参考本发明的实施例具体示出并描述了本发明,但本领域普通技术人员将理解,在不脱离由所附权利要求限定的本发明的精神或范围的情况下,可以在其中进行形式和细节上的各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1