像素电路的制作方法

1.本发明涉及一种像素电路,且特别涉及一种自发光式像素电路。

背景技术:

2.近年来,由于具有低耗电量、较薄显示面板厚度变薄、颜色鲜艳、对比更明显等优点,除此之外,还克服了动态模糊的问题,自发光显示技术已成为显示装置的主流。

3.随着半导体工艺的进步,不同的发光元件应用于画面显示上,而显示面板上则对应的配置不同的驱动电路。以同时具有顺向及逆向驱动特性的发光元件而言,则需要有对应的设计的驱动电路,以组合成一个自发光像素电路。

技术实现要素:

4.本发明提供一种像素电路,其应用具有顺向及逆向驱动的发光元件,并且提供了新颖的驱动电路。

5.本发明的像素电路,包括一发光元件、一第一区域发光开关、一第二区域发光开关、一共同发光开关、以及一驱动区块。发光元件具有耦接共用端的一端,且具有第一发光部分及第二发光部分,其中驱动第一发光部分的第一驱动电流的方向相反于驱动第二发光部分的第二驱动电流的方向。第一区域发光开关具有耦接第一电源端的第一端、接收第一画面发光信号的控制端、以及第二端。第二区域发光开关具有耦接第二电源端的第一端、接收第二画面发光信号的控制端、以及第二端。共同发光开关具有第一端、接收共同发光信号的控制端、以及耦接发光元件的另一端的第二端。驱动区块接收数据信号、第一画面栅极信号、以及第二画面栅极信号,并且耦接第一区域发光开关的第二端、第二区域发光开关的第二端及共同发光开关的第一端。驱动区块基于第一画面栅极信号及第二画面栅极信号形成第一电流路径及第二电流路径的其中之一,其中第一电流路径形成于第一区域发光开关的第二端与共同发光开关的第一端之间且递送第一驱动电流,并且第二电流路径形成于第二区域发光开关的第二端与共同发光开关的第一端之间且递送第二驱动电流,并且数据信号设定第一驱动电流及第二驱动电流的电流幅度。

6.基于上述,本发明实施例的像素电路,通过全新设计的驱动区块,可提供具有双向驱动能力的发光元件所需要的不同流向的第一驱动电流以及第二驱动电流i2,以使像素电路可以应用新型发光元件而顺利运行。

7.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合说明书附图作详细说明如下。

附图说明

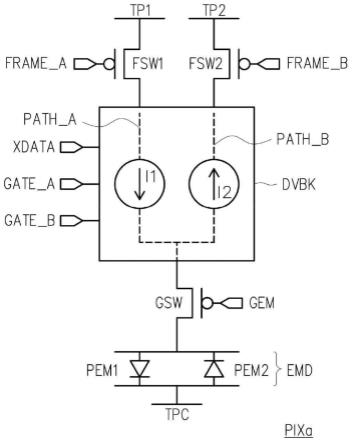

8.图1为依据本发明一实施例的像素电路的系统示意图。

9.图2为依据本发明一实施例的像素电路的电路示意图。

10.图3为依据本发明一实施例的像素电路的操作时序示意图。

11.图4a为依据本发明一实施例的像素电路于第一重置期间及第二重置期间的操作示意图。

12.图4b为依据本发明一实施例的像素电路于第一设定期间及第二设定期间的操作示意图。

13.图4c为依据本发明一实施例的像素电路于第一发光期间的操作示意图。

14.图4d为依据本发明一实施例的像素电路于第二设定期间的操作示意图。

15.图4e为依据本发明一实施例的像素电路于第二发光期间的操作示意图。

16.图5为依据本发明另一实施例的像素电路的系统示意图。

17.附图标记说明:

18.c1:第一电容

19.c2:第二电容

20.dvbk:驱动区块

21.emd:发光元件

22.frame_1:第一画面期间

23.frame_2:第二画面期间

24.frame_a:第一画面发光信号

25.frame_b:第二画面发光信号

26.fsw1:第一区域发光开关

27.fsw2:第二区域发光开关

28.gate_a:第一画面栅极信号

29.gate_b:第二画面栅极信号

30.gem、gemx:共同发光信号

31.gsw:共同发光开关

32.i1:第一驱动电流

33.i2:第二驱动电流

34.ir_dc:第一直流电平

35.path_a:第一电流路径

36.path_b:第二电流路径

37.pem1:第一发光部分

38.pem2:第二发光部分

39.pixa、pixb:像素电路

40.pm1:第一发光期间

41.pm2:第二发光期间

42.pr1:第一重置期间

43.pr2:第二重置期间

44.ps1:第一设定期间

45.ps2:第二设定期间

46.pwbk:脉冲宽度控制区块

47.res_dc:第二直流电平

48.reset:重置信号

49.set:设定信号

50.sw1:第一开关

51.sw10:第十开关

52.sw2:第二开关

53.sw3:第三开关

54.sw4:第四开关

55.sw5:第五开关

56.sw6:第六开关

57.sw7:第七开关

58.sw8:第八开关

59.sw9:第九开关

60.t_dc:时间参考直流电平

61.tdata:时间数据信号

62.tp1:第一电源端

63.tp2:第二电源端

64.tpc:共用端

65.tvr:时间电压斜率参考信号

66.xdata:数据信号

具体实施方式

67.除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

68.应当理解,尽管术语“第一”、“第二”、“第三”等在本文中可以用于描述各种元件、部件、区域、层及/或部分,但是这些元件、部件、区域、及/或部分不应受这些术语的限制。这些术语仅用于将一个元件、部件、区域、层或部分与另一个元件、部件、区域、层或部分区分开。因此,下面讨论的“第一元件”、“部件”、“区域”、“层”或“部分”可以被称为第二元件、部件、区域、层或部分而不脱离本文的教导。

69.这里使用的术语仅仅是为了描述特定实施例的目的,而不是限制性的。如本文所使用的,除非内容清楚地指示,否则单数形式“一”、“一个”和“该”旨在包括复数形式,包括“至少一个”。“或”表示“及/或”。如本文所使用的,术语“及/或”包括一个或多个相关所列项目的任何和所有组合。还应当理解,当在本说明书中使用时,术语“包括”及/或“包括”指定所述特征、区域、整体、步骤、操作、元件的存在及/或部件,但不排除一个或多个其它特征、区域整体、步骤、操作、元件、部件及/或其组合的存在或添加。

70.图1为依据本发明一实施例的像素电路的系统示意图。请参照图1,在本实施例中,像素电路pixa包括发光元件emd、第一区域发光开关fsw1、第二区域发光开关fsw2、共同发光开关gsw、以及驱动区块dvbk。

71.发光元件emd具有耦接共用端tpc的一端,且具有第一发光部分pem1及第二发光部分pem2,其中发光元件emd例如是纳米柱型(nanorod)发光元件,但本发明实施例不以此为限。第一区域发光开关fsw1具有耦接第一电源端tp1的第一端、接收第一画面发光信号frame_a的控制端、以及第二端。第二区域发光开关fsw2具有耦接第二电源端tp2的第一端、接收第二画面发光信号frame_b的控制端、以及第二端。

72.共同发光开关gsw具有第一端、接收共同发光信号gem的控制端、以及耦接发光元件emd的另一端的第二端。驱动区块dvbk接收数据信号xdata、第一画面栅极信号gate_a、以及第二画面栅极信号gate_b,并且耦接于第一区域发光开关fsw1的第二端、第二区域发光开关fsw2的第二端及共同发光开关gsw的第一端。驱动区块dvbk基于第一画面栅极信号gate_a及第二画面栅极信号gate_b形成第一电流路径path_a及第二电流路径path_b的其中之一,第一电流路径path_a形成于第一区域发光开关fsw1的第二端与共同发光开关gsw的第一端之间且递送第一驱动电流i1,并且第二电流路径path_b形成于第二区域发光开关fsw2的第二端与共同发光开关gsw的第一端之间且递送第二驱动电流i2。

73.在本实施例中,第一驱动电流i1用以驱动第一发光部分pem1,且第二驱动电流i2用以驱动第二发光部分pem2,其中第一驱动电流i1的方向相反于的第二驱动电流i2的方向,也就是说,第一发光部分pem1可视为顺向驱动,第二发光部分pem2可视为逆向驱动。并且,数据信号xdata设定第一驱动电流i1及第二驱动电流i2的电流幅度,以决定第一发光部分pem1及第二发光部分pem2的发光亮度。因此,通过全新设计的驱动区块,可提供具有顺向驱动及逆向驱动的发光元件所需要的顺向电流(例如第一驱动电流i1)以及逆向电流(例如第二驱动电流i2),以使像素电路可以顺利运行。

74.在本实施例中,第一区域发光开关fsw1、第二区域发光开关fsw2及共同发光开关gsw皆以p型晶体管为例,但本发明实施例不以此为限。

75.在本实施例中,第一电源端tp1的电压是不同于第二电源端tp2的电压。举例来说,第一电源端tp1的电压可以大于第二电源端tp2的电压,并且共用端tpc的电压介于第一电源端tp1的电压与第二电源端tp2的电压之间。因此,第一电流路径path_a递送的第一驱动电流i1是顺向电流,并且二电流路径path_b递送的第二驱动电流i2是逆向电流。

76.图2为依据本发明一实施例的像素电路的电路示意图。请参照图1及图2,其中相同或相似元件使用相同或相似标号。在本实施例中,驱动区块dvbk包括第一开关sw1、第二开关sw2、第三开关sw3、第四开关sw4、第五开关sw5、第六开关sw6、第七开关sw7、第八开关sw8、第九开关sw9、第十开关sw10、第一电容c1、以及第二电容c2。

77.第一开关sw1具有耦接第一电源端tp1的第一端、接收第一画面发光信号frame_a的控制端及第二端。第二开关sw2具有耦接第一开关sw1的第二端的第一端、接收设定信号set的控制端及接收第一直流电平ir_dc的第二端。第三开关sw3具有接收数据信号xdata的第一端、接收第一画面栅极信号gate_a的控制端及耦接第一区域发光开关fsw1的第二端的第二端。

78.第四开关sw4具有耦接第一区域发光开关fsw1的第二端的第一端、接收第二画面栅极信号gate_b的控制端及第二端。第一电容c1耦接于第一开关sw1的第二端与第四开关sw4的第二端之间。第五开关sw5具有耦接第四开关sw4的第二端的第一端、接收重置信号reset的控制端及接收第二直流电平res_dc的第二端。

79.第六开关sw6具有耦接第一区域发光开关fsw1的第二端的第一端、耦接第四开关sw4的第二端的控制端及第二端。第七开关sw7具有接收数据信号xdata的第一端、接收第二画面栅极信号gate_b的控制端及耦接第六开关sw6的第二端的第二端。第八开关sw8具有耦接第七开关sw7的第二端的第一端、接收第一画面栅极信号gate_a的一控制端及耦接第四开关sw4的第二端的一第二端。

80.第九开关sw9具有耦接发光元件emd的另一端的第一端、接收第二画面发光信号frame_b的控制端及第二端。第二电容c2耦接于第八开关sw8的第二端与第九开关sw9的第二端之间。第十开关sw10具有耦接第九开关sw9的第二端的第一端、接收设定信号set的控制端及接收第一直流电平ir_dc的第二端。

81.在本实施例中,第一开关sw1至第十开关sw10皆为p型晶体管为例,但本发明实施例不以此为限。并且,第二直流电平res_dc可以不同第一直流电平ir_dc。

82.图3为依据本发明一实施例的像素电路的操作时序示意图。请参照图2及图3,在本实施例中,示出第一画面期间frame_1及第二画面期间frame_2以举例说明,并且第二画面期间frame_2示出为第一画面期间frame_1的下一画面期间,亦即第二画面期间frame_2与第一画面期间frame_1之间没有任何的间隔。然而,本发明实施例不以此为限。

83.在本实施例中,第一画面发光信号frame_a致能于第一画面期间frame_1的多个第一发光期间pm1中,第二画面发光信号frame_b致能于第二画面期间frame_2的多个第二发光期间pm2中,并且共同发光信号gem致能于第一画面期间frame_1的所述多个第一发光期间pm1及第二画面期间frame_2的所述多个第二发光期间pm2中。

84.重置信号reset致能于第一画面期间frame_1的第一重置期间pr1及第二画面期间frame_2的第二重置期间pr2中,第一画面栅极信号gate_a致能于第一画面期间frame_1的第一设定期间ps1中,第二画面栅极信号gate_b致能于第二画面期间frame_2的第二设定期间ps2中,并且设定信号set致能于第一画面期间frame_1的第一重置期间pr1及第一设定期间ps1及第二画面期间frame_2中的第二重置期间pr2及第二设定期间ps2。

85.在本实施例中,第一设定期间ps1位于第一重置期间pr1之后,且第二设定期间ps2位于第二重置期间pr2之后。并且,这些第一发光期间pm1周期性配置于第一画面期间frame_1中,这些第二发光期间pm2周期性配置于第二画面期间frame_2中。以及,第一设定期间ps1及第一重置期间pr1不重叠于这些第一发光期间pm1,且第二设定期间ps2及第二重置期间pr2不重叠于这些第二发光期间pm2。

86.图4a为依据本发明一实施例的像素电路于第一重置期间及第二重置期间的操作示意图。请参照图2、图3及图4a,在第一画面期间frame_1的第一重置期间pr1及第二画面期间frame_2的第二重置期间pr2中,重置信号reset及设定信号set为致能,第一画面栅极信号gate_a、第二画面栅极信号gate_b、共同发光信号gem、第一画面发光信号frame_a及第二画面发光信号frame_b为禁能。

87.此时,第二开关sw2、第五开关sw5、及第十开关sw10为导通,第一区域发光开关fsw1、第二区域发光开关fsw2、共同发光开关gsw、第一开关sw1、第三开关sw3、第四开关sw4、第六开关sw6、第七开关sw7、第八开关sw8、第九开关sw9为截止。因此,第一电容c1以及第二电容c2存储第一直流电平ir_dc与第二直流电平res_dc之间的压差。其中,第一直流电平ir_dc与第二直流电平res_dc之间的压差可以用来补偿晶体管的临界电压或调整所显示

的亮度,但本发明实施例不此为限。

88.图4b为依据本发明一实施例的像素电路于第一设定期间及第二设定期间的操作示意图。请参照图2、图3及图4b,在第一画面期间frame_1的第一设定期间ps1中,设定信号set及第一画面栅极信号gate_a为致能,重置信号reset、第二画面栅极信号gate_b、共同发光信号gem、第一画面发光信号frame_a及第二画面发光信号frame_b为禁能。

89.此时,第二开关sw2、第三开关sw3、第六开关sw6、第八开关sw8、及第十开关sw10为导通,第一区域发光开关fsw1、第二区域发光开关fsw2、共同发光开关gsw、第一开关sw1、第四开关sw4、第五开关sw5、第七开关sw7、第九开关sw9为截止。因此,第一电容c1以及第二电容c2存储第一直流电平ir_dc与第二直流电平res_dc之间的压差与数据信号xdata的电压电平的总和。

90.图4c为依据本发明一实施例的像素电路于第一发光期间的操作示意图。请参照图2、图3及图4c,在第一画面期间frame_1的第一发光期间pm1中,共同发光信号gem及第一画面发光信号frame_a为致能,设定信号set、重置信号reset、第一画面栅极信号gate_a、第二画面栅极信号gate_b、及第二画面发光信号frame_b为禁能。

91.此时第一区域发光开关fsw1、共同发光开关gsw、第一开关sw1、第六开关sw6为导通,第二区域发光开关fsw2、第二开关sw2、第三开关sw3、第四开关sw4、第五开关sw5、第七开关sw7、第八开关sw8、第九开关sw9、及第十开关sw10为截止。并且,第一驱动电流i1经由导通的第一区域发光开关fsw1、第六开关sw6及共同发光开关gsw传送至第一发光部分pem1。由于第六开关sw6的导通程度相关于第一电容c1所存储的电压,因此第一驱动电流i1的电流幅度相关于数据信号xdata。

92.图4d为依据本发明一实施例的像素电路于第二设定期间的操作示意图。请参照图2、图3及图4d,在第二画面期间frame_2的第二设定期间ps2中,设定信号set及第二画面栅极信号gate_b为致能,重置信号reset、第一画面栅极信号gate_a、共同发光信号gem、第一画面发光信号frame_a及第二画面发光信号frame_b为禁能。

93.此时,第二开关sw2、第四开关sw4、第六开关sw6、第七开关sw7、及第十开关sw10为导通,第一区域发光开关fsw1、第二区域发光开关fsw2、共同发光开关gsw、第一开关sw1、第三开关sw3、第五开关sw5、第八开关sw8、第九开关sw9为截止。因此,第一电容c1以及第二电容c2仍存储第一直流电平ir_dc与第二直流电平res_dc之间的压差与数据信号xdata的电压电平的总和。

94.图4e为依据本发明一实施例的像素电路于第二发光期间的操作示意图。请参照图2、图3及图4e,在第一画面期间frame_2的第二发光期间pm2中,共同发光信号gem及第二画面发光信号frame_b为致能,设定信号set、重置信号reset、第一画面栅极信号gate_a、第二画面栅极信号gate_b、及第一画面发光信号frame_a为禁能。

95.此时第一区域发光开关fsw1、共同发光开关gsw、第六开关sw6、第九开关sw9为导通,第二区域发光开关fsw2、第一开关sw1、第二开关sw2、第三开关sw3、第四开关sw4、第五开关sw5、第七开关sw7、第八开关sw8、及第十开关sw10为截止。并且,第二驱动电流i2经由导通的第二区域发光开关fsw2、第六开关sw6及共同发光开关gsw接收自第二发光部分pem1。由于第六开关sw6的导通程度相关于第二电容c2所存储的电压,因此第二驱动电流i2的电流幅度相关于数据信号xdata。

96.图5为依据本发明另一实施例的像素电路的系统示意图。请参照图1及图5,像素电路pixb大致相同于像素电路pixa,其不同之处在于像素电路pixb还包括脉冲宽度控制区块pwbk,其中相同或相似元件使用相同或相似标号。在本实施例中,脉冲宽度控制区块pwbk耦接共同发光开关gsw的控制端,且接收时间参考直流电平t_dc、时间电压斜率参考信号tvr以及时间数据信号tdata,以提供共同发光信号gemx取代共同发光信号gem,其中共同发光信号gemx基于时间数据信号tdata而调整。

97.综上所述,本发明实施例的像素电路,通过全新设计的驱动区块,可提供具有双向驱动能力的发光元件所需要的不同流向的第一驱动电流以及第二驱动电流,以使像素电路可以应用新型发光元件而顺利运行。

98.虽然本发明已以实施例公开如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的构思和范围内,当可作些许的变动与润饰,故本发明的保护范围当视权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1