像素电路及其驱动方法和显示面板与流程

本发明涉及显示,尤其涉及一种像素电路及其驱动方法和显示面板。

背景技术:

1、随着显示技术的发展,用户对显示面板的显示质量要求越来越高。

2、显示面板在工作过程中,会有不同的工作模式,且不同工作模式对应的刷新频率不同,例如在显示静态画面和动态画面时所对应的刷新频率是不同的。然而,在高刷新率下,显示面板的画面显示效果较差。

技术实现思路

1、本发明提供了一种像素电路及其驱动方法和显示面板,以提高显示画面在高刷新率下的显示效果。

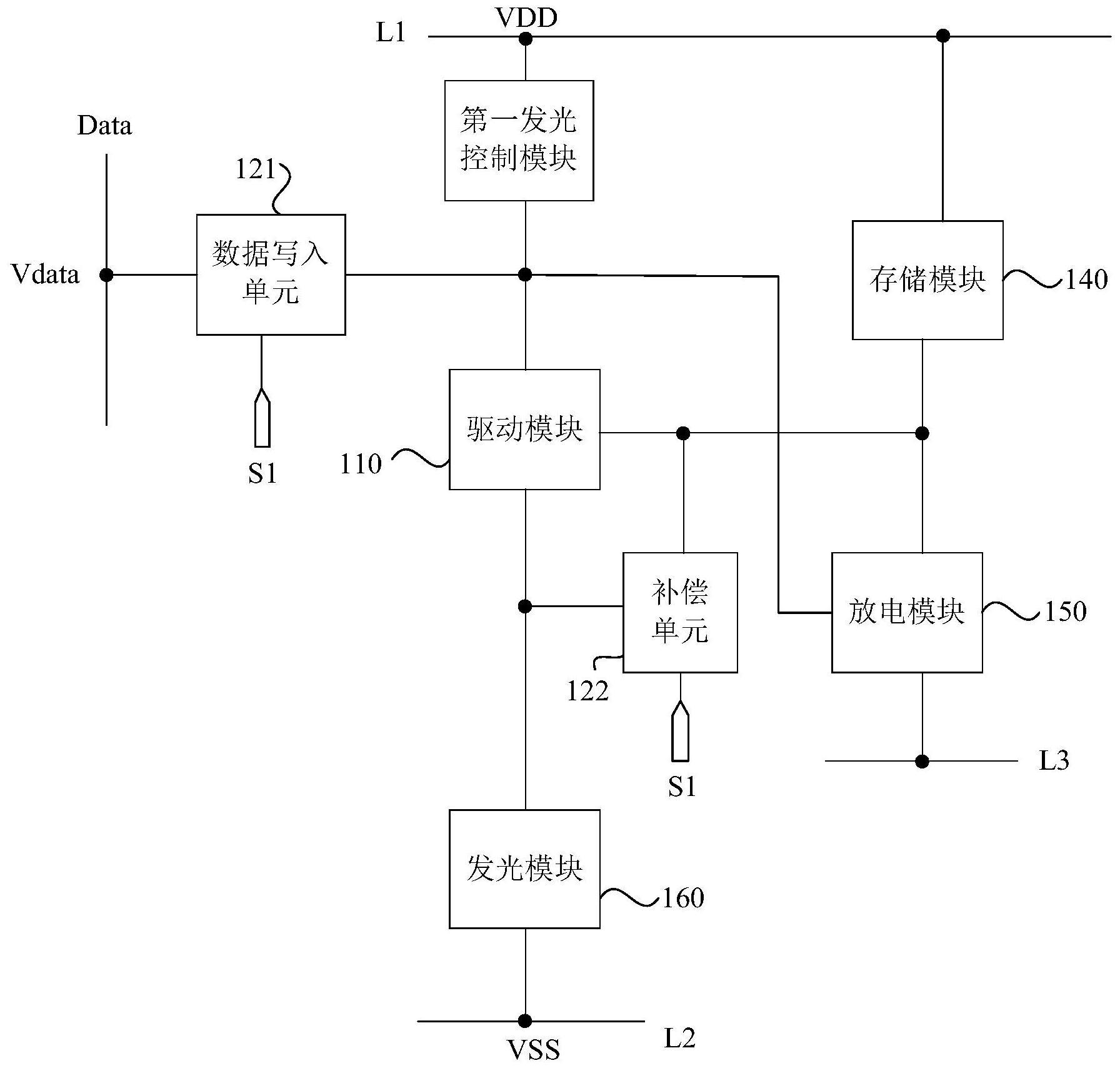

2、根据本发明的一方面,提供了一种像素电路,包括:驱动模块、数据写入模块存储模块、放电模块和发光模块;

3、数据写入模块与数据线和驱动模块连接,数据写入模块用于向驱动模块的控制端传输数据线上的数据电压,

4、存储模块与驱动模块的控制端连接,用于存储驱动模块的控制端的电压;

5、放电模块与驱动模块的控制端连接,用于响应数据电压,对驱动模块的控制端的电压进行放电控制;

6、驱动模块和发光模块连接,驱动模块用于驱动发光模块发光。

7、可选的,放电模块的关断临界电压的绝对值大于或等于驱动模块的导通临界电压的绝对值;

8、可选地,放电模块的关断临界电压与驱动模块的导通临界电压的极性相反。

9、可选的,数据写入模块包括数据写入单元和补偿单元,数据写入单元连接于数据线和驱动模块的第一端之间,补偿单元连接于驱动模块的第二端和控制端之间;

10、放电模块的第一端与驱动模块的控制端连接;

11、放电模块的控制端与驱动模块的第一端连接;或者,放电模块的控制端与数据线连接;

12、可选地,数据写入单元的控制端和补偿单元的控制端与第一扫描信号线连接;

13、可选地,驱动模块包括第一晶体管,放电模块包括第二晶体管,存储模块包括存储电容;

14、第一晶体管的第一极为驱动模块的第一端,第一晶体管的第二极为驱动模块的第二端,第一晶体管的栅极为驱动模块的控制端,

15、第二晶体管的栅极与驱动模块的第一端连接,第二晶体管的第一极与驱动模块的控制端连接,第二晶体管的第二极与第三电源线连接;

16、存储电容的第一极与第一电源线连接,存储电容的第二极与驱动模块的控制端连接;

17、其中,第一晶体管为增强型晶体管,第二晶体管为耗尽型晶体管,第二晶体管的夹断电压的绝对值大于或等于第一晶体管的阈值电压的绝对值;

18、可选地,第二晶体管的夹断电压与第一晶体管的阈值电压的极性相反;

19、可选地,第一晶体管和第二晶体管的沟道类型相同;

20、可选地,第一晶体管和第二晶体管为p型晶体管;或者,第一晶体管和第二晶体管为n型晶体管。

21、可选的,像素电路还包括漏电抑制模块,漏电抑制模块连接于放电模块的第二端与第三电源线之间,放电模块的第一端与驱动模块的控制端连接;

22、和/或,像素电路还包括泄放电阻,泄放电阻连接于放电模块和第三电源线之间;

23、可选地,漏电抑制模块连接于放电模块的第二端和泄放电阻之间;或者,漏电抑制模块连接于泄放电阻和第三电源线之间;

24、可选地,漏电抑制模块的控制端和数据写入模块的控制端均与第一扫描信号线连接;

25、可选地,漏电抑制模块包括第三晶体管,第三晶体管的栅极连接第一扫描信号线;第三晶体管的第一极与放电模块的第二端连接,或者,第三晶体管的第一极经泄放电阻与放电模块的第二端连接;第三晶体管的第二极与第三电源线连接,或者,第三晶体管的第二极经泄放电阻与第三电源线连接;

26、可选地,发光模块连接于驱动模块和第二电源线之间,第二电源线复用为第三电源线。

27、可选的,像素电路还包括第一发光控制模块和第二发光控制模块,第一发光控制模块的控制端和第二发光控制模块的控制端均与发光控制信号线连接,第一发光控制模块连接于第一电源线和驱动模块的第一端之间,第二发光模块连接于驱动模块的第二端和发光模块的第一端之间,发光模块的第二端与第二电源线连接;

28、可选地,第一发光控制模块包括第四晶体管,第二发光控制模块包括第五晶体管,第四晶体管的栅极和第五晶体管的栅极均与发光控制信号线连接,第四晶体管的第一极与第一电源线连接,第四晶体管的第二极与驱动模块的第一端连接,第五晶体管的第一极与驱动模块的第二端连接,第五晶体管的第二极与发光模块的第一端连接;

29、可选地,数据写入单元包括第六晶体管,补偿单元包括第七晶体管,第六晶体管的栅极和第七晶体管的栅极均与第一扫描信号线连接,第六晶体管的第一极与数据线连接,第六晶体管的第二极与驱动模块的第一端连接,第七晶体管的第一极与驱动模块的第二端连接,第七晶体管的第二极与驱动模块的控制端连接。

30、可选的,像素电路还包括初始化模块,初始化模块连接于初始化信号线和发光模块的第一端之间,用于在初始化阶段向发光模块的第一端传输初始化信号线上的初始化电压;

31、初始化模块包括第八晶体管,第八晶体管的栅极与第二扫描信号线连接,第八晶体管的第一极与初始化信号线连接,第八晶体管的第二极与发光模块的第一端连接。

32、根据本发明的另一方面,提供了一种像素电路的驱动方法,像素电路包括驱动模块、数据写入模块、存储模块、放电模块和发光模块;数据写入模块与数据线和驱动模块连接,存储模块与驱动模块的控制端连接,放电模块与驱动模块的控制端连接,驱动模块和发光模块连接;

33、像素电路的驱动方法包括:

34、在数据写入阶段,控制放电模块响应数据线上的数据电压,对驱动模块的控制端的电压进行放电控制,之后控制数据写入模块将数据电压写入至驱动模块的控制端;

35、在发光阶段,控制驱动模块驱动发光模块发光。

36、可选的,放电模块的关断临界电压的绝对值大于或等于驱动模块的导通临界电压的绝对值;

37、控制放电模块响应数据线上的数据电压,对驱动模块的控制端的电压进行放电控制的步骤包括:

38、若在数据写入阶段的初始时刻,数据电压与驱动模块的控制端的初始电压的差值和放电模块的关断临界电压满足导通条件时,则放电模块响应数据电压导通,对驱动模块的控制端的电压进行放电;

39、若在数据写入阶段的初始时刻,数据电压与驱动模块的控制端的初始电压的差值和放电模块的关断临界电压满足关断条件时,则放电模块响应数据电压关断,不对驱动模块的控制端的电压进行放电;

40、驱动模块的控制端的初始电压为上一显示帧,通过数据写入模块将数据电压写入至驱动模块的控制端而得到的电压。

41、可选的,数据写入模块包括数据写入单元和补偿单元,数据写入单元连接于数据线和驱动模块的第一端之间,补偿单元连接于驱动模块的第二端和控制端之间;放电模块的第一端与驱动模块的控制端连接;放电模块的控制端与驱动模块的第一端连接;或者,放电模块的控制端与数据线连接;

42、在数据写入阶段,控制数据写入模块将数据电压写入至驱动模块的控制端的步骤包括:

43、在数据写入阶段,控制数据写入单元将数据电压经补偿单元写入至驱动模块的控制端;

44、像素电路还包括初始化模块,初始化模块连接于初始化信号线和发光模块的第一端之间;

45、像素电路的驱动方法还包括:

46、在初始化阶段,控制初始化模块向发光模块的第一端传输初始化信号线上的初始化电压;

47、其中,在一显示帧内,初始化阶段位于发光阶段之前。

48、根据本发明的另一方面,提供了一种显示面板,包括本发明任意实施例所提供的像素电路。

49、本发明实施例提供的技术方案,通过设置放电模块可在数据写入阶段响应当前帧数据电压导通,对存储模块上存储的驱动模块控制端的电压进行放电,之后将数据电压再写入至驱动模块的控制端。本发明实施例提供的技术方案,无需在数据写入阶段之前对驱动模块的控制端电位进行初始化,而是利用存储模块上现有的电荷进行充电,在将数据电压写入驱动模块的控制端之前,先通过放电模块对存储模块上的电荷进行放电,直到使得驱动模块的控制端电位接近当前帧数据电压,此时驱动模块的控制端的电压仍维持在较高水平,之后将当前帧数据电压再写入至驱动模块的控制端。相对于现有的先将驱动模块的控制端电位复位成一个很低的电压再充电的方案,本发明实施例提供的技术方案能够在更短时间内将驱动模块的控制端的电位充电至目标电压,从而使得数据电压在高刷新频率下也能够完全写入至驱动模块的控制端,有效改善了因屏体刷新频率提高导致像素电路充电不足的问题,能够保证显示面板在高频驱动模式下正常显示,有利于提高显示效果。

50、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!