阵列栅驱动单元、电路,显示屏和电子设备的制作方法

本技术涉及显示屏,尤其涉及一种阵列栅驱动单元、电路,显示屏和电子设备。

背景技术:

1、显示屏的行扫描方式,通常采用阵列栅驱动(gate on array,goa)设计。显示驱动芯片(display driver integration chip,ddic)输出时钟信号输入到显示屏的goa电路,goa电路根据时钟信号产生行扫描信号到显示屏的显示单元,控制显示屏显示数据。

2、goa电路包括多个goa单元,每个goa单元对应显示单元的一行栅线。goa单元在工作过程中持续接收时钟信号,控制goa单元的电容进行充电和放电的切换,导致goa单元的功耗高。并且,在显示屏的实际运行过程中,受外界环境的温度,或静电场等因素的干扰,goa电路中各个goa单元的tft可能会产生输出异常的问题。

技术实现思路

1、本技术提供了一种阵列栅驱动单元、阵列栅驱动电路,显示屏以及电子设备,目的在于实现goa电路的低功耗运行,以及避免外界因素对goa电路运行的干扰而导致输出异常。

2、为了实现上述目的,本技术提供了以下技术方案:

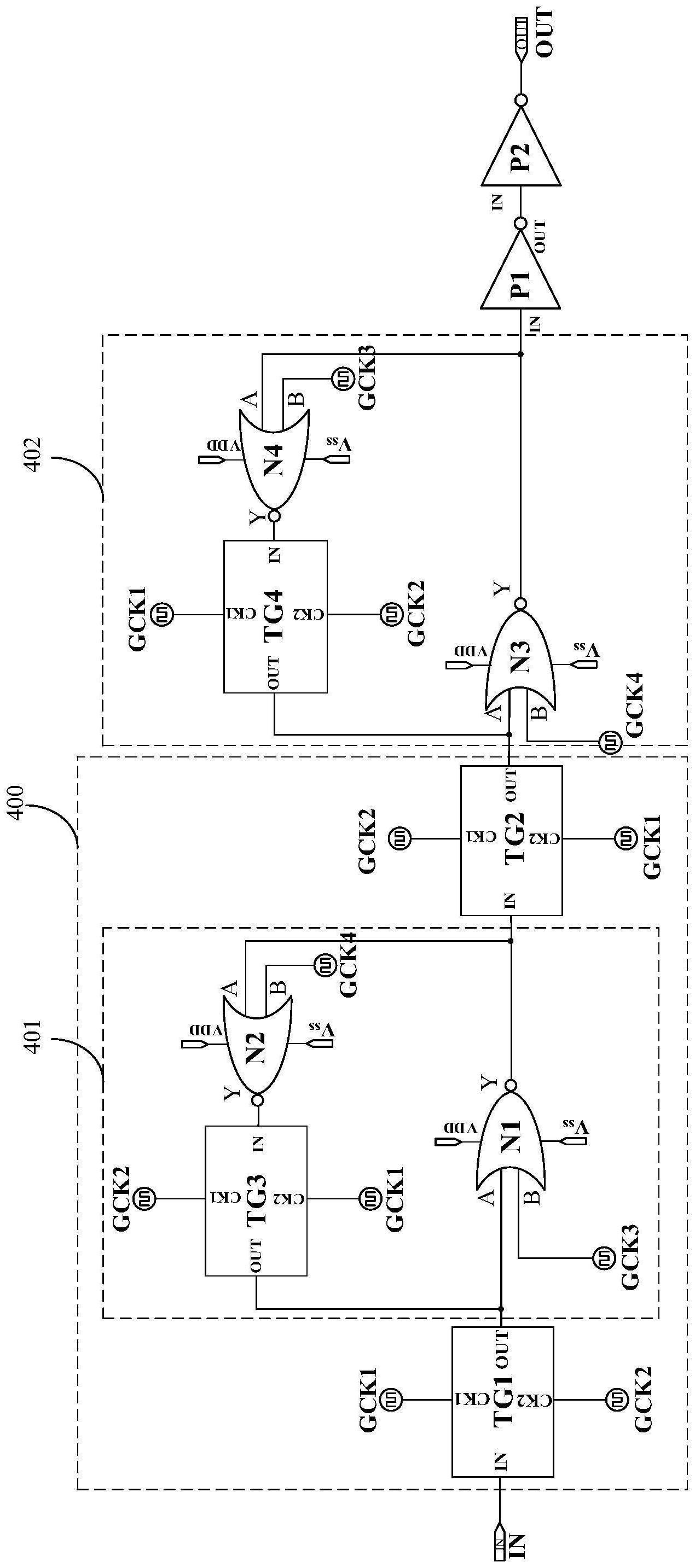

3、第一方面,本技术提供了一种阵列栅驱动单元,包括:锁存电路和逻辑门,其中:锁存电路用于接收第一信号,生成第二信号并将第二信号锁存第一时间之后输出;逻辑门的第一输入端连接锁存电路,第二输入端用于接收第一时钟信号,逻辑门的第一输入端未接收到信号,或者锁存电路输出的第二信号和第一时钟信号相同,逻辑门输出第三信号,第三信号与第一时钟信号相反。

4、由上述内容可以看出:逻辑门的第二输入端接收第一时钟信号,该时钟信号可保持稳定,不受外界环境的温度、静电场等因素的干扰,因此,逻辑门在第一时钟信号的作用下输出的第三信号,也可稳定不受外界环境的温度、静电场等因素的干扰,阵列栅驱动单元以逻辑门输出的第三信号驱动对应的栅线运行,可以保证阵列栅驱动单元输出的信号不发生异常。

5、进一步的,阵列栅驱动单元中,锁存电路接收第一信号,将第一信号锁存第一时间之后输出第二信号,逻辑门在第一时钟信号和第二信号的作用下输出第三信号驱动该阵列栅驱动单元对应的栅线运行,可以满足阵列栅驱动单元在一个时刻接收的第一信号延迟向栅线输出的要求。并且,因阵列栅驱动单元中不包括电容,可以避免电容充放电带来的功耗高的问题。

6、在一个可能的实施方式中,锁存电路包括:第一传输门、锁存回路和第二传输门,其中:第一传输门的输入端用于接收第一信号,时钟端用于接收时钟信号,第一传输门在导通状态下,第一传输门的输出端用于输出第一信号;锁存回路连接第一传输门的输出端,用于接收第一传输门输出的第一信号,生成第二信号;第二传输门的输入端连接锁存回路,用于接收第二信号,第二传输门的时钟端用于接收时钟信号,第二传输门在第一时间之后导通,第二传输门的输出端用于在导通状态输出第二信号,第一传输门和第二传输门的开关状态相反。

7、在本可能的实施方式中,第一传输门在时钟信号的作用下导通,因第二传输门的开关状态和第一传输门相反,第二传输门则截止,第一传输门导通进而将第一信号向锁存回路传输,锁存回路接收该第一信号之后生成第二信号,且因第二传输门截止,该第二信号无法经过第二传输门,第二传输门在第一时间之后导通,第二信号则可在第一时间之后,由第二传输门的输出端输出,如此实现了锁存电路接收第一信号生成第二信号将第二信号锁存第一时间。

8、在一个可能的实施方式中,锁存回路包括:第三传输门、第一或非门以及第二或非门,其中:第一或非门的第一输入端连接第三传输门的输出端,第二输入端用于接收第二时钟信号;第一或非门和第三传输门的公共端用于连接第一传输门的输出端;第二或非门的第一输入端连接第一或非门的输出端,第二输入端用于接收第一时钟信号,输出端连接第三传输门的输入端;第三传输门的时钟端用于接收时钟信号,第三传输门和第一传输门的开关状态相同。

9、在一个可能的实施方式中,逻辑门包括第三或非门。

10、在本可能的实施方式中,逻辑门为第三或非门,或非门的两个输入端中的一个输入端接收高电平,可输出低电平。因此,第三或非门的第二输入端接收的第一时钟信号为高电平,第三或非门的输出端可输入低电平,不受第三或非门的第一输入端接收的信号的限制,可适用于阵列栅驱动单元以低电平驱动栅线运行的场景。

11、在一个可能的实施方式中,锁存回路包括:第三传输门、第一与非门以及第二与非门,其中:第一与非门的第一输入端连接第三传输门的输出端,第二输入端用于接收第二时钟信号;第一与非门和第三传输门的公共端用于连接第一传输门的输出端;第二与非门的第一输入端连接第一与非门的输出端,第二输入端用于接收第一时钟信号,输出端连接第三传输门的输入端;第三传输门的时钟端用于接收时钟信号,第三传输门和第一传输门的开关状态相同。

12、在一个可能的实施方式中,逻辑门包括第三与非门。

13、在本可能的实施方式中,逻辑门为第三与非门,与非门的两个输入端中的一个输入端接收低电平,可输出高电平。因此,第三与非门的第二输入端接收的第一时钟信号为高电平,第三与非门的输出端可输入高电平,不受第三与非门的第一输入端接收的信号的限制,可适用于阵列栅驱动单元以高电平驱动栅线运行的场景。

14、在一个可能的实施方式中,还包括:稳压回路,稳压回路的输入端连接逻辑门的输出端,稳压回路的输出端连接逻辑门的第一输入端,稳压回路用于稳定逻辑门的输入端接收的信号。

15、在本可能的实施方式中,在逻辑门的输入端输入的信号为高频信号的场景下,逻辑门会存在接收信号出现误差的现象,基于此,稳压回路连接于逻辑门的输入端和输出端之间,可以起到稳定逻辑门的输入端接收的信号的作用。

16、在一个可能的实施方式中,稳压回路包括:第四传输门和第四或非门,其中:第四或非门的第一输入端连接逻辑门的输出端,第二输入端用于接收第二时钟信号,输出端连接第四传输门的输入端;第四传输门的时钟端用于接收时钟信号,输出端连接逻辑门的第一输入端。

17、在本可能的实施方式中,或非门具备保证两个输入端中的一个输入端接收高电平,可保证输出低电平的功能,因此,第四或非门的第二输入端接收第二时钟信号,该时钟信号可保持稳定为高电平,第四或非门不受第一输入端接收的信号的影响,通过第四传输门向逻辑门的输入端输出低电平,稳定逻辑门的输入端接收的低电平信号。并且,第四或非门的第一输入端连接逻辑门的输出端,接收其输出的低电平,第二时钟信号为低电平,第四或非门则通过第四传输门向逻辑门的输入端输出高电平,稳定逻辑门的输入端接收的高电平信号。进一步的,第四传输门应和第二传输门的开关状态相同。

18、在一个可能的实施方式中,稳压回路包括:第四传输门和第四与非门,其中:第四与非门的第一输入端连接逻辑门的输出端,第二输入端用于接收第二时钟信号,输出端连接第四传输门的输入端;第四传输门的时钟端用于接收时钟信号,输出端连接逻辑门的第一输入端。

19、在本可能的实施方式中,与非门具备保证两个输入端中的一个输入端接收低电平,可保证输出高电平的功能,因此,第四与非门的第二输入端接收第二时钟信号,该时钟信号可保持稳定为低电平,第四与非门不受第一输入端接收的信号的影响,通过第四传输门向逻辑门的输入端输出高电平,稳定逻辑门的输入端接收的高电平信号。并且,第四与非门的第一输入端连接逻辑门的输出端,接收其输出的高电平,第二时钟信号为高电平,第四或非门则通过第四传输门向逻辑门的输入端输出低电平,稳定逻辑门的输入端接收的低电平信号。进一步的,第四传输门应和第二传输门的开关状态相同。

20、在一个可能的实施方式中,还包括:第一反相器和第二反相器,其中:第一反相器的输入端连接逻辑门的输出端,输出端连接第二反相器的输入端。

21、在本可能的实施方式中,通过两个依次连接的反相器,可以实现稳压的作用。

22、在一个可能的实施方式中,还包括:第五或非门和第三反相器,其中:第五或非门的第一输入端连接第三或非门的输出端,第二输入端用于接收控制信号,输出端连接第三反相器的输入端。

23、在本可能的实施方式中,第五或非门的一路输入信号为高电平,则输出低电平。在需要单独控制一个阵列栅驱动单元输出的输出信号的应用场景下,只要第五或非门的第二输入端接收的控制信号一直保持高电平,第五或非门的输出端就会一直输出低电平,不受或第五或非门的第一输入端输入的输入信号的影响。第五或非门的输出端连接第三反相器,第三反相器的输出端实现了阵列栅驱动单元的输出信号一直保持高电平。阵列栅驱动单元向其对应的栅线输出高电平的行扫描信号,栅线不被启动运行。阵列栅驱动电路中的多个阵列栅驱动单元,均可被控制信号控制而输出高电平的行扫描信号,进而控制显示单元的多行栅线不运行,降低显示屏的刷新率,节省功耗。

24、在一个可能的实施方式中,还包括:第五与非门和第四反相器,其中:第五与非门的第一输入端连接第三与非门的输出端,第二输入端用于接收控制信号,输出端连接第三反相器的输入端。

25、在本可能的实施方式中,第五与非门的一路输入信号为低电平,则输出高电平。在需要单独控制一个阵列栅驱动单元输出的输出信号的应用场景下,只要第五与非门的第二输入端接收的控制信号一直保持低电平,第五与非门的输出端就会一直输出高电平,第五与非门的输出端连接第四反相器,第四反相器的输出端实现了阵列栅驱动单元的输出信号一直保持低电平,不启动栅线。阵列栅驱动电路中的多个阵列栅驱动单元,均可被控制信号控制而输出低电平的行扫描信号,进而控制显示单元的多行栅线不运行,降低显示屏的刷新率,节省功耗。

26、在一个可能的实施方式中,还包括:第六或非门、第五反相器和第六反相器,其中:第六或非门的第一输入端连接第三与非门的输出端,第二输入端用于接收控制信号,输出端连接第五反相器的输入端,第五反相器的输出端连接第六反相器的输入端。

27、在本可能的实施方式中,第六或非门的第二输入端接收控制信号维持高电平,第六或非门的输出端则可一直输出低电平,第六或非门的输出端依次连接第五反相器和第六反相器,第六反相器的输出端可一直输出低电平,实现了阵列栅驱动单元的输出信号一直保持低电平。阵列栅驱动电路中的多个阵列栅驱动单元,均可被控制信号控制输出低电平的行扫描信号,进而控制显示单元的多行栅线不运行,降低显示屏的刷新率,节省功耗。

28、第二方面,本技术提供了一种阵列栅驱动电路,包括级联的n个阵列栅驱动单元,每一个阵列栅驱动单元如如第一方面任意一项所述,n为大于3的正整数。

29、第三方面,本技术提供了一种显示屏,应用于电子设备,显示屏包括:显示单元、与显示单元连接的阵列栅驱动电路;阵列栅驱动电路包括级联的n个阵列栅驱动单元,每一个阵列栅驱动单元如第一方面任意一项所述,每一个阵列栅驱动单元连接显示单元的一行栅线,n为大于3的正整数。

30、第四方面,本技术提供了一种电子设备,包括:一个或多个处理器、存储器以及如第三方面任意一项的显示屏;存储器与一个或多个处理器耦合,存储器用于存储计算机程序代码,计算机程序代码包括计算机指令。

- 还没有人留言评论。精彩留言会获得点赞!