一种驱动电路及其驱动方法、电子纸与流程

本技术涉及显示,尤其涉及一种驱动电路及其驱动方法、电子纸。

背景技术:

1、电子纸具有纸介质一样的视觉特点,且凭借其超宽视角、超低功耗、纯反射模式等优势,成为便携式设备的新宠。现有的电子纸一般包括显示面板和驱动芯片。电子纸通过驱动芯片对显示面板中的栅线和数据线加载驱动信号来实现画面显示。

2、目前,低成本和窄边框是电子纸的发展趋势,然而,设置驱动芯片制约了电子纸向低成本和窄边框的发展。

技术实现思路

1、本技术的实施例提供了一种驱动电路及其驱动方法、电子纸,该驱动电路能够应用在电子纸上,采用该驱动电路替代电子纸上的栅极驱动芯片,能够降低电子纸的成本并有利于窄边框电子纸的制备。

2、为达到上述目的,本技术的实施例采用如下技术方案:

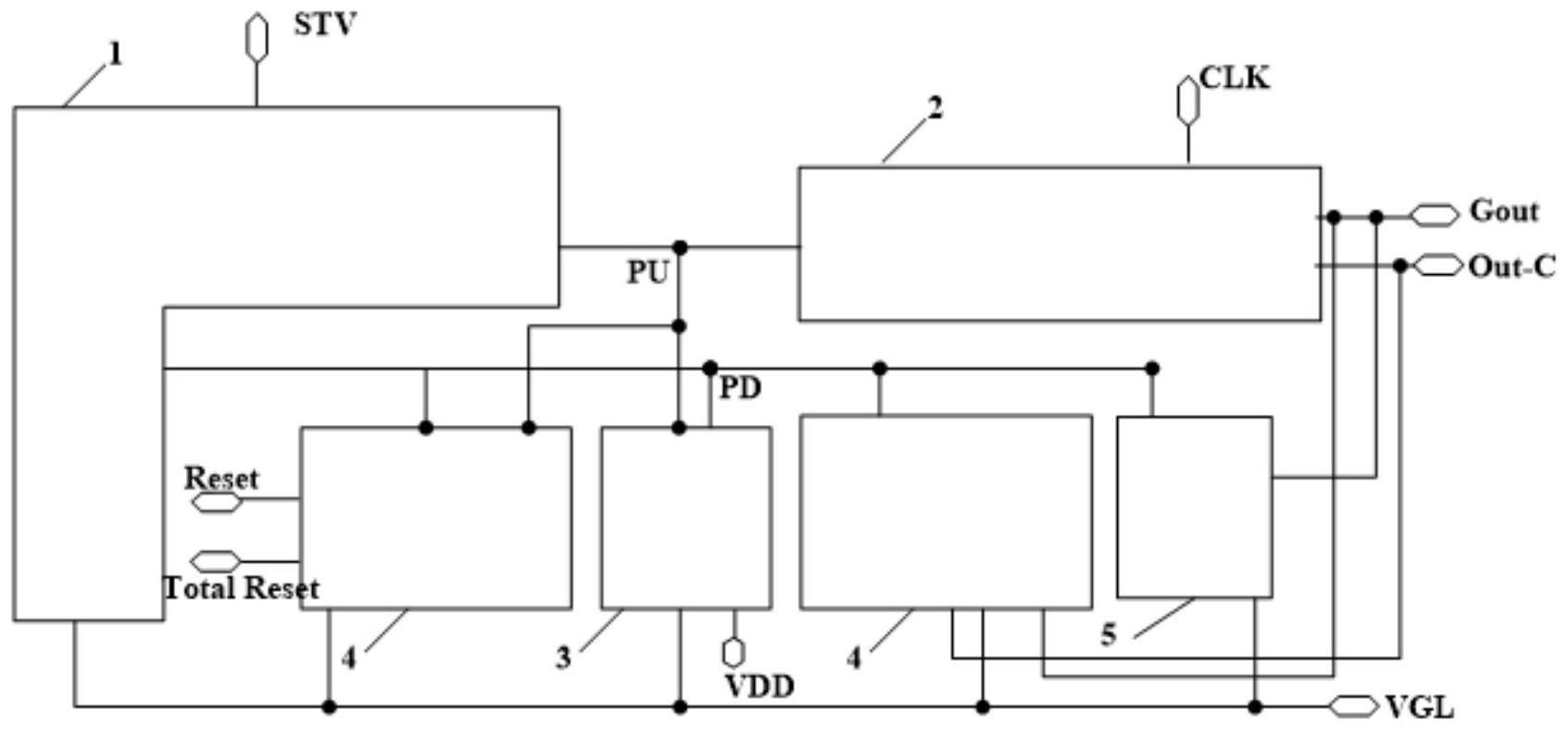

3、第一方面,本技术的实施例提供了一种驱动电路,包括级联设置的多个驱动单元,所述驱动单元与至少一条栅线电连接,所述驱动单元包括第一移位寄存器和第二移位寄存器,至少一条所述栅线分别与所述第一移位寄存器和所述第二移位寄存器电连接;

4、所述第一移位寄存器被配置为向所述栅线输入第一栅极信号,所述第二移位寄存器被配置为向所述栅线输入第二栅极信号,所述第一栅极信号和所述第二栅极信号被配置为分时输入;

5、所述第一栅极信号和所述第二栅极信号中的一个被配置为控制电子纸初始化,另一个被配置为控制所述电子纸显示。

6、在本技术的至少一个实施例中,所述驱动单元与一条所述栅线电连接;第n条所述栅线中传输的所述第一栅极信号与第n+1条所述栅线中传输的所述第一栅极信号之间间隔第一预设时间段;第n+1条所述栅线中传输的所述第一栅极信号与第n条所述栅线中传输的所述第二栅极信号之间间隔第二预设时间段;同一条所述栅线中传输的所述第一栅线信号和所述第二栅极信号之间间隔第三预设时间段;其中,n为正整数;

7、所述第二预设时间段为所述第一预设时间段的两倍,所述第三预设时间段为所述第一预设时间段的四倍。

8、在本技术的至少一个实施例中,所述第一移位寄存器和所述第二移位寄存器均包括防干扰子电路,所述第一移位寄存器的所述防干扰子电路与所述第二移位寄存器电连接,所述第二移位寄存器的所述防干扰子电路与所述第一移位寄存器电连接;

9、在所述第一移位寄存器输出所述第一栅极信号时,所述第一移位寄存器中的所述防干扰子电路被配置为在所述第一栅极信号的控制下,防止所述第一移位寄存器中其它器件对所述第一栅极信号的干扰;在所述第二移位寄存器输出所述第二栅极信号时,所述第二移位寄存器中的所述防干扰子电路被配置为在所述第二栅极信号的控制下,防止所述第二移位寄存器中其它器件对所述第二栅极信号的干扰。

10、在本技术的至少一个实施例中,所述第一移位寄存器和所述第二移位寄存器的电路结构相同;所述第一移位寄存器还包括:

11、输入子电路,分别与第一节点、第二节点、触发信号输入端和第一电平信号输入端电连接,被配置为在所述触发信号输入端输入的触发信号的控制下,拉高所述第一节点的电压;

12、输出子电路,分别与所述第一节点、时钟信号输入端、所述第一移位寄存器的第一输出端和所述第一移位寄存器的第二输出端电连接,所述输出子电路被配置为在所述第一节点的电压的控制下,将所述时钟信号输入端输入的信号分别从所述第一输出端和所述第二输出端输出。

13、在本技术的至少一个实施例中,在同一级所述驱动单元中,所述第一移位寄存器电连接的所述触发信号输入端输入的所述触发信号与所述第二移位寄存器电连接的所述触发信号输入端输入的所述触发信号的时间间隔为第四预设时间段,所述第四预设时间段和所述第三预设时间段大致相等。

14、在本技术的至少一个实施例中,所述第一移位寄存器还包括:

15、去噪子电路,分别与所述第一节点、所述第二节点、所述电源信号输入端、和所述第一电平信号输入端电连接,所述去噪子电路被配置为在所述第一节点的电压的控制下,拉低所述第二节点的电压;

16、复位子电路,分别与所述第一节点、所述第二节点、所述输入子电路、所述输出子电路、所述防干扰子电路、第一复位信号输入端、第二复位信号输入端、所述第一电平信号输入端、所述第一输出端和所述第二输出端电连接,所述复位子电路被配置为在所述第一复位信号输入端输入的第一复位信号的控制下,拉低所述第一节点、所述第一输出端和所述第二输出端的电压,所述复位子电路还被配置为在所述第二复位信号输入端输入的第二复位信号的控制下,拉低所述第一节点、所述第一输出端和所述第二输出端的电压。

17、在本技术的至少一个实施例中,所述第一移位寄存器还包括:

18、所述防干扰子电路,分别与所述第二节点、所述输出子电路、所述去噪子电路、所述复位子电路、所述第一电平信号输入端和所述第一输出端电连接,所述防干扰子电路还被配置在所述第一移位寄存器的所述输出子电路传输的信号的控制下,拉低所述第一移位寄存器的所述第二节点的电压;

19、其中,所述第一移位寄存器的所述第一输出端、所述第二移位寄存器的所述第一输出端分别与同一条所述栅线电连接;第n级所述第一移位寄存器的所述第二输出端与第n+1级所述第一移位寄存器的所述触发信号输入端电连接,n为正整数;所述防干扰子电路还被配置为在所述第一移位寄存器的所述第一输出端传输的信号的控制下,拉低所述第二移位寄存器的所述第二节点的电压。

20、在本技术的至少一个实施例中,所述驱动电路应用于电子纸,所述电子纸包括阵列排布的多个子像素和多条数据线,所述数据线和所述栅线相交且绝缘,所述子像素位于所述数据线和所述栅线限定的区域处、且所述子像素分别与所述数据线和所述栅线电连接,同一行所述子像素与同一条所述栅线电连接;

21、所述数据线传输的信号包括初始化信号和数据信号,在一个周期内,所述初始化信号和所述数据信号的时长大致相同;

22、所述第一移位寄存器电连接的所述时钟信号输入端输入的时钟信号和所述第二移位寄存器电连接的所述时钟信号输入端输入的时钟信号,两者中的在先的信号位于所述初始化信号输出的时间段内,在后的信号位于所述数据信号输出的时间段内。

23、在本技术的至少一个实施例中,所述第二节点的数量为至少一个,所述第二节点的数量与所述防干扰子电路中的晶体管的数量相同,所述防干扰子电路中的所有所述晶体管的栅极均与所述第一输出端和所述输出子电路电连接。

24、在本技术的至少一个实施例中,所述第一移位寄存器包括第一个所述第二节点和第二个所述第二节点;

25、所述输入子电路包括第一晶体管、第二晶体管和第三晶体管,所述第一晶体管的栅极和源极分别与所述触发信号输入端电连接,所述第一晶体管的漏极与所述第一节点电连接,所述第二晶体管的栅极和所述第三晶体管的栅极分别与所述触发信号输入端电连接,所述第二晶体管的源极与第一个所述第二节点电连接,所述第三晶体管的源极与第二个所述第二节点电连接,所述第二晶体管的漏极和所述第三晶体管的漏极分别与所述第一电平信号输入端电连接;

26、所述输出子电路包括第四晶体管、第五晶体管和电容器,所述第四晶体管的栅极和所述第五晶体管的栅极分别与所述第一节点电连接,所述第四晶体管的源极和所述第五晶体管的源极分别与所述时钟信号输入端电连接,所述第四晶体管的漏极和所述第二输出端电连接,所述第五晶体管的漏极与所述第一输出端电连接,所述电容器的第一电极与所述第五晶体管的栅极电连接,所述电容器的第二电极与所述第五晶体管的漏极电连接。

27、在本技术的至少一个实施例中,所述电源信号输入端包括第一电源信号输入端和第二电源信号输入端;

28、所述去噪子电路包括第六晶体管、第七晶体管、第八晶体管和第九晶体管,所述第六晶体管的栅极和源极分别与所述第一电源信号输入端电连接,所述第六晶体管的漏极与第一个所述第二节点电连接,所述第七晶体管的栅极和源极分别与所述第二电源信号输入端电连接,所述第七晶体管的漏极与第二个所述第二节点电连接,所述第八晶体管的栅极和所述第九晶体管的栅极分别与所述第一节点电连接,所述第八晶体管的漏极和所述第九晶体管的漏极分别与所述第一电平信号输入端电连接,所述第八晶体管的源极与第一个所述第二节点电连接,所述第九晶体管的源极与第二个所述第二节点电连接。

29、在本技术的至少一个实施例中,所述第一电源信号输入端输入第一电源信号,所述第二电源信号输入端输入第二电源信号,所述第一电源信号和所述第二电源信号被配置为控制所述第六晶体管和所述第七晶体管不同时导通。

30、在本技术的至少一个实施例中,所述复位子电路包括第十晶体管、第十一晶体管、第十二晶体管、第十三晶体管、第十四晶体管、第十五晶体管、第十六晶体管和第十七晶体管;

31、所述第十晶体管的漏极、所述第十一晶体管的漏极、所述第十二晶体管的漏极、所述第十三晶体管的漏极、所述第十四晶体管的漏极、所述第十五晶体管的漏极、所述第十六晶体管的漏极和所述第十七晶体管的漏极均与所述第一电平信号输入端电连接;

32、所述第十晶体管的栅极与所述第一复位信号输入端电连接,所述第十晶体管的源极与所述第一节点电连接,所述第十一晶体管的栅极与所述第二复位信号输入端电连接,所述第十一晶体管的源极与所述第一节点电连接,所述第十二晶体管的栅极与第一个所述第二节点电连接,所述第十二晶体管的源极与所述第一节点电连接,所述第十三晶体管的栅极与第二个所述第二节点电连接,所述第十三晶体管的源极与所述第一节点电连接,所述第十四晶体管的栅极和所述第十七晶体管的栅极分别与第一个所述第二节点电连接,所述第十四晶体管的源极与所述第二输出端电连接,所述第十七晶体管的源极与所述第一输出端电连接,所述第十五晶体管的栅极和所述第十六晶体管的栅极分别与第二个所述第二节点电连接,所述第十五晶体管的源极与所述第二输出端电连接,所述第十六晶体管的源极与所述第一输出端电连接。

33、在本技术的至少一个实施例中,所述防干扰子电路包括第十八晶体管和第十九晶体管,所述第十八晶体管的栅极和所述第十九晶体管的栅极分别与所述第一输出端电连接,所述第十八晶体管的漏极和所述第十九晶体管的漏极均与所述第一电平信号输入端电连接,所述第十八晶体管的源极与第二个所述第二节点电连接,所述第十九晶体管的源极与第一个所述第二节点电连接。

34、在本技术的至少一个实施例中,所述第一移位寄存器的所述第一输出端与所述第二移位寄存器的所述第一输出端电连接在一起后再与同一条所述栅线的同一端电连接。

35、在本技术的至少一个实施例中,所述第一移位寄存器的所述第一输出端与所述栅线的一端电连接,所述第二移位寄存器的所述第一输出端与同一条所述栅线的另一端电连接。

36、第二方面,本技术的实施例提供了一种电子纸,所述电子纸为全内反射型电子纸,所述电子纸包括显示区和围绕所述显示区的周边区,所述周边区包括如第一方面中任一项所述的驱动电路;

37、所述第一栅极信号和所述第二栅极信号中的在先的信号被配置为控制所述电子纸初始化,在后的信号被配置为控制所述电子纸显示。

38、在本技术的至少一个实施例中,所述周边区包括位于所述显示区两侧相对设置的第一区域和第二区域;

39、在所述第一移位寄存器的第一输出端与所述第二移位寄存器的第一输出端电连接在一起后再与同一条所述栅线电连接的情况下,所述第一移位寄存器和所述第二移位寄存器均位于所述第一区域,或者,所述第一移位寄存器和所述第二移位寄存器均位于所述第二区域;

40、在所述第一移位寄存器的所述第一输出端与所述栅线的一端电连接,所述第二移位寄存器的所述第一输出端与同一条所述栅线的另一端电连接的情况下,所述第一移位寄存器和所述第二移位寄存器的其中一个位于所述第一区域,另一个位于所述第二区域。

41、第三方面,本技术的实施例提供了一种驱动电路的驱动方法,应用于驱动如第一方面中任一项所述的驱动电路,所述方法包括:

42、在输入阶段,向移位寄存器电连接的触发信号输入端输入触发信号,向第一电源信号输入端输入第一电源信号,向第二电源信号输入端输入第二电源信号,向第一电平信号输入端输入第一电平信号;

43、在输出阶段,向时钟信号输入端输入时钟信号,向所述第一电源信号输入端输入第一电源信号,向所述第二电源信号输入端输入第二电源信号,向所述第一电平信号输入端输入第一电平信号;

44、在复位阶段,向复位信号输入端输入复位信号,向所述第一电源信号输入端输入第一电源信号,向所述第二电源信号输入端输入第二电源信号,向所述第一电平信号输入端输入第一电平信号;

45、其中,所述移位寄存器包括第一移位寄存器和第二移位寄存器,所述第一移位寄存器和所述第二移位寄存器的驱动过程相同。

46、在本技术的至少一个实施例中,所述第一移位寄存器的触发信号为第一触发信号,所述第二移位寄存器的触发信号为第二触发信号;所述第一触发信号和所述第二触发信号之间的时间间隔为第四预设时间段,所述第一移位寄存器输出的信号和所述第二移位寄存器输出的信号之间的时间间隔为第三预设时间段,所述第四预设时间段和所述第三预设时间段大致相等。

47、在本技术的至少一个实施例中,所述时钟信号输入端包括第一时钟信号输入端和第二时钟信号输入端,第n级所述驱动单元中的所述第一移位寄存器与所述第一时钟信号输入端电连接,第n+1级所述驱动单元中的所述第一移位寄存器与所述第二时钟信号输入端电连接;所述第一时钟信号输入端和所述第二时钟信号输入端输入的信号相差二分之一个周期;

48、所述时钟信号输入端包括第三时钟信号输入端和第四时钟信号输入端,第n级所述驱动单元中的所述第二移位寄存器与所述第三时钟信号输入端电连接,第n+1级所述驱动单元中的所述第二移位寄存器与所述第四时钟信号输入端电连接;所述第三时钟信号输入端和所述第四时钟信号输入端输入的信号相差二分之一个周期。

49、在本技术的至少一个实施例中,所述第一时钟信号输入端和所述第三时钟信号输入端输入的信号相差四分之一周期,所述第二时钟信号输入端和所述第四时钟信号输入端输入的信号相差四分之一周期。

50、本技术的实施例提供了一种驱动电路及其驱动方法、电子纸,该驱动电路包括级联设置的多个驱动单元,所述驱动单元与至少一条栅线电连接,所述驱动单元包括第一移位寄存器和第二移位寄存器,至少一条所述栅线分别与所述第一移位寄存器和所述第二移位寄存器电连接;所述第一移位寄存器被配置为向所述栅线输入第一栅极信号,所述第二移位寄存器被配置为向所述栅线输入第二栅极信号,所述第一栅极信号和所述第二栅极信号被配置为分时输入;所述第一栅极信号和所述第二栅极信号中的一个被配置为控制电子纸初始化,另一个被配置为控制所述电子纸显示。

51、本技术的实施例提供的驱动电路,通过设置一个驱动单元包括第一移位寄存器和第二移位寄存器,使得不同时刻输出的第一栅极信号和第二栅极信号传递到相同的栅线上;这样,在该驱动电路应用在电子纸上时,第一栅极信号和第二栅极信号分别用于控制电子纸的初始化和显示,实现电子纸的正常驱动;另外,采用该驱动电路替代电子纸上的栅极驱动芯片,能够降低电子纸的成本,还有利于窄边框电子纸的制备。

52、上述说明仅是本技术技术方案的概述,为了能够更清楚了解本技术的技术手段,而可依照说明书的内容予以实施,并且为了让本技术的上述和其它目的、特征和优点能够更明显易懂,以下特举本技术的具体实施方式。

- 还没有人留言评论。精彩留言会获得点赞!