像素电路及其驱动方法、以及显示面板与流程

本申请涉及显示,特别是涉及一种像素电路及其驱动方法、以及显示面板。

背景技术:

1、现有像素电路,在数据写入驱动晶体管栅极的阶段,同步完成对驱动晶体管的阈值补偿,当驱动晶体管的控制极电位达到data+vth(数据信号电压和阈值电压之和)时,才能完成补偿过程。由于该补偿时间较长,当需要提高显示屏刷新率时,由于数据扫描脉冲宽度大大减小减小,将导致阈值补偿不充分;而若保证补偿充分,则不能够满足高刷新率要求。因此,存在阈值补偿效果与刷新率提高之间的冲突,最终影响显示效果。

技术实现思路

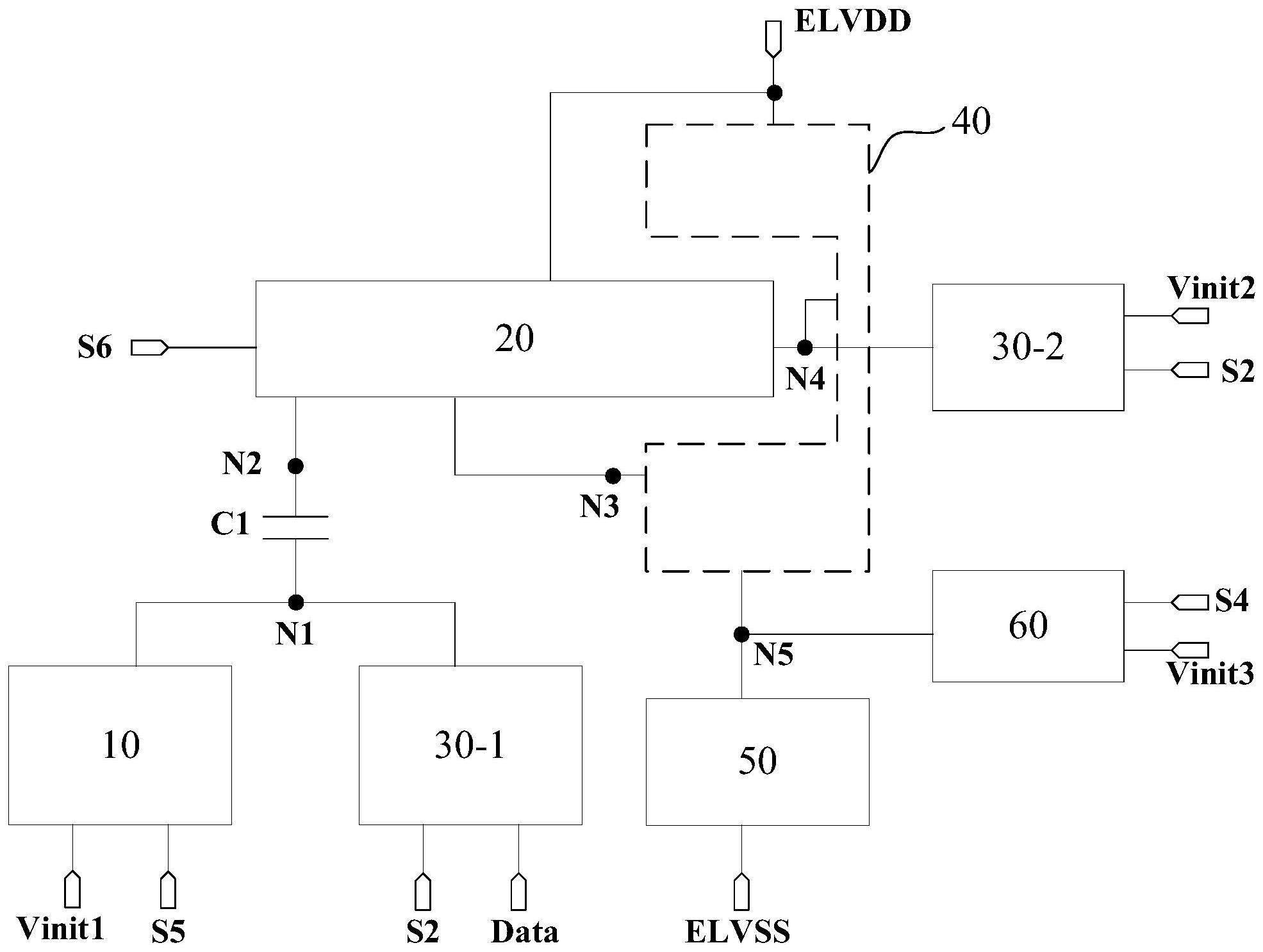

1、为了解决上述问题至少之一,本申请第一个方面提供一种像素电路,包括:第一初始化单元、驱动控制单元、写入单元、复用单元、第一存储电容、发光单元,其中

2、第一初始化单元,电连接至第一节点、第一初始化信号端、第一初始化控制端,配置为基于第一初始化控制端接入的信号初始化第一节点的电位,

3、驱动控制单元,电连接至驱动控制端、第二节点、第三节点、第四节点、以及第一电源信号端,配置为响应于驱动控制端的信号产生驱动电流;

4、第一存储电容,电连接至第一节点和第二节点;

5、写入单元,包括第一写入单元和第二写入单元,第一写入单元电连接至数据信号端、写入控制端、以及第一节点,第二写入单元电连接至第四节点、写入控制端、以及置位信号端,配置为基于写入控制端的控制,将数据信号端的信号写入第一节点,并将置位信号端的电位写入第四节点;

6、复用单元,电连接至第一电源信号端、第一复用控制端、第二复用控制端、第四节点、第三节点、以及第五节点,配置为基于第一复用控制端的控制在补偿阶段将第一电源信号端的电位写入第四节点,基于第二复用控制端的控制在初始化阶段将第五节点的电位写入第三节点,并基于第一复用控制端和第二复用控制端的控制在发光阶段将驱动电流传输至第五节点,以驱动发光单元发光。

7、在一些可选的实施例中,第一写入单元包括:第一晶体管,第二写入单元包括:第二晶体管,其中,

8、第一晶体管的第一极电连接至数据信号端,第二极电连接至第一节点,控制极电连接至所述写入控制端;

9、第二晶体管的第一极电连接至置位信号端,第二极电连接至第四节点,控制极电连接至写入控制端。

10、在一些可选的实施例中,像素电路还包括:第二初始化单元,电连接至第五节点、第二初始化信号端、第二初始化控制端,配置为基于第二初始化控制端接入的信号初始化第五节点的电位。

11、在一些可选的实施例中,复用单元包括:第三晶体管和第四晶体管,其中,

12、第三晶体管的第一极电连接至第一电源信号端,第二极电连接至第四节点,控制极电连接至第一复用控制端;

13、第四晶体管的第一极电连接至第三节点,第二极电连接至第五节点,控制极电连接至第二复用控制端。

14、在一些可选的实施例中,驱动控制单元包括:第五晶体管、第六晶体管和第二存储电容,其中,

15、第五晶体管的第一极电连接至第四节点,第二极电连接至第三节点,控制极电连接至所述第二节点;

16、第六晶体管的第一极电连接至第三节点,第二极电连接至第二节点,控制极电连接至驱动控制端;

17、第二存储电容的第一端电连接至第一电源信号端,第二端电连接至第二节点。

18、在一些可选的实施例中,第一初始化单元包括:第七晶体管,其中,

19、第七晶体管的第一极电连接至第一初始化信号端,第二极电连接至第一节点,控制极电连接至第一初始化控制端。

20、在一些可选的实施例中,第二初始化单元包括:第八晶体管,其中,

21、第八晶体管的第一极电连接至第二初始化信号端,第二极电连接至第五节点,控制极电连接第二初始化控制端。

22、本申请第二个方面提供一种显示面板,包括上文所述的像素电路。

23、本申请第二个方面提供一种应用于上文所述的像素电路的驱动方法,包括:

24、初始化阶段:第一初始化单元响应于第一初始化控制端接入的信号利用初始化信号端的电位对第一节点进行初始化,复用单元响应于第二复用控制端接入的信号将第五节点的电位写入第三节点,以对第二节点进行初始化;

25、补偿阶段:复用单元响应于第一复用控制端接入的信号将第一电源信号端的电位写入第四节点,驱动控制单元响应于驱动控制端接入的信号,利用第四节点的电位补偿第二节点的电压;

26、写入阶段:响应于写入控制端接入的信号,将数据信号端的信号写入所述第一节点,并将置位信号端的信号写入第四节点;以及

27、发光阶段:复用单元响应于第一复用控制端和第二复用控制端接入的信号将形成的驱动电流传输至发光单元以驱动发光单元发光。

28、在一些可选的实施例中,像素电路还包括第二初始化单元,配置为基于第二初始化控制端接入的信号初始化第五节点的电位,其中,

29、在初始化阶段,第二初始化控制端接入的信号早于第一初始化控制端接入的信号变为有效电平;

30、在写入阶段,第二初始化控制端接入的信号变为无效电平的时刻早于第二复用控制端接入的信号变为有效电平的时刻。

31、本申请的有益效果如下:

32、本申请针对目前现有的问题,制定一种像素电路及其驱动方法、以及显示面板,通过提供设置在第一节点和第二节点间的第一存储电容,包括第一写入单元和第二写入单元的写入单元、以及复用单元,从而能够将数据写入与补偿阶段分离开,利用第一写入单元写入数据信号,并利用复用单元在补偿阶段配合输入补偿电压,实现分阶段阈值补偿和数据写入,从而既能够充分补偿驱动晶体管的阈值电压,也能够满足高刷新率要求,提高显示效果,具有广阔的应用前景。

技术特征:

1.一种像素电路,其特征在于,包括:第一初始化单元、驱动控制单元、写入单元、复用单元、第一存储电容、发光单元,其中

2.根据权利要求1所述的像素电路,其特征在于,所述第一写入单元包括:第一晶体管,所述第二写入单元包括:第二晶体管,其中,

3.根据权利要求1所述的像素电路,其特征在于,还包括:第二初始化单元,电连接至所述第五节点、第二初始化信号端、第二初始化控制端,配置为基于所述第二初始化控制端接入的信号初始化所述第五节点的电位。

4.根据权利要求1所述的像素电路,其特征在于,所述复用单元包括:第三晶体管和第四晶体管,其中,

5.根据权利要求1所述的像素电路,其特征在于,所述驱动控制单元包括:第五晶体管、第六晶体管和第二存储电容,其中,

6.根据权利要求1所述的像素电路,其特征在于,所述第一初始化单元包括:第七晶体管,其中,

7.根据权利要求3所述的像素电路,其特征在于,所述第二初始化单元包括:第八晶体管,其中,

8.一种显示面板,其特征在于,包括如权利要求1-7中任一项所述的像素电路。

9.一种应用于权利要求1-7中任一项所述的像素电路的驱动方法,其特征在于,包括:

10.根据权利要求9所述的驱动方法,其特征在于,所述像素电路还包括第二初始化单元,配置为基于第二初始化控制端接入的信号初始化第五节点的电位,其中,

技术总结

本申请公开了一种像素电路及其驱动方法、以及显示面板,本申请实施例的像素电路包括:第一初始化单元、写入单元、复用单元、第一存储电容,其中第一存储电容,电连接至第一节点和第二节点;写入单元,基于写入控制端的控制将数据信号端的信号写入第一节点,并将置位信号端的电位写入第四节点;复用单元,基于第一复用控制端的控制在补偿阶段将第一电源信号端的电位写入第四节点,基于第二复用控制端的控制在初始化阶段将第五节点的电位写入第三节点,基于第一复用控制端和第二复用控制端的控制在发光阶段将驱动电流传输至第五节点,以驱动发光单元发光。本申请实施例的像素电路能够分时段进行阈值补偿和数据写入,改善补偿时间和高刷新率的冲突。

技术研发人员:方飞,王铸,石领,刘畅畅,吴俣,汤彩艳

受保护的技术使用者:京东方科技集团股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!