像素电路及其控制方法、半导体结构及显示装置与流程

本申请涉及集成电路,特别是涉及一种像素电路及其控制方法、半导体结构及显示装置。

背景技术:

1、硅基微显示器是一种基于硅半导体技术的显示器,其通常包括驱动电路和发光器件,针对微发光二极管显示器(micro light emitting diode display,简称micro led)或者迷你发光二极管显示器(mini light emitting diode display,简称mini led)的显示驱动,常用数字子场扫描法,即一帧(1h)显示数据包括多个子帧,每个子帧的加权值大小不同,一帧显示数据为每个子帧的灰阶叠加,从而实现256灰阶显示。因此,数字驱动为了实现256级灰阶,每个像素至少需要存储8位二进制数据。

2、然而,相关技术中当视频源数据输入进来后,需要将其按照一定的方式处理然后再将数据传输给存储模块,其中,帧缓存用于存储图像数据,其数据流处理起来比较繁琐,数据读出并写入花费的功耗较高。另外,帧缓存电路需要占据一定的面积而使得显示屏的边框较大。因此,如何在简化数据流处理、减小功耗的同时,减小微显示设备的模组整体尺寸,是亟需解决的问题。

技术实现思路

1、基于此,有必要针对上述背景技术中的问题,提供一种像素电路及其控制方法、半导体结构及显示装置,以提高像素电路中图像数据的存储效率、减小数据处理的功耗并缩小显示模组的尺寸,进而提高显示装置的集成度。

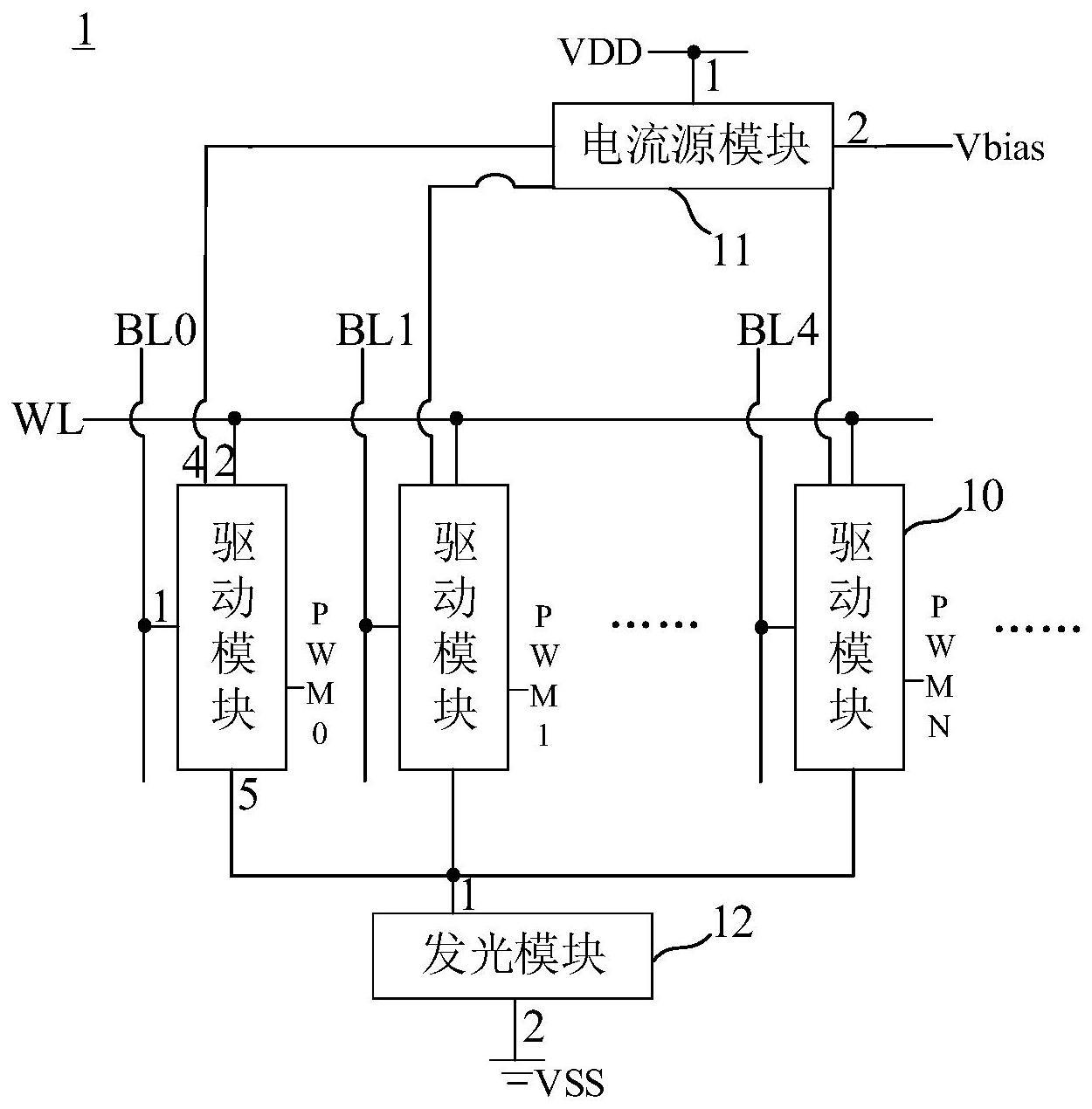

2、为实现上述目的及其他相关目的,本申请的一方面提供一种像素电路,其包括若干个驱动模块以及发光模块。其中,驱动模块被配置为:第一端与位线连接,第二端与字线连接,第四端与电流源模块连接,控制端与脉宽调制端连接;发光模块被配置为:第一端与驱动模块的第五端连接,第二端为接地端;其中,驱动模块用于写入、读取及存储视频源数据,以驱动发光模块发光。

3、于上述实施例中的像素电路中,像素电路包括若干个驱动模块以及发光模块,驱动模块用于写入、读取及存储视频源数据,以驱动发光模块发光,从而使得显示外围电路中不再需要用于存储图像数据的帧缓存模块,采用占用空间较小的行缓存模块即可,以缩小显示区外围电路面积,实现更窄的显示边框,进而减小芯片体积及重量。由于驱动模块能够同时写入、读取及存储视频源数据,无需将数据存储在外围电路中,简化了数据流,无需经过帧缓存的数据写入读出处理,还能够达到节省功耗的效果。另外,本申请提供的像素电路能够大幅度降低像素面积,在晶圆厂工艺节点先进度较低的基础上就能够实现较高的像素密度(pixels per inch,简称ppi)。

4、在其中一些实施例中,驱动模块包括存储单元、开关单元及驱动控制单元。其中,存储单元被配置为:第一端作为驱动模块的第一端,第二端作为驱动模块的第二端;开关单元被配置为:第一端与存储单元的第四端连接,第二端作为存储模块的第四端;驱动控制单元被配置为:第一端与开关单元的第三端连接,控制端作为驱动模块的控制端,第二端作为若干个驱动模块的第五端。

5、在其中一些实施例中,存储单元包括一个薄膜晶体管和一个电容,或一个薄膜晶体管;薄膜晶体管被配置为:第一端作为存储单元的第一端,第二端作为存储单元的第二端;电容被配置为:第一端与薄膜晶体管的第三端连接,第二端作为存储单元的第三端。

6、在其中一些实施例中,驱动控制单元包括一个金属氧化物半导体场效应晶体管。

7、在其中一些实施例中,开关单元包括一个金属氧化物半导体场效应晶体管。

8、在其中一些实施例中,发光模块包括一个发光二极管。

9、在其中一些实施例中,一个发光模块与多个驱动模块的第五端连接,其中,驱动模块的第五端为多个驱动模块的共同端。

10、在其中一些实施例中,薄膜晶体管为铟镓锌氧化物薄膜晶体管。

11、本申请的另一方面还提供一种半导体结构,其包括本申请实施例中任一项所述的像素电路。

12、于上述实施例中的半导体结构中,由于采用了本申请实施例中任一项所述的像素电路,从而能够节省显示外围电路中用于存储图像数据的帧缓存模块,将存储数据的功能放进像素电路中的驱动模块中,以缩小显示区外围电路面积,减小芯片体积及重量;另外,由于驱动模块能够同时写入、读取及存储视频源数据,无需将数据存储在外围电路中,还能够简化数据流的处理过程,以节省功耗并提高像素密度。

13、在其中一些实施例中,存储单元设置于开关单元与发光模块之间,以及驱动控制单元与发光模块之间。

14、在其中一些实施例中,存储单元与开关单元、驱动控制单元之间采用导电插塞键合。

15、在其中一些实施例中,发光模块与存储单元、开关单元、驱动控制单元之间采用导电插塞键合。

16、本申请的又一方面还提供一种显示装置,其包括:壳体;以及如本申请实施例中任一项所述的半导体结构,半导体结构与壳体连接并设置于壳体的内部。

17、于上述实施例中的显示装置中,包括本申请实施例中任一项所述的半导体结构,由于半导体结构中采用了本申请实施例中任一项所述的像素电路,从而能够节省显示外围电路中用于存储图像数据的帧缓存模块,缩小显示区外围电路面积,提高芯片集成度,还能够节省数据流处理的功耗并提高像素密度,从而提高显示装置的整体性能。

18、本申请的再一方面还提供一种像素电路控制方法,其用于控制本申请实施例中任一项所述的像素电路,其中,像素电路包括若干个驱动模块及发光模块;方法包括:控制驱动模块按照预设时钟周期进行逐行扫描,当第n行的字线开启时,第n行对应的像素电路的(m+1)位将第一数据写入并存储至驱动模块中,第一数据控制驱动模块的开关状态;控制各脉宽调制端依次开启对应的驱动模块,且脉宽调制端的开启时长按顺序依次变化;其中,字线的开启时长、各脉宽调制端的开启时长及一段消失时长之和,为像素电路中一帧的时长。

19、于上述实施例中的像素电路控制方法中,通过将第一数据写入并存储至驱动模块中,并控制各脉宽调制端依次开启对应的驱动模块,从而使得显示外围电路中不再需要用于存储图像数据的帧缓存模块,采用占用空间较小的行缓存模块即可,以缩小显示区外围电路面积,实现更窄的显示边框,进而减小芯片体积及重量;另外,还能够简化数据流,无需经过帧缓存的数据写入读出处理,以节省功耗。

技术特征:

1.一种像素电路,其特征在于,包括:

2.根据权利要求1所述的像素电路,其特征在于,所述驱动模块包括:

3.根据权利要求2所述的像素电路,其特征在于,所述存储单元包括一个薄膜晶体管和一个电容,或一个薄膜晶体管;

4.根据权利要求3所述的像素电路,其特征在于,包括如下特征中至少一个:

5.根据权利要求1-3任一项所述的像素电路,其特征在于,

6.一种半导体结构,其特征在于,包括权利要求1-5任一项所述的像素电路。

7.根据权利要求6所述的半导体结构,其特征在于,存储单元设置于开关单元与所述发光模块之间,以及驱动控制单元与所述发光模块之间。

8.根据权利要求7所述的半导体结构,其特征在于,所述存储单元与所述开关单元、所述驱动控制单元之间采用导电插塞键合;及/或

9.一种显示装置,其特征在于,包括:

10.一种像素电路控制方法,其特征在于,用于控制权利要求1-5任一项所述的像素电路,其中,所述像素电路包括若干个驱动模块及发光模块;所述方法包括:

技术总结

本申请涉及一种像素电路及其控制方法、半导体结构及显示装置,像素电路包括若干个驱动模块以及发光模块。其中,驱动模块被配置为:第一端与位线连接,第二端与字线连接,第四端与电流源模块连接,控制端与脉宽调制端连接;发光模块被配置为:第一端与驱动模块的第五端连接,第二端为接地端;其中,驱动模块用于写入、读取及存储视频源数据,以驱动发光模块发光。上述电路能够达到缩小显示区外围电路面积、减小边框尺寸、简化数据流及节省功耗的效果;另外,本申请提供的像素电路及结构还能够实现较高的像素密度。

技术研发人员:秦颖,何彩云

受保护的技术使用者:上海世美爱科技合伙企业(有限合伙)

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!