像素驱动电路及其驱动方法和显示设备与流程

本技术涉及显示设备,尤其涉及一种像素驱动电路及其驱动方法和显示设备。

背景技术:

1、lcd显示行业中,drd(double rate driving,双速率驱动)设计目前受到越来越多的应用,因为其可以节省覆晶薄膜(chip on film,cof)数量,降低成本。比如采用dualgate(双栅极)像素架构,每两列子像素共用一个数据线,每一行像素对应两个栅极,相比sigal-gate(单栅极)像素架构,数据线数量和cof数量减半,栅极数量和goa级数加倍。然而,如图1所示dual gate像素架构中,同时驱动两行扫描线时,同一数据线上对应要么同时连通两个不同颜色的子像素,要么没有连通子像素。而事实上在驱动时,同一数据线只能输出同一颜色像素数据,而无法同时输出两个不同颜色的像素数据,也就是说,图1所示的dual gate像素架构并不能应用于dlg(倍频刷新技术)驱动的场景。

技术实现思路

1、本技术实施例的主要目的在于提出一种像素驱动电路及其驱动方法和显示设备。旨在提供一种新型dual gate像素架构,存在同时驱动两行时,同一数据线上可同时连通两个相同颜色的子像素的情况,可应用于dlg驱动的场景。

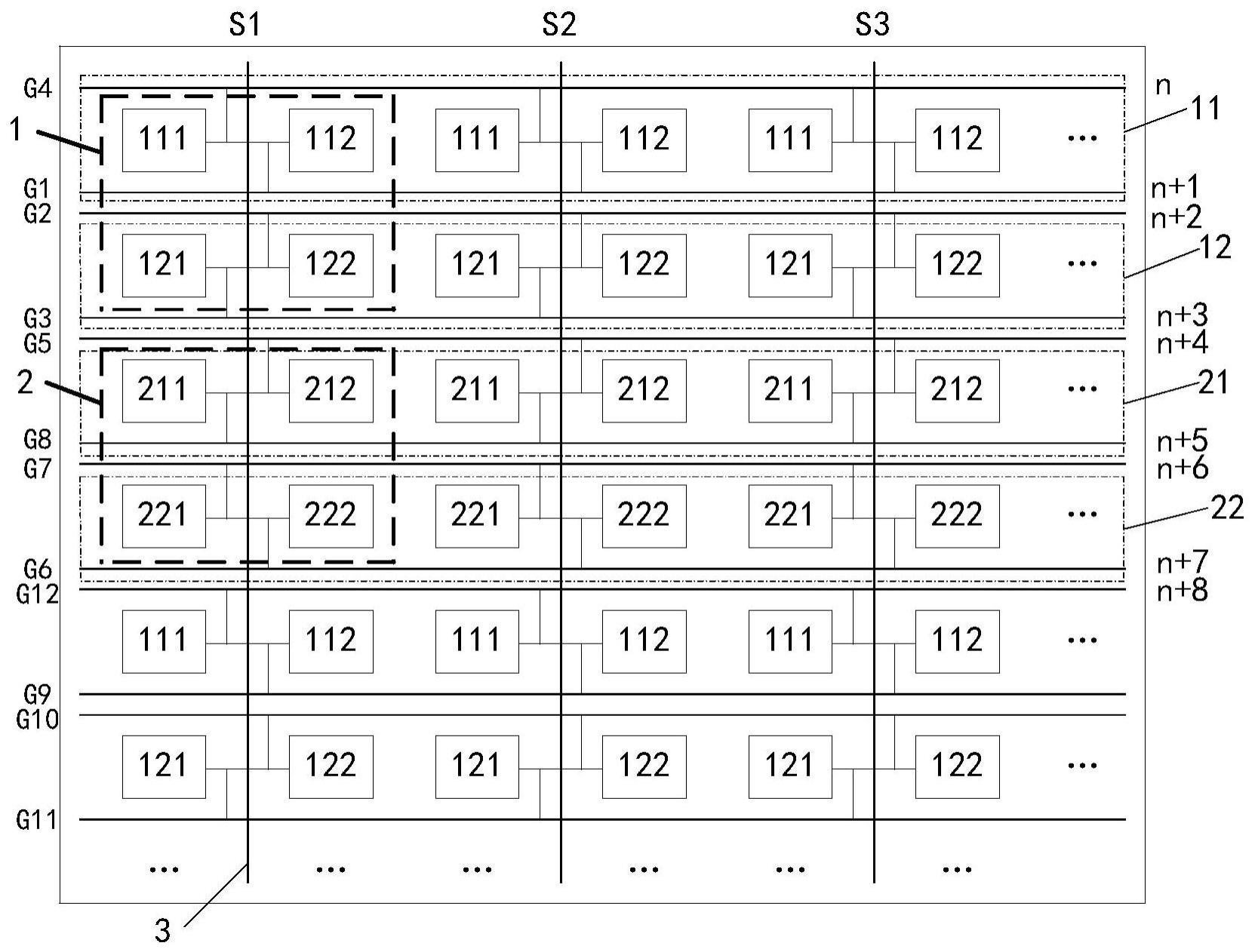

2、为实现上述目的,本技术实施例的第一方面提出了一种像素驱动电路,包括沿列方向上交替排布的第一像素组和第二像素组,所述第一像素组和所述第二像素组均连接同一共享数据线;

3、所述第一像素组包括列向相邻设置的第一行向阵列与第二行向阵列,所述第一行向阵列包括行向间隔设置的第一子像素与第二子像素,所述第二行向阵列包括行向间隔设置的第三子像素与第四子像素,所述第一子像素连接第n行扫描线,所述第二子像素连接第n+1行扫描线,所述第三子像素连接第n+3行扫描线,所述第四子像素连接第n+2行扫描线;

4、所述第二像素组包括列向相邻设置的第三行向阵列与第四行向阵列,所述第三行向阵列包括行向间隔设置的第五子像素与第六子像素,所述第四行向阵列包括行向间隔设置的第七子像素与第八子像素,所述第五子像素连接第n+5行扫描线,所述第六子像素连接第n+4行扫描线,所述第七子像素连接第n+6行扫描线,所述第八子像素连接第n+7行扫描线,n为大于等于1的自然数;

5、所述第一子像素、所述第三子像素、所述第五子像素、第七子像素沿列向依次排列形成第一列向阵列,所述第二子像素、所述第四子像素、所述第六子像素、第八子像素沿列向依次排列形成第二列向阵列,所述共享数据线与各所述扫描线交叉配置,所述共享数据线穿过所述第一列向阵列与所述第二列向阵列之间的位置,并且与所述第一列向阵列及所述第二列向阵列上的各个子像素均连接;

6、同一列向阵列中的各子像素的颜色相同。

7、在本技术的一个实施例中,所述第一行向阵列包含有交替设置的多个所述第一子像素与多个所述第二子像素,所述第二行向阵列包含有交替设置的多个所述第三子像素与多个所述第四子像素,所述第三行向阵列包含有交替设置的多个所述第五子像素与多个所述第六子像素,所述第四行向阵列包含有交替设置的多个所述第七子像素与多个所述第八子像素,所述像素驱动电路中相应形成沿行向交替排列的多个所述第一列向阵列与多个所述第二列向阵列,所述像素驱动电路中设置有行向间隔设置的多个所述共享数据线,所述共享数据线穿过相应的所述第一列向阵列与所述第二列向阵列之间的位置。

8、在本技术的一个实施例中,各所述行向阵列中的任意相邻两个子像素的颜色不同。

9、在本技术的一个实施例中,所述像素驱动电路被配置为以第一预设周期进行驱动,所述预设周期为依次同时驱动第n+1行扫描线、第n+2行扫描线,第n+3行扫描线和第n行扫描线,第n+4行扫描线和第n+7行扫描线,第n+6行扫描线和第n+5行扫描线。

10、本技术实施例的第二方面提出了一种驱动方法,用于驱动本技术任一实施例所述的像素驱动电路,所述驱动方法包括:

11、按照第一预设周期向扫描线提供扫描脉冲,所述第一预设周期为依次同时驱动第n+1行扫描线和第n+2行扫描线,第n+3行扫描线和第n行扫描线,第n+4行扫描线和第n+7行扫描线,第n+6行扫描线和第n+5行扫描线;

12、根据各个所述子像素与扫描线和共享数据线的连接关系,确定通过所述共享数据线施加于各个所述子像素的像素电压;

13、与所述扫描脉冲同步地施加所述像素电压至所述共享数据线,以驱动各个所述子像素。

14、在本技术的一个实施例中,在确定所述第一预设周期之后,所述方法包括:

15、根据所述第一预设周期确定的驱动顺序,生成相应的驱动时序信号;

16、根据所述驱动时序信号向扫描线提供扫描脉冲。

17、本技术实施例的第三方面提出了一种驱动方法,用于驱动本技术任一实施例所述的像素驱动电路,所述驱动方法包括:

18、按照第二预设周期向扫描线提供扫描脉冲,所述第二预设周期为依次逐行驱动第n+1行扫描线、第n+2行扫描线、第n+3行扫描线、第n行扫描线、第n+4行扫描线、第n+7行扫描线、第n+6行扫描线和第n+5行扫描线;

19、根据各个所述子像素与扫描线和共享数据线的连接关系,确定通过所述共享数据线施加于各个所述子像素的像素电压;

20、根据两行极性反转设定,确定施加于各个所述子像素的所述像素电压的极性;

21、与所述扫描脉冲同步地施加带有极性的像素电压至所述共享数据线,以驱动各个所述子像素。

22、在本技术的一个实施例中,驱动各个所述子像素包括驱动所述第一像素组,驱动所述第一像素组包括按顺序执行以下步骤:

23、向所述第n+1行扫描线提供扫描脉冲,并将具有第一极性的第二像素电压通过所述共享数据线施加至所述第二子像素;

24、向所述第n+2行扫描线提供扫描脉冲,并将具有所述第一极性的第四像素电压通过所述共享数据线施加至所述第四子像素;

25、向所述第n+3行扫描线提供扫描脉冲,并将具有第二极性的第三像素电压通过所述共享数据线施加至所述第三子像素,所述第一极性和所述第二极性为相反极性;

26、向所述第n行扫描线提供扫描脉冲,并将具有所述第二极性的第一像素电压通过所述共享数据线施加至所述第一子像素。

27、在本技术的一个实施例中,驱动各个所述子像素包括驱动所述第二像素组,驱动所述第二像素组包括按顺序执行以下步骤:

28、向所述第n+4行扫描线提供扫描脉冲,并将具有第二极性的第六像素电压通过所述共享数据线施加至所述第六子像素;

29、向所述第n+7行扫描线提供扫描脉冲,并将具有所述第二极性的第八像素电压通过所述共享数据线施加至所述第八子像素;

30、向所述第n+6行扫描线提供扫描脉冲,并将具有第一极性的第七像素电压通过所述共享数据线施加至所述第七子像素,所述第二极性和所述第一极性为相反极性;

31、向所述第n+5行扫描线提供扫描脉冲,并将具有所述第一极性的第五像素电压通过所述共享数据线施加至所述第五子像素。

32、本技术实施例的第四方面提出了一种显示设备,包括:

33、显示面板,所述显示面板包括本技术任一实施例所述的像素驱动电路;

34、时序控制模块,与所述显示面板连接,用于执行本技术任一实施例所述的驱动方法,以驱动所述像素驱动电路。

35、在本技术实施例提供的技术方案中,像素驱动电路包括沿列方向上交替排布的第一像素组和第二像素组,第一像素组和第二像素组均连接同一共享数据线。通过第一像素组和第二像素组的设置排布,构建出一种新型dual gate像素架构,该新型dual gate像素架构存在同时驱动两行时,同一数据线上可同时连通两个相同颜色的子像素的情况,可应用于dlg驱动的场景。

- 还没有人留言评论。精彩留言会获得点赞!