时序控制部、显示装置及其驱动方法与流程

本发明涉及时序控制部、显示装置及其驱动方法。

背景技术:

1、随着信息化技术的发展,作为使用者与信息间的连接媒介的显示装置其重要性日益显著。对应于此,如液晶显示装置(liquid crystal display device)、有机发光显示装置(organic light emitting display device)等这样的显示装置的使用正在增加。

2、对于显示装置所包括的cdr(clock and data recovery,时钟与数据恢复)电路,需要周期性地发送时钟训练图案来周期性地复原时钟信号的频率和相位。

3、此时,在提供规则且反复图案的时钟训练图案的情况下,可能会导致isi(inter-symbol interference,码间串扰)跳动、噪声集中现象等不期望的结果。

技术实现思路

1、想要解决的技术课题在于,提供可以发送各种时钟训练图案来应对isi跳动、噪声集中现象等的时序控制部、显示装置及其驱动方法。

2、想要解决的技术课题在于,提供可以事先提供对于各种时钟训练图案的设定信息来减少时钟信号的锁止时间(locking time)的时序控制部、显示装置及其驱动方法。

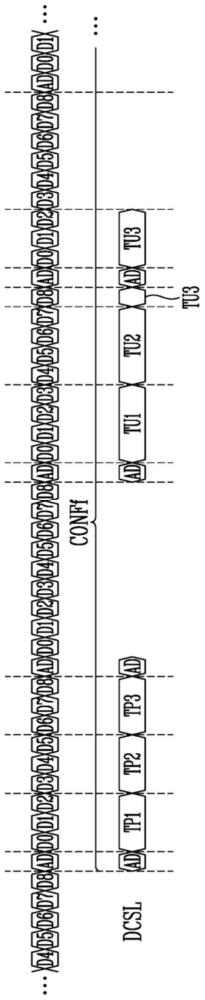

3、本发明的一实施例涉及的显示装置包括:像素,与数据线连接;数据驱动部,向所述数据线提供数据电压;以及时序控制部,通过时钟训练线和时钟数据线而与所述数据驱动部连接,所述时序控制部在向所述时钟训练线提供第一逻辑电平的时钟训练信号时向所述时钟数据线提供时钟训练图案,在向所述时钟训练线提供第二逻辑电平的所述时钟训练信号时向所述时钟数据线提供时钟数据信号而不是提供所述时钟训练图案,所述时序控制部在提供所述第二逻辑电平的所述时钟训练信号的期间内提供对于下一时钟训练图案的第一设定信号。

4、可以是,所述时钟训练图案包括多个子图案。

5、可以是,所述第一设定信号包括指代各个所述子图案的期间的子图案期间设定值(sub-pattern period setting values)。

6、可以是,所述第一设定信号还包括指代各个所述子图案的初始电平被维持的期间的初始电平期间设定值(initial-level period setting values)。

7、可以是,各个所述子图案包括至少两个单位数据,所述至少两个单位数据具有相同的时间长度,所述单位数据的初始位(initial bit)是逻辑电平不同于前一位的过渡位(transition bit)。

8、可以是,构成所述子图案的各个所述单位数据在第一期间内维持第三逻辑电平且在其余的第二期间内维持第四逻辑电平。

9、可以是,所述子图案期间设定值指代对应的子图案所包括的所述单位数据的数量。

10、可以是,所述初始电平期间设定值指代对应的子图案的第一个单位数据的所述第三逻辑电平被维持的期间。

11、可以是,所述第一设定信号指代后续的数据为帧数据。

12、可以是,所述时序控制部在提供所述第二逻辑电平的所述时钟训练信号的期间内还提供第二设定信号,所述第二设定信号指代后续的数据为像素数据或虚设数据。

13、本发明的一实施例涉及的显示装置的驱动方法是包括与数据线连接的像素、向所述数据线提供数据电压的数据驱动部以及通过时钟训练线和时钟数据线而与所述数据驱动部连接的时序控制部的显示装置的驱动方法,包括:在所述时序控制部向所述时钟训练线提供第一逻辑电平的时钟训练信号时向所述时钟数据线提供时钟训练图案的步骤;以及在所述时序控制部向所述时钟训练线提供第二逻辑电平的所述时钟训练信号时向所述时钟数据线提供时钟数据信号而不是提供所述时钟训练图案的步骤,所述时序控制部在提供所述第二逻辑电平的所述时钟训练信号的期间内提供对于下一时钟训练图案的第一设定信号。

14、可以是,所述时钟训练图案包括多个子图案。

15、可以是,所述第一设定信号包括指代各个所述子图案的期间的子图案期间设定值。

16、可以是,所述第一设定信号还包括指代各个所述子图案的初始电平被维持的期间的初始电平期间设定值。

17、可以是,各个所述子图案包括至少两个单位数据,所述至少两个单位数据具有相同的时间长度,所述单位数据的初始位是逻辑电平不同于前一位的过渡位。

18、可以是,构成所述子图案的各个所述单位数据在第一期间内维持第三逻辑电平且在其余的第二期间内维持第四逻辑电平。

19、可以是,所述子图案期间设定值指代对应的子图案所包括的所述单位数据的数量。

20、可以是,所述初始电平期间设定值指代对应的子图案的第一个单位数据的所述第三逻辑电平被维持的期间。

21、可以是,所述第一设定信号指代后续的数据为帧数据。

22、可以是,所述时序控制部在提供所述第二逻辑电平的所述时钟训练信号的期间内还提供第二设定信号,所述第二设定信号指代后续的数据为像素数据或虚设数据。

23、本发明的一实施例涉及的时序控制部是包括能够与外部连接的第一端子和第二端子的时序控制部,所述时序控制部在向所述第一端子提供第一逻辑电平的时钟训练信号时向所述第二端子提供时钟训练图案,在向所述第一端子提供第二逻辑电平的所述时钟训练信号时向所述第二端子提供时钟数据信号而不是提供所述时钟训练图案,所述时序控制部在提供所述第二逻辑电平的所述时钟训练信号的期间内提供对于下一时钟训练图案的第一设定信号。

24、可以是,所述时钟训练图案包括多个子图案。

25、可以是,所述第一设定信号包括指代各个所述子图案的期间的子图案期间设定值。

26、可以是,所述第一设定信号还包括指代各个所述子图案的初始电平被维持的期间的初始电平期间设定值。

27、可以是,各个所述子图案包括至少两个单位数据,所述至少两个单位数据具有相同的时间长度,所述单位数据的初始位是逻辑电平不同于前一位的过渡位。

28、可以是,构成所述子图案的各个所述单位数据在第一期间内维持第三逻辑电平且在其余的第二期间内维持第四逻辑电平。

29、可以是,所述子图案期间设定值指代对应的子图案所包括的所述单位数据的数量。

30、可以是,所述初始电平期间设定值指代对应的子图案的第一个单位数据的所述第三逻辑电平被维持的期间。

31、可以是,所述第一设定信号指代后续的数据为帧数据。

32、可以是,所述时序控制部在提供所述第二逻辑电平的所述时钟训练信号的期间内还提供第二设定信号,所述第二设定信号指代后续的数据为像素数据或虚设数据。

33、(发明效果)

34、本发明涉及的时序控制部、显示装置及其驱动方法发送各种时钟训练图案,从而可以应对isi跳动、噪声集中现象等。

35、此外,本发明涉及的时序控制部、显示装置及其驱动方法事先提供对于各种时钟训练图案的设定信息,从而可以减少时钟信号的锁止时间。

- 还没有人留言评论。精彩留言会获得点赞!