栅极驱动电路及显示装置的制作方法

本公开属于显示,具体涉及一种栅极驱动电路及显示装置。

背景技术:

1、随着显示技术的不断发展,近些年的显示器发展逐渐呈现出了高集成度,低成本的发展趋势。其中一项非常重要的技术就是goa(gate driver on array,阵列基板行驱动)技术的量产化的实现。利用goa技术将tft(thin film transistor,薄膜场效应晶体管)栅极开关电路集成在显示面板的阵列基板上以形成对显示面板的扫描驱动,从而可以省掉栅极驱动集成电路部分,其不仅可以从材料成本和制作工艺两方面降低产品成本,而且显示面板可以做到两边对称和窄边框的美观设计。同时由于可以省去gate方向绑定bonding的工艺,对产能和良率提升也较有利。这种利用goa技术集成在阵列基板上的栅极开关电路也称为goa电路或移位寄存器电路。

技术实现思路

1、本发明旨在至少解决现有技术中存在的技术问题之一,提供一种栅极驱动电路及显示装置。

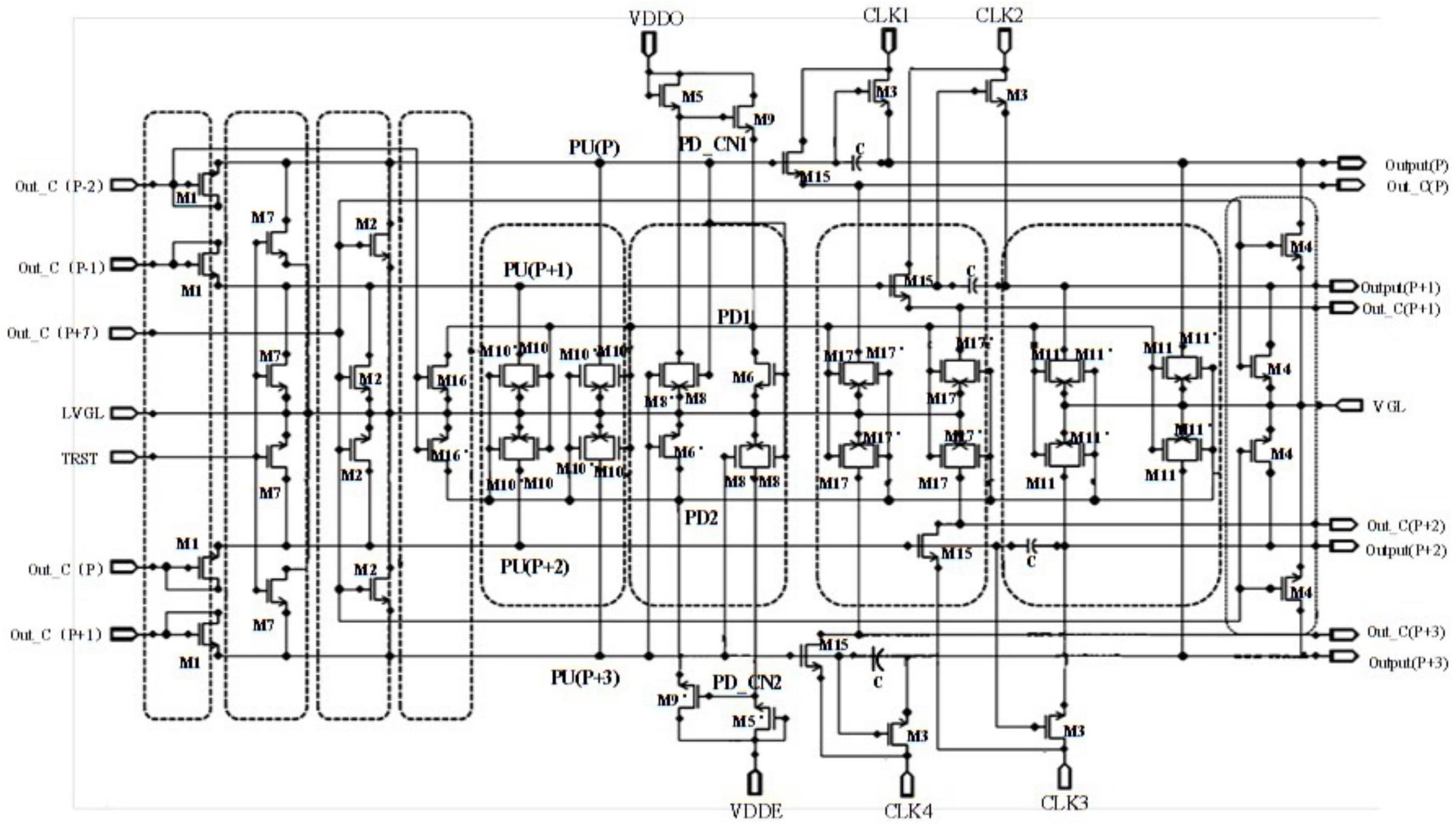

2、本公开实施例提供一种栅极驱动电路,其包括多个级联的移位寄存器和两组时钟信号线,每组时钟信号线包括2n条时钟信号线;所述多个级联的移位寄存器划分为多组移位寄存器,每组移位寄存器包括2n个移位寄存器;位于奇数组的移位寄存器连接同一组时钟信号线,位于偶数组的移位寄存器连接同一组时钟信号线,且位于奇数组和偶数组的移位寄存器连接不同组的时钟信号线;n为大于或者等于1的整数;其中,所述移位寄存器至少包括输入子电路、输出子电路、至少一个下拉控制子电路、至少一个下拉子电路;

3、所述输入子电路,被配置为响应于信号输入端的输入信号,通过所述输入信号对上拉节点进行预充电;所述输入子电路、所述输出子电路和所述下拉子电路之间的连接节点;

4、所述输出子电路,被配置为响应于所述上拉节点的电位,将时钟信号通过信号输出端进行输出;

5、所述下拉控制子电路,被配置响应于电源电压,并通过电源电压控制下拉节点的电位;一个所述下拉控制子电路连接一个所述下拉子电路和一个所述下拉子电路,且二者之间的连接节点为所述下拉节点;

6、所述下拉子电路,被配置为响应于所述上拉节点的电位,通过非工作电平信号下拉所述下拉节点的电位;其中,

7、每组所述移位寄存器中的所述下拉控制子电路共用,所述下拉子电路共用。

8、其中,所述移位寄存器还包括:第一复位子电路和第二复位子电路;

9、所述第一复位子电路,被配置响应于复位信号,通过所述非工作电平信号对所述上拉节点进行复位;

10、所述第二复位子电路,被配置响应于所述复位信号,通过所述非工作电平信号对所述信号输出端的输出进行复位。

11、其中,对于一个所述移位寄存器,所述第一复位子电路包括第二晶体管,所述第二复位子电路包括第四晶体管;

12、所述第二晶体管的第一极连接非工作电平信号端,第二极连接所述上拉节点,控制极连接复位信号端;

13、所述第四晶体管的第一极连接所述非工作电平信号端,第二极连接所述信号输出端,控制极连接所述复位信号端。

14、其中,对于位于同一组的所述移位寄存器,各所述第二晶体管的控制极和各所述第四晶体管的控制极连接同一所述复位信号端。

15、其中,所述移位寄存器还包括至少一个第一降噪子电路和至少一个第二降噪子电路;所述第一降噪子电路和第二降噪子电路均与所述下拉节点一一对应连接;

16、所述第一降噪子电路,被配置为响应于与之连接的所述下拉节点的电位,通过非工作电平信号对所述上拉节点的电位进行降噪;

17、所述第二降噪子电路,被配置为响应于与之连接的所述下拉节点的电位,通过非工作电平信号对所述信号输出端的输出进行降噪。

18、其中,对于一个所述移位寄存器,所述第一降噪子电路包括第十晶体管,所述第二降噪子电路包括第十一晶体管;

19、所述第十晶体管的第一极连接非工作电平信号端,第二极连接所述上拉节点,控制极连接所述下拉节点;

20、所述第十一晶体管的第一极连接非工作电平信号端,第二极连接所述信号输出端,控制极连接所述下拉节点。

21、其中,所述移位寄存器还包括放电子电路,被配置为响应于帧前开启信号,并通过非工作电平信号对上拉节点进行放电。

22、其中,对于一个所述移位寄存器,所述放电子电路包括第七晶体管;

23、所述第七晶体管的第一极连接非工作电平信号端,第二极连接所述上拉节点,控制极连接帧前开启信号端。

24、其中,所述移位寄存器还包括至少一个辅助子电路,所述辅助子电路与所述下拉节点一一对应连接;

25、所述辅助子电路,被配置为响应于所述输入信号,通过所述非工作电平信号对所述下拉节点进行下拉。

26、其中,位于同一组的各所述移位寄存器的辅助子电路共用。

27、其中,所述辅助子电路包括第十六晶体管;

28、所述第十六晶体管的第一极连接非工作电平信号端,第二极连接与之对应的所述下拉节点,控制极连接信号输入端。

29、其中,对于一个所述移位寄存器,所述输入子电路包括第一晶体管,所述第一晶体管的第一极和控制极均连接信号输入端,第二极连接所述上拉节点;或者,

30、所述第一晶体管的第一极连接预充电源信号端,第二极连接所述上拉节点,控制极连接信号输入端。

31、其中,对于一个所述移位寄存器,所述输出子电路包括包括第三晶体管、第十五晶体管和存储电容;

32、所述第三晶体管的第一极连接时钟信号端,第二极连接所述信号输出端和所述存储电容的第二端,控制极连接所述存储电容的第一端;

33、所述第十五晶体管的第一极连接所述时钟信号端,第二极连接级联信号输出端,控制极连接所述存储电容的第一端;

34、对于一组所述移位寄存器,各所述移位寄存器所连接的时钟信号线位于同一组,且不同的所述移位寄存器连接不同的时钟信号线。

35、其中,所述移位寄存器还包括至少一个第三降噪子电路,所述第三降噪子电路与所述下拉节点一一对应连接;

36、所述第三降噪子电路,被配置为响应于与之连接的所述下拉节点的电位,通过所述非工作电平信号对所述级联信号输出端的输出进行降噪。

37、其中,所述第三降噪子电路包括第十七晶体管;

38、所述第十七晶体管的第一极连接非工作电平信号端,第二极连接所述级联信号输出端,控制极连接所述下拉节点。

39、其中,所述下拉控制子电路包括第五晶体管和第九晶体管;

40、所述第五晶体管的第一极连接电源电压端,第二极连接与之对应的所述下拉节点,控制极连接第九晶体管的第二极;

41、所述第九晶体管的第一极和控制极均连接所述电源电压端;

42、一组所述移位寄存器中的各所述所述第五晶体管的第一极所连接电源电压端不同。

43、其中,对于一个所述移位寄存器,所述下拉子电路包括第六晶体管和第八晶体管;

44、所述第六晶体管的第一极连接非工作电平信号端,第二极连接对之对应的所述下拉节点,控制极连接所述上拉节点;

45、所述第八晶体管的第一极连接非工作电平信号端,第二极连接对之对应的所述下拉控制子电路中的第五晶体管的控制极和第九晶体管的第二极,控制极连接所述上拉节点。

46、其中,所述n为4。

47、其中,第i个所述移位寄存器的信号输入端连接第i-2个所述移位寄存器的级联信号输出端;i取大于或者等于3的整数;

48、第j组的各所述移位寄存器的复位信号端连接第j+1组中的第4个所述移位寄存器的信号输出端或者级联信号输出端;j取大于或者等于1的整数。

49、本公开实施例还一种显示装置,其包括上述任一所述的栅极驱动电路。

- 还没有人留言评论。精彩留言会获得点赞!