单个位线SRAM像素及其驱动方法与流程

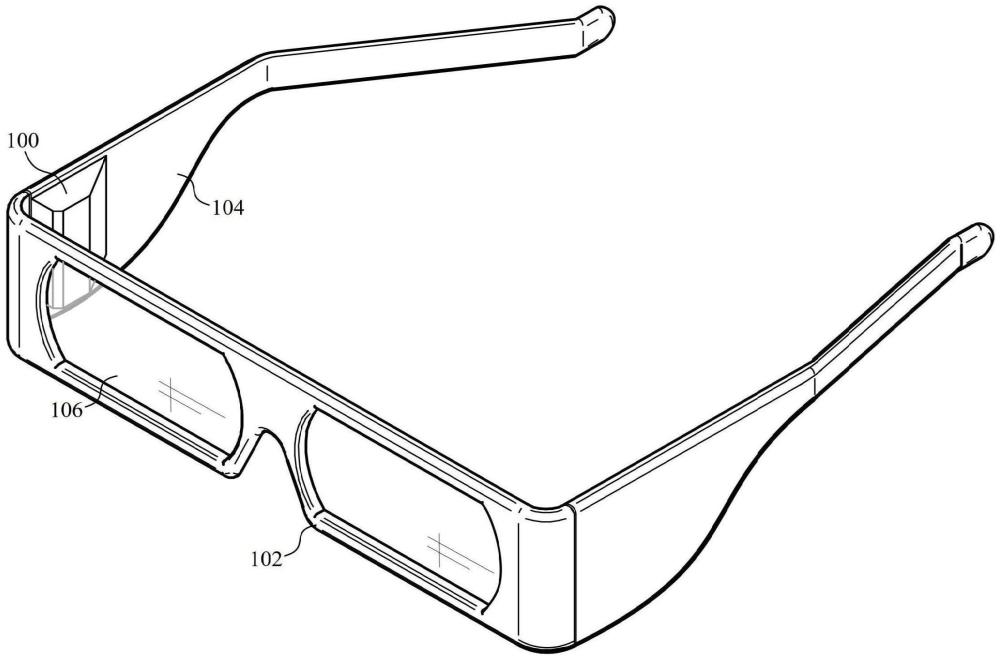

本发明总体上涉及数字显示器,并且更具体地涉及数字显示器像素电路。

背景技术:

1、随着数字显示器(例如,硅基液晶显示器、微型发光二极管显示器等)被并入到越来越多的设备中,一直需要改进其性能。典型的数字显示器包括驱动电路,该驱动电路电连接到布置成多个m列和n行的m×n像素阵列。每行像素电连接到相应的行选择线,并且每列像素电连接到相应的数据线集。每个数据线集通常包括位线和反位线。当要将数据位写入单独像素电路时,在位线上断言(assert)该位值,同时在反位线上断言该值的倒数。换句话说,将单个数据位写入像素电路需要在相应的两条不同信号线上断言两个不同的位值。

2、在驱动像素电路的阵列时,通过驱动位线消耗大量功率。当然,高功耗显著降低了数字显示器的整体性能。例如,显示器设备的高功率消耗非常快地消耗主机设备电池,并且因此限制了显示器可以结合到哪种类型的主机设备中。高功耗还导致散热问题,这对显示器设备施加了大量的设计约束。

3、已经尝试通过设计更复杂的像素电路来减轻像素阵列电路中的功耗挑战。然而,由于单独像素的非常小的尺寸约束,这些更复杂的设计非常难以实现,并且通常不可能实现。

技术实现思路

1、本发明通过提供装配在间距不大于3μm的阵列中的七晶体管电路来克服与现有技术相关联的问题。晶体管中的四个被用作锁存器。晶体管中的一个促进对一行使能的晶体管中的单个晶体管的选择性接入或保持。晶体管中的另一个晶体管仅使用单个位线来阻断(block)电流以促进锁存器在数字值之间的转变。

2、示例位存储电路包括第一电压供应线、第二电压供应线、位线、锁存器、第一开关晶体管和阻断晶体管。锁存器具有输入和输出。第一开关晶体管具有第一端子、第二端子和控制端子。响应于在第一开关晶体管的控制端子上被断言的第一控制信号,第一开关晶体管可操作以在位线和锁存器的输入之间选择性地提供导电路径(conductive path)和非导电路径。阻断晶体管包括控制端子,并且可操作以响应于第二控制信号在锁存器的输入和第二电压供应线之间选择性地提供导电路径和非导电路径。

3、示例位存储电路可另外包含具有第一端子、第二端子及控制端子的第二开关晶体管。响应于在第二开关晶体管的控制端子上被断言的第三控制信号,第二开关晶体管可以选择性地在位线和锁存器的输入之间提供导电路径和非导电路径。第一开关晶体管和第二开关晶体管可以串联耦合在位线和锁存器的输入之间。

4、在示例位存储电路中,锁存器可包含第一p沟道晶体管、第一n沟道晶体管、第二p沟道晶体管及第二n沟道晶体管。第一p沟道晶体管具有耦合到第一电压供应线的源极端子、耦合到锁存器的输出的漏极端子以及耦合到锁存器的输入的栅极端子。第一n沟道晶体管具有耦合到第二电压供应线的源极端子、耦合到锁存器的输出的漏极端子以及耦合到锁存器的输入的栅极端子。第二p沟道晶体管具有耦合到第一电压供应线的源极端子、耦合到锁存器的输入的漏极端子以及耦合到锁存器的输出的栅极端子。第二n沟道晶体管具有耦合到第二电压供应线的源极端子、经由阻断晶体管选择性地耦合到锁存器的输入的漏极端子、以及耦合到锁存器的输出的栅极端子。或者,第二n沟道晶体管可以使其源极端子经由阻断晶体管选择性地耦合到第二电压供应线,使其漏极端子耦合到锁存器的输入,并且使其栅极端子耦合到锁存器的输出。

5、示例位存储电路可用于显示设备中。举例来说,位存储电路可另外包含耦合到锁存器的输出的像素电极。像素电极可以是硅基液晶(lcos)设备的反射像素镜。

6、示例位存储电路可包括不超过七个晶体管。另外,在示例系统中,位存储电路可以与单个位线一起操作并且连接到不超过一个位线。

7、示例位存储电路可以附加地包括脉冲发生器,该脉冲发生器具有耦合到阻断晶体管的控制端子的输出。脉冲发生器可以包括在例如行地址解码器中,并且可以将所生成的脉冲与由行地址解码器生成的行使能信号协调。可替代地,阻断晶体管的控制端子可以耦合到第三电压供应线,该第三电压供应线具有在第一电压供应线的电压和第二电压供应线的电压之间的恒定电压。在这种情况下,第二控制信号可以是恒定电压,并且阻断晶体管由此可以保持在部分导电状态。

8、还公开了示例方法。一种用于将数据位写入显示器的像素的方法包括在耦合到像素的锁存器的输入的位线上断言数据位,以及在像素的第一晶体管的栅极上断言第一控制信号。响应于第一控制信号,第一晶体管至少部分地禁用像素的第二晶体管以防止影响锁存器的输入上的电压。示例方法附加地包括在像素的第三晶体管上断言使能信号以选择性地将锁存器的输入耦合到位线,并且然后改变第一控制信号以重新使能像素的第二晶体管以影响锁存器的输入上的电压。该示例方法附加地包括在第三晶体管上断言禁用信号以选择性地将位线与锁存器的输入解耦。

9、示例方法可以附加地包括在像素的第四晶体管上断言第二使能信号,以及在像素的第四晶体管上断言第二禁用信号。在第三晶体管上断言使能信号并且在第四晶体管上断言第二使能信号使得第三晶体管和第四晶体管将位线电耦合到锁存器的输入。断言第三晶体管上的使能信号和第四晶体管上的第二禁用信号将位线与锁存器的输入隔离。断言第三晶体管上的禁用信号和第四晶体管上的第二使能信号将位线与锁存器的输入隔离。

10、一种示例显示器包括第一电压供应线、第二电压供应线、以列和行布置的像素电极的阵列、多条行使能线、多条阻断信号线、多条位线以及以列和行布置的像素电路的阵列。每个像素电路可以包括锁存器、第一开关晶体管及阻断晶体管。锁存器具有耦合到位线之一的输入和耦合到像素电极之一的输出。第一开关晶体管具有耦合到行使能线中的一者的控制端子。第一开关晶体管可操作以响应于在行使能线上断言第一控制信号而在位线和锁存器的输入之间提供导电路径和非导电路径。阻断晶体管包括耦合到阻断信号线之一的控制端子,并且可操作以响应于在耦合的阻断信号线上断言的第二控制信号,在锁存器的输入和第二电压供应线之间选择性地提供导电路径和非导电路径。

11、示例显示器可以附加地包括多个列使能线。每一像素包括第二开关晶体管,具有耦合到列使能线中的一者的控制端子。第二开关晶体管可操作以响应于在所耦合的列使能线上断言第三控制信号而在位线与锁存器的输入之间选择性地提供导电路径和非导电路径。第一开关晶体管和第二开关晶体管串联耦合在位线和锁存器的输入之间。

12、在示例显示器中,锁存器中的每一个包含第一p沟道晶体管、第一n沟道晶体管、第二p沟道晶体管及第二n沟道晶体管。第一p沟道晶体管具有耦合到第一电压供应线的源极端子、耦合到锁存器的输出的漏极端子以及耦合到锁存器的输入的栅极端子。第一n沟道晶体管具有耦合到第二电压供应线的源极端子、耦合到锁存器的输出的漏极端子以及耦合到锁存器的输入的栅极端子。第二p沟道晶体管具有耦合到第一电压供应线的源极端子、耦合到锁存器的输入的漏极端子以及耦合到锁存器的输出的栅极端子。第二n沟道晶体管具有耦合到第二电压供应线的源极端子、经由阻断晶体管选择性地耦合到锁存器的输入的漏极端子、以及耦合到锁存器的输出的栅极端子。可替代地,第二n沟道晶体管可以具有经由阻断晶体管选择性地耦合到第二电压供应线的源极端子、耦合到锁存器的输入的漏极端子、以及耦合到锁存器的输出的栅极端子。

13、在示例显示器中,每个像素电路包括不超过七个晶体管。在特定实施例中,示例像素电路包括恰好七个晶体管。在示例显示器中,每个像素电路耦合到位线中的不超过一个位线。更具体地,每个像素电路恰好耦合到位线中的一条位线。

14、还公开了一种形成在p型半导体衬底中及p型半导体衬底上的位存储电路的示例阵列。每个位存储电路包括形成在p型衬底中的至少一个n阱、形成在至少一个n阱中的第一p型掺杂区、形成在至少一个n阱中的第二p型掺杂区及形成在至少一个n阱中的第三p型掺杂区。每个位存储电路另外包含形成在p型衬底中的第一n型掺杂区、形成在p型衬底中的第二n型掺杂区、形成在p型衬底中的第三n型掺杂区、形成在p型衬底中的第四n型掺杂区、形成在p型衬底中的第五n型掺杂区、形成在p型衬底中的第六n型掺杂区及形成在p型衬底中的第七n型掺杂区。

15、每个位存储电路另外包括第一多晶硅栅极、第二多晶硅栅极、第三多晶硅栅极、第四多晶硅栅极、第五多晶硅栅极、第六多晶硅栅极和第七多晶硅栅极。第一多晶硅栅极形成在设置在第一n型掺杂区和第二n型掺杂区之间的p型衬底的第一区域上方。第二多晶硅栅极形成在设置在第二n型掺杂区和第三n型掺杂区之间的p型衬底的第二区域上方。第三多晶硅栅极形成在设置在第三n型掺杂区和第四n型掺杂区之间的p型衬底的第三区域上方。第四多晶硅栅极形成在设置在第四n型掺杂区和第五n型掺杂区之间的p型衬底的第四区域上方。第五多晶硅栅极形成在设置在第一p型掺杂区和第二p型掺杂区之间的至少一个n阱的第一区域上方。第六多晶硅栅极形成在设置在第二p型掺杂区和第三p型掺杂区之间的至少一个n阱的第二区域上方。第七多晶硅栅极形成设置在第六n型掺杂区和第七n型掺杂区之间的在p型衬底的第五区域上方。

16、位存储单元的示例阵列另外包括形成在衬底及多晶硅栅极上方的一个或多个导电层。一个或多个导电层包括提供位存储单元的组件之间的互连的多个导电路径。第一导电路径将第一n型掺杂区电耦合到阵列的位线。第二导电路径将第一多晶硅栅极电耦合到阵列的第一控制线。第三导电路径将第二多晶硅栅极电耦合到阵列的第二控制线。第四导电路径将第三多晶硅栅极电耦合到阵列的第三控制线。第五导电路径电耦合第三n型掺杂区、第一p型掺杂区、第六多晶硅栅极和第七多晶硅栅极。第六导电路径电耦合第四多晶硅栅极、第五多晶硅栅极、第一p型掺杂区和第六n型掺杂区。第七导电路径将第二p型掺杂区电耦合到阵列的第一电压供应线。第八导电路径将第五n型掺杂区和第七n型掺杂区电耦合到阵列的第二电压供应线。第二电压供应线提供比第一电压供应线更低的电压。阵列具有不大于3μm的间距。

17、在位存储电路的示例阵列中,阵列的第一控制线可为行使能线。阵列的第二控制线可以是列使能线,并且第六导电路径电耦合到像素镜。

18、在位存储电路的特定示例阵列中,第一n型掺杂区、第二n型掺杂区和第三n型掺杂区中的每一个的区域大于第四n型掺杂区、第五n型掺杂区、第六n型掺杂区和第七n型掺杂区中最大的一个的区域。

- 还没有人留言评论。精彩留言会获得点赞!