LED显示驱动芯片及共阴LED显示系统、共阳LED显示系统的制作方法

本发明涉及led显示驱动领域,具体涉及一种led显示驱动芯片及共阴led显示系统、共阳led显示系统。

背景技术:

1、在led(英文全称light mitting diode,发光二极管)显示系统中,led显示驱动芯片的输出端连接led阵列中的led列线,在pwm信号的有效期间,输出驱动电流从而驱动该列线上的led灯珠发光。

2、其中,pwm信号一般由时钟信号和显示数据决定,时钟信号用于控制pwm信号在时钟周期内的上升沿和下降沿的位置,而显示数据则决定了pwm信号的宽度,以控制led灯珠的点亮时长。

3、基于led显示系统的发展,对led显示驱动芯片提出了更高的要求,不仅需要保证pwm信号的精度,还得具有更小的电路面积和较低的功耗等。然而,现有的led显示驱动芯片难以同时满足上述要求。

技术实现思路

1、本发明实施例提供一种led显示驱动芯片及共阴led显示系统、共阳led显示系统,能实现更高的pwm信号的精度,具有更小的电路面积和较低的功耗,以克服上述技术问题。

2、通过背景技术部分已知晓,本领域现阶段对led显示驱动芯片提出了更高的要求,即不仅需要保证pwm信号的精度,还得具有更小的电路面积和较低的功耗等。其中,发明人发现:用于产生时钟信号的时钟产生模块是影响led显示驱动芯片设计的关键,然而在现有的led显示驱动芯片中,所采用的时钟产生模块要么无法实现倍频功能,从而无法保证pwm的精度,若要实现倍频功能,则需要耗费更高的功耗;要么可以实现倍频功能,然而其输出的倍频时钟信号的抖动累积时间长,仍然会影响pwm的精度,一些方案中有提出对该时钟产生模块进行改进,以产生低抖动的倍频时钟,然而这需要更大的电路面积,这无法满足led显示驱动芯片对更小电路面积的要求。

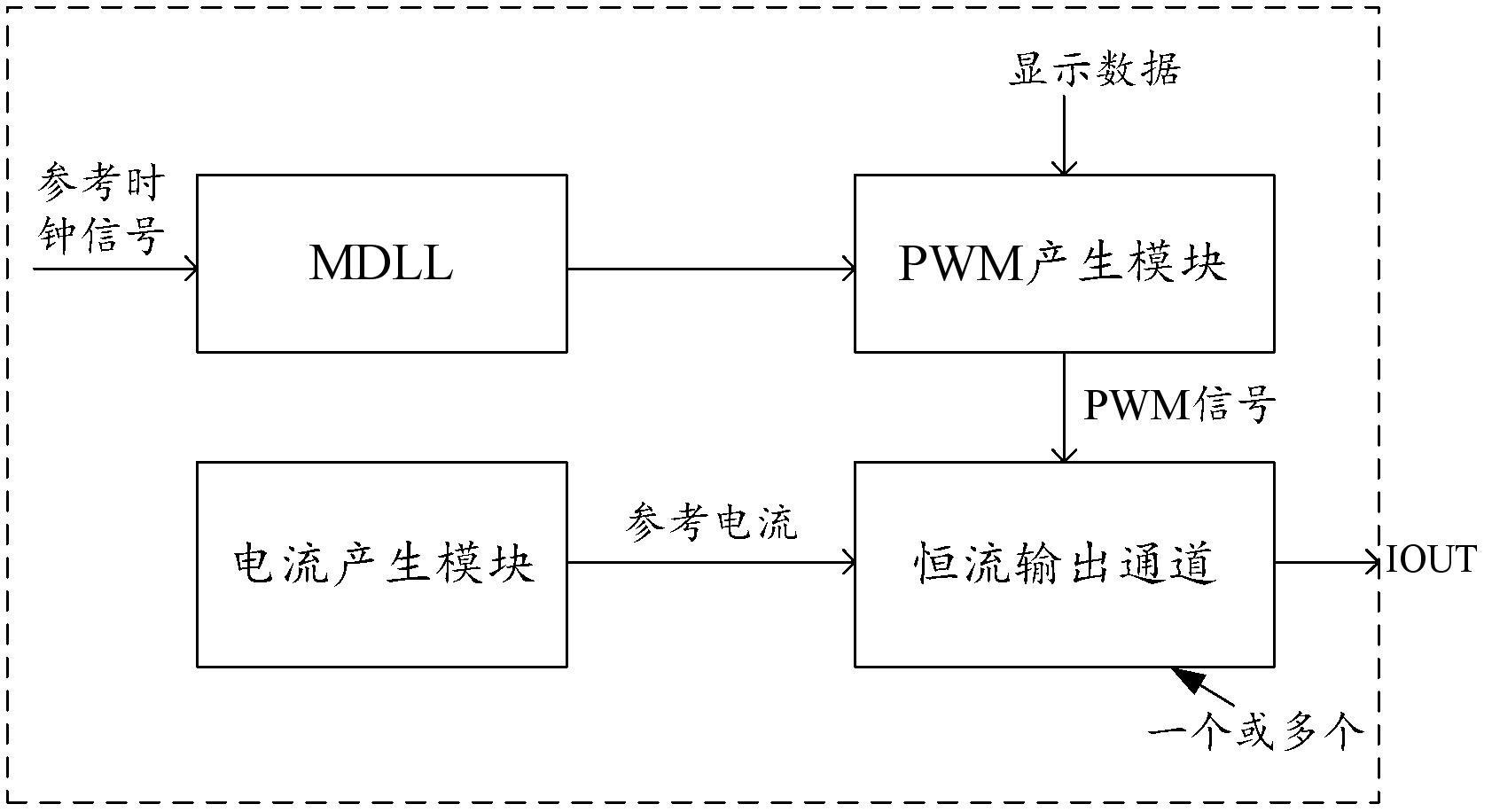

3、为了解决上述问题,从第一方面,本发明实施例公开了一种led显示驱动芯片,包括:

4、电流产生模块,用于产生参考电流;

5、倍乘延迟锁定环mdll,基于输入的参考时钟信号产生系统时钟信号;其中,mdll处于锁定状态时,系统时钟信号定期被该参考时钟信号重置;

6、pwm产生模块,基于显示数据和系统时钟信号产生pwm信号;

7、一个或多个恒流输出通道,用于在pwm信号的有效期间,基于参考电流输出驱动电流。

8、在本发明实施例中,参考时钟信号为全局时钟信号,本发明实施例利用mdll作为led显示驱动领域的时钟产生模块,可以直接基于该参考时钟信号低功耗的产生系统时钟信号,其中,该系统时钟信号可以为参考时钟信号的倍频信号和或分频信号。由于在本发明中,mdll处于锁定状态时,其所产生的系统时钟信号能定期被该参考时钟信号重置,所以mdll受非理想因素所导致的系统时钟信号的时钟抖动累积基本上只能持续一个输入参考周期,即系统时钟信号在前一个输入参考周期的时钟抖动基本不会持续到下一个输入参考周期,系统时钟信号在前一个输入参考周期的时钟抖动累积会在下一个输入参考周期时因被该参考时钟信号重置而被清除或刷新,因此其可以在更高倍频频率下具有更低的抖动,最大程度的抑制参考杂散,降低了非理想因素对系统时钟信号的干扰,能保证系统时钟信号的精度和可靠性。如此,pwm产生模块基于显示数据和该系统时钟信号的产生pwm信号也会有较高精度。同时因mdll为一阶环路设计,不需要很大的滤波电容,因此本发明的led显示驱动芯片也能具有更小电路面积。显然,本发明实施例所提出的led显示驱动芯片能有效满足本领域现阶段对led显示驱动芯片提出的更高要求。

9、在本发明一实施例中,系统时钟信号的频率fgclk满足:fgclk=fclk*m,其中,fclk为参考时钟信号的频率,m为倍频数,m为大于等于1的正整数;

10、mdll处于锁定状态时,系统时钟信号每隔1个时钟周期tclk被参考时钟信号重置,其中,tclk为参考时钟信号的时钟周期。

11、在本发明一实施例中,系统时钟信号的频率fgclk满足:fgclk=fclk*m/n,其中,fclk为参考时钟信号的频率,m为倍频数,n为分频数,m为大于等于1的正整数,n为大于等于1的正整数;mdll处于锁定状态时,系统时钟信号每隔n个时钟周期tclk被参考时钟信号重置,其中,tclk为参考时钟信号的时钟周期。

12、在本发明一实施例中,mdll还用于产生系统时钟信号的多相位时钟信号gclk<q-1:0>;其中,q=2p,p为用于产生pwm波小数部分的最大位数,多相位时钟信号中的任意相邻两个相位时钟信号之间相差1/q个时钟周期tgclk,tgclk为系统时钟信号的时钟周期;

13、pwm产生模块基于显示数据、多相位时钟信号中的第一相位时钟信号和第二相位时钟信号产生pwm信号;第二相位时钟信号与第一相位时钟信号之间相差i/q个时钟周期tgclk,i为0至(q-1)之间的整数。

14、在本发明一实施例中,mdll还用于产生系统时钟信号的第三相位时钟信号和第四相位时钟信号;第三相位时钟信号和第四相位时钟信号相差l个时钟周期tgclk,0≤l<1,tgclk为系统时钟信号的时钟周期;

15、其中,pwm产生模块基于显示数据和第三相位时钟信号产生第一pwm信号,以及基于第一pwm信号和第四相位时钟信号产生与第一pwm信号的脉宽相同的第二pwm信号,并对第一pwm信号和第二pwm信号进行逻辑运算,输出pwm信号。

16、在本发明一实施例中,led显示驱动芯片还包括:偏置模块,偏置模块中的第一mos管与恒流输出通道中的至少一个第二mos管组成电流镜;在pwm信号的有效期间,参考电流经电流镜输出为驱动电流。

17、从第二方面,本发明实施例还公开了一种共阴led显示系统,包括:

18、led阵列和至少一个led显示驱动芯片;

19、其中,led阵列中,同一行中的led的负极与共阴极节点连接,同一列中的相同颜色的led的正极与共阳极节点连接;

20、led显示驱动芯片包括:

21、电流产生模块,用于产生参考电流;

22、倍乘延迟锁定环mdll,基于输入的参考时钟信号产生系统时钟信号;其中,mdll处于锁定状态时,系统时钟信号定期被参考时钟信号重置;

23、pwm产生模块,基于显示数据和系统时钟信号产生pwm信号;

24、多个恒流输出通道,用于在pwm信号的有效期间,基于参考电流向对应的共阳极节点提供驱动电流。

25、在本发明一实施例中,系统时钟信号的频率fgclk满足:fgclk=fclk*m,mdll处于锁定状态时,系统时钟信号每隔1个时钟周期tclk被参考时钟信号重置;或,系统时钟信号的频率fgclk满足:fgclk=fclk*m/n,mdll处于锁定状态时,系统时钟信号每隔n个时钟周期tclk被参考时钟信号重置;其中,fclk为参考时钟信号的频率,tclk为参考时钟信号的时钟周期,m为倍频数,n为分频数,m为大于等于1的正整数,n为大于等于1的正整数。

26、从第三方面,本发明实施例还公开了一种共阳led显示系统,包括:

27、led阵列和至少一个led显示驱动芯片;

28、其中,led阵列中,同一行中的led的正极与共阳极节点连接,同一列中的相同颜色的led的负极与共阴极节点连接;

29、led显示驱动芯片包括:

30、电流产生模块,用于产生参考电流;

31、倍乘延迟锁定环mdll,基于输入的参考时钟信号产生系统时钟信号;其中,mdll处于锁定状态时,系统时钟信号定期被参考时钟信号重置;

32、pwm产生模块,基于显示数据和系统时钟信号产生pwm信号;

33、多个恒流输出通道,用于在pwm信号的有效期间,基于参考电流向对应的共阴极节点提供驱动电流。

34、在本发明一实施例中,系统时钟信号的频率fgclk满足:fgclk=fclk*m,mdll处于锁定状态时,系统时钟信号每隔1个时钟周期tclk被参考时钟信号重置;或,系统时钟信号的频率fgclk满足:fgclk=fclk*m/n,mdll处于锁定状态时,系统时钟信号每隔n个时钟周期tclk被参考时钟信号重置;其中,fclk为参考时钟信号clk的频率,tclk为参考时钟信号的时钟周期,m为倍频数,n为分频数,m为大于等于1的正整数,n为大于等于1的正整数。

35、本发明实施例包括以下优点:

36、本发明实施例提出的led显示驱动芯片包括:用于产生参考电流的电流产生模块,基于输入的参考时钟信号产生系统时钟信号的倍乘延迟锁定环mdll,其中,mdll处于锁定状态时,系统时钟信号定期被该参考时钟信号重置;还包括基于显示数据和系统时钟信号产生pwm信号的pwm产生模块,以及一个或多个恒流输出通道,每个恒流输出通道用于在pwm信号的有效期间,基于该参考电流输出驱动电流。本发明实施例利用mdll作为led显示驱动领域的时钟产生模块能直接实现倍频功能,无需复杂电路来提高输入频率,所以本发明的led显示驱动芯片具有较低的功耗,而由于本发明的mdll能在实现倍频功能的同时还能保证更低的输出抖动,所以本发明实施例的系统时钟信号具有高倍频、低抖动特性,能最大程度的抑制参考杂散,实现更高的pwm信号的精度,同时因mdll为一阶环路设计,不需要很大的滤波电容,因此本发明的led显示驱动芯片也能具有更小电路面积,满足本领域现阶段对led显示驱动芯片提出的更高要求。

- 还没有人留言评论。精彩留言会获得点赞!