移位寄存器及其驱动方法、栅极驱动电路、显示装置与流程

本公开涉及显示,尤其涉及一种移位寄存器及其驱动方法、栅极驱动电路、显示装置。

背景技术:

1、栅极驱动电路(也称扫描驱动电路)为显示装置中的重要组成部分。栅极驱动电路可以包括多级级联的移位寄存器,每一级移位寄存器分别与显示装置中的一行栅线电连接电连接。栅极驱动电路可以向显示装置中的多条栅线中逐行输入扫描信号(也可以称为栅信号),分别驱动显示装置中各行子像素进行显示扫描,进而使得显示装置能够进行画面显示。

2、在显示装置中设置栅极驱动电路,能够有效降低成本、提高良率。

技术实现思路

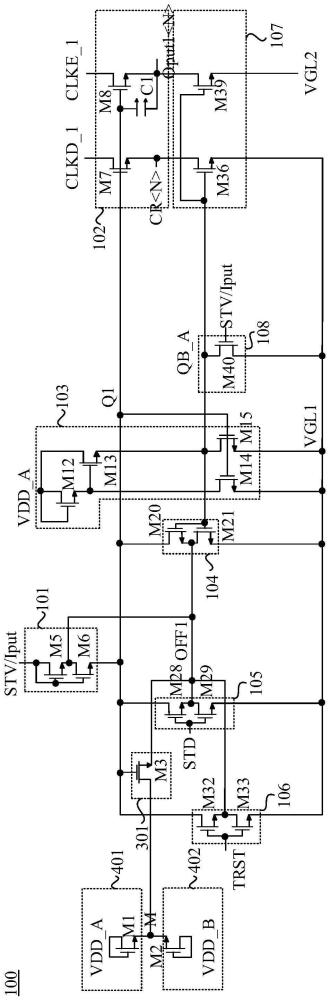

1、一方面,提供一种移位寄存器。所述移位寄存器,包括:第一扫描单元、防漏电单元和防漏电输入单元。所述第一扫描单元包括:第一输入电路,与输入信号端、第一上拉节点及第一防漏电节点电连接;所述第一输入电路被配置为,响应于在所述输入信号端处接收的输入信号,将所述输入信号传输至所述第一上拉节点。所述防漏电输入单元与第一电压信号端、第二电压信号端及防漏电输入节点电连接;所述防漏电输入单元被配置为,将所述第一电压信号传输至所述防漏电输入节点;或,将所述第二电压信号传输至所述防漏电输入节点。所述防漏电单元与所述第一上拉节点、所述第一防漏电节点及所述防漏电输入节点电连接;所述防漏电单元被配置为,在所述第一上拉节点的电压的控制下,将来自所述防漏电输入节点的第一电压信号或第二电压信号传输至所述第一防漏电节点。

2、在一些实施例中,所述防漏电输入单元包括:第一防漏电输入电路和第二防漏电输入电路。所述第一防漏电输入电路与所述第一电压信号端及所述防漏电输入节点电连接;所述第一防漏电输入电路被配置为,响应于在所述第一电压信号端处接收的第一电压信号,将所述第一电压信号传输至所述防漏电输入节点。所述第二防漏电输入电路与所述第二电压信号端及所述防漏电输入节点电连接;所述第二防漏电输入电路被配置为,响应于在所述第二电压信号端处接收的第二电压信号,将所述第二电压信号传输至所述防漏电输入节点。其中,第一电压信号与第二电压信号不同。

3、在一些实施例中,所述第一防漏电输入电路包括:第一晶体管。所述第一晶体管的控制极与所述第一电压信号端电连接,所述第一晶体管的第一极与所述第一电压信号端电连接,所述第一晶体管的第二极与所述防漏电输入节点电连接。所述第二防漏电输入电路包括:第二晶体管。所述第二晶体管的控制极与所述第二电压信号端电连接,所述第二晶体管的第一极与所述第二电压信号端电连接,所述第二晶体管的第二极与所述防漏电输入节点电连接。

4、在一些实施例中,所述防漏电单元包括:第一防漏电电路。所述第一防漏电电路与所述第一上拉节点、所述防漏电输入节点及所述第一防漏电节点电连接;所述第一防漏电电路被配置为,在所述第一上拉节点的电压的控制下,将来自所述防漏电输入节点的所述第一电压信号或所述第二电压信号传输至所述第一防漏电节点。

5、在一些实施例中,所述第一防漏电电路包括:第三晶体管。所述第三晶体管的控制极与所述第一上拉节点电连接,所述第三晶体管的第一极与所述防漏电输入节点电连接,所述第三晶体管的第二极与所述第一防漏电节点电连接。

6、在一些实施例中,所述移位寄存器,还包括:第二扫描单元。所述第二扫描单元包括:第二输入电路,与所述输入信号端、第二上拉节点及第二防漏电节点电连接;所述第二输入电路被配置为,响应于在所述输入信号端处接收的输入信号,将所述输入信号传输至所述第二上拉节点。所述防漏电单元还与所述第二上拉节点及所述第二防漏电节点电连接;所述防漏电单元还被配置为,在所述第二上拉节点的电压的控制下,将来自所述防漏电输入节点的第一电压信号或第二电压信号传输至所述第二防漏电节点。

7、在一些实施例中,所述防漏电单元还包括:第二防漏电电路。所述第二防漏电电路与所述第二上拉节点、所述防漏电输入节点及所述第二防漏电节点电连接;所述第二防漏电电路被配置为,在所述第二上拉节点的电压的控制下,将来自所述防漏电输入节点的所述第一电压信号或所述第二电压信号传输至所述第二防漏电节点。

8、在一些实施例中,所述第二防漏电电路包括:第四晶体管。所述第四晶体管的控制极与所述第二上拉节点电连接,所述第四晶体管的第一极与所述防漏电输入节点电连接,所述第四晶体管的第二极与所述第二防漏电节点电连接。

9、在一些实施例中,所述第一扫描单元还包括:第一输出电路,与所述第一上拉节点、第一时钟信号端、第二时钟信号端、移位信号端及第一扫描信号端电连接;所述第一输出电路被配置为,在所述第一上拉节点的电压的控制下,将在所述第一时钟信号端处接收的第一时钟信号传输至所述移位信号端;及,在所述第一上拉节点的电压的控制下,将在所述第二时钟信号端处接收的第二时钟信号传输至第一扫描信号端。在所述移位寄存器还包括第二扫描单元的情况下,所述第二扫描单元还包括:第二输出电路,与所述第二上拉节点、第三时钟信号端及第二扫描信号端电连接;所述第二输出电路被配置为,在所述第二上拉节点的电压的控制下,将在所述第三时钟信号端处接收的第三时钟信号传输至所述第二扫描信号端。

10、在一些实施例中,所述第一输入电路包括:第五晶体管和第六晶体管。所述第五晶体管的控制极与所述输入信号端电连接,所述第五晶体管的第一极与所述输入信号端电连接,所述第五晶体管的第二极与所述第六晶体管的第一极及所述第一防漏电节点电连接。所述第六晶体管的控制极与所述输入信号端电连接,所述第六晶体管的第二极与所述第一上拉节点电连接。所述第一输出电路包括:第七晶体管、第八晶体管和第一电容器。所述第七晶体管的控制极与所述第一上拉节点电连接,所述第七晶体管的第一极与所述第一时钟信号端电连接,所述第七晶体管的第二极与所述移位信号端电连接。所述第八晶体管的控制极与所述第一上拉节点电连接,所述第八晶体管的第一极与所述第二时钟信号端电连接,所述第八晶体管的第二极与所述第一扫描信号端电连接。所述第一电容器的第一端与所述第一上拉节点电连接,所述第一电容器的第二端与所述第一扫描信号端电连接。所述第二输入电路包括:第九晶体管和第十晶体管。所述第九晶体管的控制极与所述输入信号端电连接,所述第九晶体管的第一极与所述输入信号端电连接,所述第九晶体管的第二极与所述第十晶体管的第一极及所述第二防漏电节点电连接。所述第十晶体管的控制极与所述输入信号端电连接,所述第十晶体管的第二极与所述第二上拉节点电连接。所述第二输出电路包括:第十一晶体管和第二电容器。所述第十一晶体管的控制极与所述第二上拉节点电连接,所述第十一晶体管的第一极与所述第三时钟信号端电连接,所述第十一晶体管的第二极与所述第二扫描信号端电连接。所述第二电容器的第一端与所述第二上拉节点电连接,所述第二电容器的第二端与所述第二扫描信号端电连接。

11、在一些实施例中,所述第一输出电路还与第五时钟信号端及第一感测信号端电连接;所述第一输出电路还被配置为,在所述第一上拉节点的电压的控制下,将在所述第五时钟信号端处接收的第五时钟信号传输至所述第一感测信号端。所述第二输出电路还与第六时钟信号端及第二感测信号端电连接;所述第二输出电路还被配置为,在所述第二上拉节点的电压的控制下,将在所述第六时钟信号端处接收的第六时钟信号传输至所述第二感测信号端。

12、在一些实施例中,所述第一输出电路还包括:第五十二晶体管和第四电容器。所述第五十二晶体管的控制极与所述第一上拉节点电连接,所述第五十二晶体管的第一极与所述第五时钟信号端电连接,所述第五十二晶体管的第二极与所述第一感测信号端电连接。所述第四电容器的第一端与所述第一上拉节点电连接,所述第四电容器的第二端与所述第一感测信号端电连接。所述第二输出电路还包括:第五十三晶体管和第五电容器。所述第五十三晶体管的控制极与所述第二上拉节点电连接,所述第五十三晶体管的第一极与所述第六时钟信号端电连接,所述第五十三晶体管的第二极与所述第二感测信号端电连接。所述第五电容器的第一端与所述第二上拉节点电连接,所述第五电容器的第二端与所述第二感测信号端电连接。

13、在一些实施例中,所述第一扫描单元还包括:第一控制电路,与所述第一上拉节点、所述第一电压信号端、第一下拉节点及第三电压信号端电连接;所述第一控制电路被配置为,在所述第一上拉节点的电压和所述第一电压信号端所传输的第一电压信号的控制下,对所述第一下拉节点的电压进行控制。在所述移位寄存器还包括第二扫描单元的情况下,所述第二扫描单元还包括:第二控制电路,与所述第二上拉节点、所述第二电压信号端、第二下拉节点及所述第三电压信号端电连接;所述第二控制电路被配置为,在所述第二上拉节点的电压和所述第二电压信号端所传输的第二电压信号的控制下,对所述第二下拉节点的电压进行控制。

14、在一些实施例中,所述第一控制电路包括:第十二晶体管、第十三晶体管、第十四晶体管和第十五晶体管。所述第十二晶体管的控制极与所述第一电压信号端电连接,所述第十二晶体管的第一极与所述第一电压信号端电连接,所述第十二晶体管的第二极与所述第十三晶体管的控制极及所述第十四晶体管的第一极电连接。所述第十三晶体管的第一极与所述第一电压信号端电连接,所述第十三一晶体管的第二极与所述第一下拉节点及所述第十五晶体管的第一极电连接。所述第十四晶体管的控制极与所述第一上拉节点电连接,所述第十四晶体管的第二极与所述第三电压信号端电连接。所述第十五晶体管的控制极与所述第一上拉节点电连接,所述第十五晶体管的第二极与所述第三电压信号端电连接。所述第二控制电路包括:第十六晶体管、第十七晶体管、第十八晶体管和第十九晶体管。所述第十六晶体管的控制极与所述第二电压信号端电连接,所述第十六晶体管的第一极与所述第二电压信号端电连接,所述第十六晶体管的第二极与所述第十七晶体管的控制极及所述第十八晶体管的第一极电连接。所述第十七晶体管的第一极与所述第二电压信号端电连接,所述第十七晶体管的第二极与所述第二下拉节点及所述第十九晶体管的第一极电连接。所述第十八晶体管的控制极与所述第二上拉节点电连接,所述第十八晶体管的第二极与所述第三电压信号端电连接。所述第十九晶体管的控制极与所述第二上拉节点电连接,所述第十九晶体管的第二极与所述第三电压信号端电连接。

15、在一些实施例中,所述第一扫描单元还包括:第一复位电路,与所述第一下拉节点、所述第一上拉节点、所述第三电压信号端及所述第一防漏电节点电连接;所述第一复位电路被配置为,在所述第一下拉节点的电压的控制下,对所述第一上拉节点进行复位。在所述移位寄存器还包括第二扫描单元的情况下,所述第一复位电路还与所述第二下拉节点电连接;所述第一复位电路还被配置为,在所述第二下拉节点的电压的控制下,对所述第一上拉节点进行复位。所述第二扫描单元还包括:第二复位电路,与所述第一下拉节点、所述第二下拉节点、所述第二上拉节点、所述第三电压信号端及所述第二防漏电节点电连接;所述第二复位电路被配置为,在所述第一下拉节点的电压或所述第二下拉节点的电压的控制下,对所述第二上拉节点进行复位。

16、在一些实施例中,所述第一复位电路包括:第二十晶体管和第二十一晶体管。所述第二十晶体管的控制极与所述第一下拉节点电连接,所述第二十晶体管的第一极与所述第一上拉节点电连接,所述第二十晶体管的第二极与所述第二十一晶体管的第一极及所述第一防漏电节点电连接。所述第二十一晶体管的控制极与所述第一下拉节点电连接,所述第二十一晶体管的第二极与所述第三电压信号端电连接。在所述移位寄存器还包括第二扫描单元的情况下,所述第一复位电路还包括:第二十二晶体管和第二十三晶体管。所述第二十二晶体管的控制极与所述第二下拉节点电连接,所述第二十二晶体管的第一极与所述第一上拉节点电连接,所述第二十二晶体管的第二极与所述第二十三晶体管的第一极及所述第一防漏电节点电连接。所述第二十三晶体管的控制极与所述第二下拉节点电连接,所述第二十三晶体管的第二极与所述第三电压信号端电连接。所述第二复位电路包括:第二十四晶体管、第二十五晶体管、第二十六晶体管和第二十七晶体管。所述第二十四晶体管的控制极与所述第一下拉节点电连接,所述第二十四晶体管的第一极与所述第二上拉节点电连接,所述第二十四晶体管的第二极与所述第二十六晶体管的第一极及所述第二防漏电节点电连接。所述第二十五晶体管的控制极与所述第二下拉节点电连接,所述第二十五晶体管的第一极与所述第二上拉节点电连接,所述第二十五晶体管的第二极与所述第二十七晶体管的第一极及所述第二防漏电节点电连接。所述第二十六晶体管的控制极与所述第一下拉节点电连接,所述第二十六晶体管的第二极与所述第三电压信号端电连接。所述第二十七晶体管的控制极与所述第二下拉节点电连接,所述第二十七晶体管的第二极与所述第三电压信号端电连接。

17、在一些实施例中,所述第一扫描单元还包括:第三复位电路,与显示复位信号端、所述第一上拉节点、所述第三电压信号端及所述第一防漏电节点电连接;所述第三复位电路被配置为,在所述显示复位信号端所传输的显示复位信号的控制下,对所述第一上拉节点进行复位。所述第二扫描单元还包括:第四复位电路,与所述显示复位信号端、所述第二上拉节点、所述第三电压信号端及所述第二防漏电节点电连接;所述第四复位电路被配置为,在所述显示复位信号端所传输的显示复位信号的控制下,对所述第二上拉节点进行复位。

18、在一些实施例中,所述第三复位电路包括:第二十八晶体管和第二十九晶体管。所述第二十八晶体管的控制极与所述显示复位信号端电连接,所述第二十八晶体管的第一极与所述第一上拉节点电连接,所述第二十八晶体管的第二极与所述第二十九晶体管的第一极及所述第一防漏电节点电连接。所述第二十九晶体管的控制极与所述显示复位信号端电连接,所述第二十九晶体管的第二极与所述第三电压信号端电连接。所述第四复位电路包括:第三十晶体管和第三十一晶体管。所述第三十晶体管的控制极与所述显示复位信号端电连接,所述第三十晶体管的第一极与所述第二上拉节点电连接,所述第三十晶体管的第二极与所述第三十一晶体管的第一极及所述第二防漏电节点电连接。所述第三十一晶体管的控制极与所述显示复位信号端电连接,所述第三十一晶体管的第二极与所述第三电压信号端电连接。

19、在一些实施例中,所述第一扫描单元还包括:第五复位电路,与全局复位信号端、所述第一上拉节点、所述第三电压信号端及所述第一防漏电节点电连接;所述第五复位电路被配置为,在所述全局复位信号端所传输的全局复位信号的控制下,对所述第一上拉节点进行复位。所述第二扫描单元还包括:第六复位电路,与全局复位信号端、所述第二上拉节点、所述第三电压信号端及所述第二防漏电节点电连接;所述第六复位电路被配置为,在所述全局复位信号端所传输的全局复位信号的控制下,对所述第二上拉节点进行复位。

20、在一些实施例中,所述第五复位电路包括:第三十二晶体管和第三十三晶体管。所述第三十二晶体管的控制极与所述全局复位信号端电连接,所述第三十二晶体管的第一极与所述第一上拉节点电连接,所述第三十二晶体管的第二极与所述第三十三晶体管的第一极及所述第一防漏电节点电连接。所述第三十三晶体管的控制极与所述全局复位信号端电连接,所述第三十三晶体管的第二极与所述第三电压信号端电连接。所述第六复位电路包括:第三十四晶体管和第三十五晶体管。所述第三十四晶体管的控制极与所述全局复位信号端电连接,所述第三十四晶体管的第一极与所述第二上拉节点电连接,所述第三十四晶体管的第二极与所述第三十五晶体管的第一极及所述第二防漏电节点电连接。所述第三十五晶体管的控制极与所述全局复位信号端电连接,所述第三十五晶体管的第二极与所述第三电压信号端电连接。

21、在一些实施例中,所述第一扫描单元还包括:第七复位电路和第八复位电路。所述第七复位电路与所述第一下拉节点、所述移位信号端、所述第一扫描信号端、所述第三电压信号端及第四电压信号端电连接;所述第七复位电路被配置为,在所述第一下拉节点的电压的控制下,对所述移位信号端和所述第一扫描信号端进行复位。在所述移位寄存器还包括第二扫描单元的情况下,所述第七复位电路还与所述第二下拉节点电连接;所述第七复位电路被配置为,在所述第二下拉节点的电压的控制下,对所述移位信号端和所述第一扫描信号端进行复位。所述第八复位电路与所述输入信号端、所述第一下拉节点及所述第三电压信号端电连接;所述第八复位电路被配置为,在所述输入信号端所传输的输入信号的控制下,对所述第一下拉节点进行复位。所述第二扫描单元还包括:第九复位电路和第十复位电路。所述第九复位电路与所述第一下拉节点、所述第二下拉节点、所述第二扫描信号端及所述第四电压信号端电连接;所述第九复位电路被配置为,在所述第一下拉节点的电压或所述第二下拉节点的电压的控制下,对所述第二扫描信号端进行复位。所述第十复位电路与所述输入信号端、所述第二下拉节点及所述第三电压信号端电连接;所述第十复位电路被配置为,在所述输入信号端所传输的输入信号的控制下,对所述第二下拉节点进行复位。

22、在一些实施例中,所述第七复位电路包括:第三十六晶体管和第三十九晶体管。所述第三十六晶体管的控制极与所述第一下拉节点电连接,所述第三十六晶体管的第一极与所述移位信号端电连接,所述第三十六晶体管的第二极与所述第三电压信号端电连接。所述第三十九晶体管的控制极与所述第一下拉节点电连接,所述第三十九晶体管的第一极与所述第一扫描信号端电连接,所述第三十九晶体管的第二极与所述第四电压信号端电连接。在所述移位寄存器还包括第二扫描单元的情况下,所述第七复位电路还包括:第三十八晶体管和第三十七晶体管。所述第三十八晶体管的控制极与所述第二下拉节点电连接,所述第三十八晶体管的第一极与所述移位信号端电连接,所述第三十八晶体管的第二极与所述第三电压信号端电连接。所述第三十七晶体管的控制极与所述第二下拉节点电连接,所述第三十七晶体管的第一极与所述第一扫描信号端电连接,所述第三十七晶体管的第二极与所述第四电压信号端电连接。所述第八复位电路包括:第四十晶体管。所述第四十晶体管的控制极与所述输入信号端电连接,所述第四十晶体管的第一极与所述第一下拉节点电连接,所述第四十晶体管的第二极与所述第三电压信号端电连接。所述第九复位电路包括:第四十一晶体管和第四十二晶体管。所述第四十一晶体管的控制极与所述第二下拉节点电连接,所述第四十一晶体管的第一极与所述第二扫描信号端电连接,所述第四十一晶体管的第二极与所述第四电压信号端电连接。所述第四十二晶体管的控制极与所述第一下拉节点电连接,所述第四十二晶体管的第一极与所述第二扫描信号端电连接,所述第四十二晶体管的第二极与所述第四电压信号端电连接。所述第十复位电路包括:第四十三晶体管。所述第四十三晶体管的控制极与所述输入信号端电连接,所述第四十三晶体管的第一极与所述第二下拉节点电连接,所述第四十三晶体管的第二极与所述第三电压信号端电连接。

23、在一些实施例中,在所述第一输出电路还与第一感测信号端电连接、所述第二输出电路还与第二感测信号端电连接的情况下,所述第七复位电路还与所述第一感测信号端电连接;所述第七复位电路还被配置为,在所述第一下拉节点的电压或所述第二下拉节点的电压的控制下,对所述第一感测信号端进行复位。所述第九复位电路还与所述第二感测信号端电连接;所述第九复位电路还被配置为,在所述第一下拉节点的电压或所述第二下拉节点的电压的控制下,对所述第二感测信号端电进行复位。

24、在一些实施例中,所述第七复位电路还包括:第五十四晶体管和第五十五晶体管。所述第五十四晶体管的控制极与所述第一下拉节点电连接,所述第五十四晶体管的第一极与所述第一感测信号端电连接,所述第五十四晶体管的第二极与所述第四电压信号端电连接。所述第五十五晶体管的控制极与所述第二下拉节点电连接,所述第五十五晶体管的第一极与所述第一感测信号端电连接,所述第五十五晶体管的第二极与所述第四电压信号端电连接。所述第九复位电路还还包括:第五十六晶体管和第五十七晶体管。所述第五十六晶体管的控制极与所述第二下拉节点电连接,所述第五十六晶体管的第一极与所述第二感测信号端电连接,所述第五十六晶体管的第二极与所述第四电压信号端电连接。所述第五十七晶体管的控制极与所述第一下拉节点电连接,所述第五十七晶体管的第一极与所述第二感测信号端电连接,所述第五十七晶体管的第二极与所述第四电压信号端电连接。

25、在一些实施例中,所述移位寄存器,还包括:消隐输入单元。所述消隐输入单元与选择控制信号端、所述输入信号端、第三电压信号端、第四时钟信号端、所述第一上拉节点、所述第一防漏电节点及所述防漏电输入节点电连接。所述消隐输入单元被配置为,在所述选择控制信号端所传输的选择控制信号的控制下,将在所述第四时钟信号端处接收的第四时钟信号传输至所述第一上拉节点。在所述移位寄存器还包括第二扫描单元的情况下,所述消隐输入单元还与所述第二上拉节点及所述第二防漏电节点电连接。所述消隐输入单元还被配置为,在所述选择控制信号端所传输的选择控制信号的控制下,将在所述第四时钟信号端处接收的第四时钟信号传输至所述第二上拉节点。

26、在一些实施例中,所述消隐输入单元包括:选择控制电路、第三输入电路、第一传输电路和第三防漏电电路。所述选择控制电路与所述选择控制信号端、所述输入信号端、所述第三电压信号端、第一消隐节点及第三防漏电节点电连接;所述选择控制电路被配置为,在所述选择控制信号的控制下,将在所述输入信号端处接收的输入信号传输至所述第一消隐节点。所述第三防漏电电路与第三防漏电节点、所述第一消隐节点及所述防漏电输入节点电连接;所述第三防漏电电路被配置为,在所述第一消隐节点的电压的控制下,将来自所述防漏电输入节点的第一电压信号或第二电压信号传输至所述第三防漏电节点。所述第三输入电路与所述第一消隐节点、所述第四时钟信号端及第二消隐节点电连接;所述第三输入电路被配置为,在所述第一消隐节点的电压的控制下,将在所述第四时钟信号端处接收的第四时钟信号传输至所述第二消隐节点。所述第一传输电路与所述第四时钟信号端、所述第二消隐节点、所述第一上拉节点及所述第一防漏电节点电连接;所述第一传输电路被配置为,在所述第四时钟信号端所传输的第四时钟信号的控制下,将在所述第二消隐节点处接收的所述第四时钟信号传输至所述第一上拉节点。在所述移位寄存器还包括第二扫描单元的情况下,所述消隐输入单元还包括:第二传输电路。所述第二传输电路与所述第四时钟信号端、所述第二消隐节点、所述第二上拉节点及所述第二防漏电节点电连接;所述第二传输电路被配置为,在所述第四时钟信号端所传输的第四时钟信号的控制下,将在所述第二消隐节点处接收的所述第四时钟信号传输至所述第二上拉节点。

27、在一些实施例中,所述选择控制电路包括:第四十四晶体管、第四十五晶体管和第三电容器。所述第四十四晶体管的控制极与所述选择控制信号端电连接,所述第四十四晶体管的第一极与所述输入信号端电连接,所述第四十四晶体管的第二极与所述第四十五晶体管的第一极及所述第三防漏电节点电连接。所述第四十五晶体管的控制极与所述选择控制信号端电连接,所述第四十五晶体管的第二极与所述第一消隐节点电连接。所述第三电容器的第一端与所述第一消隐节点电连接,所述第三电容器的第二端与所述第三电压信号端电连接。所述第三防漏电电路包括:第四十六晶体管。所述第四十六晶体管的控制极与所述第一消隐节点电连接,所述第四十六晶体管的第一极与所述防漏电输入节点电连接,所述第四十六晶体管的第二极与所述第三防漏电节点电连接。所述第三输入电路包括:第四十七晶体管。所述第四十七晶体管的控制极与所述第一消隐节点电连接,所述第四十七晶体管的第一极与所述第四时钟信号端电连接,所述第四十七晶体管的第二极与所述第二消隐节点电连接。所述第一传输电路包括:第四十八晶体管和第四十九晶体管。所述第四十八晶体管的控制极与所述第四时钟信号端电连接,所述第四十八晶体管的第一极与所述第二消隐节点电连接,所述第四十八晶体管的第二极与所述第四十九晶体管的第一极及所述第一防漏电节点电连接。所述第四十九晶体管的控制极与所述第四时钟信号端电连接,所述第四十九晶体管的第二极与所述第一上拉节点电连接。所述第二传输电路包括:第五十晶体管和第五十一晶体管。所述第五十晶体管的控制极与所述第四时钟信号端电连接,所述第五十晶体管的第一极与所述第二消隐节点电连接,所述第五十晶体管的第二极与所述第五十一晶体管的第一极及所述第二防漏电节点电连接。所述第五十一晶体管的控制极与所述第四时钟信号端电连接,所述第五十一晶体管的第二极与所述第二上拉节点电连接。

28、另一方面,提供一种如上述任一项所述的移位寄存器的驱动方法。所述驱动方法,包括:在输入阶段,响应于在输入信号端处接收的输入信号,第一输入电路开启,将所述输入信号传输至第一上拉节点。响应于在第一电压信号端处接收的第一电压信号,防漏电输入单元开启,将所述第一电压信号传输至防漏电输入节点;或,响应于在第二电压信号端处接收的第二电压信号,所述防漏电输入单元开启,将所述第二电压信号传输至所述防漏电输入节点。在所述第一上拉节点的电压的控制下,防漏电单元开启,将来自所述防漏电输入节点的第一电压信号或第二电压信号传输至第一防漏电节点。

29、又一方面,提供一种栅极驱动电路。所述栅极驱动电路包括:多级级联的如上述任一实施例所述的移位寄存器。

30、又一方面,提供一种显示装置。所述显示装置包括:如上述任一实施例所述的栅极驱动电路。

- 还没有人留言评论。精彩留言会获得点赞!