反相器、栅极驱动电路以及显示面板的制作方法

本申请涉及显示,具体涉及一种反相器、栅极驱动电路以及显示面板。

背景技术:

1、目前,由于阵列基板上栅极驱动集成(gate driven on array,goa)技术在成本和功能性上相对于栅极覆晶薄膜技术(gate chip on film,gate cof)具备很大优势,因此成为了各面板厂开发的重点方向。

2、在日常使用中,中大尺寸显示面板相对于小尺寸显示面板具有使用生命周期更长的需求,因此要求中大尺寸显示面板产品在较长的使用生命周期内保证较好的稳定性,然而goa技术中的反相器模块在长时间保持正向电压的情况下将出现晶体管阈值电压正漂的现象,进而导致goa电路出现的失效情况。在相关技术中,主要采用双反相器对称设计进行交替工作的方案,来避免反相器模块中晶体管长时间保持正向电压而导致的晶体管阈值电压正漂的现象,但这会增加较多的薄膜晶体管,从而导致goa电路需占据较宽的显示区域,这不利于显示面板屏占比的提升。

技术实现思路

1、本申请提供一种反相器、栅极驱动电路以及显示面板,旨在解决目前双反相器对称设计不利于显示面板屏占比提升的技术问题。

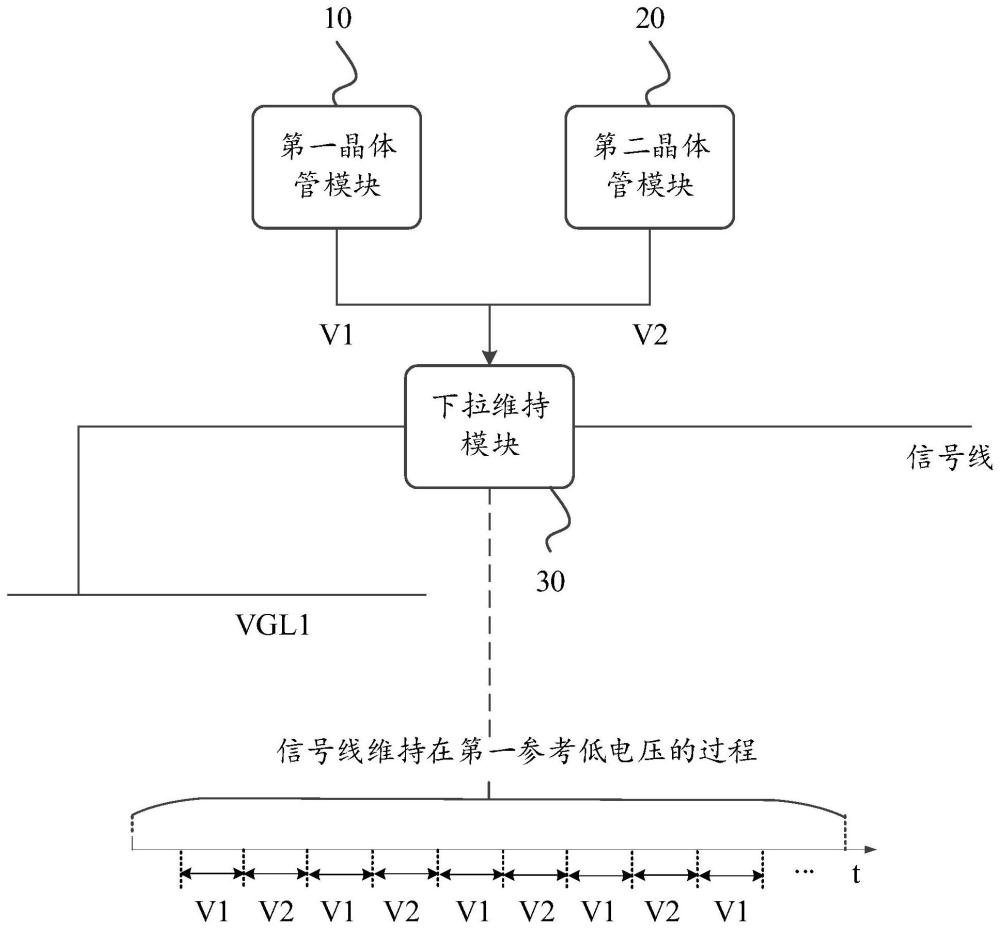

2、第一方面,本申请提供一种反相器,包括:

3、第一晶体管模块,第一晶体管模块用于间歇地输出第一预设电压;

4、第二晶体管模块,第二晶体管模块用于间歇地输出第二预设电压;

5、下拉晶体管模块,下拉晶体管模块的第一端连接信号线,下拉晶体管模块的第二端接入第一参考低电压;

6、其中,下拉晶体管模块的控制端交替地接收第一预设电压与第二预设电压,以使得下拉晶体管模块将信号线的电压维持在第一参考低电压。

7、在一些实施例中,第一预设电压的电压值大于第一参考低电压的电压值,且第二预设电压的电压值大于第一参考低电压的电压值。

8、在一些实施例中,第一预设电压的电压值大于第二预设电压的电压值。

9、在一些实施例中,第一晶体管模块包括至少一个高电位导通晶体管,第二晶体管模块包括至少一个低电位导通晶体管;

10、其中,第一晶体管模块以及第二晶体管模块的控制端接入同步的时钟信号。

11、在一些实施例中,第一晶体管模块包括第一晶体管以及第二晶体管;

12、第一晶体管的第一端接入第一输入信号,第一晶体管的第二端与第二晶体管的第一端连接;

13、第二晶体管的第二端接入第二参考低电压,下拉晶体管模块的控制端连接于第一晶体管与第二晶体管之间的第一节点;

14、将信号线的电压维持在第一参考低电压的过程中,第一晶体管间歇地导通且第二晶体管保持截止状态,以基于第一输入信号将第一节点间歇地保持为第一预设电压。

15、在一些实施例中,第一晶体管模块还包括第三晶体管以及第四晶体管;

16、第三晶体管的第一端接入第一输入信号,第三晶体管的第二端与第四晶体管的第一端连接;

17、第四晶体管的第二端接入第二参考低电压,第一晶体管的控制端连接于第三晶体管与第四晶体管之间的第二节点;

18、将信号线的电压维持在第一参考低电压的过程中,第三晶体管间歇地导通且第四晶体管保持截止状态,以使得第二节点间歇地向第一晶体管的控制端提供控制电压。

19、在一些实施例中,第三晶体管的控制端接入第二输入信号,第一输入信号与第二输入信号中的至少一者为时钟信号;或者

20、第三晶体管的控制端接入第一输入信号,第一输入信号为时钟信号。

21、在一些实施例中,第一输入信号与第二输入信号为时钟信号,且第一输入信号与第二输入信号同步;

22、第一输入信号的高电平电压小于第二输入信号的高电平电压,第一输入信号的低电平电压小于第二输入信号的低电平电压。

23、在一些实施例中,第二晶体管模块包括第五晶体管;

24、第五晶体管的第一端接入第二预设电压,第五晶体管的第二端连接于第一节点;

25、将信号线的电压维持在第一参考低电压的过程中,第五晶体管间歇地导通,且当第五晶体管与第一晶体管中一者处于导通状态时,则另外一者处于截止状态,以将第一节点交替地改变为第一预设电压与第二预设电压。

26、在一些实施例中,第二晶体管模块还包括第六晶体管;

27、第六晶体管的第一端接入第三输入信号,第六晶体管的第二端与第五晶体管的控制端连接;

28、将信号线的电压维持在第一参考低电压的过程中,第六晶体管间歇地向第五晶体管的控制端提供控制电压。

29、在一些实施例中,第六晶体管的控制端接入第四输入信号,第三输入信号与第四输入信号为时钟信号,且第三输入信号与第四输入信号同步;

30、第三输入信号的低电平电压大于第四输入信号的低电平电压,且第三输入信号的低电平电压小于第二预设电压;

31、第三输入信号的高电平电压小于第四输入信号的高电平电压,且第三输入信号的高电平电压大于第二预设电压。

32、在一些实施例中,下拉晶体管模块包括第七晶体管,信号线包括扫描信号线,第七晶体管的第一端连接扫描信号线,第七晶体管的第二端接入第一参考低电压;和/或者

33、下拉晶体管模块包括第八晶体管,信号线包括级传信号线,第八晶体管的第一端连接级传信号线,第八晶体管的第二端接入第一参考低电压。

34、第二方面,本申请提供一种栅极驱动电路,包括如第一方面所述的反相器。

35、第三方面,本申请提供一种显示面板,包括如第二方面所述的栅极驱动电路。

36、本申请通过第一晶体管模块间歇地输出第一预设电压,并且第二晶体管模块间歇地输出第二预设电压,同时通过让下拉晶体管模块的控制端交替地接收第一预设电压与第二预设电压并保持导通状态,从而最终可以将信号线(例如扫描驱动线、级传信号线)维持在第一参考低电压保持对应像素行goa电路的拉低状态。由于第一晶体管模块与第二晶体管模块间歇地导通,同时第一晶体管模块与第二晶体管模块共用了下拉晶体管模块,在避免第一晶体管模块与第二晶体管模块长时间导通出现的晶体管阈值电压正漂现象的同时,还可以减少反相器晶体管的数量,最终实现减小goa电路所占据显示区面积并提高显示面板屏占比的目的。

技术特征:

1.一种反相器,其特征在于,包括:

2.如权利要求1所述的反相器,其特征在于,所述第一预设电压的电压值大于所述第一参考低电压的电压值,且所述第二预设电压的电压值大于所述第一参考低电压的电压值。

3.如权利要求2所述的反相器,其特征在于,所述第一预设电压的电压值大于所述第二预设电压的电压值。

4.如权利要求1所述的反相器,其特征在于,所述第一晶体管模块包括至少一个高电位导通晶体管,所述第二晶体管模块包括至少一个低电位导通晶体管;

5.如权利要求1所述的反相器,其特征在于,所述第一晶体管模块包括第一晶体管以及第二晶体管;

6.如权利要求5所述的反相器,其特征在于,所述第一晶体管模块还包括第三晶体管以及第四晶体管;

7.如权利要求6所述的反相器,其特征在于,所述第三晶体管的控制端接入第二输入信号,所述第一输入信号与所述第二输入信号中的至少一者为时钟信号;或者

8.如权利要求7所述的反相器,其特征在于,所述第一输入信号与所述第二输入信号为时钟信号,且所述第一输入信号与所述第二输入信号同步;

9.如权利要求5所述的反相器,其特征在于,所述第二晶体管模块包括第五晶体管;

10.如权利要求9所述的反相器,其特征在于,所述第二晶体管模块还包括第六晶体管;

11.如权利要求10所述的反相器,其特征在于,所述第六晶体管的控制端接入第四输入信号,所述第三输入信号与所述第四输入信号为时钟信号,且所述第三输入信号与所述第四输入信号同步;

12.如权利要求1所述的反相器,其特征在于,所述下拉晶体管模块包括第七晶体管,所述信号线包括扫描信号线,所述第七晶体管的第一端连接所述扫描信号线,所述第七晶体管的第二端接入所述第一参考低电压;和/或

13.一种栅极驱动电路,其特征在于,包括如权利要求1至12任一项所述的反相器。

14.一种显示面板,其特征在于,包括如权利要求13所述的栅极驱动电路。

技术总结

本申请提供一种反相器、栅极驱动电路以及显示面板,反相器包括:第一晶体管模块,第一晶体管模块用于间歇地输出第一预设电压;第二晶体管模块,第二晶体管模块用于间歇地输出第二预设电压;下拉晶体管模块,下拉晶体管模块的第一端用于连接信号线,下拉晶体管模块的第二端用于接入第一参考低电压;其中,下拉晶体管模块的控制端用于交替地接收第一预设电压与第二预设电压,以使得下拉晶体管模块保持导通状态并将信号线维持在第一参考低电压。本申请在避免第一晶体管模块与第二晶体管模块长时间导通出现的晶体管阈值电压正漂现象的同时,还可以减少反相器晶体管的数量,有利于提高显示面板屏占比。

技术研发人员:李广耀

受保护的技术使用者:深圳市华星光电半导体显示技术有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!