一种显示面板、驱动方法及装置与流程

本技术涉及显示,尤其涉及一种显示面板、驱动方法及装置。

背景技术:

1、随着显示技术的发展,现有的显示面板可以做到低刷新频率进行显示,例如ltpo(low temperature polycrystalline oxide,低温多晶氧化物)产品能够以1hz~120hz的刷新频率进行显示。在一些特定情形下,当显示面板的显示画面不变或者显示画面更新较慢时,像素单元的驱动电路可以以低频率进行刷新。然而,当显示面板中仅部分区域画面更新较快且其余区域画面不变或者更新相对较慢时,为了使保证画面更新较快的部分区域能够实现画面的正常显示,现有的做法为全屏同时进行数据电压写入及刷新,这就导致功耗高的问题。

技术实现思路

1、有鉴于此,本技术提供一种显示面板、驱动方法及装置,以利于解决现有技术中存在的在显示面板中仅部分区域画面更新较快时存在功耗高的问题。

2、第一方面,本技术实施例提供一种显示面板,包括:至少一个移位寄存器组,第一时钟信号线组和第二时钟信号线组。移位寄存器组包括n级级联的移位寄存器。移位寄存器包括第一输出模块、第二输出模块、触发模块及第一控制模块,第一输出模块的输出端与第二输出模块的输出端电连接,第一输出模块的输出端用于输出使能信号且第二输出模块的输出端用于输出非使能信号,第一控制模块的输出端与第一输出模块的控制端电连接,触发模块的输出端与第二输出模块的控制端电连接。第i+1级移位寄存器的触发模块的输入端与第i级移位寄存器的输出端电连接,1≤i≤n-1。第一时钟信号线组包括第一时钟信号线和第二时钟信号线且第二时钟信号线组中包括第一时钟信号线和第二时钟信号线。第i级移位寄存器的触发模块的控制端与第一时钟信号线组中的第一时钟信号线电连接,第i级移位寄存器的第一控制模块的控制端与第一时钟信号线组中的第二时钟信号线电连接。第i+1级移位寄存器的触发模块的控制端与第二时钟信号线组中的第二时钟信号线电连接,第i+1级移位寄存器的第一控制模块的控制端与第二时钟信号线组中的第一时钟信号线电连接。其中,显示面板的工作模式包括第一模式。在第一模式下且第i级移位寄存器输出使能信号时,第一时钟信号线组中的第二时钟信号线用于传输有效电平且第二时钟信号线组中的第二时钟信号线用于传输非有效电平。在第一模式下且第一时钟信号线组中的第一时钟信号线在第i级移位寄存器输出使能信号后首次传输有效电平时,第二时钟信号线组中的第一时钟信号线用于传输非有效电平。

3、在第一方面的一实施例中,显示面板还包括:像素电路,像素电路包括驱动晶体管及数据写入晶体管,驱动晶体管用于产生驱动电流。数据写入晶体管的第一极与数据线电连接,数据写入晶体管的第二极与驱动晶体管电连接,数据写入晶体管的栅极与第一扫描线电连接。其中,至少一个移位寄存器组中包括第一移位寄存器组,第一移位寄存器组中的第一输出模块的输出端及第二输出模块的输出端与第一扫描线电连接。

4、在第一方面的一实施例中,显示面板还包括:像素电路,像素电路包括驱动晶体管、数据写入晶体管及阈值写入晶体管,驱动晶体管用于产生驱动电流。数据写入晶体管的第一极与数据线电连接,数据写入晶体管的第二极与驱动晶体管电连接,数据写入晶体管的栅极与第一扫描线电连接。阈值写入晶体管的第一极与驱动晶体管的第一极电连接,阈值写入晶体管的第二极与驱动晶体管的栅极电连接,阈值写入晶体管的栅极与第二扫描线电连接。其中,至少一个移位寄存器组中包括第二移位寄存器组,第二移位寄存器组中的第一输出模块的输出端及第二输出模块的输出端与第二扫描线电连接。

5、在第一方面的一实施例中,显示面板还包括:像素电路,像素电路包括驱动晶体管、数据写入晶体管及第一复位晶体管,驱动晶体管用于产生驱动电流。数据写入晶体管的第一极与数据线电连接,数据写入晶体管的第二极与驱动晶体管电连接,数据写入晶体管的栅极与第一扫描线电连接。第一复位晶体管的第一极与复位线电连接,第一复位晶体管的第二极与驱动晶体管的栅极电连接,第一复位晶体管的栅极与第三扫描线电连接。其中,至少一个移位寄存器组中包括第三移位寄存器组,第三移位寄存器组中的第一输出模块的输出端及第二输出模块的输出端与第三扫描线电连接。

6、在第一方面的一实施例中,在第一模式下,第i级移位寄存器结束输出使能信号至第1级移位寄存器触发启动前,数据线传输的信号处于保持状态。

7、在第一方面的一实施例中,触发模块包括:第一晶体管。第一晶体管的第一极与触发模块的触发端电连接,第一晶体管的第二极与第二输出模块的控制端电连接,第一晶体管的栅极与对应的时钟信号线电连接。其中,第i级移位寄存器的触发模块中的第一晶体管的栅极与第一时钟信号线组中的第一时钟信号线电连接,第i+1级移位寄存器的触发模块中的第一晶体管的栅极与第二时钟信号线组中的第二时钟信号线电连接。

8、在第一方面的一实施例中,第一控制模块包括:控制晶体管,控制晶体管的第一极用于接收对应的时钟信号线传输的时钟信号,控制晶体管的第二极与第一输出模块的控制端电连接,控制晶体管的栅极与对应的时钟信号线电连接,其中,第i级移位寄存器的第一控制模块中的控制晶体管的栅极与第一时钟信号线组中的第二时钟信号电连接,第i+1级移位寄存器的第一控制模块中的控制晶体管的栅极与第二时钟信号线组中的第一时钟信号电连接。

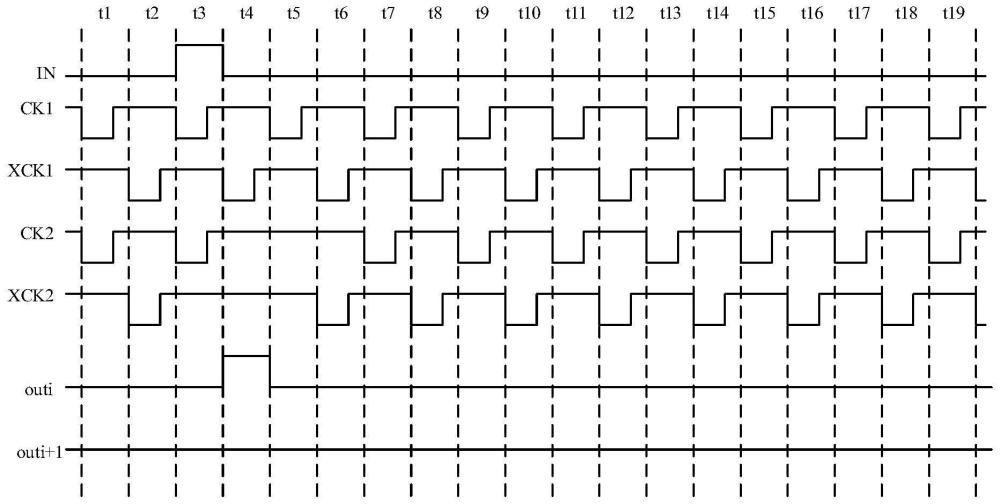

9、在第一方面的一实施例中,第一输出模块包括第一输出晶体管,第一输出晶体管的第一极电连接第一电压源线,第一输出晶体管的第二极与第一输出模块的输出端电连接,第一输出晶体管的栅极与第一控制模块的输出端电连接。

10、和/或,

11、第二输出模块包括第二输出晶体管,第二输出晶体管的第一极电连接第二电压源线,第二输出晶体管的第二极与第二输出模块的输出端电连接,第二输出晶体管的栅极与触发模块的输出端电连接。

12、第二方面,本技术实施例提供一种显示面板的驱动方法,用于驱动第一方面提供的的显示面板至少工作于第一模式下。

13、在第二方面的一种实现方式中,方法驱动显示面板工作于第一模式下。该方法包括:确定i值。第一时钟信号线组中的第一时钟信号线传输的时钟信号的频率及占空比不变,第一时钟信号线组中的第二时钟信号线传输的时钟信号的频率及占空比不变。在第1级的移位寄存器的触发端被触发后至第i级移位寄存器的第一输出模块输出使能信号前,第二时钟信号线组中的第一时钟信号线与第一时钟信号线组中的第一时钟信号线传输的时钟信号同步,第二时钟信号线组中的第二时钟信号线与第一时钟信号线组中的第二时钟信号线传输的时钟信号同步。第i级移位寄存器输出使能信号时,第二时钟信号线组中的第二时钟信号线传输非有效电平。第一时钟信号线组中的第一时钟信号线在第i级移位寄存器输出使能信号后首次传输有效电平时,第二时钟信号线组中的第一时钟信号线传输非有效电平。

14、在第二方面的一种实现方式中,该方法还包括:第一时钟信号线组中的第一时钟信号线在第i级移位寄存器输出使能信号后首次传输非效电平至第1级移位寄存器触发启动前,第二时钟信号线组中的第一时钟信号线与第一时钟信号线组中的第一时钟信号线传输的时钟信号同步,第二时钟信号线组中的第二时钟信号线与第一时钟信号线组中的第二时钟信号线传输的时钟信号同步。

15、在第二方面的一种实现方式中,显示面板还包括像素电路,像素电路包括驱动晶体管及数据写入晶体管,驱动晶体管用于产生驱动电流,数据写入晶体管的第一极与数据线电连接,数据写入晶体管的第二极与驱动晶体管电连接。方法还包括:第i级移位寄存器结束输出使能信号至第1级移位寄存器触发启动前,数据线传输的信号处于保持状态。

16、第三方面,本技术实施例提供一种显示装置,显示装置包括第一方面的任意一项实施例提供的显示面板。

17、在本技术实施例中,当显示面板工作于第一模式时,通过在第级移位寄存器输出使能信号之后使第二时钟信号线暂停输出有效电平信号,使得第级移位寄存器无法输出使能信号,进而使得级联于第i+1级移位寄存器之后移位寄存器也无法输出使能信号,因此实现了该显示面板第1级至第i级移位寄存器对应区域的画面刷新频率大于第级至第n级移位寄存器对应区域的画面刷新频率。其中,显示面板工作于第一模式时为分屏分频显示。在本实施例中,采用至少两组时钟信号线控制显示面板100的驱动,降低了显示面板分屏分频率显示的实现难度且降低显示面板的功耗。

- 还没有人留言评论。精彩留言会获得点赞!