一种高速低损耗的薄膜铌酸锂相位编码光子集成芯片的制作方法

本发明涉及光通信,特别涉及一种高速低损耗的薄膜铌酸锂相位编码光子集成芯片。

背景技术:

1、相位编码原理是基于在不等臂马赫-曾德尔干涉仪调制器(英文全称asymmetricmach-zehnder interferometer modulator,中文简称 amzm)的高速调相器中,通过数字调制的方式组合实现不同相位编码,进而实现高速的相位编码。

2、常用的相位编码的量子密钥分发(qkd)系统方案中,多采用传统分立的光学元器件通过光纤熔接等技术搭建而成。而传统的分立光学元器件光纤系统在在实际生产中,通常要求光纤切割的工艺精度达到百微米级甚至更低,这一点往往很难保证。这是制约相位编码qkd实用化和产品化的关键难点。除此之外随着调制带宽的逐渐增加,很难在系统中使用光纤熔接实现延时环,因此考虑在集成光学片上制作不等臂的amzm,可以大大减小体积,减少结构的复杂度,降低器件功耗,具有稳定性高、结构更紧凑、相位延时精度高、批量制作成本低等优点。

3、为满足高速相位调制,系统中的延时环长度往往需达到厘米量级,常见硅基波导非调制区的传播损耗典型值为2 db/cm ,其调制区波导典型损耗值达到10.8 db/cm,iii-iv族材料的波导损耗典型值为1.5 db/cm,上述材料均不满足系统低损耗要求。但是绝缘体上的薄膜铌酸锂材料(lnoi)无论在调制区还是非调制区,波导传播损耗典型值都为0.2db/cm,同单位距离下,相比前述材料可降低一个数量级。因此具有低损耗,高电光效应,稳定性高的lnoi材料成为了量子通信保密系统中的最佳选择方案。

技术实现思路

1、针对现有技术存在以上缺陷,本发明提出一种高速低损耗的薄膜铌酸锂相位编码光子集成芯片。

2、本发明的技术方案是这样实现的:

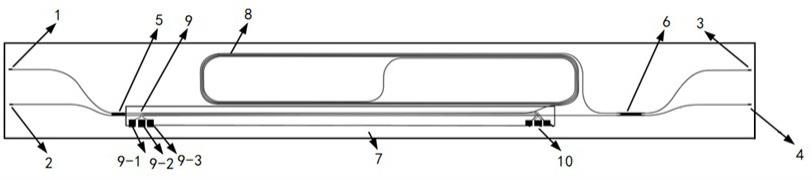

3、一种高速低损耗的薄膜铌酸锂相位编码光子集成芯片,所述芯片包括集成在绝缘体薄膜铌酸锂基上的第一模斑转换器、第二模斑转换器、第三模斑转换器、第四模斑转换器、第一多模干涉器、第二多模干涉器、电调高速相移器以及延时环,所述第一模斑转换器、第二模斑转换器分别通过不同的s波导连接第一多模干涉器输入端口,所述第一多模干涉器分别通过长臂以及短臂连接第二多模干涉器,所述长臂上连接有延时环,所述长臂以及短臂上均通过电调高速相移器并与其上行波电极连接,所述第二多模干涉器分别通过不同的s波导连接第三模斑转换器、第四模斑转换器。

4、优选地,所述行波电极包括连接在长臂上的第一行波电极组以及连接短臂上的第二行波电极组,所述第一行波电极组包括第一电极、第二电极、第三电极,三个电极设置在包含有两条平行脊线的薄膜铌酸锂脊波导上,所述第一电极、第三电极为接地电极且分别设置在两条脊线的外侧,所述第二电极为阳极电极且设置在两条脊线的内侧,三个电极高度h相等,且水平方向上距离相邻脊线的距离g也相等,两条所述脊线的宽度w相同,且两条所述脊线的高度h也相同,所述w=1.6um,h=0.5un,h=0.25um,g为1.7 um。

5、优选地,所述延时环的波导长度通过公式l=c/neff*t得到,其中l为延时环波导长度,neff为薄膜铌酸锂波导有效折射率,c为光速,t为延时时间,所述neff=2.2,c=3*10^8m/s,t取390ps,得l设计长度为5.318 cm。

6、优选地,所述电调高速相移器的电光响应 3 db 带宽在 12 ghz 以上。

7、优选地,所述第一多模干涉器、第二多模干涉器均采用多模干涉器mmi2*2,所述第一多模干涉器、第二多模干涉器与延时环通过波导构成一个不等臂的马赫曾德尔调制器,其中第一多模干涉器与延时环之间设有外部金属制成的高速调制行波电极。

8、优选地,所述延时环中的弯道绕制采用90°欧拉曲线。

9、优选地,所述90°欧拉曲线的有效半径大于150um。

10、与现有技术相比,本发明有以下有益效果:

11、本发明的一种低损耗高集成相位编码光子集成芯片,将3db耦合器与相位调制器利用光波导器件设计并集成在同一片光子芯片上,系统具有成本低、体积小、集成度高、稳定性好等优点,另外,利用多模干涉器mmi、波导+行波电极构成的高速调相器、波导延时线实现的amzi干涉环,实现了qkd系统的相位编码,具有系统简单,编码速度高、可靠性高等优点;

12、本发明提供的一种低损耗高集成相位编码光子集成芯片,利用半导体工艺保证了amzi臂长差的一致性,解决了传统相位编码qkd系统光纤切割精度难以保证的问题。

13、本发明提供的一种低损耗高集成相位编码光子集成芯片,可作为量子密钥分发(qkd)发射端器件,其发射端alice,只需要1个单光子源,相比plc波导的被动调制相位编码qkd系统的4或8个单光子源及4个amzi干涉环;大大降低了成本和系统复杂度。

14、本发明提供的一种低损耗高集成相位编码光子集成芯片,其编码amzi的高速调相器可以通过数字调制的方式组合实现0,π/2,π,3π/2,4种相位编码,实现高速的相位编码。

15、5、本发明提供的一种低损耗高集成相位编码光子集成芯片,可以同时应用在量子密钥分发接收端解码设计中,实现器件的统一性,节省研发和制造成本。

技术特征:

1.一种高速低损耗的薄膜铌酸锂相位编码光子集成芯片,其特征在于,所述芯片包括集成在绝缘体薄膜铌酸锂基上的第一模斑转换器、第二模斑转换器、第三模斑转换器、第四模斑转换器、第一多模干涉器、第二多模干涉器、电调高速相移器以及延时环,所述第一模斑转换器、第二模斑转换器分别通过不同的s波导连接第一多模干涉器输入端口,所述第一多模干涉器分别通过长臂以及短臂连接第二多模干涉器,所述长臂上连接有延时环,所述长臂以及短臂上均通过电调高速相移器并与其上行波电极连接,所述第二多模干涉器分别通过不同的s波导连接第三模斑转换器、第四模斑转换器。

2.如权利要求1所述的高速低损耗的薄膜铌酸锂相位编码光子集成芯片,其特征在于,所述行波电极包括连接在长臂上的第一行波电极组以及连接短臂上的第二行波电极组,所述第一行波电极组包括第一电极、第二电极、第三电极,三个电极设置在包含有两条平行脊线的薄膜铌酸锂脊波导上,所述第一电极、第三电极为接地电极且分别设置在两条脊线的外侧,所述第二电极为阳极电极且设置在两条脊线的内侧,三个电极高度h相等,且水平方向上距离相邻脊线的距离g也相等,两条所述脊线的宽度w相同,且两条所述脊线的高度h也相同,所述w=1.6um,h=0.5un,h=0.25um,g为1.7 um。

3.如权利要求1所述的高速低损耗的薄膜铌酸锂相位编码光子集成芯片,其特征在于,所述延时环的波导长度通过公式l=c/neff*t得到,其中l为延时环波导长度,neff为薄膜铌酸锂波导有效折射率,c为光速,t为延时时间,所述neff=2.2,c=3*10^8 m/s,t取390ps,得l设计长度为5.318 cm。

4.如权利要求3所述的高速低损耗的薄膜铌酸锂相位编码光子集成芯片,其特征在于,所述电调高速相移器的电光响应 3 db 带宽在 12 ghz 以上。

5.如权利要求1或2或3或4所述的高速低损耗的薄膜铌酸锂相位编码光子集成芯片,其特征在于,所述第一多模干涉器、第二多模干涉器均采用多模干涉器mmi2*2,所述第一多模干涉器、第二多模干涉器与延时环通过波导构成一个不等臂的马赫曾德尔调制器,其中第一多模干涉器与延时环之间设有外部金属制成的高速调制行波电极。

6.如权利要求1或2或3或4所述的高速低损耗的薄膜铌酸锂相位编码光子集成芯片,其特征在于,所述延时环中的弯道绕制采用90°欧拉曲线。

7.如权利要求6所述的高速低损耗的薄膜铌酸锂相位编码光子集成芯片,其特征在于,所述90°欧拉曲线的有效半径大于150um。

技术总结

本发明属于光通信技术领域,公开了一种高速低损耗的薄膜铌酸锂相位编码光子集成芯片,所述芯片包括集成在绝缘体薄膜铌酸锂基上的第一模斑转换器、第二模斑转换器、第三模斑转换器、第四模斑转换器、第一多模干涉器、第二多模干涉器、电调高速相移器以及延时环。与现有技术相比,将3dB耦合器与相位调制器利用光波导器件设计并集成在同一片光子芯片上,系统具有成本低、体积小、集成度高、稳定性好等优点,另外,利用多模干涉器MMI、波导+行波电极构成的高速调相器、波导延时线实现的AMZI干涉环,可实现QKD系统的相位编码,具有系统简单,编码速度高、可靠性高等有益效果。

技术研发人员:徐涛,黄大骏,齐若琳,周琛

受保护的技术使用者:浙江九州量子信息技术股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!