一种基于掺杂脊型光波导的高带宽SOI调制器

本发明属于集成光子器件和集成光电器件,尤其涉及一种基于掺杂脊型光波导的高带宽soi调制器。

背景技术:

1、为突破微电子技术的物理瓶颈,实现更大带宽、更低延时、更低功耗的数据通信,集成光子技术成为学术和工业界的研究热门方向,其中硅基光子学(silicon photonics,sip)因兼容cmos工艺而得到迅速发展。电光调制器是硅基光子集成芯片的核心器件之一,其功能是将电信号加载到光载波上,以实现光载微波信号的低延时、高速率传输,或在光域中对光载微波信号进行处理。

2、由于硅材料本身的不具有较强的电光效应,硅基相位调制器大多基于等离子色散效应(plasma dispersion effect,pde),即利用载流子浓度的变化实现光折射率的变化。通过掺杂在硅材料中形成pn结、pin结或硅-绝缘体-硅的电容结构(silicon–insulator–silicon capacitors,siscaps)。在施加外部电压时,pn结在反向偏压下增强漂移运动实现载流子耗尽、pin结在正向偏压下实现载流子注入、siscap结构在正向偏压下实现载流子累积,分别实现光波导中载流子浓度随外部偏压的变化而变化,从而达到电光调制的目的。

3、目前基于掺杂的硅基光波导的几何结构多为脊型结构,高速硅基相位调制器多掺杂为pn结,掺杂结构多为两级掺杂或者三级掺杂,即从边缘的电极接触区域到中心波导区域,掺杂浓度逐级降低。中心波导的掺杂浓度越高,外部电压变化引起的载流子浓度变化越大,电光调制效率越高,但是高掺杂也导致了更大的pn结的结电容,从而增加了调制器电极上的电信号的损耗,因此降低了电光带宽。基于目前的硅波导的掺杂方案,硅基调制器的效率和带宽成为了互相制约的两个指标。

技术实现思路

1、本发明目的在于提供一种基于掺杂脊型光波导的高带宽soi调制器,在原两级或三级浓度逐级变化的掺杂结构上,在紧贴脊型波导中心区域的两侧平板波导区域中增设了一级掺杂浓度为1016cm-3量级的低浓度掺杂区,可以极大减小pn结的结电容,从而减少调制器的电损耗,可以在不影响调制效率的情况下,提升调制带宽,以解决现有硅波导的掺杂方案导致的硅基调制器的效率和带宽两个指标互相制约的技术问题。

2、为解决上述技术问题,本发明的具体技术方案如下:

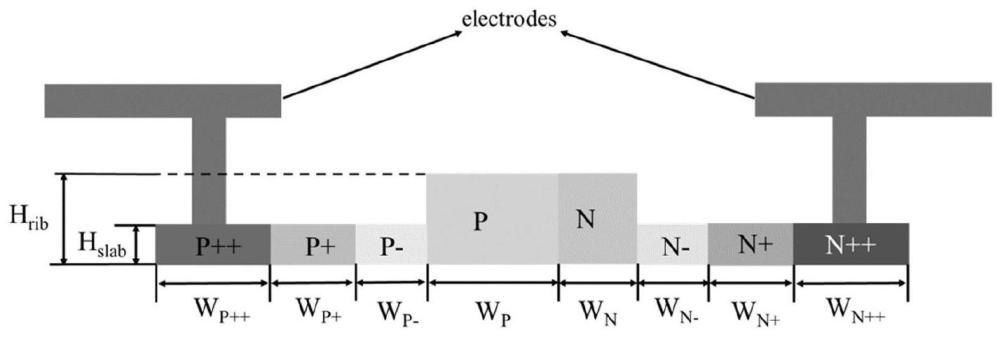

3、本发明所述的基于掺杂脊型光波导的高带宽soi调制器,该调制器通过行波电极将调制信号电压加载在掺杂脊型光波导上,改变波导中的载流子掺杂浓度,进而改变波导材料的折射率,实现了对传播光模式的相位调制功能,扩展驱动两条掺杂脊型波导构成马赫曾德结构,可以实现强度调制功能,若扩展多条脊型掺杂波导,可以实现高阶调制器功能;所述调制器由掺杂脊型光波导和行波电极组成,所述脊型光波导为采用soi工艺制备的掺杂硅脊型波导,该掺杂脊型波导内嵌在sio2包层中,其截面结构包括依次排列的p++掺杂区、p+掺杂区、p-掺杂区、p掺杂区、n掺杂区、n-掺杂区、n+掺杂和n++掺杂区,其中p掺杂区和n掺杂区位于脊型波导的中心区域。脊型波导中心区域高度为hrib,p++、p+、p-、n-、n+、n++区域位于平板波导区域;平板波导区域高度为hslab,脊型波导的中心区域高度hrib高于平板波导区域的高度hslab;传播光模式位于p掺杂区和n掺杂区域所在脊型波导中心区域;p-和n-掺杂区域位于紧贴在脊型中心区域两侧的平板波导区域,其掺杂浓度为1015cm-3~1016cm-3数量级,p-和n-低掺杂浓度区域的存在,在不影响调制效率的前提下,显著减小了调制器的交流结电容,从而减小了调制器的电损耗,进而大幅提升电光带宽;p+和n+掺杂区域是掺杂过渡区,p+掺杂区域位于p-掺杂区和p++掺杂区之间,n+掺杂区位于n-掺杂区和n++掺杂区域之间,p+和n+掺杂区域的掺杂浓度高于p-和n-区域,低于p++和n++掺杂区域;脊型波导的p++区域和n++区域是与行波电极相接触的区域;行波电极位于掺杂脊型波导的上方,通过行波电极上的金属通孔与掺杂脊型波导的p++区域和n++区域的掺杂硅直接连接,形成欧姆接触,同时行波电极的上表面与外部探针或金属引线相连接,用于外部调制电信号输入和与终端阻抗的连接。

4、进一步的,所述脊型光波导p++掺杂区域的掺杂浓度范围为1×1019cm-3~1×1022cm-3,其宽度wp++范围为1μm~6μm。

5、进一步的,所述脊型光波导n++掺杂区域的掺杂浓度范围为1×1019cm-3~1×1022cm-3,其宽度wp++范围为1μm~6μm。

6、进一步的,所述脊型光波导p+掺杂区域的掺杂浓度范围为5×1016cm-3~1×1019cm-3,其宽度wp+范围为0~1μm。

7、进一步的,所述脊型光波导n+掺杂区域的掺杂浓度范围为5×1016cm-3~1×1019cm-3,其宽度wp+范围为0~1μm。

8、进一步的,所述脊型光波导p-掺杂区域的掺杂浓度范围为1×1015cm-3~5×1016cm-3,其宽度wp-范围为200nm~2μm。

9、进一步的,所述脊型光波导n-掺杂区域的掺杂浓度范围为1×1015cm-3~5×1016cm-3,其宽度wp-范围为200nm~2μm。

10、进一步的,所述脊型光波导p掺杂区域的掺杂浓度范围为1×1017cm-3~2×1018cm-3,其宽度wp范围为150nm~350nm。

11、进一步的,所述脊型光波导n掺杂区域的掺杂浓度范围为1×1017cm-3~2×1018cm-3,其宽度wn范围为150nm~350nm。

12、进一步的,所述调制器的行波电极包括共面波导(coplanar waveguide,cpw,也称作为地-信号-地,ground-signal-ground,gsg电极),共面带状线(coplanar stripline,cps,也称作为地-信号,ground-signal,gs电极),以及在gsg电极和gs电极基础上扩展出来的gsgsg和gssgssg电极,用于对单个掺杂脊型波导或多个掺杂脊型波导进行驱动。

13、本发明的一种基于掺杂脊型光波导的高带宽soi调制器具有以下优点:

14、(1)与现有技术相比,本发明提供了一种基于掺杂脊型光波导的高带宽soi调制器,通过在紧贴脊型波导的中心区域的平板波导区域增设浓度为1016cm-3量级或1015cm-3量级的低掺杂区域,在不影响调制器的调制效率的情况下,可以显著减小掺杂pn结的交流结电容,有效减小调制器的电损耗,在配以适合的慢波行波电极的条件下可以实现调制带宽的大幅度提升。

15、(2)与现有技术相比,本发明所需工艺复杂度没有显著提升,且掺杂区浓度和掺杂区域的宽度具有较大的工艺容差。

技术特征:

1.一种基于掺杂脊型光波导的高带宽绝缘衬底上硅soi调制器,其特征在于,所述调制器由掺杂脊型光波导和行波电极组成;所述脊型光波导为采用soi工艺制备的掺杂硅脊型波导,该掺杂脊型波导内嵌在sio2包层中,其截面结构包括依次排列的p++掺杂区、p+掺杂区、p-掺杂区、p掺杂区、n掺杂区、n-掺杂区、n+掺杂和n++掺杂区,其中p掺杂区和n掺杂区位于脊型波导的中心区域,脊型波导中心区域高度为hrib,p++、p+、p-、n-、n+、n++区域位于平板波导区域;平板波导区域高度为hslab,脊型波导的中心区域高度hrib高于平板波导区域的高度hslab;传播光模式位于p掺杂区和n掺杂区域所在脊型波导中心区域;p-和n-掺杂区域位于紧贴在脊型中心区域两侧的平板波导区域,其掺杂浓度为1015cm-3~1016cm-3数量级;p+和n+掺杂区域是掺杂过渡区,p+掺杂区域位于p-掺杂区和p++掺杂区之间,n+掺杂区位于n-掺杂区和n++掺杂区域之间,p+和n+掺杂区域的掺杂浓度高于p-和n-区域,低于p++和n++掺杂区域;脊型波导的p++区域和n++区域是与行波电极相接触的区域;行波电极位于掺杂脊型波导的上方,通过行波电极上的金属通孔与掺杂脊型波导的p++区域和n++区域的掺杂硅直接连接,形成欧姆接触,同时行波电极的上表面与外部探针或金属引线相连接,用于外部调制电信号输入和与终端阻抗的连接。

2.根据权利要求1所述的基于掺杂脊型光波导的高带宽soi调制器,其特征在于,p++掺杂区域的掺杂浓度范围为1×1019cm-3~1×1022cm-3,其宽度wp++范围为1μm~6μm。

3.根据权利要求1所述的基于掺杂脊型光波导的高带宽soi调制器,其特征在于,n++掺杂区域的掺杂浓度范围为1×1019cm-3~1×1022cm-3,其宽度wn++范围为1μm~6μm。

4.根据权利要求1所述的基于掺杂脊型光波导的高带宽soi调制器,其特征在于,p+掺杂区域的掺杂浓度范围为5×1016cm-3~1×1019cm-3,其宽度wp+范围为0~1μm。

5.根据权利要求1所述的基于掺杂脊型光波导的高带宽soi调制器,其特征在于,n+掺杂区域的掺杂浓度范围为5×1016cm-3~1×1019cm-3,其宽度wn+范围为0~1μm。

6.根据权利要求1所述的基于掺杂脊型光波导的高带宽soi调制器,其特征在于,p-掺杂区域的掺杂浓度范围为1×1015cm-3~5×1016cm-3,其宽度wp-范围为200nm~2μm。

7.根据权利要求1所述的基于掺杂脊型光波导的高带宽soi调制器,其特征在于,n-掺杂区域的掺杂浓度范围为1×1015cm-3~5×1016cm-3,其宽度wn-范围为200nm~2μm。

8.根据权利要求1所述的基于掺杂脊型光波导的高带宽soi调制器,其特征在于,p掺杂区域的掺杂浓度范围为1×1017cm-3~2×1018cm-3,其宽度wp范围为150nm~350nm。

9.根据权利要求1所述的基于掺杂脊型光波导的高带宽soi调制器,其特征在于,p掺杂区域的掺杂浓度范围为1×1017cm-3~2×1018cm-3,其宽度wn范围为150nm~350nm。

10.根据权利要求1所述的基于掺杂脊型光波导的高带宽soi调制器,其特征在于,所述行波电极的型式包括共面波导gsg电,共面带状线gs电极,以及在gsg电极和gs电极基础上扩展出来的gsgsg和gssgssg电极。

技术总结

本发明公开了一种基于掺杂脊型光波导的高带宽SOI调制器。所述脊型光波导为采用掺杂硅制备而成的脊型波导,其结构包括P++掺杂区、P+掺杂区、P‑掺杂区、P掺杂区、N掺杂区、N‑掺杂区、N+掺杂区、N++掺杂区,其中P掺杂区和N掺杂区位于脊型波导的中心区域,P++、P+、P‑、N++、N+、N‑掺杂区域位于平板波导区域。以行波电极进行驱动,本发明可以实现高效率高带宽的电光调制。

技术研发人员:恽斌峰,陈逸飞,胡国华,崔一平

受保护的技术使用者:东南大学

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!