具有PUC结构的3DNAND闪存器件及其制备方法

具有puc结构的3d nand闪存器件及其制备方法

技术领域

1.本公开涉及存储器技术领域,尤其涉及一种具有puc结构的3dnand闪存器件及其制备方法。

背景技术:

2.现有技术中的3d nand闪存器件中,通常会采用在外围的cmos电路上继续制备存储单元阵列(peripheral under core,puc)的puc结构来减小芯片(即die)的尺寸。其中,在这种具有puc结构的3d nand闪存器件中,当外围cmos电路制备完成后,可以通过生长出多晶硅层作为存储单元阵列的“衬底”。但是,现有技术中直接采用退火结晶的方式进行多晶硅层衬底(即衬底结构)结晶的方式,使得衬底结构的晶粒尺寸较小,存在大量的晶界,并且晶界的方向和位置都是随机的。因此,衬底结构存在大量的晶界处,会存在许多陷阱,导致该“衬底”迁移率降低,对电子和空穴的传输造成影响。

技术实现要素:

3.(一)要解决的技术问题

4.为解决现有技术中衬底结构直接采用退火结晶所造成的晶界处存在缺陷影响器件性能的技术问题,本公开提供了一种具有puc结构的3d nand闪存器件及其制备方法,以优化具有puc结构的3d nand闪存器件中“衬底”的性能,改善衬底结构的结晶晶粒尺寸,以增大晶粒尺寸,减小晶界数量和陷阱数量,从而提高“衬底”迁移率,降低对电子和空穴的传输的影响。

5.(二)技术方案

6.本公开的一个方面提供了一种具有puc结构的3d nand闪存器件,其中,包括衬底结构,衬底结构作为puc结构的支撑结构,设置于puc结构下方;其中,衬底结构通过金属诱导横向结晶工艺处理形成,以实现横向诱导结晶,晶界方向应多为垂直方向,提高衬底结构的迁移率,降低电子和空穴的传输影响。

7.根据本公开的实施例,衬底结构包括多晶硅层,多晶硅层设置于衬底结构的上部,与puc结构的下部连接设置。

8.根据本公开的实施例,多晶硅层包括未掺杂多晶硅层、n型多晶硅层、p型多晶硅层和离子注入多晶硅层中至少之一。

9.根据本公开的实施例,衬底结构还包括诱导形成层、间隔层和电路层。诱导形成层设置于多晶硅层下方,用于作为衬底结构的导电层;间隔层设置于诱导形成层下方;电路层设置于间隔层下方;其中,间隔层用于间隔电路层和诱导形成层,以确保在金属诱导横向结晶工艺处理的过程中,诱导形成层不会对电路层产生影响。

10.根据本公开的实施例,诱导形成层材料为金属和/或对应的金属硅化物;间隔层为teos层;电路层为cmos层。

11.本公开的另一个方面提供了一种上述的具有puc结构的3d nand闪存器件的制备

方法,其中,包括:形成衬底结构;在衬底结构上形成puc结构,以构成3d nand闪存器件;其中,在形成衬底结构中,包括:通过金属诱导横向结晶工艺处理形成衬底结构,以提高衬底结构的迁移率,降低电子和空穴的传输影响。

12.根据本公开的实施例,在通过金属诱导横向结晶工艺处理形成衬底结构中,包括:形成初始衬底结构;对初始衬底结构进行金属诱导横向结晶工艺处理,形成衬底结构;其中,初始衬底结构包括自下而上依次设置的初始电路层、初始间隔层、非晶硅层和诱导层,分别用于形成衬底结构的电路层、间隔层、多晶硅层和诱导形成层。

13.根据本公开的实施例,在形成初始衬底结构中,包括:在初始电路层上形成初始间隔层;在初始间隔层上形成非晶硅层;在非晶硅层上形成诱导层。

14.根据本公开的实施例,在对初始衬底结构进行金属诱导横向结晶工艺处理,形成衬底结构中,包括:以300℃-800℃的退火温度,在氮气或氢气的气体氛围中对初始衬底结构执行热退火工艺,以形成衬底结构。

15.根据本公开的实施例,在对初始衬底结构进行金属诱导横向结晶工艺处理,形成衬底结构之前,还包括:对非晶硅层进行原位掺杂工艺处理,形成n型非晶硅层或p型非晶硅层;或者对所述非晶硅层进行离子注入工艺处理,形成离子非晶硅层。

16.(三)有益效果

17.本公开提供了一种具有puc结构的3d nand闪存器件及其制备方法。其中,该3d nand闪存器件包括衬底结构,衬底结构作为puc结构的支撑结构,设置于puc结构下方;其中,衬底结构通过金属诱导横向结晶工艺处理形成,以实现横向诱导结晶,晶界方向应多为垂直方向,提高衬底结构的迁移率,降低电子和空穴的传输影响。因此,可以实现对具有puc结构的3d nand闪存器件中“衬底”的性能优化,改善衬底结构的结晶晶粒尺寸,从而增大晶粒尺寸,减小晶界数量和陷阱数量,进一步提高“衬底”迁移率,降低对电子和空穴的传输的影响。

附图说明

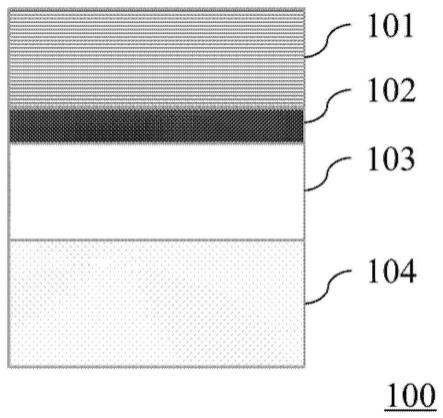

18.图1示意性示出了根据本公开实施例的具有puc结构的3d nand闪存器件的衬底结构100的结构组成图;

19.图2示意性示出了根据本公开实施例的具有puc结构的3d nand闪存器件的制备方法流程图;

20.图3示意性示出了根据本公开实施例的具有puc结构的3d nand闪存器件的未掺杂衬底结构的加工过程图;

21.图4示意性示出了根据本公开实施例的具有puc结构的3d nand闪存器件的进行原位掺杂的衬底结构的加工过程图;

22.图5示意性示出了根据本公开实施例的具有puc结构的3d nand闪存器件的进行离子注入的衬底结构的加工过程图。

具体实施方式

23.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

24.需要说明的是,在附图或说明书正文中,未绘示或描述的实现方式,均为所属技术领域中普通技术人员所知的形式,并未进行详细说明。此外,上述对各元件和方法的定义并不仅限于实施例中提到的各种具体结构、形状或方式,本领域普通技术人员可对其进行简单地更改或替换。

25.还需要说明的是,实施例中提到的方向用语,例如“上”、“下”、“前”、“后”、“左”、“右”等,仅是参考附图的方向,并非用来限制本公开的保护范围。贯穿附图,相同的元素由相同或相近的附图标记来表示。在可能导致对本公开的理解造成混淆时,将省略常规结构或构造。

26.并且图中各部件的形状和尺寸不反映真实大小和比例,而仅示意本公开实施例的内容。另外,在权利要求中,不应将位于括号之间的任何参考符号构造成对权利要求的限制。

27.再者,单词“包含”不排除存在未列在权利要求中的元件或步骤。位于元件之前的单词“一”或“一个”不排除存在多个这样的元件。

28.说明书与权利要求中所使用的序数例如“第一”、“第二”、“第三”等的用词,以修饰相应的元件,其本身并不意味着该元件有任何的序数,也不代表某一元件与另一元件的顺序或是制造方法上的顺序,这些序数的使用仅用来使具有某命名的一元件得以和另一具有相同命名的元件能做出清楚区分。

29.本领域那些技术人员可以理解,可以对实施例中的设备中的模块进行自适应性地改变并且把他们设置在与该实施例不同的一个或多个设备中。可以把实施例中的模块或单元或组件组合成一个模块或单元或组件,以及此外可以把他们分成多个子模块或子单元或子组件。除了这样的特征和/或过程或者单元中的至少一些是相互排斥之外,可以采用任何组合对本说明书(包括伴随的权利要求、摘要和附图)中公开的所有特征以及如此公开的任何方法或者设备的所有过程或单元进行组合。除非另外明确陈述,本说明书(包括伴随的权利要求、摘要和附图)中公开的每个特征可以由提供相同、等同或相似目的的代替特征来代替。并且,在列举了若干装置的单元权利要求中,这些装置中的若干个可以是通过同一个硬件项来具体体现。

30.类似地,应当理解,为了精简本公开并帮助理解各个公开方面的一个或多个,在上面对本公开的示例性实施例的描述中,本公开的各个特征有时被一起分组到单个实施例、图、或者对其的描述中。然而,并不应将该公开的方法解释成反映如下意图:即所要求保护的本公开要求比在每个权利要求中所明确记载的特征更多的特征。更确切地说,如下面的权利要求书所反映的那样,公开方面在于少于前面公开的单个实施例的所有特征。因此,遵循具体实施方式的权利要求书由此明确地并入该具体实施方式,其中每个权利要求本身都作为本公开的单独实施例。

31.在现有的具有puc结构中,在如外围的cmos电路层上形成的多晶硅衬底,通常可以采用热退火方式将非晶硅变为多晶硅,但是,这种方式晶粒尺寸较小会产生大量的晶界,因而,存在大量的陷阱,并且晶界的方向也是随机的。

32.为解决现有技术中衬底结构直接采用退火结晶所造成的晶界处存在缺陷影响器件性能的技术问题,本公开提供了一种具有puc结构的3d nand闪存器件及其制备方法,以优化具有puc结构的3d nand闪存器件中“衬底”的性能,改善衬底结构的结晶晶粒尺寸,以

增大晶粒尺寸,减小晶界数量和陷阱数量,从而提高“衬底”迁移率,降低对电子和空穴的传输的影响。

33.如图1所示,本公开的一个方面提供了一种具有puc结构的3d nand闪存器件,其中,包括衬底结构100,衬底结构100作为puc结构的支撑结构,设置于puc结构下方;

34.其中,衬底结构100通过金属诱导横向结晶(metal-induced lateral crystallization,简称milc)工艺处理形成,以实现横向诱导结晶,晶界方向应多为垂直方向,提高衬底结构的迁移率,降低电子和空穴的传输影响。

35.通过金属诱导横向结晶工艺对具有puc结构的3d nand闪存器件进行处理,实际是实现了针对衬底结构100的衬底结构优化,实现衬底结构100中的晶粒尺寸更大、缺陷数量显著减少的衬底结构,如多晶硅衬底结构,从而提高器件的整体性能。

36.其中,金属诱导横向结晶工艺一般是需要利用金属如镍(ni)等在衬底结构100的(如非晶硅薄膜)表面形成诱导层,之后诱导非晶硅横向结晶生成多晶硅薄膜。该方法可以诱导生成尺寸在几十到几百微米的晶粒,并且晶界将会大都只存在在垂直方向(水平或其他方向晶界应很少),可以显著减少晶界数量和缺陷,从而有助于提高器件的整体性能。

37.因此,相对于现有技术具有puc结构的3d nand闪存器件的传统热退火工艺直接形成多晶硅衬底结构的方式,通过milc工艺制备的衬底结构(如多晶硅衬底)的晶粒尺寸更大、晶界方向为垂直方向,极大减少了晶界处的陷阱,显著提高器件整体性能。而且,由于milc方法制备的晶粒尺寸很大(晶粒尺寸在几十到几百微米),因此,在3d nand闪存器件中,大多数沟道孔将落在晶粒内部,因此,可以认为这些沟道孔在单晶硅上,从而可以进一步达到提升器件整体性能的效果。

38.如图1所示,根据本公开的实施例,衬底结构100包括多晶硅层101,多晶硅层101设置于衬底结构100的上部,与puc结构的下部连接设置。

39.在puc结构的3d nand闪存器件中,由于采用milc方法对衬底结构进行处理,可以使得衬底结构100的多晶硅层101的横向诱导结晶的晶粒尺寸较大,因此,在大多数区域可以将衬底结构100的多晶硅层101认定为单晶硅。

40.其中,利用milc工艺形成的多晶硅层101后续会与3d nand闪存器件的多晶硅的沟道相连。其中,多晶硅层101的材料仍可以硅衬底为主,以利于形成具有n型或者p型掺杂的衬底结构100。其中,多晶硅层101厚度20nm~1um,以确保puc结构形成之后的器件稳定性。

41.如图1、图3-图5所示,根据本公开的实施例,多晶硅层101包括未掺杂多晶硅层(如图1、图3所示)、n型多晶硅层(如图4所示)、p型多晶硅层(如图4所示)和离子注入多晶硅层(如图5所示)中至少之一。

42.不同类型的多晶硅层101可以实现对不同类型的3d nand闪存器件的puc结构的支撑效果,以达到不同的器件效果。

43.如图1所示,根据本公开的实施例,衬底结构100还包括诱导形成层102、间隔层103和电路层104。

44.诱导形成层102设置于多晶硅层101下方,用于作为衬底结构100的导电层;

45.间隔层103设置于诱导形成层102下方;

46.电路层104设置于间隔层103下方;

47.其中,间隔层103用于间隔电路层104和诱导形成层102,以确保在金属诱导横向结

晶工艺处理的过程中,诱导形成层102不会对电路层104产生影响。

48.如图1所示,根据本公开的实施例,诱导形成层102材料为金属和/或对应的金属硅化物;间隔层103为teos层;电路层104为cmos层。

49.诱导形成层102主要采用金属或其对应的金属硅化物,其中金属如镍ni、钛ti、钯pd等,采用金属诱导横向结晶工艺的制备温度可以在300℃~800℃的范围。其中,由于金属诱导结晶,所以在晶界处会残留少量金属,且会在最终形成的诱导形成层102中形成金属硅化物,如nisi2、ni2si、nisi和ni等至少之一构成诱导形成层102,诱导形成层102厚度5nm~100nm。整个金属诱导横向结晶工艺的退火时间在几十秒级与数小时间不等,退火氛围可以通入n2、h2等气体实现,不同金属在硅中扩散情况不同,因而存在差异,所制备的薄膜厚度不同,因而时间也会不同。其中,cmos电路可以作为电路层104的主要构成基础,形成cmos层,teos层为一正硅酸乙酯材料形成的间隔层103。

50.如图1所示,基于上述milc方法制备的多晶硅层101的衬底结构100在传统沟道结构和侧墙沟道结构的应用中,可以适用于几十到几百层的堆叠单元,同时,该多晶硅层101不同的掺杂类型(n型掺杂或p型掺杂),还可以分别适用于gidl擦除或体擦除的器件结构。

51.应用一:通过对多晶硅层101上进行p型掺杂,之后进行milc工艺处理,形成的p型掺杂的多晶硅层101的衬底结构可以应用于体擦除结构(如统体擦除结构、体擦除侧墙沟道结构等)的puc结构的3d nand闪存器件。

52.应用二:通过对多晶硅层101上进行n型掺杂,之后进行milc工艺处理,形成的n型掺杂的多晶硅层101的衬底结构可以应用于gidl擦除结构(如统gidl擦除结构、gidl擦除侧墙沟道结构等)的puc结构。

53.如图2所示,本公开的另一个方面提供了一种上述的具有puc结构的3d nand闪存器件的制备方法,其中,包括步骤s201-s202。

54.在步骤s201中,形成衬底结构;

55.在步骤s202中,在衬底结构上形成puc结构,以构成3d nand闪存器件;

56.其中,在形成衬底结构中,包括步骤s2011。在步骤s2011中,通过金属诱导横向结晶工艺处理形成衬底结构,以实现横向诱导结晶,晶界方向应多为垂直方向,提高衬底结构的迁移率,降低电子和空穴的传输影响。

57.因此,相对于现有技术具有puc结构的3d nand闪存器件的传统热退火工艺直接形成多晶硅衬底结构的方式,通过milc工艺制备的衬底结构(如多晶硅衬底)的晶粒尺寸更大、晶界方向为垂直方向,极大减少了晶界处的陷阱,显著提高器件整体性能。而且,由于milc方法制备的晶粒尺寸很大(晶粒尺寸在几十到几百微米),因此,在3d nand闪存器件中,大多数沟道孔将落在晶粒内部,因此,可以认为这些沟道孔在单晶硅上,从而可以进一步达到提升器件整体性能的效果。

58.根据本公开的实施例,在步骤s2011通过金属诱导横向结晶工艺处理形成衬底结构中,包括:

59.形成初始衬底结构;

60.对初始衬底结构进行金属诱导横向结晶工艺处理,形成衬底结构;

61.其中,初始衬底结构包括自下而上依次设置的初始电路层、初始间隔层、非晶硅层和诱导层,分别用于形成衬底结构的电路层、间隔层、多晶硅层和诱导形成层。

62.根据本公开的实施例,在形成初始衬底结构中,包括:

63.在初始电路层上形成初始间隔层;

64.在初始间隔层上形成非晶硅层;

65.在非晶硅层上形成诱导层。

66.如图3所示,在制备衬底结构的过程中,先形成电路层304,在电路层304上沉积间隔层303,之后在间隔层303上沉积非晶硅层301,最后在非晶硅层301上形成一层金属层作为诱导层302。

67.其中,电路层304可以是cmos电路层,间隔层303可以是teos层,诱导层302可以是ni。

68.具体地,形成teos层的反应温度在500~850℃的范围,具体反应过程符合如下反应式:

69.si(oc2h5)4+2h2o

→

sio2+4c2h5oh。

70.此外,通过在反应温度500℃以下,并通入反应气体si2h6和/或sih4的条件下,通过低压力化学气相沉积(low pressure chemical vapor deposition,简称lpcvd)工艺在teos上形成非晶硅层301。

71.本公开实施例的上述制备方法的关键点在3d nand闪存的cmos相关晶圆的电路层制备完成后,再沉积teos层的间隔层,以此作为底部结构,进而采用milc工艺形成接近晶粒尺寸很大的多晶硅层101的衬底结构100。该制备方法与非milc工艺相比,主要优势在于拥有更大的晶粒尺寸,接近于单晶结构,要比非milc工艺形成的晶粒尺寸更大,非电阻率降低,而且milc工艺会在形成的多晶硅薄膜中会含有少量金属元素,以增强衬底结构的导电性,这也是预期之外的技术效果。

72.根据本公开的实施例,在对初始衬底结构进行金属诱导横向结晶工艺处理,形成衬底结构中,包括:

73.以300℃-800℃的退火温度,在氮气或氢气的气体氛围中对初始衬底结构执行热退火工艺,以形成衬底结构。

74.如图3所示,在形成诱导层302之后,对该具有诱导层302的初始衬底结构进行milc工艺处理,使得诱导层302形成位于多晶硅层301

′

和间隔层303

′

之间的诱导形成层302

′

,间隔层303

′

仍然位于电路层304

′

上。

75.如图3所示,当诱导层302为ni时,经过milc工艺的热退火处理,金属ni的诱导层302与非晶硅硅层301在界面处形成nisi2的硅化物,利用硅化物释放的潜热及界面处因晶格失错而提供的晶格位置,非晶硅原子在界面处重结晶,形成多晶硅晶粒,nisi2层被破坏,ni原子逐渐向a-si层的底层迁移,直到非晶硅层基本上全部晶化,ni诱导横向结晶生成多晶硅层301

′

。

76.此外,如图3所示,首先在非晶硅层301表面沉积10~20nm的金属ni层作为诱导层302,随后在300~800℃(一般可以选择500~600℃)的退火工艺下,氮气和(或)氢气氛围下退火(时间一般为小时级别),从而实现ni诱导非晶硅结晶,待结晶完全后实现金属诱导横向结晶,通过h2so4:h2o2(比例》1)的溶液处理表面去除表面一定厚度残留ni及nisi化合物,之后进行化学机械抛光(chemical mechanical polishing)工艺进一步对表面进行处理,形成诱导形成层302

′

。其中,诱导形成层302

′

可以是nisi2、ni2si、nisi和ni等至少之一的混

合层。

77.其中,上述该milc工艺进行结晶的方式所形成的晶界处会存在少许ni原子,但由于该层结构在puc中的应用,主要用于底部共源极,结合高浓度磷砷或者硼元素的掺杂(如n型掺杂或p型掺杂),少许ni原子带来的影响反而可以忽略。

78.根据本公开的实施例,在对初始衬底结构进行金属诱导横向结晶工艺处理,形成衬底结构之前,还包括:

79.对非晶硅层进行原位掺杂工艺处理,形成n型非晶硅层或p型非晶硅层;或者

80.对所述非晶硅层进行离子注入工艺处理,形成离子非晶硅层。

81.如图4和图5所示,对于本公开实施例的制备方法,对于不同掺杂类型的衬底结构而言,依照掺杂类型的不同,可以对非晶硅层401进行p型掺杂(如掺硼b)或n型掺杂(如掺磷p和/或砷as);

82.如图4所示,在形成诱导层402之前,在形成在电路层404上的间隔层403表面上直接形成非晶硅层401,在形成具有p型掺杂非晶硅层401的过程中,通过lpcvd工艺以500℃以下的反应温度下通入si2h6、sih4和b2h6中至少一种反应气体,对非晶硅层401进行硼b掺杂,形成p型掺杂的非晶硅层401。之后,在p型掺杂的非晶硅层401上形成诱导层402,对具有诱导层402的初始衬底结构进行milc工艺处理,使得诱导层402形成位于多晶硅层401

′

和间隔层403

′

之间的诱导形成层402

′

,间隔层403

′

仍然位于电路层404

′

上。

83.其中,p型掺杂的具有puc结构的3d nand闪存器件的结构形式主要应用于如下4种:(1)统3d nand结构,3d nand沟道与milc形成的底部结构直接连通,采用体擦除结构;(2)3d nand沟道通过侧墙连接,电流路径(蓝色部分)和擦除路径(红色部分)采用不同的结构,中间采用扩散工艺实现n型和p型扩散区域(渐变);(3)侧墙结构首先外延生长底部多晶硅层,再进行n型多晶硅层沉积;(4)侧墙结构直接沉积n型多晶硅层。

84.需要说明的是,若将上述p型掺杂衬底结构形成过程中,lpcvd工艺通入的反应气体更换为si2h6、sih4和ph3中至少一种反应气体,则可以实现对非晶硅层401进行磷p掺杂,形成n型掺杂的非晶硅层401,其他不作赘述。

85.相应地,n型掺杂的具有puc结构的3d nand闪存器件的结构形式主要应用于如下3种:(1)传统3d nand结构,3d nand沟道与milc形成的底部结构直接连通,采用gidl擦除;(2)3d nand沟道通过侧墙连接,中间采用扩散工艺实现n型扩散区域,侧墙结构上下均有n+掺杂源;(3)3d nand沟道通过侧墙连接,与结构

②

不同点在于侧墙掺杂方式,沉积对应n型掺杂类型多晶硅。

86.如图5所示,在形成诱导层502之前,在形成在电路层404上的间隔层403表面上,通过lpcvd工艺以500℃以下的反应温度下通入si2h6、sih4中至少一种反应气体直接形成非晶硅层501,之后对非晶硅层501进行磷p、硼b和砷as中至少之一的离子注入,形成离子非晶硅层501

′

。之后,在离子非晶硅层501

′

上形成诱导层502,构成初始衬底结构,对具有诱导层502的初始衬底结构进行milc工艺处理,使得诱导层502形成位于离子多晶硅层501

″

和间隔层503

′

之间的诱导形成层502

′

,间隔层503

′

仍然位于电路层504

′

上。

87.可见,本公开实施例的上述方法可以快速实现对原位掺杂多晶硅层、离子注入的多晶硅层的形成,整个形成制备过程工艺简单高效,也进一步证明了上述milc工艺可以应用于多晶硅层的形成,以利于器件的整体稳定性的保证。

88.至此,已经结合附图对本公开实施例进行了详细描述。

89.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1