一种具有门电压可调性的二维铁电阻变存储器

1.本发明属于纳米人工复合物、微纳米器件、存储器件、人工神经突触器件等应用研究领域,具体提供一种具有门电压可调性的二维铁电阻变存储器及其制备方法。

背景技术:

2.阻变存储器是通过材料在电激励的作用下出现不同电阻状态的可逆转变(阻变效应)而实现信息存储,由于其具有比传统存储器更高的集成度,更高的能效,因而在高密度存储和神经形态计算领域极具应用前景。目前针对阻变存储器的研究主要集中在金属氧化物体系,通常以电极/绝缘体/电极简单的三明治结构形式存在,其电阻转变行为往往源于绝缘体内部包括金属离子和空位在内的原子级元素的迁移。然而,这种原子级别的元素迁移往往是随机且不可控的,存在稳定性及可控性差等问题。

3.铁电体(大多是绝缘体)通常是指具有自发极化(电偶极子自发排布),且在外电场的调控下极化方向可逆翻转的一类材料。这种极化翻转是一种可控的快速反应,不会引起材料内部化学反应。当前,科研人员将铁电材料与阻变效应相结合提出了非易失性的稳定性强的铁电阻变存储器,其数据读写快、存储密度高、能耗低并具有高的循环次数,被认为是下一代高密度、高性能存储器的最具潜力的竞争者之一。然而,传统铁电材料如钙钛矿铁电材料(pzt,bto)等由于退极化场、缺陷富集、漏电流较大等因素的困扰,铁电性在超薄尺度下难以维持,阻碍了铁电阻变存储器向低维度、高密度器件方向的发展。此外,存储性能具有可调性的存储器可以用于功能更加多样的信息存储技术,如存内运算等。然而,截至目前,具有可调性的铁电阻变存储器尚未有报道。

4.综上所述,设计一种工艺简单、成本低廉、低维度、稳定性高且具有可调性的铁电阻变存储器是当前阻变存储器发展中一个亟需解决的问题。

技术实现要素:

5.本发明的目的是提供一种可以使阻变存储器具有门电压可调性的方法,以及采用该方法获得的具有门电压可调性的二维铁电阻变存储器。所述阻变存储器是基于二维层状铁电材料以及二维层状半导体材料制备的,并通过引入mosfet赋予该器件可调性。该方法摒除了传统铁电阻变存储器复杂的制备工艺,能够获得存储性能优异且兼具门电压可调性的新型二维铁电阻变存储器。

6.本发明技术方案如下:

7.一种使铁电阻变存储器具有门电压可调性的方法,其特征在于:以二维层状半导体材料和二维层状金属材料作为电极层,利用二维层状半导体材料的原子级厚度及门电压可调性,使二维铁电阻变存储器具有门电压可调性。

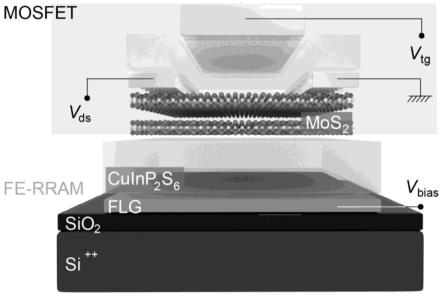

8.本发明还提供了一种具有门电压可调性的二维铁电阻变存储器,其特征在于,所述二维铁电阻变存储器与金属氧化物半导体场效应晶体管(以下简称mosfet)相集成,具体组成如下:

9.以二维层状半导体材料作为铁电阻变存储器的上电极层以及mosfet中的沟道层;

10.以二维层状铁电材料作为铁电绝缘层;

11.以二维层状金属材料作为底电极层;

12.以二维层状绝缘体作为mosfet中的介电层。

13.所述二维铁电阻变存储器的存储性能受门电压的调控作用。

14.作为优选的技术方案:

15.所述二维层状铁电材料的厚度为10-50nm,二维层状半导体材料、二维层状金属材料的厚度为1-10nm,二维层状绝缘材料的厚度为10-50nm,可以通过力学解离单晶块体或化学生长等方式制备。

16.所述二维层状半导体材料为mos2、ws2、gate、mose2、wse2、bp、之一种或多种;

17.所述二维层状铁电材料为cuinp2s6;

18.所述二维层状金属材料为多层石墨烯、1t-mote2、nbse2、crte2之一种或多种;

19.所述二维层状绝缘体为六方氮化硼、crocl之一种或多种。

20.所述的二维层状半导体的费米能级和载流子浓度可通过施加门电压进行有效调控,优选为硫化钼(mos2);二维层状铁电材料优选cuinp2s6;二维层状金属材料优选为多层石墨烯(flg);二维层状绝缘体材料优选为六方氮化硼(h-bn)。

21.本发明所述二维铁电阻变存储器以金属或多层石墨烯作为mosfet中的栅极层。

22.本发明所述二维铁电阻变存储器器件放置的基底为si基底、石英基底、云母片或柔性基底。

23.本发明还提供了所述具有门电压可调性的二维铁电阻变存储器的制备方法,其特征在于:将二维层状半导体材料、二维层状铁电材料、二维层状金属材料以及二维层状绝缘体通过范德华堆垛的方式得到异质结;利用电子束曝光(ebl)、反应离子刻蚀以及电子束蒸发(ebe)技术蒸镀金属电极,从而获得具有门电压可调性的二维铁电阻变存储器。

24.所述金属电极所采用的金属为cr、ti、au、pd、sc、ni之一种或多种。

25.本发明所述二维层状半导体、金属、铁电、绝缘材料可通过以下方法获得:化学气相沉积(cvd)、力学剥离解理、溶液中超声剥离或化学剥离。

26.本发明所述阻变存储器利用二维层状铁电材料的铁电极化翻转实现对器件电阻状态的可逆调控,从而达到存储的目的。并且,通过引入mosfet,施加门电压对上电极层二维层状半导体材料电学性能(费米能级、载流子浓度等)进行调控,进而实现对其存储性能的有效调控。

27.本发明利用二维层状材料的可堆垛性,通过范德华堆垛技术以及微纳加工技术,以二维层状半导体材料(如mos2)为上电极层,以二维层状铁电材料(如cuinp2s6)为铁电绝缘层,以二维层状金属材料(如flg)作为底电极,获得了具有高达106的开关比、长的存储时间(》103s)以及高度均一性的二维铁电阻变存储器。此外,通过引入mosfet架构,利用门电压对二维半导体材料的电学性能(如费米能级、载流子浓度等)进行调控,实现对器件存储性能的有效调控。不同门电压下,其存储窗口的差异可达102量级。

28.本发明为优化铁电阻变存储器的制备工艺提供了一个新方案,并且所制备的二维铁电阻变存储器的存储性能具有门电压可调性,拓宽了其在高密度存储、神经形态计算等领域的应用前景。

29.本发明所述方法的优点在于:

30.1、采用二维层状材料制备铁电阻变存储器有利于器件的小型化和高密度集成;

31.2、该制备方法工艺简单且与目前主流的半导体加工工艺相兼容,有利于实际生产;

32.3、能够制备出存储性能优异的铁电阻变存储器,其开关比大(高达106),数据可长时间保存;

33.4、通过引入mosfet,可对存储器的存储性能进行有效调控。

附图说明

34.图1为二维铁电阻变存储器的制备过程示意图:a:利用干法转印,将cuinp2s6落在flg上;b:干法转印mos2;c:电子束蒸发制备金属电极;d-e:干法转印h-bn;f:电子束蒸发制备金属顶层栅极。

35.图2为实施例1二维铁电阻变存储器结构示意图。

36.图3为实施例1二维铁电阻变存储器的光学照片。

37.图4为实施例1二维铁电阻变存储器的截面透射电镜照片。

38.图5为实施例1二维铁电阻变存储器界面能量色散x射线光谱图。

39.图6为实施例1二维铁电阻变存储器在不同阻态下的i-v曲线。

40.图7为实施例1二维铁电阻变存储器在两种阻态下的数据保持能力测量。

41.图8为实施例1二维铁电阻变存储器的均一性表征。

42.图9为实施例1不同门电压下存储器的存储窗口。

具体实施方式

43.实施例1

44.(1)使用scope隐形胶带对二维层状铁电材料cuinp2s6进行机械剥离,然后转移到有机聚合物聚二甲基硅氧烷(pdms)上,通过干法转印技术将pdms上的cuinp2s6(40nm)转移到挑选好的二维层状金属材料多层石墨烯(flg,8nm)上,得到cuinp2s6/flg结构,随后在丙酮、异丙醇(ipa)中各浸泡15分钟,以去除样品表面的有机残留,图1(a);

45.(2)使用scope隐形胶带对二维层状半导体材料mos2进行机械剥离,然后转移到pdms上,再通过干法转印将pdms上的mos2(10nm)转移到上述cuinp2s6/flg结构上,得到mos2/cuinp2s6/flg结构,需要注意的是mos2(上电极)与flg(下电极)不能相连,避免上下电极短路,图1(b);

46.(3)利用电子束曝光(ebl)、电子束蒸发(ebe)技术,在mos2上蒸镀金属au源漏电极,图1(c);

47.(4)利用干法转移技术,使用粘性聚合物(pdms/ppc双层结构)将六方氮化硼(h-bn,30nm)转移至粘性聚合物上,然后将h-bn融留在上述带有金属电极的mos2/cuinp2s6/flg结构上,随后使用丙酮和ipa将堆垛结构上的残留聚合物全部去除,图1(d-e);

48.(5)再次利用ebl、ebe技术,制备金属au顶栅,制备得到与mosfet架构相集成的二维铁电阻变存储器au/h-bn/mos2/cuinp2s6/flg,其中au/h-bn/mos2为mosfet,可用来调节mos2中的费米能级和载流子浓度,mos2/cuinp2s6/flg为二维铁电阻变存储器,图1(f);

49.(6)通过将mos2接地,在flg上施加电压,可测量器件的阻变特性,图3;

50.(7)通过给顶栅施加门电压,可对器件的阻变特性进行有效调控,随着mos2中的载流子浓度从高调到低,器件的阻变窗口发生了明显的缩小,开关比缩小了近两个量级。

51.实施例2

52.(1)使用cvd生长薄层二维层状铁电材料cuinp2s6,然后通过干法转印技术将所生长的cuinp2s6(40nm)转移到挑选好的二维层状金属材料1t-mote2(10nm)上,得到cuinp2s6/1t-mote2结构,随后在丙酮、异丙醇(ipa)中各浸泡15分钟,以去除样品表面的有机残留;

53.(2)使用scope隐形胶带对二维层状半导体材料mos2进行机械剥离,然后转移到pdms上,再通过干法转印将pdms上的mos2(10nm)到上述cuinp2s6/1t-mote2结构上,得到mos2/cuinp2s6/1t-mote2结构,需要注意的是mos2(上电极)与1t-mote2(下电极)不能相连,避免上下电极短路;

54.(3)利用电子束曝光(ebl)、热蒸镀技术,在mos2上蒸镀金属pt源漏电极;

55.(4)利用干法转移技术,使用粘性聚合物(pdms/ppc双层结构)将六方氮化硼(h-bn,30nm)转移至粘性聚合物上,然后将h-bn融留在上述带有金属电极的mos2/cuinp2s6/1t-mote2结构上,随后使用丙酮和ipa将堆垛结构上的残留聚合物全部去除;

56.(5)再次利用ebl、热蒸镀技术制备金属pt顶栅,制备得到与mosfet架构相集成的二维铁电阻变存储器pt/h-bn/mos2/cuinp2s6/1t-mote2,其中pt/h-bn/mos2为mosfet,可用来调节mos2中的费米能级和载流子浓度,mos2/cuinp2s6/1t-mote2为二维铁电阻变存储器;

57.(6)通过将mos2接地,在1t-mote2上施加电压,可测量器件的阻变特性;

58.(7)通过给顶栅施加门电压,可对器件的阻变特性进行有效调控。

59.实施例3

60.(1)使用cvd生长薄层二维层状铁电材料cuinp2s6,然后通过干法转印技术将所生长的cuinp2s6(40nm)转移到挑选好的二维层状金属材料多层石墨烯(flg,10nm)上,得到cuinp2s6/flg结构,随后在丙酮、异丙醇(ipa)中各浸泡15分钟,以去除样品表面的有机残留;

61.(2)使用scope隐形胶带对二维层状半导体材料gate进行机械剥离,然后转移到pdms上,再通过干法转印将pdms上的gate(10nm)到上述cuinp2s6/flg结构上,得到gate/cuinp2s6/flg结构,需要注意的是gate(上电极)与flg(下电极)不能相连,避免上下电极短路;

62.(3)利用电子束曝光(ebl)、热蒸镀技术,在gate上蒸镀金属pt源漏电极;

63.(4)利用干法转移技术,使用粘性聚合物(pdms/ppc双层结构)将六方氮化硼(h-bn,30nm)转移至粘性聚合物上,然后将h-bn融留在上述带有金属电极的gate/cuinp2s6/flg结构上,随后使用丙酮和ipa将堆垛结构上的残留聚合物全部去除;

64.(5)再次利用ebl、热蒸镀技术,制备金属pt顶栅,制备得到与mosfet架构相集成的二维铁电阻变存储器pt/h-bn/gate/cuinp2s6/flg,其中pt/h-bn/gate为mosfet,可用来调节gate中的费米能级和载流子浓度,gate/cuinp2s6/flg为二维铁电阻变存储器;

65.(6)通过将gate接地,在flg上施加电压,可测量器件的阻变特性;

66.(7)通过给顶栅施加门电压,可对器件的阻变特性进行有效调控。

67.实施例4

68.(1)使用cvd生长薄层二维层状铁电材料cuinp2s6,然后通过干法转印技术将所生长的cuinp2s6(30nm)转移到挑选好的二维层状金属材料1t-mote2(10nm)上,得到cuinp2s6/1t-mote2结构,随后在丙酮、异丙醇(ipa)中各浸泡15分钟,以去除样品表面的有机残留;

69.(2)使用scope隐形胶带对二维层状半导体材料gate进行机械剥离,然后转移到pdms上,再通过干法转印将pdms上的gate(5nm)到上述cuinp2s6/1t-mote2结构上,得到gate/cuinp2s6/1t-mote2结构,需要注意的是gate(上电极)与1t-mote2(下电极)不能相连,避免上下电极短路;

70.(3)利用电子束曝光(ebl)、热蒸镀技术,在gate上蒸镀金属pt源漏电极;

71.(4)利用干法转移技术,使用粘性聚合物(pdms/ppc双层结构)将crocl(30nm)转移至粘性聚合物上,然后将crocl融留在上述带有金属电极的gate/cuinp2s6/1t-mote2结构上,随后使用丙酮和ipa将堆垛结构上的残留聚合物全部去除;

72.(5)再次利用ebl、热蒸镀技术制备金属pt顶栅,制备得到与mosfet架构相集成的二维铁电阻变存储器pt/crocl/gate/cuinp2s6/1t-mote2,其中pt/crocl/gate为mosfet,可用来调节gate中的费米能级和载流子浓度,gate/cuinp2s6/1t-mote2为二维铁电阻变存储器;

73.(6)通过将gate接地,在1t-mote2上施加电压,可测量器件的阻变特性;

74.(7)通过给顶栅施加门电压,可对器件的阻变特性进行有效调控。

75.本发明未尽事宜为公知技术。

76.上述实施例只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1