发光显示装置及其制造方法与流程

发光显示装置及其制造方法

1.相关申请的交叉引用

2.本技术要求于2021年8月27日在韩国知识产权局提交的第10-2021-0114163号韩国专利申请的优先权,该韩国专利申请通过引用包含于此。

技术领域

3.本技术领域涉及一种发光显示装置和一种用于制造发光显示装置的方法。

背景技术:

4.发光显示装置包括发光二极管并且可以通过控制发光二极管的亮度水平来显示图像。发光显示装置不需要背光,并且因此可以理想地薄且轻。

5.发光显示装置可以被包括在各种电子装置中,诸如智能电话、平板计算机、监视器、电视和用于汽车的用户界面。

技术实现要素:

6.一种发光显示装置可以包括用于限定像素区域的像素限定层。像素限定层可以包括黑色颜料,用于改善显示装置的光学特性(诸如对比度)。在形成黑色像素限定层的工艺和/或后续工艺中,如果不需要的黑色颜料或与黑色像素限定层相关的不需要的材料残留在显示装置中,则通过显示装置显示的图像中可能出现诸如暗点的缺陷。实施例可以涉及可以防止或最小化缺陷使得可以获得令人满意的图像质量的发光显示装置和相关的制造方法。

7.根据实施例的发光显示装置包括以下元件:基底;晶体管,设置在所述基底上;绝缘层,设置在所述晶体管上;像素电极,设置在所述绝缘层上;延伸电极,从所述像素电极延伸并且电连接到所述晶体管;以及像素限定层,设置在所述绝缘层上,并且所述像素限定层包括与所述像素电极重叠的开口。所述像素限定层与所述延伸电极重叠,并且所述延伸电极比所述像素电极厚。

8.所述延伸电极包括多个层,并且所述多个层的最上层包括氧化物半导体。

9.所述最上层可以包括氧化铟锌(izo)、氧化铟镓锌(igzo)、氧化铟锌锡(izto)、氧化锌锡(zto)和氧化锌(zno)中的至少一种。

10.所述延伸电极的所述多个层可以包括从所述像素电极连续延伸的一层或多层、以及所述最上层。

11.从所述像素电极连续延伸的所述一层或多层可以包括包含透明导电氧化物的第一导电层、包含金属的第二导电层和包含透明导电氧化物的第三导电层。

12.所述延伸电极可以比所述像素电极厚所述延伸电极的最上层的厚度。

13.所述像素限定层可以在限定所述开口的边缘处具有双台阶结构。

14.所述像素限定层的所述边缘可以具有在截面图中上表面的斜率朝向所述开口增加并且随后减小的拐点。

15.所述延伸电极可以穿过形成在所述绝缘层中的接触孔连接到所述晶体管或者连接到与所述晶体管连接的连接构件。

16.所述像素限定层可以是包含黑色颜料的黑色像素限定层。

17.根据实施例的一种发光显示装置包括以下元件:基底;晶体管,设置在所述基底上;一个或多个绝缘层,设置在所述晶体管上;像素电极,设置在是一个或多个绝缘层上并且包括多个导电层;延伸电极,从所述像素电极延伸并且电连接到所述晶体管;像素限定层,设置在所述绝缘层上,所述像素限定层包括与所述像素电极重叠的开口并且覆盖所述像素电极的边缘和所述延伸电极;发射层,设置在所述像素电极上并且与所述开口重叠;以及公共电极,设置在所述发射层上。所述延伸电极包括多个导电层和设置在所述多个导电层上的氧化物半导体层。

18.所述氧化物半导体层可以包括氧化铟锌(izo)、氧化铟镓锌(igzo)、氧化铟锌锡(izto)、氧化锌锡(zto)和氧化锌(zno)中的至少一种。

19.所述延伸电极的所述多个导电层可以从所述像素电极的多个导电层连续延伸。

20.所述延伸电极的厚度可以大于所述像素电极的厚度。

21.所述像素限定层可以是包含黑色颜料的黑色像素限定层。所述发光显示装置还可以包括设置在所述像素限定层上并且包含与所述像素限定层的材料不同的材料的间隔物。

22.所述一个或多个绝缘层可以包括钝化层、设置在所述钝化层上的第一平坦化层和设置在所述第一平坦化层上的第二平坦化层。所述发光显示装置还可以包括设置在所述第一平坦化层和所述第二平坦化层之间的连接构件。所述连接构件可以穿过形成在所述钝化层和所述第一平坦化层中的接触孔连接到所述晶体管。所述延伸电极可以穿过形成在所述第二平坦化层中的接触孔连接到所述连接构件。

23.根据实施例的用于制造发光显示装置的方法包括以下步骤:在基底上形成晶体管;在所述晶体管上形成绝缘层;在所述绝缘层上形成导电材料层,并且在所述导电材料层上形成掩模层;通过将所述掩模层和所述导电材料层图案化形成像素电极,以及从所述像素电极延伸并且电连接到所述晶体管的延伸电极;通过在所述绝缘层上涂覆和图案化黑色光刻胶,形成包括与所述像素电极重叠的开口的像素限定层;去除设置在所述像素电极上的所述掩模层;并且固化所述像素限定层。

24.所述掩模层可以包括氧化物半导体。

25.所述去除所述掩模层可以包括使用所述像素限定材料层作为掩模的湿法蚀刻。

26.在所述去除所述掩模层期间,可以在所述像素限定层和所述像素电极之间形成间隙,并且在所述固化所述像素限定层期间,可以通过对所述像素限定层进行回流来填充所述间隙。

27.实施例可以涉及一种发光显示装置。所述发光显示装置可以包括基底、晶体管、绝缘层、像素电极、延伸电极和像素限定层。所述晶体管可以与所述基底重叠。所述绝缘层可以与所述晶体管重叠。所述像素电极可以设置在所述绝缘层的上表面上。所述延伸电极可以从所述像素电极延伸。所述像素电极可以通过所述延伸电极电连接到所述晶体管。所述像素限定层可以设置在所述绝缘层上,可以包括暴露所述像素电极的开口,并且可以覆盖所述延伸电极。所述延伸电极的一部分可以设置在所述绝缘层的所述上表面上,可以平行于所述绝缘层的所述上表面纵向延伸,并且可以在垂直于所述绝缘层的所述上表面的方向

上比所述像素电极厚。

28.所述延伸电极可以包括第一层和第二层。所述第一层可以设置在所述第二层和所述像素限定层之间,并且所述第一层可以包括氧化物半导体。

29.所述第一层可以包括氧化铟锌(izo)、氧化铟镓锌(igzo)、氧化铟锌锡(izto)、氧化锌锡(zto)和氧化锌(zno)中的至少一种。

30.所述第二层可以直接连接到所述像素电极。

31.所述第二层可以包括第一透明导电氧化物层、金属层和第二透明导电氧化物层。

32.所述延伸电极可以比所述像素电极厚所述第一层的厚度。

33.所述像素限定层可以具有与所述延伸电极重叠的凹入结构。

34.所述像素限定层可以具有定位在所述凹入结构和所述开口之间的凸起结构。

35.所述绝缘层可以包括接触孔。所述延伸电极可以部分地设置在所述接触孔内。

36.所述像素限定层可以是包含黑色颜料的黑色像素限定层。

37.实施例可以涉及一种发光显示装置。所述发光显示装置可以包括以下元件:基底;晶体管,与所述基底重叠;绝缘层,与所述晶体管重叠;像素电极,设置在所述绝缘层的上表面上并且包括多个第一导电层和多个第二导电层;延伸电极,从所述像素电极延伸,设置在所述绝缘层的所述上表面上,包括多个第二导电层,并且包括设置在所述多个第二导电层上的氧化物半导体层,其中,所述像素电极可以通过所述延伸电极电连接到所述晶体管;像素限定层,设置在所述绝缘层上,暴露所述像素电极的暴露部分,覆盖所述像素电极的边缘,并且覆盖所述延伸电极;发射层,与所述像素电极的所述暴露部分重叠;以及公共电极,与所述发射层重叠。

38.所述氧化物半导体层可以包括氧化铟锌(izo)、氧化铟镓锌(igzo)、氧化铟锌锡(izto)、氧化锌锡(zto)和氧化锌(zno)中的至少一种。

39.所述多个第二导电层可以直接连接到所述多个第一导电层。

40.所述延伸电极的一部分可以平行于所述绝缘层的所述上表面纵向延伸,并且可以在垂直于所述绝缘层的所述上表面的方向上比所述像素电极厚。

41.所述发光显示装置还可以包括间隔物。所述像素限定层可以设置在所述绝缘层和所述间隔物之间并且可以包括黑色颜料。所述间隔物的材料可以与所述像素限定层的材料不同。

42.所述发光显示装置还可以包括连接构件。所述氧化物半导体层可以通过所述多个第二导电层电连接到所述连接构件。所述多个第二导电层可以通过所述连接构件电连接到所述晶体管。

43.实施例可以涉及一种用于制造发光显示装置的方法。所述方法可以包括以下步骤:形成与基底的晶体管重叠;形成与所述晶体管的绝缘层重叠;在所述绝缘层上形成导电材料层;在所述导电材料层上形成掩模材料层;部分地去除所述掩模材料层和所述导电材料层以形成掩模层和导电层;形成像素限定材料层,所述像素限定材料层部分地覆盖所述掩模层的覆盖部分并且包括暴露所述掩模层的暴露部分的开口;去除所述掩模层的至少所述暴露部分以形成像素电极和延伸电极,其中,所述像素电极可以包括所述导电层的第一部分并且可以通过所述延伸电极电连接到所述晶体管,并且其中,所述延伸电极可以包括所述导电层的第二部分和所述掩模层的所述覆盖部分;并且固化所述像素限定材料层以形

成(部分地)暴露所述像素电极并且覆盖所述延伸电极像素的像素限定层。

44.所述掩模层包括氧化物半导体。

45.所述方法可以包括:使用所述像素限定材料层作为掩模,湿法蚀刻所述掩模层的所述暴露部分。

46.所述方法可以包括:在所述固化期间对所述像素限定材料层进行回流以填充所述像素限定材料层和所述像素电极之间的间隙。当所述去除所述掩模层的至少所述暴露部分时可以形成所述间隙。

47.根据实施例,发光显示装置可以显示具有最少缺陷(诸如暗点)和具有令人满意的图像质量的图像。

附图说明

48.图1是根据实施例的发光显示装置的示意性俯视图。

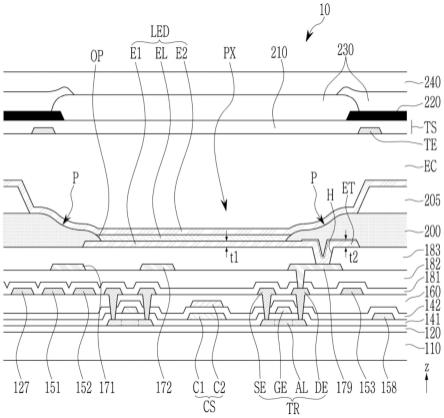

49.图2是根据实施例的发光显示装置的显示面板中的一个像素区域的示意性截面图。

50.图3、图4、图5、图6、图7、图8、图9、图10、图11和图12是示出与根据一个或多个实施例的用于制造发光显示装置的方法相关的结构和工艺的截面图。

51.图13是示出在根据实施例的发光显示装置的平面图中显示面板中的像素限定层的开口及其附近的图片。

52.图14是根据实施例的发光显示装置的显示面板的一个像素区域的示意性截面图。

53.图15是根据实施例的发光显示装置的像素的等效电路图。

具体实施方式

54.参照附图描述实施例的示例。

55.尽管可以使用“第一”、“第二”等术语来描述各种元件,但是这些元件不应受这些术语的限制。这些术语可以用于将一个元件与另一元件区分开。在不脱离一个或多个实施例的教导的情况下,“第一”元件可以被称为“第二”元件。将元件描述为“第一”元件可能不需要或暗示存在“第二”元件或其他元件。术语“第一”、“第二”等可以用于区分元件的不同类别或不同组。为简洁起见,术语“第一”、“第二”等可以分别表示“第一类(或第一组)”、“第二类(或第二组)”等。

56.当第一元件被称为“在”第二元件“上”时,第一元件可以直接在第二元件上,或者在第一元件和第二元件之间可以存在一个或多个居间元件。当第一元件被称为“直接在”第二元件“上”时,在第一元件和第二元件之间不存在(除了诸如空气的环境元素以外的)居间元件。

57.术语“连接”可以表示“直接连接”或“间接连接”。术语“连接”可以表示“机械连接”和/或“电连接”。术语“连接”可以表示“电连接”或“不通过居间晶体管电连接”。术语“绝缘”可以表示“电绝缘”或“电隔离”。术语“导电”可以表示“电学上导电”。术语“驱动”可以表示“操作”或“控制”。术语“包括”可以表示“由

……

组成”。术语“相邻”可以表示“紧邻”。元件在特定方向上延伸的表述可以表示元件在特定方向上纵向延伸和/或元件的纵向方向在特定方向上。术语“图案”可以表示“构件”。术语“限定”可以表示“形成”或“提供”。与对象重叠的

空间或开口的表述可以表示空间或开口(的位置)与对象(的位置)重叠。术语“重叠”可以等同于“被

……

重叠”。第一元件在平面图中与第二元件重叠的表述可以表示第一元件在垂直于基底的方向上与第二元件重叠。

58.在附图中,符号“x”、“y”和“z”用于表示方向,其中“x”是第一方向,“y”是垂直于第一方向的第二方向,并且“z”是垂直于第一方向和第二方向中的每一个的第三方向。

59.图1是根据实施例的发光显示装置的示意性俯视图。

60.参照图1,发光显示装置(也被称为显示装置)可以包括显示面板10、接合到显示面板10的柔性印刷电路膜20、以及集成电路芯片30。

61.显示面板10可以包括用于显示图像的显示区域da,并且可以包括用于容纳用于产生和/或传输施加到显示区域da的信号的电路和/或信号线的非显示区域na。非显示区域na可以围绕显示区域da。

62.在显示区域da中,像素px可以以矩阵形式(或阵列)设置。诸如如图15中所示的栅极线(也被称为扫描线)151、数据线171和驱动电压线172的信号线可以设置在显示区域da中。如图15中所示,栅极线151、数据线171和驱动电压线172等连接到像素px,并且像素px从这些信号线接收栅极信号(也被称为扫描信号)gw、数据电压v

dat

和驱动电压(第一电源电压或高电位电源电压)el

vdd

。像素px可以是诸如发光二极管led(参照图15)的发光装置。

63.用于检测用户的接触和/或非接触触摸的触摸传感器可以设置在显示区域da中。在平面图中,显示区域da可以具有各种形状中的一种或多种,诸如四边形形状、其他多边形形状、圆形形状和/或椭圆形形状。

64.焊盘部分pp可以定位在非显示区域na中,并且可以包括用于从一个或多个外部装置接收信号的焊盘。焊盘部分pp可以沿着显示面板10的一个边缘在第一方向x上定向。柔性印刷电路膜20可以接合到焊盘部分pp,并且柔性印刷电路膜20的焊盘可以电连接到焊盘部分pp的焊盘。

65.产生和/或处理用于驱动显示面板10的信号的至少一个驱动单元可以定位在非显示区域na中。像素px可以根据由栅极驱动器产生的栅极信号gw(参照图15)来接收数据电压v

dat

(参照图15)。栅极驱动器可以集成在显示面板10上,并且定位在显示区域da的至少一侧上。数据驱动器和信号控制器可以实现在集成电路芯片30(也被称为驱动ic芯片30)中,并且集成电路芯片30可以被安装在非显示区域na中。集成电路芯片30可以被安装在柔性印刷电路膜20等上,并且电连接到显示面板10。

66.图2是根据实施例的显示面板10中的一个像素区域的示意性截面图。

67.参照图2,显示面板10可以包括基底110、形成在基底110上(和/或与基底110重叠)的晶体管tr、以及连接到晶体管tr的发光二极管led。发光二极管led可以与像素px相对应。

68.基底110可以是玻璃基底。基底110可以是包括诸如聚酰亚胺、聚酰胺或聚对苯二甲酸乙二醇酯的聚合物的柔性基底。

69.缓冲层120可以定位在基底110上。当形成半导体层al时,缓冲层120阻挡来自基底110的杂质以改善半导体层al的特性,并且可以通过在基底110上方提供平坦表面来减轻半导体层al的应力。缓冲层120可以包括氮化硅(sin

x

)、氧化硅(sio

x

)和氮氧化硅(sio

x

ny)中的至少一种。缓冲层120可以包括非晶硅。

70.半导体层al可以定位在缓冲层120上。半导体层al可以包括第一区、第二区、以及

在第一区和第二区之间的沟道区。半导体层al可以包括多晶硅、非晶硅或氧化物半导体。

71.第一栅极绝缘层141可以定位在半导体层al上。第一栅极绝缘层141可以包括诸如氧化硅、氮化硅或氮化硅的无机绝缘材料,并且可以是单层或多层。

72.第一栅极导电层可以定位在第一栅极绝缘层141上,并且可以包括旁路控制线158、栅极电极ge和存储电容器cs的第一电极c1等。第一栅极导电层的构件可以由相同的材料在相同的工艺中形成。栅极电极ge可以与半导体层al的沟道区重叠。第一栅极导电层可以包括钼(mo)、铝(al)、铜(cu)和钛(ti)中的至少一种,并且可以是单层或多层。

73.第二栅极绝缘层142可以定位在第一栅极导电层上。第二栅极绝缘层142可以包括诸如氮化硅、氧化硅和氮氧化硅中的至少一种的无机绝缘材料,并且可以是单层或多层。

74.第二栅极导电层可以定位在第二栅极绝缘层142上,并且可以包括存储电容器cs的第二电极c2等。第二电极c2可以与第一电极c1重叠;第一电极c1、第二电极c2和居间的第二栅极绝缘层142可以形成存储电容器cs。第二栅极导电层的构件可以由相同的材料在相同的工艺中形成。第二栅极导电层可以包括钼(mo)、铝(al)、铜(cu)或钛(ti)等,并且可以是单层或多层。

75.层间绝缘层160可以定位在第二栅极导电层上。层间绝缘层160可以包括诸如氮化硅、氧化硅和氮化硅中的至少一种的无机绝缘材料,并且可以是单层或多层。当层间绝缘层160是多层结构时,下层可以包括氮化硅,并且上层可以包括氧化硅。

76.第一数据导电层可以定位在层间绝缘层160上,并且可以包括晶体管tr的第一电极se和第二电极de、初始化电压线127、扫描线151、先前扫描线152(或相邻的扫描线152)和发光控制线153等。第一数据导电层的构件可以由相同的材料在相同的工艺中形成。第一电极se和第二电极de中的一个可以是晶体管tr的源极电极,并且另一个可以是晶体管tr的漏极电极。初始化电压线127、扫描线151、先前扫描线152和发光控制线153中的至少一个可以被包括在第一栅极导电层或第二栅极导电层中。第一数据导电层可以包括铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钙(ca)、钼(mo)、钛(ti)、钨(w)和铜(cu)中的至少一种,可以是单层也可以是多层。例如,第一数据导电层可以包括包含诸如钼(mo)、铬(cr)、钽(ta)、钛(ti)中的至少一种的难熔金属的下层,并且可以包括包含诸如至少铝(al)、铜(cu)和银(ag)中的一种的具有低电阻率的金属的中间层,并且可以包括包含难熔金属的上层。例如,第一数据导电层可以具有钛-铝-钛(ti-al-ti)的三层结构。

77.钝化层181可以定位在第一数据导电层上。钝化层181可以包括诸如氧化硅或氮化硅的无机绝缘材料,。

78.第一平坦化层182可以定位在钝化层181上。第一平坦化层182可以包括有机绝缘材料,诸如通用聚合物(诸如聚甲基丙烯酸甲酯)、聚苯乙烯、具有酚基的聚合物的衍生物、基于丙烯酸的聚合物、基于酰亚胺的聚合物(例如,聚酰亚胺)和基于硅氧烷的聚合物中的至少一种。

79.第二数据导电层可以定位在第一平坦化层182上,并且可以包括数据线171、驱动电压线172和连接构件179等。连接构件179可以穿过形成在第一平坦化层182和钝化层181中的接触孔连接到晶体管tr的第二电极de。第二数据导电层还可以包括初始化电压线127、扫描线151、先前扫描线152和发光控制线153中的至少一个。数据线171和驱动电压线172中

的至少一个可以被包括在第一数据导电层中。第二数据导电层的构件可以由相同的材料在相同的工艺中形成。第二数据导电层可以包括铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钙(ca)、钼(mo)、钛(ti)、钨(w)和铜(cu)中的至少一种,并且可以是单层或多层。例如,第二数据导电层可以具有钛-铝-钛(ti-al-ti)的三层结构。

80.第二平坦化层183可以定位在第二数据导电层上。第二平坦化层183可以包括有机绝缘材料,诸如通用聚合物(诸如聚甲基丙烯酸甲酯)、聚苯乙烯、具有酚基的聚合物的衍生物、基于丙烯酸的聚合物、基于酰亚胺的聚合物(例如,聚酰亚胺)和基于硅氧烷的聚合物中的至少一种。

81.发光二极管led的像素电极e1和延伸电极et可以(直接)定位在第二平坦化层183的上表面上。延伸电极et可以从像素电极e1延伸,并且可以穿过形成在第二平坦化层183中的接触孔h连接到连接构件179。延伸电极et可以包括定位在接触孔h中的连接部分,并且可以包括(直接)定位在第二平坦化层183的上表面上并且在平行于第二平坦化层183的上表面的方向上纵向延伸的延伸部分。延伸电极et可以与像素电极e1一体地形成。延伸电极et(的延伸部分)的厚度t2可以比像素电极e1的厚度t1厚。由于连接构件179连接到第二电极de,因此像素电极e1可以通过延伸电极et和连接构件179电连接到第二电极de。像素电极e1和延伸电极et可以由反射导电材料、半透明导电材料和透明导电材料中的至少一种形成和/或包括反射导电材料、半透明导电材料和透明导电材料中的至少一种。像素电极e1可以包括诸如氧化铟锡(ito)或氧化铟锌(izo)的透明导电材料。像素电极e1可以包括诸如锂(li)、钙(ca)、铝(al)、银(ag)、镁(mg)或金(au)的金属。像素电极e1可以具有诸如ito-ag-ito的三层结构的多层结构。延伸电极et可以具有包括在与像素电极e1相同的三层(例如,ito-ag-ito层)上的附加层(掩模层)的四层结构。因此,延伸电极et的厚度t2可以比像素电极e1的厚度t1大附加层的厚度。掩模层可以是氧化物半导体层。

82.像素限定层200(也被称为分隔层)可以定位在第二平坦化层183上,并且可以具有(部分地)暴露像素电极e1的开口op。像素限定层200可以覆盖像素电极e1的边缘。像素电极e1的覆盖宽度可以为大约3μm或更小。像素限定层200可以覆盖整个延伸电极et,并且开口op可以不暴露延伸电极et。像素限定层200可以包括诸如基于丙烯酸的聚合物、基于酰亚胺的聚合物或基于酰胺的聚合物的有机绝缘材料。像素限定层200可以是包含黑色颜料的黑色的像素限定层200。例如,像素限定层200可以包括聚酰亚胺粘合剂和红色、绿色和蓝色混合的颜料。像素限定层200可以包括cardo粘合剂树脂与内酰胺黑色颜料和蓝色颜料的混合物。像素限定层200可以包括炭黑。

83.黑色的像素限定层200可以改善对比度,并且可以阻挡由下面的金属层反射的光。

84.像素限定层200的开口op可以通过光刻工艺形成,并且像素限定层200的厚度可以朝向靠近像素限定层200的开口op的边缘逐渐减小。在像素限定层200的厚度的变化中,在截面图中在像素限定层200的靠近开口op的边缘部分的上表面的斜率可以朝着开口op增加或恒定。像素限定层200的厚度可以朝向边缘逐渐减小。像素限定层200可以具有拐点p。在截面图中,像素限定层200的在间隔物205和拐点p之间的上表面的斜率大于像素限定层200的在拐点p和开口op之间的上表面的斜率。在间隔物205和开口op之间,像素限定层200可以具有与拐点p相对应并且定位在两个凸起结构之间的凹入结构(或凹陷结构)。凸起结构中

的一个可以定位在开口op和凹入结构之间。像素限定层200可以在间隔物205和开口op之间具有双台阶结构。像素限定层200的双台阶结构可以是像素限定层200的边缘在固化期间回流的结果。凹入结构(或凹陷结构)可以与延伸电极et重叠。

85.发射层el可以定位在像素电极e1(的暴露部分)上。发射层el可以与像素限定层200的边缘重叠,并且发射层el的至少一部分可以定位在开口op中。发射层el可以包括发射原色中的一种(诸如红色、绿色和蓝色中的一种)的光的材料层。发射层el可以具有堆叠发射不同颜色的光的材料层的结构。在像素电极e1上,除了发射层el之外,还可以定位有空穴注入层、空穴传输层、电子传输层和电子注入层中的至少一个。

86.间隔物205可以定位在像素限定层200上。间隔物205可以包括诸如基于丙烯酸的聚合物、基于酰亚胺的聚合物或基于酰胺的聚合物的有机绝缘材料。

87.公共电极e2(也被称为对电极)可以定位在发射层el和像素限定层200上。公共电极e2可以遍及多个像素px定位。公共电极e2可以包括诸如钙(ca)、钡(ba)、镁(mg)、铝(al)、银(ag)、铂(pt)、钯(pd)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)和锂(li)中的至少一种的金属。公共电极e2可以包括诸如氧化铟锡(ito)或氧化铟锌(izo)的透明导电氧化物(tco)。

88.像素电极e1、发射层el和公共电极e2可以形成可以作为有机发光二极管的发光二极管led。像素电极e1可以是阳极(即,空穴注入电极),并且公共电极e2可以是阴极(即,电子注入电极),反之亦然。像素限定层200的开口op可以与发光二极管led的发光区相对应。

89.封装层ec可以定位在公共电极e2上。封装层ec可以是包括堆叠在公共电极e2上的至少一个无机层和至少一个有机层的薄膜封装层。例如,封装层ec可以具有第一无机层、有机层和第二无机层的三层结构。封装层ec可以是基底。

90.触摸传感器层ts可以定位在封装层ec上,可以包括触摸电极te,并且可以包括覆盖触摸电极te的钝化层210。触摸传感器层ts可以检测用户的接触和/或非接触触摸。触摸电极te可以由金属(以网状结构)、透明导电材料或导电聚合物等形成。钝化层210可以包括诸如氮化硅、氧化硅或氮氧化硅的无机绝缘材料、或者诸如基于丙烯酸的聚合物或基于聚酰亚胺的树脂的有机材料。可以包括无机绝缘材料的缓冲层可以定位在封装层ec和触摸传感器层ts之间。触摸传感器层ts可以形成在封装层ec上,或者可以形成在单独的基底上并且附接到封装层ec。

91.光阻挡构件220可以定位在触摸传感器层ts上。光阻挡构件220可以包括黑色颜料或染料,并且可以阻挡由显示面板10的金属层反射的光。光阻挡构件220可以不与作为发光区的开口op重叠。光阻挡构件220可以被称为黑矩阵。

92.滤色器230可以定位在触摸传感器层ts上。例如,滤色器230可以透射红色、绿色和蓝色之中的一种颜色的光。不同颜色的滤色器230可以在重叠区中与光阻挡构件220重叠。

93.滤色器230和光阻挡构件220可以组合用作抗反射层。可以不需要作为抗反射层的偏振层。有利地,可以获得令人满意的光输出效率,并且可以最小化显示面板10的厚度。滤色器230可以包括量子点或磷光体,并且可以将从发光二极管led发射的光转换成红色或绿色的光。外涂层240可以定位在滤色器230上。显示面板10可以可选地包括偏振层作为抗反射层。偏振层可以通过诸如光学透明粘合剂(oca)的粘合剂构件附接到触摸传感器层ts。

94.图3至图12是示出与根据实施例的用于制造发光显示装置的方法相关的结构和工艺的截面图。

95.参照图3,可以在基底110上形成缓冲层120。在缓冲层120上形成半导体材料层之后,执行图案化以形成晶体管tr的半导体层al。图案化可以表示通过光刻工艺等部分地去除层来形成预定图案。可以在半导体层al上形成第一栅极绝缘层141。在第一栅极绝缘层141上形成导电材料层后,进行图案化以形成包括晶体管tr的栅极电极ge、存储电容器cs的第一电极c1和旁路控制线158等的第一栅极导电层。可以在第一栅极导电层上形成第二栅极绝缘层142。可以在第二栅极绝缘层142上形成包括存储电容器cs的第二电极c2等的第二栅极导电层。可以在第二栅极导电层上形成层间绝缘层160。在层间绝缘层160上形成导电材料层,并且随后进行图案化以形成包括晶体管tr的第一电极se和第二电极de、初始化电压线127、扫描线151、先前扫描线152和发光控制线153等的第一数据导电层。可以在第一数据导电层上形成钝化层181。可以在钝化层181上形成第一平坦化层182。在第一平坦化层182上形成导电材料层并且进行图案化之后,可以形成可以包括数据线171、驱动电压线172和连接构件179等的第二数据导电层。可以在第二数据导电层上形成第二平坦化层183。可以对第二平坦化层183进行图案化以形成暴露连接构件179的接触孔h。

96.参照图4,可以在第二平坦化层183上形成导电材料层190,并且可以在导电材料层190上形成掩模材料层194。可以直接在导电材料层190上形成掩模材料层194(即,在导电材料层190和掩模材料层194之间没有插入另一层)。导电材料层190可以穿过接触孔h(直接)连接到连接构件179。参照示出了图4的区a1的图5,导电材料层190可以包括堆叠的第一导电层191、第二导电层192和第三导电层193,并且可以在第三导电层193上形成掩模材料层194。第一导电层191可以包括透明导电氧化物(例如,ito)。第二导电层192可以包括金属(例如,银(ag))。第三导电层193可以包括透明导电氧化物(例如,ito)。

97.掩模材料层194可以由可以使用具有高选择性的蚀刻剂蚀刻的材料形成,并且可以包括氧化物半导体。氧化物半导体可以包括至少一种金属(诸如锌(zn)、铟(in)、镓(ga)、锡(sn)和钛(ti)中的至少一种)的至少一种氧化物。氧化物半导体可以包括氧化铟锌(izo)、氧化铟镓锌(igzo)、氧化铟锌(izto)、氧化锌锡(zto)和氧化锌(zno)中的至少一种。掩模材料层194可以包括氧化铟镓锌(igzo)和/或氧化铟锌(izo)。取决于氧含量,氧化物半导体可以具有导体特性或绝缘体特性。

98.参照图4和6,可以将导电材料层190和掩模材料层194进行图案化以形成包括像素电极e1和延伸电极et的(剩余)导电层和(剩余)掩模层196。可以通过蚀刻导电材料层190和掩模材料层194来执行导电材料层190和掩模材料层194的图案化。例如,在掩模材料层194上施加(例如,涂覆)光刻胶之后,使用光掩模形成感光膜图案pr,并且使用感光膜图案pr湿法蚀刻掩模材料层194和导电材料层190以形成像素电极e1和延伸电极et。当蚀刻导电材料层190时,由于掩模材料层194覆盖导电材料层190,因此可以防止或减少对导电材料层190(特别是像素电极e1边缘附近的第三导电层193)的损坏。如果第三导电层193被严重损坏,则第二导电层192的材料可能在后续工艺(例如,像素限定层200的固化)中通过第三导电层193泄漏。泄漏的材料(例如,银(ag))可能结块,并且可能导致像素电极e1和公共电极e2之间的短路,这可能导致显示的图像中出现暗点。可以通过使用掩模材料层194防止对第三导电层193的损坏来防止暗点。

99.在将导电材料层190和掩模材料层194图案化之后,掩模层196可以定位在像素电极e1上。延伸电极et的最上层可以是掩模层196的一部分。由于延伸电极et与像素电极e1一

体形成,并且延伸电极et通过连接构件179电连接到晶体管tr,因此像素电极e1可以电连接到晶体管tr。可以通过剥离工艺去除定位在像素电极e1和延伸电极et上的感光膜图案pr。

100.参照图7,具有暴露像素电极e1的开口op的像素限定层200可以通过在第二平坦化层183上施加有色材料层并且图案化有色材料层来形成。可以在第二平坦化层183、像素电极e1和延伸电极et上涂覆黑色光刻胶。接着,在第一温度下进行软烘。接着,使用光掩模选择性地照射光并且显影用于图案化。可以使用显影剂去除涂覆的光刻胶中未被光照射的区。结果,可以暴露掩模层196的至少一部分。去除的区可以与开口op相对应。在对像素限定层200进行显影之后,可以在第二温度下进行硬烘。像素限定层200可以覆盖像素电极e1的边缘,并且可以完全覆盖延伸电极et。黑色光刻胶可以是分散有黑色颜料的光敏化合物,并且光敏化合物可以包括聚合物、单体和光聚合引发剂。黑色光刻胶可以是负性光刻胶。当形成像素限定层200时,像素电极e1被掩模层196覆盖,并且因此可以防止用于形成像素限定层200的材料接触或粘附到像素电极e1。

101.参照图7和图8,掩模层196的定位在像素电极e1上的部分(包括掩模层196的暴露部分和一些覆盖部分)可以通过使用像素限定层200作为掩模通过蚀刻来去除。因此,如图7至图9中所示,像素电极e1可以包括第一导电层191、第二导电层192和第三导电层193,并且可以不包括掩模层196的部分。延伸电极et可以包括第一层和第二层,第一层可以包括在第三导电层193上的覆盖掩模层198(即,掩模层196的覆盖部分),并且第二层可以包括第一导电层191(即,第一透明导电氧化物层)、第二导电层192(即,金属层)和第三导电层193(即,第二透明导电氧化物层)。像素电极e1的最上层可以是第三导电层193,并且延伸电极et的最上层可以是覆盖掩模层198。第一层可以设置在第二层与像素限定层200之间。此外,由于覆盖掩模层198是在对导电材料层190和掩模材料层194(包括氧化物半导体)进行图案化之后形成的掩模层196的覆盖部分,覆盖掩模层198(即,第一层)可以包括氧化物半导体。第二层可以直接连接像素电极e1。像素电极e1的厚度t1可以比延伸电极et的厚度t2薄覆盖掩模层198(即,第一层)的厚度。

102.当去除掩模层196在像素电极e1上的部分时,也可以去除与像素限定层200相关联的上覆的不需要的材料。如果与像素限定层200相关联的不需要的材料导致像素电极e1和公共电极e2之间的短路,则在显示的图像中可能出现不希望的暗点。由于当去除掩模层196的部分时去除了不需要的材料,因此可以防止暗点。

103.可以使用对像素电极e1(特别是对第三导电层193)具有高选择比的蚀刻剂对掩模层196在像素电极e1上的部分进行湿蚀刻。尽管掩模层196用于防止在发光显示装置的制造工艺中损坏像素电极e1,但是可以在不增加光掩模的情况下去除掩模层196在像素电极e1上的部分。由于湿法刻蚀的各向同性,因此也可以去除掩模层196在像素电极e1的被像素限定层200覆盖的边缘上的部分。结果,可以在像素限定层200和像素电极e1之间形成间隙g。

104.参照图10,在已经去除了掩模层196(参照图7)的在像素电极e1上的部分之后,像素限定层200可以在第三温度下固化。第三温度可以高于第一温度和第二温度,并且可以是例如大约230℃或更高,或者可以是大约250℃至大约300℃。在固化期间,像素限定层200的边缘可能由于高温而回流。因此,可以填充像素限定层200和像素电极e1之间的间隙g(参照图8),使得像素限定层200可以直接接触像素电极e1的边缘的上表面,并且可以覆盖像素电极e1的边缘。随着像素限定层200的边缘扩展到开口op,可以减小开口op的宽度,并且可以

形成像素限定层200的双台阶结构。像素限定层200的边缘部分可以具有拐点p。在截面图中,像素限定层200的在间隔物205(参照图11)和拐点p之间的上表面的斜率大于像素限定层200的在拐点p和开口op之间的上表面的斜率。

105.参照图11,可以在像素限定层200上形成间隔物205。间隔物205可以支撑用于沉积发射层el(参照图12)的精细金属掩模,以防止精细金属掩模损坏下面的结构。间隔物205可以包括与像素限定层200的材料不同的材料,并且可以包括诸如基于丙烯酸的聚合物、基于酰亚胺的聚合物或基于酰胺的聚合物的有机绝缘材料。间隔物205可以在显示装置的平面图中具有一种或多种形状,诸如多边形(例如,三角形)和圆形中的一种或多种。

106.参照图12,可以在像素电极e1上形成发射层el,并且可以在发射层el上形成公共电极e2。可以使用精细金属掩模来沉积发射层el,并且可以使用开放掩模来沉积公共电极e2。接着,可以在公共电极e2上形成图2中示出的封装层ec。

107.图13是示出在根据实施例的发光显示装置的平面图中显示面板中的像素限定层的开口及其附近的图片。

108.参照图7和图13,由箭头指示的相对亮的部分与限定开口op的基本上四边形形状的像素限定层200的边缘部分相对应。像素限定层200的边缘略微倾斜,并且具有双台阶结构。双台阶结构可能是由于去除了掩模层196在像素电极e1上的部分,并且然后对像素限定层200的边缘进行回流所致。左边的三角形结构是形成在像素限定层200上的间隔物205(参照图12)。

109.图14是根据实施例的发光显示装置的显示面板10'的一个像素区域的示意性截面图。

110.与图2中示出的显示面板10相比,图14中示出的显示面板10'不包括第二数据导电层。在显示面板10'中,平坦化层180可以定位在包括晶体管tr的第一电极se和第二电极de的第一数据导电层上,并且延伸电极et可以从像素电极e1延伸,并且可以穿过形成在平坦化层180中的接触孔h连接到晶体管tr的第二电极de。因此,像素电极e1可以通过延伸电极et连接到晶体管tr的第二电极de。参照图2描述的初始化电压线127、扫描线151、先前扫描线152、发光控制线153、数据线171和驱动电压线172可以被包括在第一栅极导电层、第二栅极导电层、第一数据导电层或另一可能的导电层中。

111.图15是根据实施例的发光显示装置的像素px的等效电路图。

112.参照图15,像素px可以包括连接到信号线127、151、152、153、158、171和172的晶体管t1至t7、存储电容器cs和发光二极管led。

113.晶体管t1至t7可以包括驱动晶体管t1、开关晶体管t2、补偿晶体管t3、初始化晶体管t4、操作控制晶体管t5、发光控制晶体管t6和旁路晶体管t7。

114.信号线127、151、152、153、158、171和172可以包括初始化电压线127、扫描线151、先前扫描线152、发光控制线153、旁路控制线158、数据线171和驱动电压线172。

115.扫描线151可以将扫描信号gw传输到开关晶体管t2和补偿晶体管t3。先前扫描线152可以将先前扫描信号gi传输到初始化晶体管t4。发光控制线153可以将发射控制信号em传输到操作控制晶体管t5和发光控制晶体管t6。旁路控制线158可以将旁路信号gb传输到旁路晶体管t7。旁路控制线158也可以连接到先前扫描线152。

116.数据线171可以接收数据电压v

dat

,并且驱动电压线172和初始化电压线127可以分

别接收驱动电压el

vdd

和初始化电压v

int

。初始化电压v

int

可以将驱动晶体管t1初始化。

117.晶体管t1至t7分别包括栅极电极g1、g2、g3、g4、g5、g6和g7,可以分别包括第一电极s1、s2、s3、s4、s5、s6和s7,并且可以分别包括第二电极d1、d2、d3、d4、d5、d6和d7。存储电容器cs包括第一电极c1和第二电极c2。晶体管t1至t7的电极和存储电容器cs的电极可以如图15中所示连接。发光二极管led的阳极可以通过发光控制晶体管t6与驱动晶体管t1的第二电极d1连接,并且供应有驱动电流id。发光二极管led的阴极可以施加有公共电压el

vss

(也被称为第二电源电压或低电位电源电压)。

118.在像素px的电路结构中,晶体管的数量、电容器的数量以及它们之间的连接可以根据实施例进行修改。

119.尽管已经描述了实施例的示例,但是具体实施例不限于所公开的实施例。具体实施例旨在覆盖所附权利要求的范围内的各种修改和等效布置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1