一种适应卫星信道的传真设备系统的制作方法

1.本实用新型属于数字语音通信技术领域,涉及适用于卫星信道的传真算法的集成实现,具体是一种适应卫星信道的传真设备系统。

背景技术:

2.数字声码器(vocoder)在一种为降低信道传输码率而对话音进行压缩和解压缩的一种数字装置。声码器在发送端接收数字化语音或者模拟化语音,对数字语音信号进行压缩编码,在接收端进行数字语音解码,还原成原始的模拟语音信号或者数字信号。通过声码器降低语音传输对信道带宽的要求,多用于无线话音通信和保密话音通信,尤其在移动通信领域得到了广泛地应用。

3.为了更好地节省传输信道带宽,增强语音通信抗干扰能力和保密性能,需要尽可能地降低语音编码速率。为此,国内外提出了各种语音编码算法,包括melp、ambe、celp等。目前,我国卫星通信、数字对讲语音通信、超短波通信等无线通信正在迅猛发展。为了满足我国无线通信自主发展的需要,高质量多速率功能完善接口灵活的声码器成为了必须解决的问题。

4.当前,声码器的算法研究已经非常成熟。编码算法种类繁多,包括国外的melp、ambe、celp等,国内的selp。编码速率从高速率、中速率和低速率也都基本覆盖,从64kbps到0.6kbps都有相应的算法提出。这些算法为声码器的研制开发提供的基本的技术基础。

5.基于这些语音编码算法的研究成功,研制出了各种各样的声码器,用于满足话音通信的需要。其中,应用最广泛的就是声码器在移动通信中的应用,这类应用的方式,都是由大的移动厂商或方案提供商在基带芯片中将语音编码算法进行集成。但是,这种应用方式的代价较高,集成后后期无法修改,主要应用于移动通信这一类应用量大、实现方案已经标准化的领域。在卫星通信等领域,应用量还达不到采用基带芯片集成的方法,而且不同类型卫星采用的编码速率和功能要求可能会发生变化,声码器一般采用单独的模块实现。

6.国内采用单独模块实现声码器的技术也相对较多。比如采用dsp芯片实现语音编码算法。或者采用专用编解码芯片实现话音通信功能。但是,这些实现方案基本存在以下问题。一是都采用国外设计与生产的dsp芯片,受芯片厂家影响较大,尤其在贸易摩擦加剧的情况下,自主性无法得到保证。二是使用国外芯片,可能存在后门问题,安全性存疑。三是由于dsp芯片使用范围较通用cpu更窄,国内厂商生产较少,可靠性及运算能力都不可靠,应该采用公共架构的通用cpu来进行设计。四是除了主要芯片外,很多较小芯片也采用国外芯片,距离全国产化要求差距较大。

技术实现要素:

7.实用新型目的:提供一种适应卫星信道的传真设备系统,解决上述提到的问题。

8.技术方案:一种适应卫星信道的传真设备系统,包括:主控处理单元、逻辑编程单元、信号转换单元、以及闪存单元。

9.在进一步的实施例中,主控处理单元包括:arm芯片u2、电阻r1、电阻r2、电阻r8、电容e2、电容e3、电阻r14、电阻r15、电阻r29、电阻r30、电容c25、电容c26、电容e7、差模滤波电感fb1、电容c13、电容c14、电阻r32、电阻r33、电阻r17、电阻r19、电阻r9、电阻r10、电阻r12、晶振y1;所述arm芯片u2的adcinbo-adcinb7引脚同时与所述电阻r1的一端连接,所述电阻r1的另一端接地,所述arm芯片u2的adcinao-adcina7引脚同时与所述电阻r2的一端连接,所述电阻r2的另一端接地,所述arm芯片u2的vssa2引脚、vssa1引脚、vss引脚接地,所述arm芯片u2的vdda1引脚、vdda2引脚、vddio引脚和vdd3vfl引脚接vdd3v3,所述arm芯片u2的vdd引脚接vddcore,所述arm芯片u2的adcrefm引脚与所述电容e2的一端连接,所述arm芯片u2的adcrefp引脚与所述电容e3的一端连接,所述arm芯片u2的adcresext引脚与所述电阻r8的一端连接,所述arm芯片u2的acssrefbg引脚、adclo引脚、vss1引脚分别与所述电阻r8的另一端、所述电容e2的另一端和所述电容e3的另一端连接,所述arm芯片u2的gpioa2/pwm3引脚与所述电阻r15的一端连接,所述arm芯片u2的gpioa2/pwm4引脚与所述电阻r14的一端连接,所述电阻r15的另一端与所述电阻r14的另一端连接且输入vdd3v3;所述arm芯片u2的gpio0引脚同时与所述电阻r32的一端、所述电容c13的一端和诉讼电阻r32的一端连接,所述arm芯片u2的gpio1引脚同时与所述电阻r30的一端、所述电容c14的一端和诉讼电阻r33的一端连接,所述arm芯片u2的gpio2引脚与所述电阻r39的一端连接,所述电阻r30的另一端同时与所述电阻r29的另一端和所述电阻r31的另一端连接且接vdd3v3,所述电容c13的另一端与电容c14的另一端都接地,所述电阻r32的另一端与所述电阻r33的另一端进行输出,所述arm芯片u2的xhold引脚与所述电阻r9的一端连接,所述arm芯片u2的xready引脚与所述电阻r10的一端连接,所述电阻r9的另一端与所述电阻r10的另一端连接且接vdd3v3,所述arm芯片u2的xwe引脚、xr/w引脚接电话接口tp3和电话接口tp4,所述arm芯片u2的xmp/mc引脚与所述电阻r12的一端连接,所述电阻r12的另一端接地,所述arm芯片u2的gpiof10引脚与所述电阻r17的一端连接,所述arm芯片u2的gpiof11引脚与所述电阻r19的一端连接,所述arm芯片u2的x1引脚与所述电阻r35的一端连接,所述晶振y1的3号引脚与所述电阻r35的另一端连接,所述晶振y1的4号引脚同时与所述电容c26的一端、所述电容e7的一端和所述差模滤波电感fb1的一端连接,所述晶振y1的1号引脚不接,所述晶振y1的2号引脚同时与所述电容c26的另一端、所述电容e7的另一端和所述电容c25的一端连接且接地,所述电容c25的另一端与所述差模滤波电感fb1的另一端连接且接vdd1v8。

10.在进一步的实施例中,闪存单元包括:flash存储器u1、电容c1、电容e1、电容c2、电阻r7、电阻r5;其中,所述flash存储器u1的a0-a18引脚与所述arm芯片u2的xa1-xa18引脚依次连接,所述flash存储器u1的dq0-dq15引脚与所述arm芯片u2的d0-d15引脚依次连接,所述flash存储器u1的rst#引脚同时与所述电阻r5的一端和所述电容c1的一端连接,所述电容c1的另一端接地,所述flash存储器u1的vss1引脚和vss2引脚接地,所述flash存储器u1的ry/by#引脚同时与所述电阻r7的一端和电话接口tp1连接,所述flash存储器u1的vdd引脚同时与所述电容c2的一端和所述电容e1的一端连接且接vdd3v3,所述电容c2的另一端和所述电容e1的另一端接地,所述电阻r5的另一端接vdd3v3,所述flash存储器u1的wp3#引脚接vdd3v3。

11.在进一步的实施例中,信号转换单元包括:集成电路u3、晶振y2、电容c27、电容c28、电容e10、差模滤波电感fb2、电阻r56、电容e8、电容e9、电阻r52、电阻r46、电阻r47、功

率分析器u4;其中,所述集成电路u3的gnd引脚接地,所述集成电路u3的clk0/i引脚同时与所述电阻r56的一端和所述功率分析器u4的x1/xclkin引脚连接,所述集成电路u3的vcc引脚接vdd3v3,所述晶振y2的3号引脚与所述电阻r56的一端连接,所述晶振y2的4号引脚同时与所述电容c28的一端、所述电容e10的一端和所述差模滤波电感fb2的一端连接,所述晶振y2的1号引脚不接,所述晶振y1的2号引脚同时与所述电容c26的另一端、所述电容e7的另一端和所述电容c25的一端连接且接地,所述电容c25的另一端与所述差模滤波电感fb1的另一端连接且接vdd1v8。

12.在进一步的实施例中,逻辑编程单元包括:音频编解码器u5、电容c62、电容c63、电容c64、电容c67、电容c68、电阻r63、电阻r64、电阻r76、电阻r78、电阻r74、电容c65、电容e23、电容c66、电容c60、电容c61、微处理器u6、电阻r79、电阻r81、电阻r75、电阻r77、电容c69、电阻r80、电阻r23、电阻r83、稳压芯片u7、电容c70、电容e24、电容c72、电容c71、电容e17、稳压芯片u11、电容c85、电容e21、电容c84、电容c83、电容e26、电阻r92、led灯d7、电阻r84;其中,所述音频编解码器u5的ep引脚输出,所述音频编解码器u5的20号引脚同时与所述电阻r63的一端和所述电阻r64的一端连接,所述电阻r63的另一端接地,所述电阻r64的另一端接vdd3v3,所述音频编解码器u5的18号引脚与所述电容c61的一端连接,所述音频编解码器u5的17号引脚与所述电容c60的一端连接,所述音频编解码器u5的16号引脚与所述电容c62的一端连接,所述电容c62的另一端与所述电容c60的另一端输出,所述音频编解码器u5的2号引脚与所述电阻r74的一端连接,所述音频编解码器u5的3号引脚同时与所述电容e23的一端和所述电容c65的一端连接且接vdd3v3,所述音频编解码器u5的4号引脚与所述电容c66的一端连接,所述音频编解码器u5的5号引脚同时与所述电容c66的另一端、所述电容c65的另一端和所述电容e23的另一端连接且接地,所述音频编解码器u5的6号引脚与所述电阻r76的一端连接,所述音频编解码器u5的8号引脚与所述电阻r78的一端连接,所述音频编解码器u5的15号引脚与所述电容c63的一端连接,所述音频编解码器u5的14号引脚与所述电容c64的一端连接,所述音频编解码器u5的13号引脚接电话接口tp10、所述音频编解码器u5的11号引脚同时与所述电容c67的一端和所述电容c68的一端连接且接vdd3v3,所述音频编解码器u5的10号引脚同时与所述电容c67的另一端和所述电容c68的另一端连接且输出,所述微处理器u6的1号引脚同时与所述电阻r79的一端和所述电阻r81的一端连接,所述微处理器u6的2号引脚同时与所述电阻r81的另一端、所述电阻r75的一端、所述电阻r77的一端和所述电容c69的一端连接且接vdd3v3,所述电容c29的另一端接地,所述微处理器u6的8号引脚与所述电阻r80的一端连接,所述微处理器u6的7号引脚与所述电阻r82的一端连接,所述微处理器u6的6号引脚与所述电阻r83的一端连接,所述微处理器u6的3号引脚、4号引脚接地,所述电阻r75的另一端与所述电阻r82的另一端连接,所述电阻r77的另一端与所述电阻r80的另一端连接;所述稳压芯片u7的1号引脚、3号引脚同时与所述电容c70的一端和所述电容e24的一端连接,所述稳压芯片u7的4号引脚与所述电容c72的一端连接,所述稳压芯片u7的5号引脚同时与所述电容c71的一端和所述电容e17的一端连接且接电话接口,所述稳压芯片u7的2号引脚同时与所述电容c70的另一端、所述电容e24的另一端、所述电容c72的另一端、所述电容c71的另一端和所述电容e17的另一端连接且接地,所述led灯d7的正极接vdd3v3,所述led灯d7的负极与所述电阻r84的一端连接,所述电阻r84的另一端接地,所述稳压芯片u11的1号引脚、3号引脚同时与所述电容c85的一端和所述电容e21的

一端连接,所述稳压芯片u7的4号引脚与所述电容c84的一端连接,所述稳压芯片u7的5号引脚同时与所述电容c83的一端和所述电容e26的一端连接且接电话接口,所述稳压芯片u7的2号引脚同时与所述电容c85的另一端、所述电容e21的另一端、所述电容c84的另一端、所述电容c83的另一端和所述电容e26的另一端连接且接地,所述电容e26的另一端接电话接口,所述点r92的一端接vdd,所述电阻r92的另一端接vdd3v3。

13.在进一步的实施例中,所述的arm芯片u2型号为gd32f407,所述flash存储器u1的型号为29lv16、所述晶振y1和所述晶振y2的型号均为18.432mhz,所述集成电路u3的型号为sg4128v-75t100i,所述功率分析器u4的型号为wt3000,所述音频编解码器u5的型号为es8311,所述微处理器u6的型号为sgm706r,所述稳压芯片u7和所述稳压芯片u11的型号均为me6211/6207c33。

14.在进一步的实施例中,信号转换单元还包括:电容c31、电容c32、电容c34、电容c35、电容c36、电容c37、电容c33、电容c38、电容c39、电容c40、电容e12、电容e13、电容c41、电容c42、电容c43、电容c44、电容c45、电容c46、电容c47、电容c48、电容c49、电容c50电容e14、电容c51、电容c52、电容c53、电容c54、电容c55、电容c56、电容c57、电容c58、电容c59;其中,所述电容c31、所述电容c32、所述电容c34、所述电容c35、所述电容c36、所述电容c37、所述电容c33、所述电容c38、所述电容c39、所述电容c40和所述电容e12的一端依次连接且接vdd3v3,所述电容c31、所述电容c32、所述电容c34、所述电容c35、所述电容c36、所述电容c37、所述电容c33、所述电容c38、所述电容c39、所述电容c40和所述电容e12的另一端依次连接且接地;所述电容c41、所述电容c42、所述电容c44、所述电容c45、所述电容c46、所述电容c47、所述电容c43、所述电容c48、所述电容c49、所述电容c50和所述电容e13的一端依次连接且接vdd3v3,所述电容c41、所述电容c42、所述电容c44、所述电容c45、所述电容c46、所述电容c47、所述电容c43、所述电容c48、所述电容c49、所述电容c50和所述电容e13的另一端依次连接且接地;所述电容c51、所述电容c52、所述电容c54、所述电容c55、所述电容c56、所述电容c57、所述电容c53、所述电容c58、所述电容c59和所述电容e14的一端依次连接且接vdd3v3,所述电容c51、所述电容c52、所述电容c54、所述电容c55、所述电容c56、所述电容c57、所述电容c53、所述电容c58、所述电容c59和所述电容e14的另一端依次连接且接地。

15.在进一步的实施例中,语音编码速率和语音编码速率可以进行切换;由于卫星通信不同轨道的卫星、不同的通信波段,其通信带宽不同,这就要求不同条件下语音编码速率不同。另外,卫星通信对抗干扰能力的要求和调制方式等也对语音编码的速率提出了不同需要;而且,编码速率要求能实时进行切换;另外,基于各种互通考虑,声码器要实现多种语音编码算法;采用dsp芯片优化实时实现。该发明独劈新径,采用通用的cortex

-ꢀ

m内核芯片,实现了编码模式基本覆盖了中低速率领域的各种语音编码模式和语音编码速率;语音编码速率主要包括64kbps、8kbps、4kbps、2.4kbps、2.0kbps等。从而满足了卫星通信各个轨道卫星、各个波段卫星、各种应用环境的各种需求,确保了高质量话音通信和互通;为了实现速率的实时切换,同时采用同一模式软件切换、不同模式动态加载的方式相结合,并提出了一种加速实时加载的方法提高速率切换的实时性;速率切换由上位机发起,通过监控接口发送速率切换命令;声码器对速率切换命令进行实时响应,实时切换到上位机要求的速率,完成编码和解码功能。

16.在进一步的实施例中,可以实现语音通信相关功能,通信终端信令包括提示音、拨

号音、忙音、按键音等;这些信令音的实现包括信令音的产生和检测两大功能;语音通信中的其他主要功能主要包括回波抵消、噪声抑制、话音激活检测、舒适噪声产生等;回波抵消主要针对二线话机的信号在二/四线转换过程中的信号泄露问题,避免在通话中从对端传来说话人自己的说话声;回波抵消可以采用回波抵消芯片实现,也可以采用回波抵消算法软件实现;噪声抑制主要针对背景噪声对语音的影响,抑制背景噪声,如背景风扇声、风声、枪炮声等。噪声抑制可以采用噪声抑制芯片实现,也可以采用噪声抑制算法实现。

17.在进一步的实施例中,信令检测采用了频谱分析和信号分类判决技术;频谱分析可以采用fft、goertzel等算法;对频谱分析结果,根据不同信号的特性进行判决检测;例如,针对dtmf信号,主要根据高低频谱对的频谱幅度大小差距、频谱位置、频谱峰值度等进行判决。针对用户信令音,主要根据频率峰值度、信令音时长特性等进行检测;为了避免误判,对检测结果采用了平滑后处理等技术。

18.在进一步的实施例中,语音编解码的优化实现:

19.a、算法级优化

20.首先进行的是算法级的优化;这个层次上的优化要结合实现的功能,考虑在不影响性能的前提下,换用速度更快、占用内存更少的替代算法;例如,语音处理通常都是在频域进行,因此要将分帧后的语音数据进行fft处理;处理完之后,还要将频域数据进行反变换,合成到时域;不论是正变化还是反变换,n点的实数fft都可以通过调用n/2点的cfft来处理;

21.b、语言级优化;

22.a)减少不必要的变量;

23.b)将频繁调用的较小的子程序并入到调用程序中;

24.c)对于多级循环,如果循环次数较少而且循环体不大,可以考虑直接展开在上一级循环中,以节省循环过多时对辅助寄存器的占用;

25.c、汇编级优化;

26.c语言级优化后,可以借助arm工具,将重要c程序转化为可被c调用的汇编函数;如果主程序中存在计算量过多的部分,可以考虑用子函数实现,然后将子函数转化为汇编,这样既能保持程序有较高的可读性,同时效率又能有所提高;对于汇编程序的优化,主要是联系所用芯片的语言,了解常用指令及专用数字信号处理的指令等。从c编译后的汇编函数手工优化,保留各个参数的压栈顺序,可以满足这一要求。

27.在进一步的实施例中,为了满足不同型号产品需要,设计了灵活的接口。接口包括语音接口、监控接口和信道接口;语音接口用于输入输出语音信号,该接口可以选择采用模拟语音输入输出,也可以采用数字pcm语音输入输出;监控接口用于发送和接收语音命令、语音状态,如速率切换命令、声码器状态、信令产生命令等。信道接口用于传输和发送语音编码数据。

28.有益效果:本实用新型可以有效提高语音编码质量;语音编码在64kbps速率下,语音编码质量pesq得分可以达到4.0分。在8kbps速率下,语音编码质量pesq得分可以达到3.5分。在4kbps速率下,语音编码质量pesq得分可以达到3.4分。在2.4kbps/2kbps速率下,语音编码质量pesq得分可以达到3.2分;同时可以进行语音编码模式和速率切换;通过监控接口,发送各种语音编码模式和速率切换命令。声码器在接收到切换命令后能正常快速切换,

通过监控接口上报切换成功命令和各种模式的指示灯指示切换成功;同时具有回波抵消功能;因为卫星通信线路较长,会造成通话中说话的人会被自己声音的回波干扰;而本实用新型的回波抵消可以抵消的回波延时达到64ms;此外本实用新型由噪声抑制功能;背景噪声会对用户的通话语音造成干扰,本发明实现的噪声抑制可以将白噪声衰减达到35db;同时可以准确的信号音产生,信号音产生频率准确度可以达到100%,时长控制没有误差;同时具有信令检测功能;对各种按键音和信号音能准确检测,并通过监控接口上报。信号音检出率为100%,误检率为0.1%。

附图说明

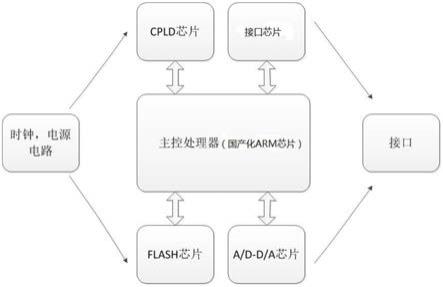

29.图1是本实用新型的总体方案图。

30.图2是本实用新型的接口示意图。

31.图3是本实用新型的实施方式结构示意图。

32.图4是本实用新型的主控处理单元电路图。

33.图5是本实用新型的闪存单元电路图。

34.图6是本实用新型的信号转换单元部分电路图。

35.图7是本实用新型的信号转换单元部分电路图。

36.图8是本实用新型的信号转换单元部分电路图。

37.图9是本实用新型的逻辑编程单元部分电路图。

38.图10是本实用新型的逻辑编程单元部分电路图。

具体实施方式

39.在下文的描述中,给出了大量具体的细节以便提供对本实用新型更为彻底的理解。然而,对于本领域技术人员而言显而易见的是,本实用新型可以无需一个或多个这些细节而得以实施;在其他的例子中,为了避免与本实用新型发生混淆,对于本领域公知的一些技术特征未进行描述。

40.一种适应卫星信道的传真设备系统,包括:主控处理单元、逻辑编程单元、信号转换单元、以及闪存单元。

41.其中,主控处理单元包括:arm芯片u2、电阻r1、电阻r2、电阻r8、电容e2、电容e3、电阻r14、电阻r15、电阻r29、电阻r30、电容c25、电容c26、电容e7、差模滤波电感fb1、电容c13、电容c14、电阻r32、电阻r33、电阻r17、电阻r19、电阻r9、电阻r10、电阻r12、晶振y1;

42.闪存单元包括:flash存储器u1、电容c1、电容e1、电容c2、电阻r7、电阻r5;

43.信号转换单元包括:集成电路u3、晶振y2、电容c27、电容c28、电容e10、差模滤波电感fb2、电阻r56、电容e8、电容e9、电阻r52、电阻r46、电阻r47、功率分析器u4;电容c31、电容c32、电容c34、电容c35、电容c36、电容c37、电容c33、电容c38、电容c39、电容c40、电容e12、电容e13、电容c41、电容c42、电容c43、电容c44、电容c45、电容c46、电容c47、电容c48、电容c49、电容c50电容e14、电容c51、电容c52、电容c53、电容c54、电容c55、电容c56、电容c57、电容c58、电容c59;

44.逻辑编程单元包括:音频编解码器u5、电容c62、电容c63、电容c64、电容c67、电容c68、电阻r63、电阻r64、电阻r76、电阻r78、电阻r74、电容c65、电容e23、电容c66、电容c60、

电容c61、微处理器u6、电阻r79、电阻r81、电阻r75、电阻r77、电容c69、电阻r80、电阻r23、电阻r83、稳压芯片u7、电容c70、电容e24、电容c72、电容c71、电容e17、稳压芯片u11、电容c85、电容e21、电容c84、电容c83、电容e26、电阻r92、led灯d7、电阻r84。

45.如图4所示,所述arm芯片u2的adcinbo-adcinb7引脚同时与所述电阻r1的一端连接,所述电阻r1的另一端接地,所述arm芯片u2的adcinao-adcina7引脚同时与所述电阻r2的一端连接,所述电阻r2的另一端接地,所述arm芯片u2的vssa2引脚、vssa1引脚、vss引脚接地,所述arm芯片u2的vdda1引脚、vdda2引脚、vddio引脚和vdd3vfl引脚接vdd3v3,所述arm芯片u2的vdd引脚接vddcore,所述arm芯片u2的adcrefm引脚与所述电容e2的一端连接,所述arm芯片u2的adcrefp引脚与所述电容e3的一端连接,所述arm芯片u2的adcresext引脚与所述电阻r8的一端连接,所述arm芯片u2的acssrefbg引脚、adclo引脚、vss1引脚分别与所述电阻r8的另一端、所述电容e2的另一端和所述电容e3的另一端连接,所述arm芯片u2的gpioa2/pwm3引脚与所述电阻r15的一端连接,所述arm芯片u2的gpioa2/pwm4引脚与所述电阻r14的一端连接,所述电阻r15的另一端与所述电阻r14的另一端连接且输入vdd3v3;所述arm芯片u2的gpio0引脚同时与所述电阻r32的一端、所述电容c13的一端和诉讼电阻r32的一端连接,所述arm芯片u2的gpio1引脚同时与所述电阻r30的一端、所述电容c14的一端和诉讼电阻r33的一端连接,所述arm芯片u2的gpio2引脚与所述电阻r39的一端连接,所述电阻r30的另一端同时与所述电阻r29的另一端和所述电阻r31的另一端连接且接vdd3v3,所述电容c13的另一端与电容c14的另一端都接地,所述电阻r32的另一端与所述电阻r33的另一端进行输出,所述arm芯片u2的xhold引脚与所述电阻r9的一端连接,所述arm芯片u2的xready引脚与所述电阻r10的一端连接,所述电阻r9的另一端与所述电阻r10的另一端连接且接vdd3v3,所述arm芯片u2的xwe引脚、xr/w引脚接电话接口tp3和电话接口tp4,所述arm芯片u2的xmp/mc引脚与所述电阻r12的一端连接,所述电阻r12的另一端接地,所述arm芯片u2的gpiof10引脚与所述电阻r17的一端连接,所述arm芯片u2的gpiof11引脚与所述电阻r19的一端连接,所述arm芯片u2的x1引脚与所述电阻r35的一端连接,所述晶振y1的3号引脚与所述电阻r35的另一端连接,所述晶振y1的4号引脚同时与所述电容c26的一端、所述电容e7的一端和所述差模滤波电感fb1的一端连接,所述晶振y1的1号引脚不接,所述晶振y1的2号引脚同时与所述电容c26的另一端、所述电容e7的另一端和所述电容c25的一端连接且接地,所述电容c25的另一端与所述差模滤波电感fb1的另一端连接且接vdd1v8。

46.如图5所示,所述flash存储器u1的a0-a18引脚与所述arm芯片u2的xa1-xa18引脚依次连接,所述flash存储器u1的dq0-dq15引脚与所述arm芯片u2的d0-d15引脚依次连接,所述flash存储器u1的rst#引脚同时与所述电阻r5的一端和所述电容c1的一端连接,所述电容c1的另一端接地,所述flash存储器u1的vss1引脚和vss2引脚接地,所述flash存储器u1的ry/by#引脚同时与所述电阻r7的一端和电话接口tp1连接,所述flash存储器u1的vdd引脚同时与所述电容c2的一端和所述电容e1的一端连接且接vdd3v3,所述电容c2的另一端和所述电容e1的另一端接地,所述电阻r5的另一端接vdd3v3,所述flash存储器u1的wp3#引脚接vdd3v3。

47.如图6、图7和图8所示,所述集成电路u3的gnd引脚接地,所述集成电路u3的clk0/i引脚同时与所述电阻r56的一端和所述功率分析器u4的x1/xclkin引脚连接,所述集成电路u3的vcc引脚接vdd3v3,所述晶振y2的3号引脚与所述电阻r56的一端连接,所述晶振y2的4

号引脚同时与所述电容c28的一端、所述电容e10的一端和所述差模滤波电感fb2的一端连接,所述晶振y2的1号引脚不接,所述晶振y1的2号引脚同时与所述电容c26的另一端、所述电容e7的另一端和所述电容c25的一端连接且接地,所述电容c25的另一端与所述差模滤波电感fb1的另一端连接且接vdd1v8;所述电容c31、所述电容c32、所述电容c34、所述电容c35、所述电容c36、所述电容c37、所述电容c33、所述电容c38、所述电容c39、所述电容c40和所述电容e12的一端依次连接且接vdd3v3,所述电容c31、所述电容c32、所述电容c34、所述电容c35、所述电容c36、所述电容c37、所述电容c33、所述电容c38、所述电容c39、所述电容c40和所述电容e12的另一端依次连接且接地;所述电容c41、所述电容c42、所述电容c44、所述电容c45、所述电容c46、所述电容c47、所述电容c43、所述电容c48、所述电容c49、所述电容c50和所述电容e13的一端依次连接且接vdd3v3,所述电容c41、所述电容c42、所述电容c44、所述电容c45、所述电容c46、所述电容c47、所述电容c43、所述电容c48、所述电容c49、所述电容c50和所述电容e13的另一端依次连接且接地;所述电容c51、所述电容c52、所述电容c54、所述电容c55、所述电容c56、所述电容c57、所述电容c53、所述电容c58、所述电容c59和所述电容e14的一端依次连接且接vdd3v3,所述电容c51、所述电容c52、所述电容c54、所述电容c55、所述电容c56、所述电容c57、所述电容c53、所述电容c58、所述电容c59和所述电容e14的另一端依次连接且接地。

48.如图9和图10所示,所述音频编解码器u5的ep引脚输出,所述音频编解码器u5的20号引脚同时与所述电阻r63的一端和所述电阻r64的一端连接,所述电阻r63的另一端接地,所述电阻r64的另一端接vdd3v3,所述音频编解码器u5的18号引脚与所述电容c61的一端连接,所述音频编解码器u5的17号引脚与所述电容c60的一端连接,所述音频编解码器u5的16号引脚与所述电容c62的一端连接,所述电容c62的另一端与所述电容c60的另一端输出,所述音频编解码器u5的2号引脚与所述电阻r74的一端连接,所述音频编解码器u5的3号引脚同时与所述电容e23的一端和所述电容c65的一端连接且接vdd3v3,所述音频编解码器u5的4号引脚与所述电容c66的一端连接,所述音频编解码器u5的5号引脚同时与所述电容c66的另一端、所述电容c65的另一端和所述电容e23的另一端连接且接地,所述音频编解码器u5的6号引脚与所述电阻r76的一端连接,所述音频编解码器u5的8号引脚与所述电阻r78的一端连接,所述音频编解码器u5的15号引脚与所述电容c63的一端连接,所述音频编解码器u5的14号引脚与所述电容c64的一端连接,所述音频编解码器u5的13号引脚接电话接口tp10、所述音频编解码器u5的11号引脚同时与所述电容c67的一端和所述电容c68的一端连接且接vdd3v3,所述音频编解码器u5的10号引脚同时与所述电容c67的另一端和所述电容c68的另一端连接且输出,所述微处理器u6的1号引脚同时与所述电阻r79的一端和所述电阻r81的一端连接,所述微处理器u6的2号引脚同时与所述电阻r81的另一端、所述电阻r75的一端、所述电阻r77的一端和所述电容c69的一端连接且接vdd3v3,所述电容c29的另一端接地,所述微处理器u6的8号引脚与所述电阻r80的一端连接,所述微处理器u6的7号引脚与所述电阻r82的一端连接,所述微处理器u6的6号引脚与所述电阻r83的一端连接,所述微处理器u6的3号引脚、4号引脚接地,所述电阻r75的另一端与所述电阻r82的另一端连接,所述电阻r77的另一端与所述电阻r80的另一端连接;所述稳压芯片u7的1号引脚、3号引脚同时与所述电容c70的一端和所述电容e24的一端连接,所述稳压芯片u7的4号引脚与所述电容c72的一端连接,所述稳压芯片u7的5号引脚同时与所述电容c71的一端和所述电容e17的一端

连接且接电话接口,所述稳压芯片u7的2号引脚同时与所述电容c70的另一端、所述电容e24的另一端、所述电容c72的另一端、所述电容c71的另一端和所述电容e17的另一端连接且接地,所述led灯d7的正极接vdd3v3,所述led灯d7的负极与所述电阻r84的一端连接,所述电阻r84的另一端接地,所述稳压芯片u11的1号引脚、3号引脚同时与所述电容c85的一端和所述电容e21的一端连接,所述稳压芯片u7的4号引脚与所述电容c84的一端连接,所述稳压芯片u7的5号引脚同时与所述电容c83的一端和所述电容e26的一端连接且接电话接口,所述稳压芯片u7的2号引脚同时与所述电容c85的另一端、所述电容e21的另一端、所述电容c84的另一端、所述电容c83的另一端和所述电容e26的另一端连接且接地,所述电容e26的另一端接电话接口,所述点r92的一端接vdd,所述电阻r92的另一端接vdd3v3。

49.在一个实施例中,本利用了包括主控处理器gd32f407芯片,复杂可编程逻辑器sg1128芯片,外部flash gd25q16芯片,codec转换cjc8988s芯片来实现声码器的各个功能。实施方案实现了全国产化。

50.在一个实施例中,声码器通过接口部分和上位机连接,实现声音编码,切换编码速率等功能。当声码器工作在突发工作模式,主控gd32f407配置cpld及各接口芯片功能模块,当有话音传输进来,声码器开始工作,否则,声码器处于不工作状态;当声码器工作在连续模式,默认一直有话音传输进来,声码器一直处于工作状态。

51.在一个实施例中,当声码器工作的时候,主控gd32f407配合cjc8988s codec转换芯片将语音信号转换成数字信号或者模拟信号输出;同时主gd32f407根据监控接口收到的信令帧调整工作模式;比如接收到信道的突发模式信令帧,主控gd32f407就会根据协议判断接下来要满足的工作的条件,配合对cjc8988s codec转换芯片芯片进行配置,实现上位机编码模式,2.4kbps编码速率的要求。

52.在一个实施例中,对传输的语音数据进行处理,将语音信号采样、量化、编码,然后通过本实用新型的算法,将音频信号中的冗余部分去除;这样处理过的pcm数字信号就可以按照第一实施方式进行收发数据。

53.本实用新型可以使得工作人员按照符合数据传输格式的方式和外部设备通信,发送查询帧对传输过程进行监控,能够很好的运用到卫星通信、数字无线通信、电话通信等领域中去。

54.以上结合附图详细描述了本实用新型的优选实施方式,但是,本实用新型并不限于上述实施方式中的具体细节,在本实用新型的技术构思范围内,可以对本实用新型的技术方案进行多种等同变换,这些等同变换均属于本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1